Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                  |

| Core Size                  | 32-Bit Single-Core                                                |

| Speed                      | 120MHz                                                            |

| Connectivity               | 1-Wire, EBI/EMI, I <sup>2</sup> C, QSPI, SPI, UART/USART, USB     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 105                                                               |

| Program Memory Size        | 3MB (3M x 8)                                                      |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 1M x 8                                                            |

| Voltage - Supply (Vcc/Vdd) | 0.99V ~ 3.6V                                                      |

| Data Converters            | A/D 4x10b Sigma-Delta                                             |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 140-WFBGA, WLBGA                                                  |

| Supplier Device Package    | 140-WLP (4.47x4.43)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/max32652gwe   |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

### **Electrical Characteristics**

(Limits are 100% tested at  $T_A = +25^{\circ}$ C and  $T_A = +105^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested. General Purpose I/O are only tested at  $T_A = +105^{\circ}$ C.)

| PARAMETER                                         | SYMBOL             | CONDITIONS                                                                                                                                                                                                                                                  | MIN          | TYP   | MAX  | UNITS  |  |

|---------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|------|--------|--|

| POWER                                             |                    |                                                                                                                                                                                                                                                             |              |       |      |        |  |

| Supply Voltage, Core                              | V <sub>CORE</sub>  | f <sub>SYS_CLK</sub> = 120MHz                                                                                                                                                                                                                               | 0.99         | 1.1   | 1.21 | V      |  |

| Supply Voltage, Analog                            | V <sub>DDA</sub>   |                                                                                                                                                                                                                                                             | 1.71         | 1.8   | 1.89 | V      |  |

| Supply Voltage, RTC                               | V <sub>RTC</sub>   |                                                                                                                                                                                                                                                             | 1.71         | 1.8   | 1.89 | V      |  |

| Supply Voltage, GPIO                              | V <sub>DDIO</sub>  |                                                                                                                                                                                                                                                             | 1.71         | 1.8   | 1.89 | V      |  |

| Supply Voltage, GPIO<br>(High)                    | V <sub>DDIOH</sub> |                                                                                                                                                                                                                                                             | 1.71         | 1.8   | 3.6  | V      |  |

|                                                   |                    | Monitors V <sub>CORE</sub>                                                                                                                                                                                                                                  |              | 0.835 |      |        |  |

| Power-Fail Reset Voltage                          |                    | Monitors V <sub>DDA</sub>                                                                                                                                                                                                                                   |              | 1.67  |      | v      |  |

| Fower-Fail Reset vollage                          | V <sub>RST</sub>   | Monitors V <sub>RTC</sub>                                                                                                                                                                                                                                   |              | 1.67  |      |        |  |

|                                                   |                    | Monitors V <sub>DDIO</sub>                                                                                                                                                                                                                                  |              | 1.67  |      |        |  |

| Power-Fail Reset Voltage                          | V <sub>RST</sub>   | Monitors V <sub>DDB</sub>                                                                                                                                                                                                                                   |              | 2.95  |      | V      |  |

| Power-Fail Reset Voltage                          | V <sub>RST</sub>   | Monitors V <sub>DDIOH</sub>                                                                                                                                                                                                                                 |              | 1.67  |      | V      |  |

|                                                   |                    | Monitors V <sub>CORE</sub>                                                                                                                                                                                                                                  |              | 0.594 |      |        |  |

| Power-On Reset Voltage                            | V <sub>POR</sub>   | Monitors V <sub>DDA</sub>                                                                                                                                                                                                                                   | 1.52<br>1.17 |       |      | V      |  |

|                                                   |                    | Monitors V <sub>RTC</sub>                                                                                                                                                                                                                                   |              |       |      |        |  |

| RAM Data Retention<br>Voltage                     | V <sub>DRV</sub>   |                                                                                                                                                                                                                                                             |              | 0.81  |      | V      |  |

| V <sub>CORE</sub> Dynamic Current,<br>Active Mode | ICORE_DACT         | Total current into V <sub>CORE</sub> pins, f <sub>SYS_CLK</sub> =<br>120MHz, V <sub>CORE</sub> = 1.1V, CPU in Active mode,<br>executing from cache, inputs tied to V <sub>SS</sub> , V <sub>DDIO</sub> ,<br>or V <sub>DDIOH</sub> , outputs source/sink 0mA |              | 95    |      | µA/MHz |  |

| V <sub>CORE</sub> Fixed Current,                  |                    | 120MHz oscillator enabled, total current into $V_{CORE}$ pins, CPU in Active mode 0MHz execution, inputs tied to $V_{SS}$ , $V_{DDIO}$ , or $V_{DDIOH}$ , outputs source/sink 0mA                                                                           | 1020         |       |      |        |  |

| Active Mode                                       | CORE_FACT          | 7.3728MHz oscillator enabled, total current into $V_{CORE}$ pins, CPU in Active mode 0MHz execution, inputs tied to $V_{SS}$ , $V_{DDIO}$ , or $V_{DDIOH}$ , outputs source/sink 0mA                                                                        |              | 356   |      | - μΑ   |  |

| V <sub>DDA</sub> Fixed Current,<br>Active Mode    |                    | 120MHz oscillator enabled, total current into $V_{DDA}$ pins, CPU in Active mode 0MHz execution, inputs tied to $V_{SS}$ , $V_{DDIO}$ , or $V_{DDIOH}$ , outputs source/sink 0mA , $V_{CORE}$ and $V_{DDA}$ voltage monitors enabled                        | 348          |       |      |        |  |

|                                                   | IDDA_FACT          | 7.3728MHz oscillator enabled, total current into $V_{DDA}$ pins, CPU in Active mode 0MHz execution, inputs tied to $V_{SS}, V_{DDIO},$ or $V_{DDIOH},$ outputs source/sink 0mA , $V_{CORE}$ and $V_{DDA}$ voltage monitors enabled                          |              | 39    |      | - μΑ   |  |

# Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A = +25^{\circ}$ C and  $T_A = +105^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested. General-purpose I/O are only tested at  $T_A = +105^{\circ}$ C.)

| PARAMETER                                               | SYMBOL              | CONDITIONS                                                                         | MIN                       | TYP          | MAX              | UNITS |

|---------------------------------------------------------|---------------------|------------------------------------------------------------------------------------|---------------------------|--------------|------------------|-------|

| USB                                                     |                     | ·                                                                                  |                           |              |                  |       |

| USB Supply Voltage                                      | V <sub>DDB</sub>    |                                                                                    | 3.0                       | 3.3          | 3.6              | V     |

| D+, D- Pin Capacitance                                  | C <sub>IN_USB</sub> | Pin to $V_{SS}$                                                                    |                           | 8            |                  | pF    |

| Driver Output Resistance                                | R <sub>DRV</sub>    | Steady state drive                                                                 |                           | 45<br>±10%   |                  | Ω     |

| USB/FULL SPEED                                          |                     |                                                                                    |                           |              |                  |       |

| Single-Ended Input High<br>Voltage (DP, DM)             | V <sub>IH_USB</sub> |                                                                                    | 2.0                       |              |                  | V     |

| Single-Ended Input Low<br>Voltage (DP, DM)              | V <sub>IL_USB</sub> |                                                                                    |                           |              | 0.6              | V     |

| Output High Voltage<br>(DP, DM)                         | V <sub>OH_USB</sub> | R <sub>L</sub> = 1.5 kΩ from DP and DM to V <sub>SS</sub> , I <sub>OH</sub> = -4mA | V <sub>DDB</sub> -<br>0.4 |              | V <sub>DDB</sub> | V     |

| Output Low Voltage<br>(DP, DM)                          | V <sub>OL_USB</sub> | R <sub>L</sub> = 1.5 kΩ from DP to V <sub>DDB</sub> , I <sub>OL</sub> = 4mA        | V <sub>SS</sub>           |              | 0.4              | V     |

| Differential Input<br>Sensitivity                       | V <sub>DI</sub>     | [DP to DM]                                                                         | 0.2                       |              |                  | V     |

| Common Mode Voltage<br>Range                            | V <sub>CM</sub>     | Includes V <sub>DI</sub> range                                                     | 0.8                       |              | 2.5              | V     |

| Transition Time (Rise/Fall)<br>D+, D- (Note 11)         | t <sub>RF</sub>     | C <sub>L</sub> = 50pF                                                              | 4                         |              | 20               | ns    |

| Pullup Resistor on<br>Upstream Ports                    | R <sub>PU</sub>     |                                                                                    | 1.05                      | 1.5          | 1.95             | kΩ    |

| USB/HI-SPEED                                            |                     |                                                                                    |                           |              |                  |       |

| Hi-Speed Data Signaling<br>Common-Mode Voltage<br>Range | V <sub>HSCM</sub>   |                                                                                    | -50                       |              | +500             | mV    |

| Hi-Speed Squelch                                        | V <sub>HSSQ</sub>   | Squelch detected                                                                   |                           | 100          |                  | mV    |

| Detection Threshold                                     | VHSSQ               | No squelch detected                                                                |                           | 200          |                  | IIIV  |

| Hi-Speed Idle Level<br>Output Voltage                   | V <sub>HSOI</sub>   |                                                                                    | -10                       |              | +10              | mV    |

| Hi-Speed Low Level<br>Output Voltage                    | V <sub>HSOL</sub>   |                                                                                    | -10                       |              | +10              | mV    |

| Hi-Speed High Level<br>Output Voltage                   | V <sub>HSOH</sub>   |                                                                                    |                           | 400<br>± 40  |                  | mV    |

| Chirp-J Output Voltage<br>(Differential)                | V <sub>CHIRPJ</sub> |                                                                                    |                           | 900<br>±200  |                  | mV    |

| Chirp-K Output Voltage<br>(Differential)                | V <sub>CHIRPK</sub> |                                                                                    |                           | -700<br>±200 |                  | mV    |

# Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A = +25^{\circ}$ C and  $T_A = +105^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested. General Purpose I/O are only tested at  $T_A = +105^{\circ}$ C.)

| PARAMETER                                                                 | SYMBOL                | CONDITIONS                                                                                    | MIN                          | TYP     | MAX                         | UNITS |

|---------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------|------------------------------|---------|-----------------------------|-------|

| CLOCKS                                                                    |                       |                                                                                               |                              |         |                             |       |

| System Clock Frequency                                                    | fsys_clk              |                                                                                               | 0.256                        |         | 120,000                     | kHz   |

| System Clock Period                                                       | tsys_clk              |                                                                                               | 1/                           | fsys_cl | .K                          | ns    |

| High-Speed Oscillator<br>Frequency                                        | f <sub>HSCLK</sub>    | Measured at +25°C, 120MHz                                                                     |                              | 120 ±1  |                             | MHz   |

| Low-Power Oscillator<br>Frequency                                         | flpclk                |                                                                                               |                              | 40      |                             | MHz   |

| 7MHz Oscillator<br>Frequency                                              | f7MCLK                |                                                                                               |                              | 7.3728  |                             | MHz   |

| Nano-Ring Oscillator<br>Frequency                                         | f <sub>NANO</sub>     |                                                                                               |                              | 8       |                             | KHz   |

| RTC Input Frequency                                                       | f <sub>32KIN</sub>    | 32kHz watch crystal, C <sub>L</sub> = 6pF, ESR < 70k $\Omega$                                 |                              | 32.768  |                             | kHz   |

| RTC Operating Current                                                     | IRTC_ACTSLP           | Sleep or Active mode                                                                          |                              | 0.39    |                             | μA    |

| RTC Power Up Time                                                         | <sup>t</sup> RTC_ON   |                                                                                               |                              | 250     |                             | ms    |

| GENERAL-PURPOSE I/O                                                       |                       |                                                                                               |                              |         |                             |       |

| Input Low Voltage for All<br>GPIO                                         | VIL_VDDIO             | V <sub>DDIO</sub> selected as I/O supply                                                      |                              |         | 0.3 ×<br>V <sub>DDIO</sub>  | V     |

| Input Low Voltage for All<br>GPIO except P1.[21:18],<br>P1.[16:11], P3.0  | VIL_VDDIOH            | V <sub>DDIOH</sub> selected as I/O supply                                                     |                              |         | 0.3 ×<br>V <sub>DDIOH</sub> | V     |

| Input Low Voltage for<br>RSTN                                             | V <sub>IL_RSTN</sub>  |                                                                                               |                              |         | 0.3 ×<br>V <sub>DDIO</sub>  | V     |

| Input High Voltage for All GPIO                                           | VIH_VDDIO             | V <sub>DDIO</sub> selected as I/O supply                                                      | 0.75 ×<br>V <sub>DDIO</sub>  |         |                             | V     |

| Input High Voltage for All<br>GPIO except P1.[21:18],<br>P1.[16:11], P3.0 | VIH_VDDIOH            | V <sub>DDIOH</sub> selected as I/O supply                                                     | 0.75 ×<br>V <sub>DDIOH</sub> |         |                             | V     |

| Input High Voltage for RSTN                                               | V <sub>IH_RSTN</sub>  |                                                                                               | 0.75 x<br>V <sub>DDIO</sub>  |         |                             | V     |

|                                                                           |                       | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V, DS[1:0] = 00, I <sub>OL</sub> = 1mA    |                              | 0.2     | 0.4                         |       |

| Output Low Voltage for All                                                |                       | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V, DS[1:0] = 01, I <sub>OL</sub> = 2mA    |                              | 0.2     | 0.4                         | V     |

| GPIO                                                                      | V <sub>OL_VDDIO</sub> | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V,<br>DS[1:0] = 10, I <sub>OL</sub> = 4mA |                              | 0.2     | 0.4                         | v     |

|                                                                           |                       | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V,<br>DS[1:0] = 11, I <sub>OL</sub> = 8mA |                              | 0.2     | 0.4                         |       |

# Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A = +25^{\circ}$ C and  $T_A = +105^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested. General-purpose I/O are only tested at  $T_A = +105^{\circ}$ C.)

| PARAMETER                                          | SYMBOL                | CONDITIONS                                                                                                                    | MIN                         | TYP | MAX   | UNITS |  |

|----------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|-------|-------|--|

|                                                    |                       | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub> = 1.71V,<br>DS[1:0] = 00, I <sub>OL</sub> = 1mA                 |                             | 0.2 | 0.4   |       |  |

| Output Low Voltage for All GPIO except P1.[21:18], |                       | $V_{DDIOH}$ selected as I/O supply, $V_{DDIOH}$ = 1.71V, DS[1:0] = 01, I <sub>OL</sub> = 2mA                                  |                             | 0.2 | 0.4   | V     |  |

| P1.[16:11], P3.0                                   | VOL_VDDIOH            | $V_{DDIOH}$ selected as I/O supply, $V_{DDIOH}$ = 1.71V, DS[1:0] = 10, I <sub>OL</sub> = 4mA                                  |                             | 0.2 | 0.4   | v     |  |

|                                                    |                       | $V_{DDIOH}$ selected as I/O supply, $V_{DDIOH}$ = 1.71V, DS[1:0] = 11, I <sub>OL</sub> = 8mA                                  |                             | 0.2 | 0.4   |       |  |

| Combined I <sub>OL</sub> , All GPIO                | I <sub>OL_TOTAL</sub> |                                                                                                                               |                             |     | 48    | mA    |  |

|                                                    |                       | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V,<br>DS[1:0] = 00, I <sub>OL</sub> = -1mA                                | V <sub>DDIO</sub><br>- 0.4  |     |       |       |  |

| Output High Voltage for                            |                       | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V,<br>DS[1:0] = 01, I <sub>OL</sub> = -2mA                                | V <sub>DDIO</sub><br>- 0.4  |     |       | V     |  |

| All GPIO                                           | VOH_VDDIO             | $V_{DDIO}$ selected as I/O supply, $V_{DDIO}$ = 1.71V,<br>DS[1:0] = 10, I <sub>OL</sub> = -4mA                                | V <sub>DDIO</sub><br>- 0.4  |     |       | v     |  |

|                                                    |                       | V <sub>DDIO</sub> selected as I/O supply, V <sub>DDIO</sub> = 1.71V,<br>DS[1:0] = 00, I <sub>OL</sub> = -8mA                  | V <sub>DDIO</sub><br>- 0.4  |     |       |       |  |

|                                                    | Vон_vddioн            | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub> = 1.71V,<br>DS[1:0] = 00, I <sub>OL</sub> = -1mA                | V <sub>DDIOH</sub><br>- 0.4 |     |       | - V   |  |

| Output High Voltage for All                        |                       | $V_{DDIOH}$ selected as I/O supply, $V_{DDIOH}$ = 1.71V, DS[1:0] = 01, I <sub>OL</sub> = -2mA                                 | V <sub>DDIOH</sub><br>- 0.4 |     |       |       |  |

| GPIO except P1.[21:18],<br>P1.[16:11], P3.0        |                       | $V_{DDIOH}$ selected as I/O supply, $V_{DDIOH}$ = 1.71V, DS[1:0] = 10, I <sub>OL</sub> = -8mA                                 | V <sub>DDIOH</sub><br>- 0.4 |     |       | v     |  |

|                                                    |                       | $V_{DDIOH}$ selected as I/O supply, $V_{DDIOH}$ = 1.71V, DS[1:0] = 11, I <sub>OL</sub> = -8mA                                 | V <sub>DDIOH</sub><br>- 0.4 |     |       |       |  |

| Combined I <sub>OH</sub> , All GPIO                | IOH_TOTAL             |                                                                                                                               |                             |     | -48   | mA    |  |

| Input Hysteresis (Schmitt)                         | VIHYS                 |                                                                                                                               |                             | 300 |       | mV    |  |

| Input Leakage Current<br>Low                       | IIL                   | $V_{DDIO}$ = 1.89V, $V_{DDIOH}$ = 3.6V, $V_{DDIOH}$ selected<br>as I/O supply, $V_{IN}$ = 0V, internal pullup disabled        | -1000                       |     | +1000 | nA    |  |

|                                                    | ЦН                    | $V_{DDIO}$ = 1.89V, $V_{DDIOH}$ = 3.6V, $V_{DDIOH}$ selected<br>as I/O supply, $V_{IN}$ = 3.6V, internal pulldown<br>disabled | -1000                       |     | +1000 | nA    |  |

| Input Leakage Current<br>High                      | I <sub>OFF</sub>      | $V_{DDIO}$ = 0V, $V_{DDIOH}$ = 0V, $V_{DDIO}$ selected as I/O supply, $V_{IN}$ < 1.89V                                        | -1                          |     | +1    |       |  |

|                                                    | I <sub>IH3V</sub>     | $V_{DDIO} = V_{DDIOH} = 1.71V$ , $V_{DDIO}$ selected as I/O supply, $V_{IN} = 3.6V$                                           | -2                          |     | +2    | μA    |  |

| Input Pullup Resistor<br>TMS, TCK, TDI             | R <sub>PU_T</sub>     |                                                                                                                               |                             | 25  |       | kΩ    |  |

| Input Pullup Resistor<br>RSTN                      | R <sub>PU_R</sub>     |                                                                                                                               |                             | 1   |       | MΩ    |  |

# Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

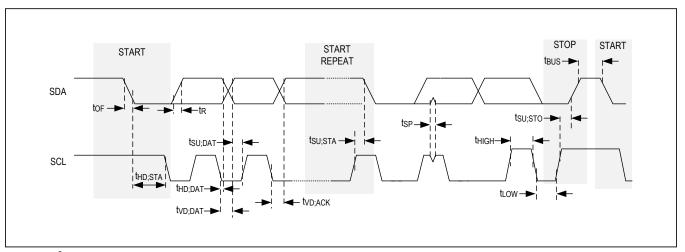

### Electrical Characteristics—I<sup>2</sup>C (continued)

(Timing specifications are guaranteed by design and not production tested.)

| PARAMETER                                        | SYMBOL              | CONDITIONS                | MIN  | TYP | MAX  | UNITS |

|--------------------------------------------------|---------------------|---------------------------|------|-----|------|-------|

| FAST MODE PLUS                                   |                     |                           | ·    |     |      |       |

| Output Fall Time                                 | t <sub>OF</sub>     | From VIH(MIN) to VIL(MAX) |      | 80  |      | ns    |

| Pulse Width Suppressed by<br>Input Filter        | t <sub>SP</sub>     |                           |      | 75  |      | ns    |

| SCL Clock Frequency                              | fscl                |                           | 0    |     | 1000 | kHz   |

| Low Period SCL Clock                             | tLOW                |                           | 0.5  |     |      | μs    |

| High Time SCL clock                              | t <sub>HIGH</sub>   |                           | 0.26 |     |      | μs    |

| Setup Time for Repeated<br>Start Condition       | t <sub>SU;STA</sub> |                           | 0.26 |     |      | μs    |

| Hold Time for Repeated Start Condition           | <sup>t</sup> HD;STA |                           | 0.26 |     |      | μs    |

| Data Setup Time                                  | <sup>t</sup> SU;DAT |                           |      | 50  |      | ns    |

| Data Hold Time                                   | t <sub>HD;DAT</sub> |                           |      | 10  |      | ns    |

| Rise Time for SDA and SCL                        | t <sub>R</sub>      |                           |      | 50  |      | ns    |

| Fall Time for SDA and SCL                        | t <sub>F</sub>      |                           |      | 30  |      | ns    |

| Setup Time for a Stop<br>Condition               | tsu;sto             |                           | 0.26 |     |      | μs    |

| Bus Free Time Between a Stop and Start Condition | t <sub>BUS</sub>    |                           | 0.5  |     |      | μs    |

| Data Valid Time                                  | t <sub>VD;DAT</sub> |                           | 0.45 |     |      | μs    |

| Data Valid Acknowledge Time                      | t <sub>VD;ACK</sub> |                           | 0.45 |     |      | μs    |

Figure 3. I<sup>2</sup>C Timing Diagram

# Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

### **Electrical Characteristics—I<sup>2</sup>C Slave**

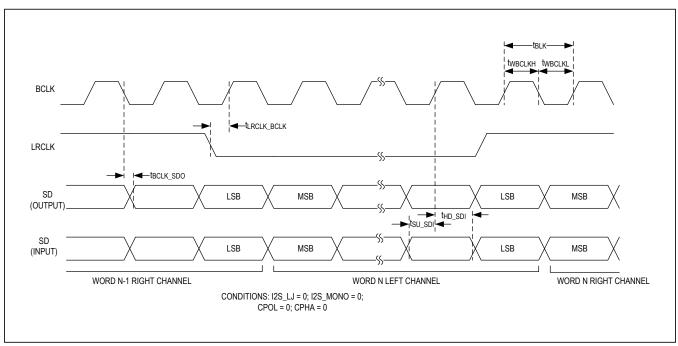

| PARAMETER                                | SYMBOL                  | CONDITIONS            | MIN | TYP | MAX   | UNITS               |

|------------------------------------------|-------------------------|-----------------------|-----|-----|-------|---------------------|

| Bit Clock Frequency                      | f <sub>BCLK</sub>       | 96kHz LRCLK frequency |     |     | 3.072 | MHz                 |

| BCLK High Time                           | twbclkh                 |                       |     | 0.5 |       | 1/f <sub>BCLK</sub> |

| BCLK Low Time                            |                         |                       |     | 0.5 |       | 1/f <sub>BCLK</sub> |

| LRCLK Setup Time                         | <sup>t</sup> LRCLK_BLCK |                       |     | 25  |       | ns                  |

| Delay Time, BCLK to SD<br>(Output) Valid | <sup>t</sup> BCLK_SDO   |                       |     | 12  |       | ns                  |

| Setup Time for SD<br>(Input)             | tsu_sdi                 |                       |     | 6   |       | ns                  |

| Hold Time SD (Input)                     | t <sub>HD_SDI</sub>     |                       |     | 3   |       | ns                  |

(Timing specifications are guaranteed by design and not production tested,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ .)

Figure 4. I<sup>2</sup>S Timing Diagram

# Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

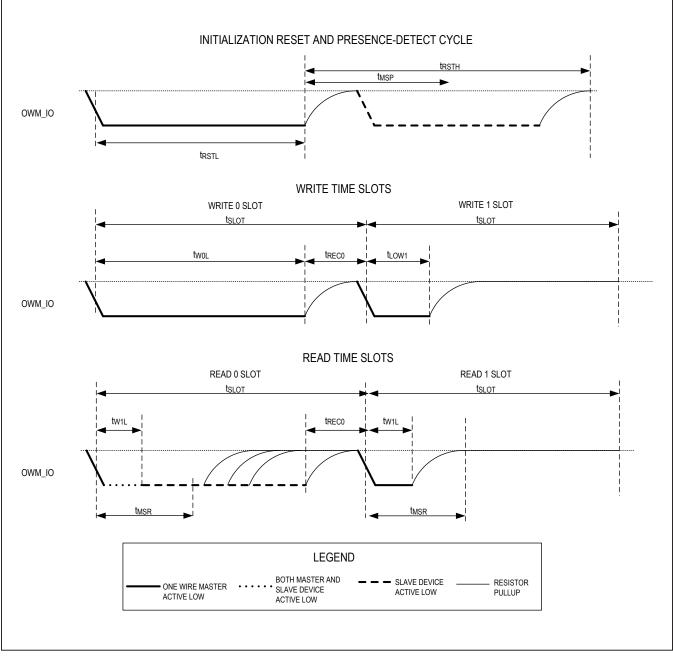

Figure 7. One-Wire Master Data Timing Diagram

# Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

### **Pin Description**

| PIN                                           |                              |                                                       | FUNCTION           |                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-----------------------------------------------|------------------------------|-------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 140 WLP                                       | 96 WLP                       | 144 TQFP                                              | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                                                               |  |  |

| POWER                                         |                              |                                                       |                    |                                                                                                                                                                                                                                                                                                                                                        |  |  |

| H1, H4,<br>D12                                | G1, C8                       | 5, 14, 88                                             | V <sub>CORE</sub>  | Core Supply Voltage. This pin must be bypassed to $V_{SS}$ with a $1.0\mu F$ capacitor as close as possible to the package.                                                                                                                                                                                                                            |  |  |

| H11                                           | G10                          | 99                                                    | V <sub>DDA</sub>   | 1.8V Analog Supply Voltage. This pin must be bypassed to $V_{\mbox{SSA}}$ with 1.0 $\mu\mbox{F}$ and 0.01 $\mu\mbox{F}$ capacitors as close as possible to the package.                                                                                                                                                                                |  |  |

| B11                                           | B9                           | 76                                                    | V <sub>DDB</sub>   | USB Transceiver Supply Voltage. This pin must be bypassed to $V_{SS}$ with a 1.0µF capacitor as close as possible to the package.                                                                                                                                                                                                                      |  |  |

| A7                                            | A5                           | 21                                                    |                    | GPIO Supply Voltage. This pin must be bypassed to $V_{SS}$ with 1.0µF and 0.01µF capacitors as close as possible to the package.                                                                                                                                                                                                                       |  |  |

| E4, F1                                        | B1, K5                       | 33, 55                                                | V <sub>DDIO</sub>  | GPIO Supply Voltage. This pin must be bypassed to $V_{SS}$ with a $1.0\mu F$ and a $0.01\mu F$ capacitor as close as possible to the package.                                                                                                                                                                                                          |  |  |

| M7                                            |                              | 126                                                   |                    | GPIO Supply Voltage. This pin must be bypassed to $V_{SS}$ with 1.0µF and 0.01µF capacitors as close as possible to the package.                                                                                                                                                                                                                       |  |  |

| A6                                            | B5                           | 9                                                     |                    | GPIO Supply Voltage, High. $V_{DDIOH} \ge V_{DDIO}$ . This pin must be bypassed to $V_{SS}$ with 1.0µF and 0.01µF capacitorx as close as possible to the package.                                                                                                                                                                                      |  |  |

| G1, G4,<br>M6                                 | F1, K4                       | 18, 54, 128                                           | V <sub>DDIOH</sub> | GPIO Supply Voltage, High. $V_{DDIOH} \ge V_{DDIO}$ . This pin must be bypassed to $V_{SS}$ with 1.0µF and 0.01µF capacitors as close as possible to the package.                                                                                                                                                                                      |  |  |

| M11                                           | H8                           | 111                                                   | V <sub>RTC</sub>   | RTC Supply Voltage. This pin must be bypassed to $V_{SS}$ with a $1.0\mu F$ capacitor as close as possible to the package.                                                                                                                                                                                                                             |  |  |

| A4, A8,<br>C11, D1,<br>D11, F4,<br>J1, M4, M9 | B6, C1,<br>C9, D8,<br>K7, J2 | 11, 27, 29,<br>47, 60, 80,<br>81, 85, 89,<br>119, 136 | V <sub>SS</sub>    | Digital Ground                                                                                                                                                                                                                                                                                                                                         |  |  |

| H12                                           | G9                           | 98                                                    | V <sub>SSA</sub>   | Analog Ground                                                                                                                                                                                                                                                                                                                                          |  |  |

| RESET                                         |                              |                                                       |                    |                                                                                                                                                                                                                                                                                                                                                        |  |  |

| L10                                           | K8                           | 114                                                   | RSTN               | Hardware Power Reset (Active-Low) Input. The device remains in reset while this pin is in its active state. When the pin transitions to its inactive state, the device performs a POR reset (resetting all logic on all supplies except for real-time clock circuitry) and begins execution. This pin has an internal pullup to the $V_{DDIO}$ supply. |  |  |

| CLOCK                                         |                              |                                                       |                    |                                                                                                                                                                                                                                                                                                                                                        |  |  |

| L12                                           | J10                          | 107                                                   | 32KIN              | 32kHz Crystal Oscillator Input. Connect a 32kHz crystal between 32KIN and 32KOUT for RTC operation. Optionally, an external clock source can be driven on 32KIN if the 32KOUT pin is left unconnected.                                                                                                                                                 |  |  |

| K12                                           | H10                          | 106                                                   | 32KOUT             | 32kHz Crystal Oscillator Output                                                                                                                                                                                                                                                                                                                        |  |  |

| GPIO AND A                                    | LTERNATE                     | FUNCTIONS                                             |                    |                                                                                                                                                                                                                                                                                                                                                        |  |  |

| F5                                            | _                            | _                                                     | P0.0               | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.                                                                                                                                                          |  |  |

| L2                                            | _                            | 2                                                     | P0.1               | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.                                                                                                                                                          |  |  |

# Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

### **Pin Description (continued)**

|         | PIN    |          |       |                                                                                                                                                                                               |  |  |  |

|---------|--------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 140 WLP | 96 WLP | 144 TQFP | NAME  | FUNCTION                                                                                                                                                                                      |  |  |  |

| К3      | _      | 3        | P0.2  | General-Purpose I/O, Port 0. Most port pins have multiple special functions. See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.    |  |  |  |

| L1      | _      | 4        | P0.3  | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| J3      | _      | 6        | P0.4  | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| K2      | _      | 7        | P0.5  | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| K1      | _      | 8        | P0.6  | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| H3      | _      | 12       | P0.7  | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| H2      | _      | 13       | P0.8  | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| G3      | _      | 15       | P0.9  | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| G2      | _      | 17       | P0.10 | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| F2      | E2     | 22       | P0.11 | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| F3      | _      | 23       | P0.12 | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| E2      | E1     | 25       | P0.13 | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| E3      | D1     | 26       | P0.14 | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , Table 4 and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.        |  |  |  |

| D2      | G4     | 28       | P0.15 | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| C1      | F3     | 30       | P0.16 | General-Purpose I/O, Port 0. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

# Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

### **Pin Description (continued)**

|         | PIN    |          |       | E                                                                                                                                                                                                                                    |  |  |

|---------|--------|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 140 WLP | 96 WLP | 144 TQFP | NAME  | FUNCTION                                                                                                                                                                                                                             |  |  |

| C8      | C5     | 58       | P1.15 | General-Purpose I/O, Port 1. Most port pins have multiple special functions. This pin is connected to $V_{DDIO}$ only. See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |

| B8      | D5     | 59       | P1.16 | General-Purpose I/O, Port 1. Most port pins have multiple special functions. This pin is connected to $V_{DDIO}$ only. See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |

| E9      | _      | 69       | P1.17 | General-Purpose I/O, Port 1. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.                                        |  |  |

| B9      | В7     | 63       | P1.18 | General-Purpose I/O, Port 1. Most port pins have multiple special functions. This pin is connected to $V_{DDIO}$ only. See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |

| C9      | C6     | 62       | P1.19 | General-Purpose I/O, Port 1. Most port pins have multiple special functions. This pin is connected to $V_{DDIO}$ only. See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |

| C10     | E6     | 66       | P1.20 | General-Purpose I/O, Port 1. Most port pins have multiple special functions. This pin is connected to $V_{DDIO}$ only. See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |

| B10     | B8     | 67       | P1.21 | General-Purpose I/O, Port 1. Most port pins have multiple special functions. This pin is connected to $V_{DDIO}$ only. See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |

| _       | _      | 75       | P1.22 | General-Purpose I/O, Port 1. Most port pins have multiple special functions. See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.                                           |  |  |

| F9      | C7     | 70       | P1.23 | General-Purpose I/O, Port 1. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.                                        |  |  |

| H9      | E7     | 92       | P1.24 | General-Purpose I/O, Port 1. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.                                        |  |  |

| G9      | D6     | 72       | P1.25 | General-Purpose I/O, Port 1. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.                                        |  |  |

| M10     | J8     | 115      | P1.26 | General-Purpose I/O, Port 1. Most port pins have multiple special functions. See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.                                           |  |  |

| 19      | H7     | 116      | P1.27 | General-Purpose I/O, Port 1. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.                                        |  |  |

| K9      | J7     | 117      | P1.28 | General-Purpose I/O, Port 1. Most port pins have multiple special functions. See Table 3, Table 4 and TTable 5 GPIO and Alternate Function Matrix tables for details.                                                                |  |  |

| L9      | H6     | 118      | P1.29 | General-Purpose I/O, Port 1. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.                                        |  |  |

# Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

### **Pin Description (continued)**

|         | PIN    |          |       |                                                                                                                                                                                               |  |  |  |

|---------|--------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 140 WLP | 96 WLP | 144 TQFP | NAME  | FUNCTION                                                                                                                                                                                      |  |  |  |

| J5      | G3     | 140      | P2.13 | General-Purpose I/O, Port 2. Most port pins have multiple special functions See Table 3, Table 4 and Table 5 GPIO and Alternate Function Matrix tables for details.                           |  |  |  |

| K4      | J1     | 143      | P2.14 | General-Purpose I/O, Port 2. Most port pins have multiple special functions. See Table 3, Table 4 and Table 5 GPIO and Alternate Function Matrix tables for details.                          |  |  |  |

| H5      | H1     | 144      | P2.15 | General-Purpose I/O, Port 2. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| J4      | G2     | 1        | P2.16 | General-Purpose I/O, Port 2. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| G7      | F2     | 19       | P2.17 | General-Purpose I/O, Port 2. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and Table 5 GPIO and Alternate Function Matrix tables for details.        |  |  |  |

| F7      | H5     | 20       | P2.18 | General-Purpose I/O, Port 2. Most port pins have multiple special functions. See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.    |  |  |  |

| D7      | _      | _        | P2.19 | General-Purpose I/O, Port 2. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and Table 5 GPIO and Alternate Function Matrix tables for details.        |  |  |  |

| E7      | _      | _        | P2.20 | General-Purpose I/O, Port 2. Most port pins have multiple special functions. See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.    |  |  |  |

| E8      | _      | _        | P2.21 | General-Purpose I/O, Port 2. Most port pins have multiple special functions. See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.    |  |  |  |

| D9      | _      | _        | P2.22 | General-Purpose I/O, Port 2. Most port pins have multiple special functions. See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.    |  |  |  |

| D8      | A6     | 57       | P2.23 | General-Purpose I/O, Port 2. Most port pins have multiple special functions. See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details.    |  |  |  |

| H7      | _      | _        | P2.24 | General-Purpose I/O, Port 2. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| K6      | _      | 133      | P2.25 | General-Purpose I/O, Port 2. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| J6      | _      | 135      | P2.26 | General-Purpose I/O, Port 2. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

| H6      | _      | _        | P2.27 | General-Purpose I/O, Port 2. Most port pins have multiple special functions.<br>See <u>Table 3</u> , <u>Table 4</u> and <u>Table 5</u> GPIO and Alternate Function Matrix tables for details. |  |  |  |

#### Memory

#### **Internal Flash Memory**

3MB of internal flash memory provides nonvolatile storage of program and data memory.

Flash can be expanded through the SPIXF flash serial interface backed by 16KB of cache. The SPIXF flash interface can address an additional 128MB.

#### Internal SRAM

The internal 1MB SRAM provides low-power retention of application information in all power modes except shutdown. The SRAM can be divided into granular banks that create a flexible SRAM retention architecture. This data retention feature is optional and configurable. This granularity allows the application to minimize its power consumption by only retaining the most essential data.

SRAM can be expanded through the SPIXR SRAM serial interface backed by 16KB of cache. The SPIXR SRAM interface can address an additional 512MB.

#### **Secure Digital Interface**

The secure digital interface (SDI) provides high-speed, high-density data storage capability for media files and large long-term data logs. This interface supports eMMC, SD, SDHC, and SDXC memory devices up to 4GB at transfer rates up to 30MB/s. The 7-pin interface (4 data, 1 clock, 1 command, 1 write-protect) supports the following specifications:

- SD Host Controller Standard Specification Version 3.00

- SDIO Card Specification Version 3.0

- SD Memory Card Specification Version 3.01

- SD Memory Card Security Specification Version 1.01

- MMC Specification Version 4.51

#### Spansion HyperBus/Xccela Bus

The Spansion HyperBus/Xccela bus interface provides access to external Cypress Spansion HyperBus and Xccela bus memory products both SRAM and/or flash. This interface provides a means of high-speed execution from external SRAM or flash allowing system expansion when internal memory resources are insufficient. Up to 8MB SRAM or 512MB flash at a speed of up to 60MHz or 120MBps is supported. It is a high-speed low-pin count interface that is memory-mapped into the CPU memory space making access to this external memory as easy as

### Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

accessing on-chip RAM. Data is transferred over a highspeed, 8-bit bus. Slave memory devices are selected with two chip selects. HyperBus transfers are clocked using a differential clock while Xccela bus transfers use a singleended clock. This interface supports 1.8V operation only.

Features of the HyperBus/Xccela bus interface include:

- Master/slave system

- 120MBps maximum data transfer rate

- Double data rate (DDR): two data transfers per clock cycle

- Transparent bus operation to the processor

- 16KB write-through cache

- Two chip selects for two memory ports

- Each port supports memories up to 512MB

- Addresses two external memories, one at a time

- Interfaces to HyperFlash, HyperRAM, and Xccela PSRAM

- Zero wait state burst mode operation

- Low-power Half Sleep mode

- Puts the external memory device into low power mode while retaining memory contents

- Configurable timing parameters

#### **Clocking Scheme**

The high-frequency oscillator operates at a maximum frequency of 120MHz.

Optionally, 4 other oscillators can be selected depending upon power needs:

- 40MHz low-power oscillator

- 8kHz nano-ring oscillator

- 32.768kHz oscillator (external crystal required)

- 7.3728MHz oscillator

This clock is the primary clock source for the digital logic and peripherals. Select the 7.3728MHz internal oscillator to optimize active power consumption. Using the 7.3727MHz oscillator allows UART communications to meet a  $\pm 2\%$  baud rate tolerance.

Wakeup is possible from either the 7.3728MHz internal oscillator or the high-frequency oscillator. The device exits power-on reset using the the 40MHz oscillator.

An external 32.768kHz timebase is required when using the RTC.

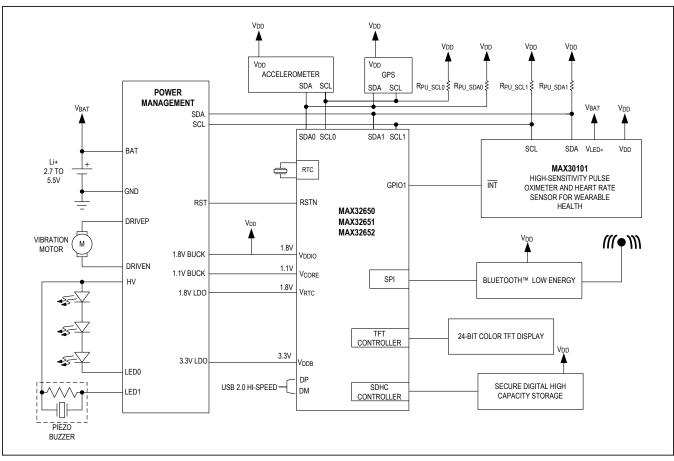

#### **USB** Controller

The integrated USB device controller is compliant with the Hi-Speed (480Mbps) USB 2.0 specification. The integrated USB physical interface (PHY) reduces board space and system cost. An integrated voltage regulator enables smart switching between the main supply and  $V_{DDB}$  when connected to a USB host controller.

- Supports DMA for the endpoint buffers. A total of 12 endpoint buffers are supported with configurable selection of IN or OUT in addition to endpoint 0.

- · Isochronous, bulk, interrupt, and control transfers

- · Automatic packet splitting and combining

- FIFOs up to 4096 bytes deep

- Double packet buffering

- USB 2.0 test mode support

#### I<sup>2</sup>C Interface

The I<sup>2</sup>C interface is a bidirectional, two-wire serial bus that provides a medium-speed communications network. It can operate as a one-to-one, one-to-many or many-to-many communications medium. Two I<sup>2</sup>C master/slave interface to a wide variety of I<sup>2</sup>C-compatible peripherals. These engines support standard mode, fast mode, and fast mode plus I<sup>2</sup>C speeds. It provides the following features:

- Master or slave mode operation

- Supports standard 7-bit addressing or 10-bit addressing

- RESTART condition

- Interactive Receive mode

- Tx FIFO preloading

- Support for clock stretching to allow slower slave devices to operate on higher speed busses

- Multiple transfer rates

- Standard mode: 100kbps

- Fast mode: 400kbps

- Fast mode plus: 1000kbps

- Internal filter to reject noise spikes

- Receiver FIFO depth of 8 bytes

- Transmitter FIFO depth of 8 bytes

The MAX32650–MAX32652 provide two instances of the I<sup>2</sup>C peripheral (I2C0 and I2C1).

### Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

#### UART

The universal asynchronous receiver-transmitter (UART) interface supports full-duplex asynchronous communication with optional hardware flow control (HFC) modes to prevent data overruns. If HFC mode is enabled on a given port, the system uses two extra pins to implement the industry standard request to send (RTS) and clear to send (CTS) flow control signaling. Each UART is individually programmable.

- 2-wire interface or 4-wire interface with flow control

- 32-byte send/receive FIFO

- Full-duplex operation for asynchronous data transfers

- Interrupts available for frame error, parity error, CTS, Rx FIFO overrun and FIFO full/partially full conditions

- Automatic parity and frame error detection

- Independent baud-rate generator

- Programmable 9th bit parity support

- Multidrop support

- Start/stop bit support

- Hardware flow control using RTS/CTS

- Baud rate generation with ±2% optionally utilizing the 7.3727MHz relaxation oscillator

- Maximum baud rate 4000kB

- Two DMA channels can be connected (read and write FIFOs)

- Programmable word size (5 bits to 8 bits)

The MAX32650–MAX32652 provide three instances of the UART peripheral (UART0, UART1, and UART2) according to the specifications in Table 2.

#### Serial Peripheral Interface Execute in Place (SPIX) Master

There are two SPI execute-in-place master interfaces. One for SRAM (SPIXR) and one for flash (SPIXF) with dedicated slave selects. This feature allows the CPU to transparently execute instructions stored in an external SPI memory device. Instructions fetched through the SPI master are cached like instructions fetched from internal program memory. The SPI SRAM master provides writeback capability. These two SPI execute in place master interfaces can also be used to access large amounts of external static data that would otherwise reside in internal data memory.

# Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

| INSTANCE |          | MAXIMUM BAUD |        |           |

|----------|----------|--------------|--------|-----------|

| INSTANCE | 144 TQFP | 140 WLP      | 96 WLP | RATE (KB) |

| UART0    | YES      | YES          | NO     | 4000      |

| UART1    | YES      | YES          | YES    | 4000      |

| UART2    | YES      | YES          | NO     | 4000      |

### Table 2. UART Configuration Options

#### **1-Wire Master**

Maxim's 1-wire bus consists of a single line to provide both power and data communications and a ground return. The bus supports a serial, multidrop communication protocol between a master and one or more slave devices with the minimum amount of interconnection.

Maxim's 1-wire bus consists of one signal that carries data and also supplies power to the slave devices, and a ground return. The bus master communicates serially with one or more slave devices through the bidirectional, multidrop 1-Wire bus. The single contact serial interface is ideal for communication networks requiring minimal interconnection.

The provided 1-Wire master supports the following features:

- Single contact for control and operation

- Unique factory identifier for any 1-Wire device

- Multiple device capability on a single line

The MAX32650–MAX32652 1-Wire master supports both the standard (15.6kbps) and overdrive (110kbps) speeds.

#### 24-Bit Color TFT Controller

The 24-bit color TFT controller is controlled by the CPU through the APB and fed graphic data through the AHB. The controller supports the following display types:

- Active matrix TFT panels with up to 24-bit bus interface

- Single/dual-panel monochrome STN panels (4-bit and 8-bit bus interface)

- Single/dual-panel color STN panels, 8-bit bus interface

- TFT panels up to 24bpp, direct 8:8:8 RGB

- Color STN panels up to 16bpp, direct 5:5:5 with one bit not being used

- Mono STN panels up to 4bpp, pelletized, 16 gray scales selected from 16

The controller can be programmed to operate a wide range of panel resolutions (including, but not limited to the following settings):

- 320 x 200, 320 x 240,

- 640 x 200, 640 x 240, 640 x 480

- 800 x 600

- 1024 x 768

- 2048 x 2048

- 4096 x 4096

#### Debug and Development Interface (SWD/JTAG)

Special versions of the device are available with a serial wire debug or JTAG interface that is used only during application development and debugging. The interface is used for code loading, ICE debug activities, and control of boundary scan activities. Devices in mass production must have the debugging/development interface disabled.

The <u>Ordering Information</u> contains unique part numbers for devices with the debugging/development interface enabled or disabled.

#### Trust Protection Unit (MAX32651 Only)

#### **True Random Number Generator**

Random numbers are a vital part of a secure application, providing random numbers that can be used for cryptographic seeds or strong encryption keys to ensure data privacy.

Software can use random numbers to trigger asynchronous events that result in nondeterministic behavior. This is helpful in thwarting replay attacks or key search approaches. An effective true random number generator (TRNG) must be continuously updated by a high-entropy source.

The provided TRNG is continuously driven by a physicallyunpredictable entropy source. It generates a 128-bit true random number in 128 system clock cycles.

The TRNG can support the system-level validation of many security standards such as FIPS 140-2, PCI-PED, and Common Criteria. Contact Maxim for details of compliance with specific standards.

#### MAA

The provided high-speed, hardware-based modulo arithmetic accelerator (MAA) performs mathematical computations that support strong cryptographic algorithms. These include:

- 2048-bit DSA

- 4096-bit RSA

- Elliptic curve public key infrastructure

#### AES

The dedicated hardware-based AES engine supports the following algorithms:

- AES-128

- AES-192

- AES-256

The AES keys are automatically generated by the engine and stored in dedicated flash to protect against tampering. Key generation and storage is transparent to the user.

#### SHA-256

SHA-256 is a cryptographic hash function part of the SHA-2 family of algorithms. It authenticates user data and verifies its integrity. It is used for digital signatures.

The device provides a hardware SHA-256 engine for fast computation of 256-bit digests.

#### **Memory Decryption Integrity Unit**

The external SPI flash can optionally be encrypted for additional security. Data can be transparently encrypted when it is loaded and decrypted on-the-fly. Encryption keys are stored in the always-on domain and preserved as long as  $V_{\text{RTC}}$  is present.

#### Secure Bootloader

The secure bootloader provides a secure, authenticated communication channel with a system host. The secure communication protocol (SCP) allows the programming of internal and external memory.

The secure bootloader provides the following features:

- Life cycle management

- Authentications using ECDSA P-256, with 256-bit ECC key pairs and SHA-256 secure hash function

- Preprogrammed Maxim manufacturer root key (MRK)

- Programmable customer root key (CRK)

- Support for 2048- or 4096-bit RSA digital signature

### Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

#### **Additional Documentation and Technical Support**

Designers must have the following documents to use all the features of this device:

- This data sheet, which contains electrical/timing specifications, package information, and pin descriptions

- The corresponding revision-specific errata sheet

- The corresponding user guide, which contains detailed information and programming guidelines for core features and peripherals

### **Applications Information**

#### **GPIO and Alternate Function Matrix, 140 WLP**

# Table 3. GPIO and Alternate FunctionMatrix, 140 WLP

| GPIO  | ALTERNATE<br>FUNCTION 1 | ALTERNATE<br>FUNCTION 2 |

|-------|-------------------------|-------------------------|

| P0.0  | PT3                     | SPIXF_SDIO2**           |

| P0.1  | SPIXR_SDIO0**           | —                       |

| P0.2  | SPIXR_SDIO2**           | —                       |

| P0.3  | SPIXR_SCK**             | —                       |

| P0.4  | SPIXR_SDIO3**           | —                       |

| P0.5  | SPIXR_SDIO1**           | —                       |

| P0.6  | SPIXR_SS0**             | —                       |

| P0.7  | SPIXF_SS0**             | —                       |

| P0.8  | SPIXF_SCK**             | —                       |

| P0.9  | SPIXF_SDIO1**           | —                       |

| P0.10 | SPIXF_SDIO0**           | —                       |

| P0.11 | SPIXF_SDIO2**           | —                       |

| P0.12 | SPIXF_SDIO3**           | —                       |

| P0.13 | SPI3_SS1                | CLCD_G0                 |

| P0.14 | SPI3_SS2                | CLCD_G1                 |

| P0.15 | SPI3_SDIO3              | CLCD_G2                 |

| P0.16 | SPI3_SCK                | CLCD_G3                 |

| P0.17 | SPI3_SDIO2              | CLCD_G4                 |

| P0.18 | SPI3_SS3                | CLCD_G5                 |

| P0.19 | SPI3_SS0                | CLCD_G6                 |

| P0.20 | SPI3_SDIO1              | CLCD_G7                 |

| P0.21 | SPI3_SDIO0              | —                       |

| P0.22 | SPI0_SS0                | CLCD_VDEN               |

| P0.23 | PT15                    | CLCD_CLK                |

### Ultra-Low Power Arm Cortex-M4 with FPU-Based Microcontroller for Battery-Powered Applications

### Table 3. GPIO and Alternate Function Matrix, 140 WLP (continued)

| GPIO | ALTERNATE<br>FUNCTION 1 | ALTERNATE<br>FUNCTION 2 |

|------|-------------------------|-------------------------|