Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |  |

|----------------------------|-------------------------------------------------------------------------|--|

| Product Status             | Active                                                                  |  |

| Core Processor             | ARM® Cortex®-M0+                                                        |  |

| Core Size                  | 32-Bit Single-Core                                                      |  |

| Speed                      | 32MHz                                                                   |  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                            |  |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, LCD, POR, PWM, WDT                    |  |

| Number of I/O              | 37                                                                      |  |

| Program Memory Size        | 64KB (64K x 8)                                                          |  |

| Program Memory Type        | FLASH                                                                   |  |

| EEPROM Size                | 2K x 8                                                                  |  |

| RAM Size                   | 8K x 8                                                                  |  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |  |

| Data Converters            | A/D 10x12b; D/A 1x12b                                                   |  |

| Oscillator Type            | Internal                                                                |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |  |

| Mounting Type              | Surface Mount                                                           |  |

| Package / Case             | 48-LQFP                                                                 |  |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l053c8t6tr |  |

# **Contents**

| 1 | Intro | Introduction 9                                           |    |  |  |  |  |  |

|---|-------|----------------------------------------------------------|----|--|--|--|--|--|

| 2 | Desc  | ription                                                  | 0  |  |  |  |  |  |

|   | 2.1   | Device overview                                          | 11 |  |  |  |  |  |

|   | 2.2   | Ultra-low-power device continuum                         | 13 |  |  |  |  |  |

| 3 | Func  | tional overview1                                         | 4  |  |  |  |  |  |

|   | 3.1   | Low-power modes                                          | 14 |  |  |  |  |  |

|   | 3.2   | Interconnect matrix                                      | 19 |  |  |  |  |  |

|   | 3.3   | ARM® Cortex®-M0+ core with MPU                           | 20 |  |  |  |  |  |

|   | 3.4   | Reset and supply management                              | 21 |  |  |  |  |  |

|   |       | 3.4.1 Power supply schemes                               | 21 |  |  |  |  |  |

|   |       | 3.4.2 Power supply supervisor                            | 21 |  |  |  |  |  |

|   |       | 3.4.3 Voltage regulator                                  | 22 |  |  |  |  |  |

|   | 3.5   | Clock management                                         | 22 |  |  |  |  |  |

|   | 3.6   | Low-power real-time clock and backup registers           | 25 |  |  |  |  |  |

|   | 3.7   | General-purpose inputs/outputs (GPIOs)                   | 25 |  |  |  |  |  |

|   | 3.8   | Memories 2                                               | 26 |  |  |  |  |  |

|   | 3.9   | Boot modes 2                                             | 26 |  |  |  |  |  |

|   | 3.10  | Direct memory access (DMA)                               | 27 |  |  |  |  |  |

|   | 3.11  | Liquid crystal display (LCD) 2                           | 27 |  |  |  |  |  |

|   | 3.12  | Analog-to-digital converter (ADC)                        | 27 |  |  |  |  |  |

|   | 3.13  | Temperature sensor                                       | 28 |  |  |  |  |  |

|   |       | 3.13.1 Internal voltage reference (V <sub>REFINT</sub> ) | 28 |  |  |  |  |  |

|   |       | 3.13.2 V <sub>LCD</sub> voltage monitoring               | 29 |  |  |  |  |  |

|   | 3.14  | Digital-to-analog converter (DAC)                        | 29 |  |  |  |  |  |

|   | 3.15  | Ultra-low-power comparators and reference voltage        | 29 |  |  |  |  |  |

|   | 3.16  | System configuration controller 3                        | 30 |  |  |  |  |  |

|   | 3.17  | Touch sensing controller (TSC) 3                         | 30 |  |  |  |  |  |

|   | 3.18  | Timers and watchdogs                                     | 31 |  |  |  |  |  |

|   |       | 3.18.1 General-purpose timers (TIM2, TIM21 and TIM22)    | 31 |  |  |  |  |  |

|   |       | 3.18.2 Low-power Timer (LPTIM)                           | 32 |  |  |  |  |  |

| Table 46. | HSI48 oscillator characteristics77                                        |

|-----------|---------------------------------------------------------------------------|

| Table 47. | LSI oscillator characteristics                                            |

| Table 48. | MSI oscillator characteristics                                            |

| Table 49. | PLL characteristics                                                       |

| Table 50. | RAM and hardware registers                                                |

| Table 51. | Flash memory and data EEPROM characteristics                              |

| Table 52. | Flash memory and data EEPROM endurance and retention 80                   |

| Table 53. | EMS characteristics                                                       |

| Table 54. | EMI characteristics                                                       |

| Table 55. | ESD absolute maximum ratings                                              |

| Table 56. | Electrical sensitivities                                                  |

| Table 57. | I/O current injection susceptibility                                      |

| Table 58. | I/O static characteristics                                                |

| Table 59. | Output voltage characteristics                                            |

| Table 60. | I/O AC characteristics                                                    |

| Table 61. | NRST pin characteristics                                                  |

| Table 62. | ADC characteristics                                                       |

| Table 63. | R <sub>AIN</sub> max for f <sub>ADC</sub> = 16 MHz92                      |

| Table 64. | ADC accuracy92                                                            |

| Table 65. | DAC characteristics                                                       |

| Table 66. | Temperature sensor calibration values99                                   |

| Table 67. | Temperature sensor characteristics                                        |

| Table 68. | Comparator 1 characteristics                                              |

| Table 69. | Comparator 2 characteristics                                              |

| Table 70. | TIMx characteristics                                                      |

| Table 71. | I2C analog filter characteristics102                                      |

| Table 72. | USART/LPUART characteristics                                              |

| Table 73. | SPI characteristics in voltage Range 1                                    |

| Table 74. | SPI characteristics in voltage Range 2                                    |

| Table 75. | SPI characteristics in voltage Range 3                                    |

| Table 76. | I2S characteristics                                                       |

| Table 77. | USB startup time110                                                       |

| Table 78. | USB DC electrical characteristics                                         |

| Table 79. | USB: full speed electrical characteristics                                |

| Table 80. | LCD controller characteristics                                            |

| Table 81. | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data |

|           | package mechanical data                                                   |

| Table 82. | TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball   |

|           | grid array package mechanical data117                                     |

| Table 83. | TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)                   |

| Table 84. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package mechanical data   |

| Table 85. | Thermal characteristics123                                                |

| Table 86. | STM32L053x6/8 ordering information scheme125                              |

| Table 87. | Document revision history                                                 |

## 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of core and features, from 8-bit proprietary core up to ARM® Cortex®-M4, including ARM® Cortex®-M3 and ARM® Cortex®-M0+. The STM32Lx series are the best choice to answer your needs in terms of ultra-low-power features. The STM32 ultra-low-power series are the best solution for applications such as gaz/water meter, keyboard/mouse or fitness and healthcare application. Several built-in features like LCD drivers, dual-bank memory, low-power run mode, operational amplifiers, 128-bit AES, DAC, crystal-less USB and many other definitely help you building a highly cost optimized application by reducing BOM cost. STMicroelectronics, as a reliable and long-term manufacturer, ensures as much as possible pin-to-pin compatibility between all STM8Lx and STM32Lx on one hand, and between all STM32Lx and STM32Fx on the other hand. Thanks to this unprecedented scalability, your legacy application can be upgraded to respond to the latest market feature and efficiency requirements.

### 3.2 Interconnect matrix

Several peripherals are directly interconnected. This allows autonomous communication between peripherals, thus saving CPU resources and power consumption. In addition, these hardware connections allow fast and predictable latency.

Depending on peripherals, these interconnections can operate in Run, Sleep, Low-power run, Low-power sleep and Stop modes.

Table 5. STM32L0xx peripherals interconnect matrix

| Interconnect source | Interconnect destination | Interconnect action                                                | Run | Sleep | Low-<br>power<br>run | Low-<br>power<br>sleep | Stop |

|---------------------|--------------------------|--------------------------------------------------------------------|-----|-------|----------------------|------------------------|------|

| COMPx               | TIM2,TIM21,<br>TIM22     | Timer input channel,<br>trigger from analog<br>signals comparison  | Υ   | Y     | Y                    | Y                      | -    |

| COIVIFX             | LPTIM                    | Timer input channel,<br>trigger from analog<br>signals comparison  | Υ   | Υ     | Y                    | Y                      | Y    |

| TIMx                | TIMx                     | Timer triggered by other timer                                     | Y   | Υ     | Y                    | Y                      | -    |

| RTC                 | TIM21                    | Timer triggered by Auto wake-up                                    | Y   | Υ     | Y                    | Y                      | -    |

| RIC                 | LPTIM                    | Timer triggered by RTC event                                       | Υ   | Υ     | Y                    | Y                      | Υ    |

| All clock<br>source | TIMx                     | Clock source used as input channel for RC measurement and trimming | Y   | Y     | Y                    | Y                      | -    |

| USB                 | CRS/HSI48                | the clock recovery<br>system trims the HSI48<br>based on USB SOF   | Y   | Y     | -                    | -                      | -    |

|                     | TIMx                     | Timer input channel and trigger                                    | Y   | Υ     | Y                    | Y                      | -    |

| GPIO                | LPTIM                    | Timer input channel and trigger                                    | Y   | Υ     | Y                    | Y                      | Υ    |

|                     | ADC,DAC                  | Conversion trigger                                                 | Υ   | Υ     | Y                    | Y                      | -    |

#### 3.8 Memories

The STM32L053x6/8 devices have the following features:

- 8 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 32 or 64 Kbytes of embedded Flash program memory

- 2 Kbytes of data EEPROM

- Information block containing 32 user and factory options bytes plus 4 Kbytes of system memory

The user options bytes are used to write-protect or read-out protect the memory (with 4 Kbyte granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no protection

- Level 1: memory readout protected.

- The Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

- Level 2: chip readout protected, debug features (Cortex-M0+ serial wire) and boot in RAM selection disabled (debugline fuse)

The firewall protects parts of code/data from access by the rest of the code that is executed outside of the protected area. The granularity of the protected code segment or the non-volatile data segment is 256 bytes (Flash memory or EEPROM) against 64 bytes for the volatile data segment (RAM).

The whole non-volatile memory embeds the error correction code (ECC) feature.

### 3.9 Boot modes

At startup, BOOT0 pin and nBOOT1 option bit are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- · Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using SPI1(PA4, PA5, PA6, PA7) or SPI2 (PB12, PB13, PB14, PB15), USART1(PA9, PA10) or USART2(PA2, PA3). See STM32™ microcontroller system memory boot mode AN2606 for details.

577

### 3.13.2 V<sub>LCD</sub> voltage monitoring

This embedded hardware feature allows the application to measure the  $V_{LCD}$  supply voltage using the internal ADC channel ADC\_IN16. As the  $V_{LCD}$  voltage may be higher than  $V_{DDA}$ , and thus outside the ADC input range, the ADC input is connected to LCD\_VLCD2 (which provides  $1/3V_{LCD}$  when the LCD is configured 1/3Bias and  $1/4V_{LCD}$  when the LCD is configured 1/4Bias or 1/2Bias).

## 3.14 Digital-to-analog converter (DAC)

One 12-bit buffered DAC can be used to convert digital signal into analog voltage signal output. An optional amplifier can be used to reduce the output signal impedance.

This digital Interface supports the following features:

- One data holding register

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- DMA capability (including the underrun interrupt)

- External triggers for conversion

- Input reference voltage V<sub>REF+</sub>

Four DAC trigger inputs are used in the STM32L053x6/8. The DAC channel is triggered through the timer update outputs that are also connected to different DMA channels.

## 3.15 Ultra-low-power comparators and reference voltage

The STM32L053x6/8 embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with ultra low consumption

- One comparator with rail-to-rail inputs, fast or slow mode.

- The threshold can be one of the following:

- DAC output

- External I/O pins

- Internal reference voltage (V<sub>RFFINT</sub>)

- submultiple of Internal reference voltage(1/4, 1/2, 3/4) for the rail to rail comparator.

Both comparators can wake up the devices from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1 µA typical).

|       | -                              | -           |       |

|-------|--------------------------------|-------------|-------|

| Group | Capacitive sensing signal name | Pin<br>name | Group |

|       | TSC_G4_IO1                     | PA9         |       |

| 4     | TSC_G4_IO2                     | PA10        | 8     |

| 4     | TSC_G4_IO3                     | PA11        |       |

|       | TSC_G4_IO4                     | PA12        |       |

Table 8. Capacitive sensing GPIOs available on STM32L053x6/8 devices

| Group | Capacitive sensing<br>signal name | Pin<br>name |

|-------|-----------------------------------|-------------|

|       | TSC_G8_IO1                        | PC6         |

| 8     | TSC_G8_IO2                        | PC7         |

|       | TSC_G8_IO3                        | PC8         |

|       | TSC_G8_IO4                        | PC9         |

<sup>.</sup> This GPIO offers a reduced touch sensing sensitivity. It is thus recommended to use it as sampling capacitor I/O.

## 3.18 Timers and watchdogs

The ultra-low-power STM32L053x6/8 devices include three general-purpose timers, one low-power timer (LPTIM), one basic timer, two watchdog timers and the SysTick timer.

*Table 9* compares the features of the general-purpose and basic timers.

**DMA** Counter Capture/compare Complementary Timer Counter type Prescaler factor request resolution channels outputs generation Up, down, Any integer between TIM2 16-bit Yes 4 No up/down 1 and 65536 TIM21, Up, down, Any integer between 16-bit No 2 No TIM22 up/down 1 and 65536 Any integer between TIM6 16-bit Up Yes 0 No 1 and 65536

Table 9. Timer feature comparison

#### 3.18.1 General-purpose timers (TIM2, TIM21 and TIM22)

There are three synchronizable general-purpose timers embedded in the STM32L053x6/8 devices (see *Table 9* for differences).

#### TIM<sub>2</sub>

TIM2 is based on 16-bit auto-reload up/down counter. It includes a 16-bit prescaler. It features four independent channels each for input capture/output compare, PWM or one-pulse mode output.

The TIM2 general-purpose timers can work together or with the TIM21 and TIM22 general-purpose timers via the Timer Link feature for synchronization or event chaining. Their counter can be frozen in debug mode. Any of the general-purpose timers can be used to generate PWM outputs.

TIM2 has independent DMA request generation.

This timer is capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 3 hall-effect sensors.

#### 3.18.6 Window watchdog (WWDG)

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 3.19 Communication interfaces

### 3.19.1 I<sup>2</sup>C bus

two I<sup>2</sup>C interface (I2C1, I2C2) can operate in multimaster or slave modes.

Each I<sup>2</sup>C interface can support Standard mode (Sm, up to 100 kbit/s), Fast mode (Fm, up to 400 kbit/s) and Fast Mode Plus (Fm+, up to 1 Mbit/s) with 20 mA output drive on some I/Os.

7-bit and 10-bit addressing modes, multiple 7-bit slave addresses (2 addresses, 1 with configurable mask) are also supported as well as programmable analog and digital noise filters.

**Analog filter Digital filter** Pulse width of Programmable length from 1 to 15 ≥ 50 ns I2C peripheral clocks suppressed spikes 1. Extra filtering capability vs. **Benefits** Available in Stop mode standard requirements. 2. Stable length Wakeup from Stop on address Variations depending on Drawbacks match is not available when digital temperature, voltage, process filter is enabled.

Table 10. Comparison of I2C analog and digital filters

In addition, I2C1 provides hardware support for SMBus 2.0 and PMBus 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

Each I2C interface can be served by the DMA controller.

Refer to Table 11 for an overview of I2C interface features.

Table 11. STM32L053x6/8 I<sup>2</sup>C implementation

| I2C features <sup>(1)</sup>                                  | I2C1 | I2C2             |

|--------------------------------------------------------------|------|------------------|

| 7-bit addressing mode                                        | Х    | Х                |

| 10-bit addressing mode                                       | Х    | Х                |

| Standard mode (up to 100 kbit/s)                             | Х    | Х                |

| Fast mode (up to 400 kbit/s)                                 | Х    | Х                |

| Fast Mode Plus with 20 mA output drive I/Os (up to 1 Mbit/s) | Х    | X <sup>(2)</sup> |

| Independent clock                                            | Х    | -                |

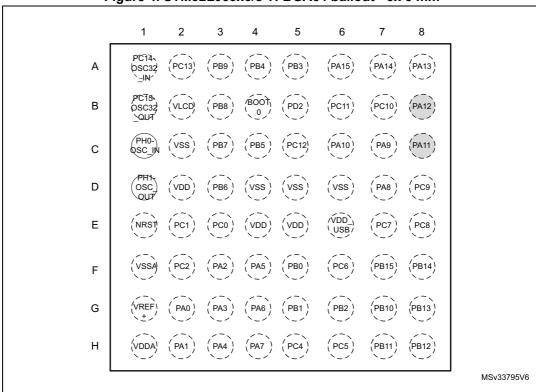

Figure 4. STM32L053x6/8 TFBGA64 ballout - 5x 5 mm

<sup>1.</sup> The above figure shows the package top view.

<sup>2.</sup> I/O pin supplied by VDD\_USB.

Table 15. STM32L053x6/8 pin definitions (continued)

| Pin    | num    | ber     |                                       |          |               |       | pin definitions (continue                                                                           | ,                               |

|--------|--------|---------|---------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------|---------------------------------|

| LQFP48 | LQFP64 | TFBGA64 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                 | Additional functions            |

| -      | 25     | Н6      | PC5                                   | I/O      | FT            | -     | LCD_SEG23,<br>LPUART1_RX,<br>TSC_G3_IO1                                                             | ADC_IN15                        |

| 18     | 26     | F5      | PB0                                   | I/O      | FT            | -     | EVENTOUT, LCD_SEG5,<br>TSC_G3_IO2                                                                   | LCD_VLCD3, ADC_IN8,<br>VREF_OUT |

| 19     | 27     | G5      | PB1                                   | I/O      | FT            | -     | LCD_SEG6,<br>TSC_G3_IO3,<br>LPUART1_RTS_DE                                                          | ADC_IN9, VREF_OUT               |

| 20     | 28     | G6      | PB2                                   | I/O      | FT            | -     | LPTIM1_OUT,<br>TSC_G3_IO4                                                                           | LCD_VLCD1                       |

| 21     | 29     | G7      | PB10                                  | I/O      | FT            | -     | LCD_SEG10, TIM2_CH3,<br>TSC_SYNC,<br>LPUART1_TX, SPI2_SCK,<br>I2C2_SCL                              | -                               |

| 22     | 30     | H7      | PB11                                  | I/O      | FT            | -     | EVENTOUT, LCD_SEG11,<br>TIM2_CH4, TSC_G6_IO1,<br>LPUART1_RX, I2C2_SDA                               | -                               |

| 23     | 31     | D6      | VSS                                   | S        |               | -     | -                                                                                                   | -                               |

| 24     | 32     | E5      | VDD                                   | S        |               | -     | -                                                                                                   | -                               |

| 25     | 33     | Н8      | PB12                                  | I/O      | FT            | -     | SPI2_NSS/I2S2_WS,<br>LCD_SEG12,<br>LPUART1_RTS_DE,<br>TSC_G6_IO2,<br>I2C2_SMBA, EVENTOUT            | LCD_VLCD2                       |

| 26     | 34     | G8      | PB13                                  | I/O      | FTf           | -     | SPI2_SCK/I2S2_CK,<br>LCD_SEG13,<br>TSC_G6_IO3,<br>LPUART1_CTS,<br>I2C2_SCL, TIM21_CH1               | -                               |

| 27     | 35     | F8      | PB14                                  | I/O      | FTf           | -     | SPI2_MISO/I2S2_MCK,<br>LCD_SEG14, RTC_OUT,<br>TSC_G6_IO4,<br>LPUART1_RTS_DE,<br>I2C2_SDA, TIM21_CH2 | -                               |

| 28     | 36     | F7      | PB15                                  | I/O      | FT            | -     | SPI2_MOSI/I2S2_SD,<br>LCD_SEG15, RTC_REFIN                                                          | -                               |

# 6.3 Operating conditions

## 6.3.1 General operating conditions

Table 24. General operating conditions

| Symbol             | Parameter                                                                        | Conditions                                 | Min  | Max                  | Unit           |  |

|--------------------|----------------------------------------------------------------------------------|--------------------------------------------|------|----------------------|----------------|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                                                     | -                                          | 0    | 32                   |                |  |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                                                    | -                                          | 0    | 32                   | MHz            |  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                                                    | -                                          | 0    | 32                   |                |  |

|                    |                                                                                  | BOR detector disabled                      | 1.65 | 3.6                  |                |  |

| V <sub>DD</sub>    | Standard operating voltage                                                       | BOR detector enabled, at power-on          | 1.8  | 3.6                  | V              |  |

|                    |                                                                                  | BOR detector disabled, after power-on      | 1.65 | 3.6                  |                |  |

| V <sub>DDA</sub>   | Analog operating voltage (DAC not used)                                          | Must be the same voltage as $V_{DD}^{(1)}$ | 1.65 | 3.6                  | ٧              |  |

| $V_{DDA}$          | Analog operating voltage (all features)                                          | Must be the same voltage as $V_{DD}^{(1)}$ | 1.8  | 3.6                  | <b>\</b>       |  |

| V <sub>DD_US</sub> | Standard operating voltage, USB                                                  | USB peripheral used                        | 3.0  | 3.6                  | V              |  |

| В                  | domain <sup>(2)</sup>                                                            | USB peripheral not used                    | 1.65 | 3.6                  | V              |  |

|                    | Input voltage on FT, FTf and RST pins <sup>(3)</sup>                             | 2.0 V ≤V <sub>DD</sub> ≤3.6 V              | -0.3 | 5.5                  |                |  |

|                    | Imput voltage on F1, F11 and R31 pins                                            | 1.65 V ≤V <sub>DD</sub> ≤2.0 V             | -0.3 | 5.2                  | - <sub>V</sub> |  |

| V <sub>IN</sub>    | Input voltage on BOOT0 pin                                                       | -                                          | 0    | 5.5                  | V              |  |

|                    | Input voltage on TC pin                                                          | -                                          | -0.3 | V <sub>DD</sub> +0.3 |                |  |

|                    |                                                                                  | TFBGA64 package                            | -    | 327                  |                |  |

|                    | Power dissipation at $T_A = 85$ °C (range 6) or $T_A = 105$ °C (rage 7) $^{(4)}$ | LQFP64 package                             | -    | 444                  |                |  |

| $P_{D}$            | 7                                                                                | LQFP48 package                             | -    | 363                  | mW             |  |

| ΓD                 |                                                                                  | TFBGA64 package                            | -    | 81                   | mvv            |  |

|                    | Power dissipation at $T_A = 125 ^{\circ}\text{C}$ (range $3)^{(4)}$              | LQFP64 package                             | -    | 111                  |                |  |

|                    |                                                                                  | LQFP48 package                             | -    | 91                   |                |  |

|                    |                                                                                  | Maximum power dissipation (range 6)        | -40  | 85                   |                |  |

| Та                 | Temperature range                                                                | Maximum power dissipation (range 7)        | -40  | 105                  |                |  |

|                    |                                                                                  | Maximum power dissipation (range 3)        | -40  | 125                  | °C             |  |

|                    | Junction temperature range (range 6)                                             | -40 °C ≤T <sub>A</sub> ≤85 °               | -40  | 105                  |                |  |

| TJ                 | Junction temperature range (range 7)                                             | -40 °C ≤T <sub>A</sub> ≤105 °C             | -40  | 125                  | -              |  |

|                    | Junction temperature range (range 3)                                             | -40 °C ≤T <sub>A</sub> ≤125 °C             | -40  | 130                  |                |  |

It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and normal operation.

- 2.  $V_{DD\_USB}$  must respect the following conditions:

- When  $V_{DD}$  is powered-on ( $V_{DD}$  <  $V_{DD}$   $_{min}$ ),  $V_{DD}$   $_{USB}$  should be always lower than  $V_{DD}$ .

- When  $V_{DD}$  is powered-down ( $V_{DD}$  <  $V_{DD}$   $_{min}$ ),  $V_{DD}$   $_{USB}$  should be always lower than  $V_{DD}$ .

- In operating mode,  $V_{DD\ USB}$  could be lower or higher  $V_{DD.}$

- If the USB is not used,  $V_{DD\_USB}$  must range from  $V_{DD\_min}$  to  $V_{DD\_max}$  to be able to use PA11 and PA12 as standard I/Os.

- 3. To sustain a voltage higher than  $V_{DD}$ +0.3V, the internal pull-up/pull-down resistors must be disabled.

- If T<sub>A</sub> is lower, higher P<sub>D</sub> values are allowed as long as T<sub>J</sub> does not exceed T<sub>J</sub> max (see Table 85: Thermal characteristics on page 123).

Table 36. Typical and maximum current consumptions in Standby mode

| Symbol          | Parameter                      | Conditi                                 | Тур                                        | Max <sup>(1)</sup>                         | Unit |                |  |

|-----------------|--------------------------------|-----------------------------------------|--------------------------------------------|--------------------------------------------|------|----------------|--|

|                 |                                |                                         |                                            | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 1.3  | 1.7            |  |

|                 |                                |                                         | T <sub>A</sub> = 55 °C                     | -                                          | 2.9  |                |  |

|                 |                                | Independent watchdog<br>and LSI enabled | T <sub>A</sub> = 85 °C                     | -                                          | 3.3  |                |  |

|                 | Supply current in Standby mode | u.14                                    | T <sub>A</sub> = 105 °C                    | -                                          | 4.1  |                |  |

| I <sub>DD</sub> |                                |                                         | T <sub>A</sub> = 125 °C                    | -                                          | 8.5  |                |  |

| (Standby)       |                                | Independent watchdog<br>and LSI OFF     | $T_A = -40 \text{ to } 25^{\circ}\text{C}$ | 0.29                                       | 0.6  | - μA<br>-<br>- |  |

|                 |                                |                                         | T <sub>A</sub> = 55 °C                     | 0.32                                       | 0.9  |                |  |

|                 |                                |                                         | T <sub>A</sub> = 85 °C                     | 0.5                                        | 2.3  |                |  |

|                 |                                |                                         | T <sub>A</sub> = 105 °C                    | 0.94                                       | 3    |                |  |

|                 |                                |                                         | T <sub>A</sub> = 125 °C                    | 2.6                                        | 7    |                |  |

<sup>1.</sup> Guaranteed by characterization results at 125  $^{\circ}$ C, unless otherwise specified

Table 37. Average current consumption during Wakeup

| Symbol                             | parameter                                   | System frequency     | Current<br>consumption<br>during wakeup | Unit |

|------------------------------------|---------------------------------------------|----------------------|-----------------------------------------|------|

|                                    |                                             | HSI                  | 1                                       |      |

|                                    |                                             | HSI/4                | 0,7                                     |      |

| I <sub>DD</sub> (Wakeup from Stop) | Supply current during Wakeup from Stop mode | MSI clock = 4,2 MHz  | 0,7                                     |      |

| , ,                                |                                             | MSI clock = 1,05 MHz | 0,4                                     |      |

|                                    |                                             | MSI clock = 65 KHz   | 0,1                                     | mA   |

| I <sub>DD</sub> (Reset)            | Reset pin pulled down                       | -                    | 0,21                                    |      |

| I <sub>DD</sub> (Power-up)         | BOR ON                                      | -                    | 0,23                                    |      |

| I <sub>DD</sub> (Wakeup from       | With Fast wakeup set                        | MSI clock = 2,1 MHz  | 0,5                                     |      |

| StandBy)                           | With Fast wakeup disabled                   | MSI clock = 2,1 MHz  | 0,12                                    |      |

#### On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in the following tables. The MCU is placed under the following conditions:

- $\bullet$   $\,$  all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked OFF

- with only one peripheral clocked on

Table 38. Peripheral current consumption in Run or Sleep mode<sup>(1)</sup>

|      |                     | Typical                                               | 25 °C                                                 |                                                       |                               |                                |

|------|---------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------|--------------------------------|

| Pei  | ripheral            | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | Low-power<br>sleep and<br>run | Unit                           |

|      | CRS                 | 2.5                                                   | 2                                                     | 2                                                     | 2                             |                                |

|      | DAC1                | 4                                                     | 3.5                                                   | 3                                                     | 2.5                           |                                |

|      | I2C1                | 11                                                    | 9.5                                                   | 7.5                                                   | 9                             |                                |

|      | I2C2                | 4                                                     | 3.5                                                   | 3                                                     | 2.5                           |                                |

|      | LCD1                | 4                                                     | 3.5                                                   | 3                                                     | 2.5                           |                                |

|      | LPTIM1              | 10                                                    | 8.5                                                   | 6.5                                                   | 8                             |                                |

| APB1 | LPUART1             | 8                                                     | 6.5                                                   | 5.5                                                   | 6                             | μΑ/ΜΗz<br>(f <sub>HCLK</sub> ) |

|      | SPI2                | 9                                                     | 4.5                                                   | 3.5                                                   | 4                             |                                |

|      | USB                 | 8.5                                                   | 4.5                                                   | 4                                                     | 4.5                           |                                |

|      | USART2              | 14.5                                                  | 12                                                    | 9.5                                                   | 11                            |                                |

|      | TIM2                | 10.5                                                  | 8.5                                                   | 7                                                     | 9                             |                                |

|      | TIM6                | 3.5                                                   | 3                                                     | 2.5                                                   | 2                             |                                |

|      | WWDG                | 3                                                     | 2                                                     | 2                                                     | 2                             |                                |

|      | ADC1 <sup>(2)</sup> | 5.5                                                   | 5                                                     | 3.5                                                   | 4                             |                                |

|      | SPI1                | 4                                                     | 3                                                     | 3                                                     | 2.5                           |                                |

|      | USART1              | 14.5                                                  | 11.5                                                  | 9.5                                                   | 12                            |                                |

| APB2 | TIM21               | 7.5                                                   | 6                                                     | 5                                                     | 5.5                           | μΑ/MHz                         |

| AFD2 | TIM22               | 7                                                     | 6                                                     | 5                                                     | 6                             | (f <sub>HCLK</sub> )           |

|      | FIREWALL            | 1.5                                                   | 1                                                     | 1                                                     | 0.5                           |                                |

|      | DBGMCU              | 1.5                                                   | 1                                                     | 1                                                     | 0.5                           |                                |

|      | SYSCFG              | 2.5                                                   | 2                                                     | 2                                                     | 1.5                           |                                |

68/132 DocID025844 Rev 7

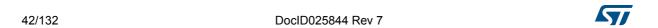

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 44*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                   | Parameter                                 | Conditions <sup>(2)</sup>                       | Min <sup>(2)</sup> | Тур    | Max  | Unit    |

|--------------------------|-------------------------------------------|-------------------------------------------------|--------------------|--------|------|---------|

| f <sub>LSE</sub>         | LSE oscillator frequency                  |                                                 | -                  | 32.768 | -    | kHz     |

| G <sub>m</sub>           | Maximum critical crystal transconductance | LSEDRV[1:0]=00 lower driving capability         |                    |        | 0.5  |         |

|                          |                                           | LSEDRV[1:0]= 01 medium low driving capability   | -                  | -      | 0.75 | uA/V    |

|                          |                                           | LSEDRV[1:0] = 10 medium high driving capability |                    |        | 1.7  | - μΑν ν |

|                          |                                           | LSEDRV[1:0]=11 higher driving capability        | -                  | -      | 2.7  |         |

| t <sub>SU(LSE)</sub> (3) | Startup time                              | V <sub>DD</sub> is stabilized                   | -                  | 2      | -    | S       |

Table 44. LSE oscillator characteristics<sup>(1)</sup>

Note: For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Figure 20. Typical application with a 32.768 kHz crystal

Note:

An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

<sup>1.</sup> Guaranteed by design.

Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

Guaranteed by characterization results. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer. To increase speed, address a lower-drive quartz with a high- driver mode.

#### 6.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibility to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (higher than 5 LSB TUE), out of conventional limits of induced leakage current on adjacent pins (out of  $-5 \mu A/+0 \mu A$  range), or other functional failure (for example reset occurrence oscillator frequency deviation, LCD levels).

The test results are given in the *Table 57*.

Table 57. I/O current injection susceptibility

|                  |                                                                  | Functional s       |                    |      |  |

|------------------|------------------------------------------------------------------|--------------------|--------------------|------|--|

| Symbol           | Description                                                      | Negative injection | Positive injection | Unit |  |

|                  | Injected current on BOOT0                                        | -0                 | NA                 |      |  |

| I <sub>INJ</sub> | Injected current on PA0, PA4, PA5, PA11, PA12, PC15, PH0 and PH1 | -5                 | 0                  | mA   |  |

|                  | Injected current on any other FT, FTf pins                       | -5 <sup>(1)</sup>  | NA                 |      |  |

|                  | Injected current on any other pins                               | -5 <sup>(1)</sup>  | +5                 |      |  |

It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

84/132 DocID025844 Rev 7

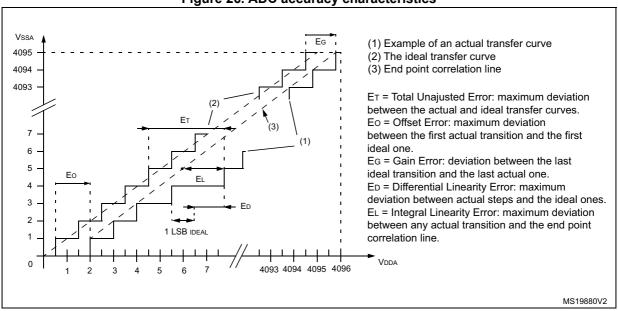

| Symbol | Parameter                    | Conditions                                                         | Min  | Тур  | Max | Unit |

|--------|------------------------------|--------------------------------------------------------------------|------|------|-----|------|

| ET     | Total unadjusted error       |                                                                    | -    | 2    | 5   |      |

| EO     | Offset error                 |                                                                    | -    | 1    | 2.5 |      |

| EG     | Gain error                   | 1.65 V < V <sub>REF+</sub> < V <sub>DDA</sub> < 3.6 V, range 1/2/3 | -    | 1    | 2   | LSB  |

| EL     | Integral linearity error     |                                                                    | -    | 1.5  | 3   |      |

| ED     | Differential linearity error |                                                                    | -    | 1    | 2   |      |

| ENOB   | Effective number of bits     |                                                                    | 10.0 | 11.0 | -   | bits |

| SINAD  | Signal-to-noise distortion   |                                                                    | 62   | 69   | -   |      |

| SNR    | Signal-to-noise ratio        |                                                                    | 61   | 69   | -   | dB   |

| THD    | Total harmonic distortion    |                                                                    | -    | -85  | -65 |      |

Table 64. ADC accuracy<sup>(1)(2)(3)</sup> (continued)

- 1. ADC DC accuracy values are measured after internal calibration.

- ADC Accuracy vs. Negative Injection Current: Injecting negative current on any of the standard (non-robust) analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current.

Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.12 does not affect the ADC accuracy.

- Better performance may be achieved in restricted V<sub>DDA</sub>, frequency and temperature ranges.

- 4. This number is obtained by the test board without additional noise, resulting in non-optimized value for oversampling mode.

Figure 26. ADC accuracy characteristics

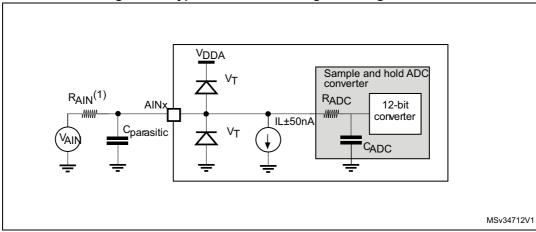

Figure 27. Typical connection diagram using the ADC

- 1. Refer to Table 62: ADC characteristics for the values of RAIN, RADC and CADC.

- C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

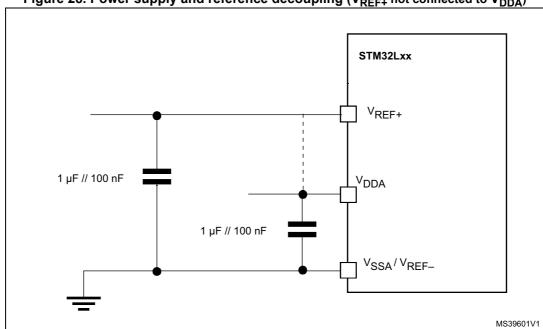

#### General PCB design guidelines

Power supply decoupling should be performed as shown in *Figure 28* or *Figure 29*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed as close as possible to the chip.

Figure 28. Power supply and reference decoupling ( $V_{REF+}$  not connected to  $V_{DDA}$ )

## 6.3.16 DAC electrical characteristics

Data guaranteed by design, not tested in production, unless otherwise specified.

Table 65. DAC characteristics

| Symbol                          | Parameter                                | Cond                                                    | litions   | Min                                                     | Тур     | Max                    | Unit |     |   |

|---------------------------------|------------------------------------------|---------------------------------------------------------|-----------|---------------------------------------------------------|---------|------------------------|------|-----|---|

| $V_{DDA}$                       | Analog supply voltage                    | -                                                       |           | 1.8                                                     | -       | 3.6                    | V    |     |   |

| V <sub>REF+</sub>               | Reference supply voltage                 | V <sub>REF+</sub> must always be below V <sub>DDA</sub> |           | V <sub>REF+</sub> must always be below V <sub>DDA</sub> |         | 1.8                    | -    | 3.6 | ٧ |

| V <sub>REF-</sub>               | Lower reference voltage                  | -                                                       |           | V <sub>SSA</sub>                                        |         |                        | V    |     |   |

| I <sub>DDVREF+</sub> (1)        | Current consumption on V <sub>REF+</sub> | No load, middle code (0x800)                            |           | -                                                       | 130     | 220                    |      |     |   |

| IDDVREF+` '                     | supply V <sub>REF+</sub> = 3.3 V         | No load, wor<br>(0x000)                                 | st code   | -                                                       | 220     | 3.6                    | μΑ   |     |   |

| (2)                             | Current consumption on V <sub>DDA</sub>  | No load, mid<br>(0x800)                                 | ldle code | -                                                       | 210 320 |                        | - μΑ |     |   |

| I <sub>DDA</sub> <sup>(2)</sup> | supply,<br>V <sub>DDA</sub> = 3.3 V      | No load, worst code (0xF1C)                             |           | -                                                       | 320     | 520                    |      |     |   |

| R <sub>I</sub> <sup>(3)</sup>   | Resistive load                           | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$  | -         | -                                                       | kO      |                        |      |     |   |

| RL <sup>(*)</sup>               |                                          |                                                         | connected | 25                                                      | -       | -                      | · kΩ |     |   |

| C <sub>L</sub> <sup>(3)</sup>   | Capacitive load                          | DAC output buffer ON                                    |           | -                                                       | -       | 50                     | pF   |     |   |

| R <sub>O</sub>                  | Output impedance                         | DAC output buffer OFF                                   |           | 12                                                      | 16      | 20                     | kΩ   |     |   |

| V <sub>DAC_OUT</sub>            | Voltage on DAC_OUT output                | DAC output buffer ON                                    |           | 0.2                                                     | -       | V <sub>DDA</sub> – 0.2 | ٧    |     |   |

|                                 |                                          | DAC output buffer OFF                                   |           | 0.5                                                     | -       |                        | mV   |     |   |

## 7.3 LQFP48 package information

Figure 43. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline

1. Drawing is not to scale.