Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                       |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 32MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT      |

| Number of I/O              | 51                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 2K x 8                                                                 |

| RAM Size                   | 8K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-TFBGA                                                               |

| Supplier Device Package    | 64-TFBGA (5x5)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l053r8h6d |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                           |            |       | Low-         | Low-           |                  | Stop                 |   | Standby              |

|-------------------------------------------|------------|-------|--------------|----------------|------------------|----------------------|---|----------------------|

| IPs                                       | Run/Active | Sleep | power<br>run | power<br>sleep |                  | Wakeup<br>capability |   | Wakeup<br>capability |

| CPU                                       | Y          |       | Y            |                |                  |                      |   |                      |

| Flash memory                              | 0          | 0     | 0            | 0              |                  |                      |   |                      |

| RAM                                       | Y          | Y     | Y            | Y              | Υ                |                      |   |                      |

| Backup registers                          | Y          | Y     | Y            | Y              | Υ                |                      | Y |                      |

| EEPROM                                    | 0          | 0     | 0            | 0              |                  |                      |   |                      |

| Brown-out reset<br>(BOR)                  | 0          | 0     | 0            | 0              | 0                | 0                    | 0 | 0                    |

| DMA                                       | 0          | 0     | 0            | 0              |                  |                      |   |                      |

| Programmable<br>Voltage Detector<br>(PVD) | 0          | 0     | 0            | ο              | 0                | 0                    | - |                      |

| Power-on/down<br>reset (POR/PDR)          | Y          | Y     | Y            | Y              | Y                | Y                    | Y | Y                    |

| High Speed<br>Internal (HSI)              | 0          | 0     |              |                | (2)              |                      |   |                      |

| High Speed<br>External (HSE)              | 0          | 0     | 0            | 0              |                  |                      |   |                      |

| Low Speed Internal<br>(LSI)               | 0          | 0     | 0            | 0              | 0                |                      | 0 |                      |

| Low Speed<br>External (LSE)               | 0          | 0     | 0            | 0              | 0                |                      | 0 |                      |

| Multi-Speed<br>Internal (MSI)             | 0          | 0     | Y            | Y              |                  |                      |   |                      |

| Inter-Connect<br>Controller               | Y          | Y     | Y            | Y              | Y                |                      |   |                      |

| RTC                                       | 0          | 0     | 0            | 0              | 0                | 0                    | 0 |                      |

| RTC Tamper                                | 0          | 0     | 0            | 0              | 0                | 0                    | 0 | 0                    |

| Auto WakeUp<br>(AWU)                      | 0          | 0     | 0            | 0              | 0                | 0                    | 0 | 0                    |

| LCD                                       | 0          | 0     | 0            | 0              | 0                |                      |   |                      |

| USB                                       | 0          | 0     |              |                |                  | 0                    |   |                      |

| USART                                     | 0          | 0     | 0            | 0              | O <sup>(3)</sup> | 0                    |   |                      |

| LPUART                                    | 0          | 0     | 0            | 0              | O <sup>(3)</sup> | 0                    |   |                      |

| SPI                                       | 0          | 0     | 0            | 0              |                  |                      |   |                      |

| I2C                                       | 0          | 0     | 0            | 0              | O <sup>(4)</sup> | 0                    |   |                      |

| ADC                                       | 0          | 0     |              |                |                  |                      |   |                      |

Table 4. Functionalities depending on the working mode (from Run/active down to standby) <sup>(1)</sup>

# 3.3 ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core with MPU

The Cortex-M0+ processor is an entry-level 32-bit ARM Cortex processor designed for a broad range of embedded applications. It offers significant benefits to developers, including:

- a simple architecture that is easy to learn and program

- ultra-low power, energy-efficient operation

- excellent code density

- deterministic, high-performance interrupt handling

- upward compatibility with Cortex-M processor family

- platform security robustness, with integrated Memory Protection Unit (MPU).

The Cortex-M0+ processor is built on a highly area and power optimized 32-bit processor core, with a 2-stage pipeline Von Neumann architecture. The processor delivers exceptional energy efficiency through a small but powerful instruction set and extensively optimized design, providing high-end processing hardware including a single-cycle multiplier.

The Cortex-M0+ processor provides the exceptional performance expected of a modern 32bit architecture, with a higher code density than other 8-bit and 16-bit microcontrollers.

Owing to its embedded ARM core, the STM32L053x6/8 are compatible with all ARM tools and software.

#### Nested vectored interrupt controller (NVIC)

The ultra-low-power STM32L053x6/8 embed a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels and 4 priority levels.

The Cortex-M0+ processor closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance. The NVIC:

- includes a Non-Maskable Interrupt (NMI)

- provides zero jitter interrupt option

- provides four interrupt priority levels

The tight integration of the processor core and NVIC provides fast execution of Interrupt Service Routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to abandon and restart load-multiple and store-multiple operations. Interrupt handlers do not require any assembler wrapper code, removing any code overhead from the ISRs. Tail-chaining optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes, that include a deep sleep function that enables the entire device to enter rapidly stop or standby mode.

This hardware block provides flexible interrupt management features with minimal interrupt latency.

## 3.8 Memories

The STM32L053x6/8 devices have the following features:

- 8 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states. With the enhanced bus matrix, operating the RAM does not lead to any performance penalty during accesses to the system bus (AHB and APB buses).

- The non-volatile memory is divided into three arrays:

- 32 or 64 Kbytes of embedded Flash program memory

- 2 Kbytes of data EEPROM

- Information block containing 32 user and factory options bytes plus 4 Kbytes of system memory

The user options bytes are used to write-protect or read-out protect the memory (with 4 Kbyte granularity) and/or readout-protect the whole memory with the following options:

- Level 0: no protection

- Level 1: memory readout protected.

The Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected

• Level 2: chip readout protected, debug features (Cortex-M0+ serial wire) and boot in RAM selection disabled (debugline fuse)

The firewall protects parts of code/data from access by the rest of the code that is executed outside of the protected area. The granularity of the protected code segment or the non-volatile data segment is 256 bytes (Flash memory or EEPROM) against 64 bytes for the volatile data segment (RAM).

The whole non-volatile memory embeds the error correction code (ECC) feature.

# 3.9 Boot modes

At startup, BOOT0 pin and nBOOT1 option bit are used to select one of three boot options:

- Boot from Flash memory

- Boot from System memory

- Boot from embedded RAM

The boot loader is located in System memory. It is used to reprogram the Flash memory by using SPI1(PA4, PA5, PA6, PA7) or SPI2 (PB12, PB13, PB14, PB15), USART1(PA9, PA10) or USART2(PA2, PA3). See STM32<sup>™</sup> microcontroller system memory boot mode AN2606 for details.

## 3.13.2 V<sub>LCD</sub> voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>LCD</sub> supply voltage using the internal ADC channel ADC\_IN16. As the V<sub>LCD</sub> voltage may be higher than V<sub>DDA</sub>, and thus outside the ADC input range, the ADC input is connected to LCD\_VLCD2 (which provides 1/3V<sub>LCD</sub> when the LCD is configured 1/3Bias and 1/4V<sub>LCD</sub> when the LCD is configured 1/4Bias or 1/2Bias).

# 3.14 Digital-to-analog converter (DAC)

One 12-bit buffered DAC can be used to convert digital signal into analog voltage signal output. An optional amplifier can be used to reduce the output signal impedance.

This digital Interface supports the following features:

- One data holding register

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- DMA capability (including the underrun interrupt)

- External triggers for conversion

- Input reference voltage V<sub>REF+</sub>

Four DAC trigger inputs are used in the STM32L053x6/8. The DAC channel is triggered through the timer update outputs that are also connected to different DMA channels.

## 3.15 Ultra-low-power comparators and reference voltage

The STM32L053x6/8 embed two comparators sharing the same current bias and reference voltage. The reference voltage can be internal or external (coming from an I/O).

- One comparator with ultra low consumption

- One comparator with rail-to-rail inputs, fast or slow mode.

- The threshold can be one of the following:

- DAC output

- External I/O pins

- Internal reference voltage (V<sub>REFINT</sub>)

- submultiple of Internal reference voltage(1/4, 1/2, 3/4) for the rail to rail comparator.

Both comparators can wake up the devices from Stop mode, and be combined into a window comparator.

The internal reference voltage is available externally via a low-power / low-current output buffer (driving current capability of 1  $\mu$ A typical).

#### TIM21 and TIM22

TIM21 and TIM22 are based on a 16-bit auto-reload up/down counter. They include a 16-bit prescaler. They have two independent channels for input capture/output compare, PWM or one-pulse mode output. They can work together and be synchronized with the TIM2, full-featured general-purpose timers.

They can also be used as simple time bases and be clocked by the LSE clock source (32.768 kHz) to provide time bases independent from the main CPU clock.

## 3.18.2 Low-power Timer (LPTIM)

The low-power timer has an independent clock and is running also in Stop mode if it is clocked by LSE, LSI or an external clock. It is able to wakeup the devices from Stop mode.

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous / one shot mode

- Selectable software / hardware input trigger

- Selectable clock source

- Internal clock source: LSE, LSI, HSI or APB clock

- External clock source over LPTIM input (working even with no internal clock source running, used by the Pulse Counter Application)

- Programmable digital glitch filter

- Encoder mode

## 3.18.3 Basic timer (TIM6)

This timer can be used as a generic 16-bit timebase. It is mainly used for DAC trigger generation.

#### 3.18.4 SysTick timer

This timer is dedicated to the OS, but could also be used as a standard downcounter. It is based on a 24-bit downcounter with autoreload capability and a programmable clock source. It features a maskable system interrupt generation when the counter reaches '0'.

## 3.18.5 Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 37 kHz internal RC and, as it operates independently of the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

| Table 15. STM32L053x6/8 pin definitions (continued) | Table 15 | STM32L053x6/8 | pin definitions | (continued) |

|-----------------------------------------------------|----------|---------------|-----------------|-------------|

|-----------------------------------------------------|----------|---------------|-----------------|-------------|

| Pin    | num    | ber     |                                       |          |               |       |                                                                    |                      |

|--------|--------|---------|---------------------------------------|----------|---------------|-------|--------------------------------------------------------------------|----------------------|

| LQFP48 | LQFP64 | TFBGA64 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                | Additional functions |

| -      | 37     | F6      | PC6                                   | I/O      | FT            | -     | TIM22_CH1,LCD_SEG24,<br>TSC_G8_IO1                                 | -                    |

| -      | 38     | E7      | PC7                                   | I/O      | FT            | -     | TIM22_CH2, LCD_SEG25,<br>TSC_G8_IO2                                | -                    |

| -      | 39     | E8      | PC8                                   | I/O      | FT            | -     | TIM22_ETR, LCD_SEG26,<br>TSC_G8_IO3                                | -                    |

| -      | 40     | D8      | PC9                                   | I/O      | FT            | -     | TIM21_ETR, LCD_SEG27,<br>USB_NOE, TSC_G8_IO4                       | -                    |

| 29     | 41     | D7      | PA8                                   | I/O      | FT            | -     | MCO, LCD_COM0,<br>USB_CRS_SYNC,<br>EVENTOUT, USART1_CK             | -                    |

| 30     | 42     | C7      | PA9                                   | I/O      | FT            | -     | MCO, LCD_COM1,<br>TSC_G4_IO1,<br>USART1_TX                         | -                    |

| 31     | 43     | C6      | PA10                                  | I/O      | FT            | -     | LCD_COM2,<br>TSC_G4_IO2,<br>USART1_RX                              | -                    |

| 32     | 44     | C8      | PA11                                  | I/O      | FT            | (2)   | SPI1_MISO, EVENTOUT,<br>TSC_G4_IO3,<br>USART1_CTS,<br>COMP1_OUT    | USB_DM               |

| 33     | 45     | B8      | PA12                                  | I/O      | FT            | (2)   | SPI1_MOSI, EVENTOUT,<br>TSC_G4_IO4,<br>USART1_RTS_DE,<br>COMP2_OUT | USB_DP               |

| 34     | 46     | A8      | PA13                                  | I/O      | FT            | -     | SWDIO, USB_NOE                                                     | -                    |

| 35     | 47     | D5      | VSS                                   | S        |               | -     | -                                                                  | -                    |

| 36     | 48     | E6      | VDD_USB                               | S        |               | -     | -                                                                  | -                    |

| 37     | 49     | A7      | PA14                                  | I/O      | FT            | -     | SWCLK, USART2_TX                                                   | -                    |

| 38     | 50     | A6      | PA15                                  | I/O      | FT            | -     | SPI1_NSS, LCD_SEG17,<br>TIM2_ETR, EVENTOUT,<br>USART2_RX, TIM2_CH1 | -                    |

| -      | 51     | B7      | PC10                                  | I/O      | FT            | -     | LPUART1_TX,<br>LCD_COM4/LCD_SEG28/<br>LCD_SEG40                    | -                    |

DocID025844 Rev 7

| 45/132            |        |            |                                 |           | Table 16. Alter        | nate function    | port A            |            |          |           |

|-------------------|--------|------------|---------------------------------|-----------|------------------------|------------------|-------------------|------------|----------|-----------|

| 32                | Port   |            | AF0                             | AF1       | AF2                    | AF3              | AF4               | AF5        | AF6      | AF7       |

|                   |        |            | SPI1/TIM21/SYS_A<br>F/EVENTOUT/ | LCD       | USB/TIM2/<br>EVENTOUT/ | TSC/<br>EVENTOUT | USART1/2/3        | TIM2/21/22 | EVENTOUT | COMP1/2   |

|                   |        | PA0        | -                               | -         | TIM2_CH1               | TSC_G1_IO1       | USART2_CTS        | TIM2_ETR   | -        | COMP1_OUT |

|                   |        | PA1        | EVENTOUT                        | LCD_SEG0  | TIM2_CH2               | TSC_G1_IO2       | USART2_RTS_<br>DE | TIM21_ETR  | -        | -         |

|                   |        | PA2        | TIM21_CH1                       | LCD_SEG1  | TIM2_CH3               | TSC_G1_IO3       | USART2_TX         | -          | -        | COMP2_OUT |

|                   |        | PA3        | TIM21_CH2                       | LCD_SEG2  | TIM2_CH4               | TSC_G1_IO4       | USART2_RX         | -          | -        | -         |

|                   |        | PA4<br>(1) | SPI1_NSS                        | -         | -                      | TSC_G2_IO1       | USART2_CK         | TIM22_ETR  | -        | -         |

| D                 |        | PA5        | SPI1_SCK                        | -         | TIM2_ETR               | TSC_G2_IO2       | -                 | TIM2_CH1   | -        | -         |

| DocID025844 Rev 7 |        | PA6        | SPI1_MISO                       | LCD_SEG3  | -                      | TSC_G2_IO3       | LPUART1_CTS       | TIM22_CH1  | EVENTOUT | COMP1_OUT |

| 025               | Port A | PA7        | SPI1_MOSI                       | LCD_SEG4  | -                      | TSC_G2_IO4       | -                 | TIM22_CH2  | EVENTOUT | COMP2_OUT |

| 844               |        | PA8        | МСО                             | LCD_COM0  | USB_CRS_SYNC           | EVENTOUT         | USART1_CK         | -          | -        | -         |

| Rev               |        | PA9        | МСО                             | LCD_COM1  | -                      | TSC_G4_IO1       | USART1_TX         | -          | -        | -         |

| 7                 |        | PA10       | -                               | LCD_COM2  | -                      | TSC_G4_IO2       | USART1_RX         | -          | -        | -         |

|                   |        | PA11       | SPI1_MISO                       | -         | EVENTOUT               | TSC_G4_IO3       | USART1_CTS        | -          | -        | COMP1_OUT |

|                   |        | PA12       | SPI1_MOSI                       | -         | EVENTOUT               | TSC_G4_IO4       | USART1_RTS_<br>DE | -          | -        | COMP2_OUT |

|                   |        | PA13       | SWDIO                           | -         | USB_NOE                | -                | -                 | -          | -        | -         |

|                   |        | PA14       | SWCLK                           | -         | -                      | -                | USART2_TX         | -          | -        | -         |

|                   |        | PA15       | SPI1_NSS                        | LCD_SEG17 | TIM2_ETR               | EVENTOUT         | USART2_RX         | TIM2_CH1   | -        | -         |

1. This GPIO offers a reduced touch sensing sensitivity. It is thus recommended to use it as sampling capacitor I/O.

STM32L053x6 STM32L053x8

5

| Table 20. Alternate function port H |     |              |  |  |  |

|-------------------------------------|-----|--------------|--|--|--|

| Port                                |     | AF0          |  |  |  |

|                                     |     | USB          |  |  |  |

| Port H                              | PH0 | USB_CRS_SYNC |  |  |  |

| FUILE                               | PH1 | _            |  |  |  |

STM32L053x6 STM32L053x8

| Symbol            | Parameter Conditions |                                           | Min  | Тур  | Max  | Unit |

|-------------------|----------------------|-------------------------------------------|------|------|------|------|

| V <sub>PVD6</sub> | PVD threshold 6      | Falling edge                              | 2.97 | 3.05 | 3.09 | V    |

|                   |                      | Rising edge                               | 3.08 | 3.15 | 3.20 | v    |

|                   | Hysteresis voltage   | BOR0 threshold                            | -    | 40   | -    |      |

| V <sub>hyst</sub> |                      | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |

Table 25. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

## 6.3.3 Embedded internal reference voltage

The parameters given in *Table 27* are based on characterization results, unless otherwise specified.

| Table 26. Embedde | ed internal ref | ference vo | ltage o | calibration values |

|-------------------|-----------------|------------|---------|--------------------|

|                   |                 |            |         |                    |

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

| Symbol                                   | Parameter                                                                                    | Conditions                                                                              | Min   | Тур   | Max   | Unit   |

|------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|--------|

| V <sub>REFINT out</sub> <sup>(2)</sup>   | Internal reference voltage                                                                   | – 40 °C < T <sub>J</sub> < +125 °C                                                      | 1.202 | 1.224 | 1.242 | V      |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                                              | -                                                                                       | -     | 2     | 3     | ms     |

| V <sub>VREF_MEAS</sub>                   | V <sub>DDA</sub> and V <sub>REF+</sub> voltage during<br>V <sub>REFINT</sub> factory measure | -                                                                                       | 2.99  | 3     | 3.01  | V      |

| A <sub>VREF_MEAS</sub>                   | Accuracy of factory-measured $V_{REFINT}$ value <sup>(3)</sup>                               | Including uncertainties<br>due to ADC and<br>V <sub>DDA</sub> /V <sub>REF+</sub> values | -     | -     | ±5    | mV     |

| T <sub>Coeff</sub> <sup>(4)</sup>        | Temperature coefficient                                                                      | –40 °C < T <sub>J</sub> < +125 °C                                                       | -     | 25    | 100   | ppm/°C |

| A <sub>Coeff</sub> <sup>(4)</sup>        | Long-term stability                                                                          | 1000 hours, T= 25 °C                                                                    | -     | -     | 1000  | ppm    |

| V <sub>DDCoeff</sub> <sup>(4)</sup>      | Voltage coefficient                                                                          | 3.0 V < V <sub>DDA</sub> < 3.6 V                                                        | -     | -     | 2000  | ppm/V  |

| T <sub>S_vrefint</sub> <sup>(4)(5)</sup> | ADC sampling time when<br>reading the internal reference<br>voltage                          | -                                                                                       | 5     | 10    | -     | μs     |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>      | Startup time of reference voltage buffer for ADC                                             | -                                                                                       | -     | -     | 10    | μs     |

| I <sub>BUF_ADC</sub> <sup>(4)</sup>      | Consumption of reference voltage buffer for ADC                                              | -                                                                                       | -     | 13.5  | 25    | μA     |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output current <sup>(6)</sup>                                                       | -                                                                                       | -     | -     | 1     | μA     |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output load                                                                         | -                                                                                       | -     | -     | 50    | pF     |

## Table 27. Embedded internal reference voltage<sup>(1)</sup>

| Cumhal                     | Devinhevel                   | Typical consum         | ption, T <sub>A</sub> = 25 °C | 11   |  |

|----------------------------|------------------------------|------------------------|-------------------------------|------|--|

| Symbol                     | Peripheral                   | V <sub>DD</sub> =1.8 V | V <sub>DD</sub> =3.0 V        | Unit |  |

| I <sub>DD(PVD / BOR)</sub> | -                            | 0.7                    | 1.2                           |      |  |

| I <sub>REFINT</sub>        | -                            | -                      | 1.4                           |      |  |

| -                          | LSE Low drive <sup>(2)</sup> | 0,1                    | 0,1                           |      |  |

| -                          | LPTIM1, Input 100 Hz         | 0,01                   | 0,01                          | μA   |  |

| -                          | LPTIM1, Input 1 MHz          | 6                      | 6                             |      |  |

| -                          | LPUART1                      | 0,2                    | 0,2                           |      |  |

| -                          | RTC                          | 0,3                    | 0,48                          | -    |  |

| -                          | LCD1 (static duty)           | 0,15                   | 0,15                          |      |  |

| -                          | LCD1 (1/8 duty)              | 1,6                    | 2,6                           | μA   |  |

| Table 39. Periphera | I current consumptio | on in Stop and St | tandby mode <sup>(1)</sup> |

|---------------------|----------------------|-------------------|----------------------------|

|---------------------|----------------------|-------------------|----------------------------|

1. LPTIM peripheral cannot operate in Standby mode.

2. LSE Low drive consumption is the difference between an external clock on OSC32\_IN and a quartz between OSC32\_IN and OSC32\_OUT.-

## 6.3.5 Wakeup time from low-power mode

The wakeup times given in the following table are measured with the MSI or HSI16 RC oscillator. The clock source used to wake up the device depends on the current operating mode:

- Sleep mode: the clock source is the clock that was set before entering Sleep mode

- Stop mode: the clock source is either the MSI oscillator in the range configured before entering Stop mode, the HSI16 or HSI16/4.

- Standby mode: the clock source is the MSI oscillator running at 2.1 MHz

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

## High-speed internal 48 MHz (HSI48) RC oscillator

| Symbol                  | Parameter                                                                          | Conditions             | Min                 | Тур  | Мах                | Unit |  |  |

|-------------------------|------------------------------------------------------------------------------------|------------------------|---------------------|------|--------------------|------|--|--|

| f <sub>HSI48</sub>      | Frequency                                                                          |                        | -                   | 48   | -                  | MHz  |  |  |

| TRIM                    | HSI48 user-trimming step                                                           |                        | 0.09 <sup>(2)</sup> | 0.14 | 0.2 <sup>(2)</sup> | %    |  |  |

| DuCy <sub>(HSI48)</sub> | Duty cycle                                                                         |                        | 45 <sup>(2)</sup>   | -    | 55 <sup>(2)</sup>  | %    |  |  |

| ACC <sub>HSI48</sub>    | Accuracy of the HSI48<br>oscillator (factory calibrated<br>before CRS calibration) | T <sub>A</sub> = 25 °C | -4 <sup>(3)</sup>   | -    | 4 <sup>(3)</sup>   | %    |  |  |

| t <sub>su(HSI48)</sub>  | HSI48 oscillator startup time                                                      |                        | -                   | -    | 6 <sup>(2)</sup>   | μs   |  |  |

| I <sub>DDA(HSI48)</sub> | HSI48 oscillator power<br>consumption                                              |                        | -                   | 330  | 380 <sup>(2)</sup> | μA   |  |  |

1.  $V_{DDA}$  = 3.3 V,  $T_A$  = -40 to 125 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

## Low-speed internal (LSI) RC oscillator

#### Table 47. LSI oscillator characteristics

| Symbol                              | Parameter                                                               | Min | Тур | Max | Unit |

|-------------------------------------|-------------------------------------------------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(1)</sup>     | LSI frequency                                                           | 26  | 38  | 56  | kHz  |

| D <sub>LSI</sub> <sup>(2)</sup>     | LSI oscillator frequency drift $0^{\circ}C \leq T_{A} \leq 85^{\circ}C$ | -10 | -   | 4   | %    |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time                                             | -   | -   | 200 | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption                                        | -   | 400 | 510 | nA   |

1. Guaranteed by test in production.

2. This is a deviation for an individual part, once the initial frequency has been measured.

3. Guaranteed by design.

## Multi-speed internal (MSI) RC oscillator

#### Table 48. MSI oscillator characteristics

| Symbol           | Parameter                                                                                | Condition        | Тур     | Max | Unit |

|------------------|------------------------------------------------------------------------------------------|------------------|---------|-----|------|

|                  |                                                                                          | MSI range 0      | 65.5    | -   |      |

|                  |                                                                                          | MSI range 1      | 131     | -   | kHz  |

|                  |                                                                                          | MSI range 2      | 2 262 - | -   | КПИ  |

| f <sub>MSI</sub> | Frequency after factory calibration, done at $V_{DD}$ = 3.3 V and T <sub>A</sub> = 25 °C | MSI range 3      | 524     | -   |      |

|                  |                                                                                          | MSI range 4 1.05 | -       |     |      |

|                  |                                                                                          | MSI range 5      | 2.1     | -   | MHz  |

|                  |                                                                                          | MSI range 6      | 4.2     | -   |      |

## 6.3.13 I/O port characteristics

#### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 58* are derived from tests performed under the conditions summarized in *Table 24*. All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                         | Conditions                                                                                                    | Min                 | Тур                                | Max                                | Unit |  |

|------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------|------------------------------------|------|--|

| V <sub>IL</sub>  | Input low level voltage                           | TC, FT, FTf, RST<br>I/Os                                                                                      | -                   | -                                  | 0.3V <sub>DD</sub>                 |      |  |

|                  |                                                   | BOOT0 pin                                                                                                     | -                   | -                                  | 0.14V <sub>DD</sub> <sup>(1)</sup> |      |  |

| V <sub>IH</sub>  | Input high level voltage                          | All I/Os                                                                                                      | 0.7 V <sub>DD</sub> | -                                  | -                                  | V    |  |

| V                | I/O Schmitt trigger voltage hysteresis            | Standard I/Os                                                                                                 | -                   | 10% V <sub>DD</sub> <sup>(3)</sup> | -                                  |      |  |

| V <sub>hys</sub> | (2)                                               | BOOT0 pin                                                                                                     | -                   | 0.01                               | -                                  |      |  |

|                  |                                                   | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>All I/Os except for<br>PA11, PA12, BOOT0<br>and FTf I/Os | -                   | -                                  | ±50                                |      |  |

|                  |                                                   | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub> ,<br>PA11 and PA12 I/Os                                     | -                   | -                                  | -50/+250                           | nA   |  |

|                  |                                                   | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>FTf I/Os                                                 | -                   | -                                  | ±100                               |      |  |

| I <sub>lkg</sub> | Input leakage current <sup>(4)</sup>              | V <sub>DD</sub> ≤V <sub>IN</sub> ≤5 V<br>All I/Os except for<br>PA11, PA12, BOOT0<br>and FTf I/Os             | -                   | -                                  | 200                                | nA   |  |

|                  |                                                   | V <sub>DD</sub> ≤V <sub>IN</sub> ≤5 V<br>FTf I/Os                                                             | -                   | -                                  | 500                                |      |  |

|                  |                                                   | V <sub>DD</sub> ⊴V <sub>IN</sub> ⊴5 V<br>PA11, PA12 and<br>BOOT0                                              | -                   | -                                  | 10                                 | μA   |  |

| R <sub>PU</sub>  | Weak pull-up equivalent resistor <sup>(5)</sup>   | V <sub>IN</sub> = V <sub>SS</sub>                                                                             | 30                  | 45                                 | 60                                 | kΩ   |  |

| R <sub>PD</sub>  | Weak pull-down equivalent resistor <sup>(5)</sup> | $V_{IN} = V_{DD}$                                                                                             | 30                  | 45                                 | 60                                 | kΩ   |  |

| C <sub>IO</sub>  | I/O pin capacitance                               | -                                                                                                             | -                   | 5                                  | -                                  | pF   |  |

| Table 58. I/O static characteristi | cs |

|------------------------------------|----|

|------------------------------------|----|

1. Guaranteed by characterization.

2. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

3. With a minimum of 200 mV. Guaranteed by characterization results.

4. The max. value may be exceeded if negative current is injected on adjacent pins.

Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

## 6.3.17 Temperature sensor characteristics

| Calibration value name | Description                                                               | Memory address            |  |  |  |  |  |

|------------------------|---------------------------------------------------------------------------|---------------------------|--|--|--|--|--|

| TS_CAL1                | TS ADC raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3 V  | 0x1FF8 007A - 0x1FF8 007B |  |  |  |  |  |

| TS_CAL2                | TS ADC raw data acquired at temperature of 130 °C, V <sub>DDA</sub> = 3 V | 0x1FF8 007E - 0x1FF8 007F |  |  |  |  |  |

Table 66. Temperature sensor calibration values

Table 67. Temperature sensor characteristics

| Symbol                                | Parameter                                      |      | Тур  | Max       | Unit  |

|---------------------------------------|------------------------------------------------|------|------|-----------|-------|

| T <sub>L</sub> <sup>(1)</sup>         | V <sub>SENSE</sub> linearity with temperature  | -    | ±1   | <u>+2</u> | °C    |

| Avg_Slope <sup>(1)</sup>              | Average slope                                  | 1.48 | 1.61 | 1.75      | mV/°C |

| V <sub>130</sub>                      | Voltage at 130°C ±5°C <sup>(2)</sup>           | 640  | 670  | 700       | mV    |

| I <sub>DDA(TEMP)</sub> <sup>(3)</sup> | Current consumption                            | -    | 3.4  | 6         | μA    |

| t <sub>START</sub> <sup>(3)</sup>     | Startup time                                   | -    | -    | 10        |       |

| T <sub>S_temp</sub> <sup>(4)(3)</sup> | ADC sampling time when reading the temperature | 10   | -    | -         | μs    |

1. Guaranteed by characterization results.

2. Measured at V\_{DD} = 3 V  $\pm 10$  mV. V130 ADC conversion result is stored in the TS\_CAL2 byte.

3. Guaranteed by design.

4. Shortest sampling time can be determined in the application by multiple iterations.

## 6.3.18 Comparators

| Symbol                   | Parameter                                                      | Conditions | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |  |

|--------------------------|----------------------------------------------------------------|------------|--------------------|-----|--------------------|-----------|--|

| $V_{DDA}$                | Analog supply voltage                                          | -          | 1.65               |     | 3.6                | V         |  |

| R <sub>400K</sub>        | R <sub>400K</sub> value                                        | -          | -                  | 400 | -                  | kΩ        |  |

| R <sub>10K</sub>         | R <sub>10K</sub> value                                         | -          | -                  | 10  | -                  | K22       |  |

| V <sub>IN</sub>          | Comparator 1 input voltage range                               | -          | 0.6                | -   | V <sub>DDA</sub>   | V         |  |

| t <sub>START</sub>       | Comparator startup time                                        | -          | -                  | 7   | 10                 |           |  |

| td                       | Propagation delay <sup>(2)</sup>                               | -          | -                  | 3   | 10                 | μs        |  |

| Voffset                  | Comparator offset                                              | -          | -                  | ±3  | ±10                | mV        |  |

| d <sub>Voffset</sub> /dt | Comparator offset variation in worst voltage stress conditions |            | 0                  | 1.5 | 10                 | mV/1000 h |  |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                             | -          | -                  | 160 | 260                | nA        |  |

#### Table 68. Comparator 1 characteristics

1. Guaranteed by characterization.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage not included.

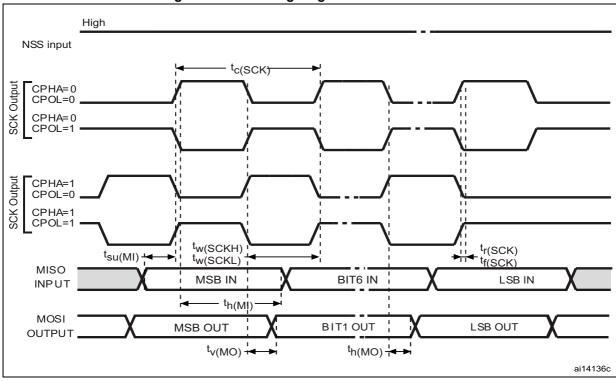

Figure 33. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

#### **I2S** characteristics

| Symbol                 | Parameter                                        | Conditions                             | Min      | Мах                   | Unit |

|------------------------|--------------------------------------------------|----------------------------------------|----------|-----------------------|------|

| f <sub>MCK</sub>       | I2S Main clock output                            | -                                      | 256 x 8K | 256xFs <sup>(2)</sup> | MHz  |

| £                      | 120 alook froguenov                              | Master data: 32 bits                   | -        | 64xFs                 | MHz  |

| f <sub>CK</sub>        | I2S clock frequency                              | Slave data: 32 bits                    | -        | 64xFs                 | MHZ  |

| D <sub>CK</sub>        | I2S clock frequency duty<br>cycle Slave receiver |                                        | 30       | 70                    | %    |

| t <sub>v(WS)</sub>     | WS valid time                                    | Master mode                            | -        | 15                    |      |

| t <sub>h(WS)</sub>     | WS hold time                                     | Master mode                            | 11       | -                     |      |

| t <sub>su(WS)</sub>    | WS setup time                                    | Slave mode                             | 6        | -                     |      |

| t <sub>h(WS)</sub>     | WS hold time                                     | Slave mode                             | 2        | -                     |      |

| t <sub>su(SD_MR)</sub> | Data input setup time                            | Master receiver                        | 0        | -                     |      |

| t <sub>su(SD_SR)</sub> | Data input setup time                            | Slave receiver                         | 6.5      | -                     | ns   |

| t <sub>h(SD_MR)</sub>  | Data input hold time                             | Master receiver                        | 18       | -                     | 115  |

| t <sub>h(SD_SR)</sub>  |                                                  | Slave receiver                         | 15.5     | -                     |      |

| $t_{v(SD\_ST)}$        | Data output valid time                           | Slave transmitter (after enable edge)  | -        | 77                    |      |

| t <sub>v(SD_MT)</sub>  |                                                  | Master transmitter (after enable edge) | -        | 8                     |      |

| t <sub>h(SD_ST)</sub>  | Data output hold time                            | Slave transmitter (after enable edge)  | 18       | -                     |      |

| t <sub>h(SD_MT)</sub>  |                                                  | Master transmitter (after enable edge) | 1.5      | -                     |      |

#### Table 76. I2S characteristics<sup>(1)</sup>

1. Guaranteed by characterization results.

2. 256xFs maximum value is equal to the maximum clock frequency.

Note: Refer to the I2S section of the product reference manual for more details about the sampling frequency (Fs),  $f_{MCK}$ ,  $f_{CK}$  and  $D_{CK}$  values. These values reflect only the digital peripheral behavior, source clock precision might slightly change them. DCK depends mainly on the ODD bit value, digital contribution leads to a min of (I2SDIV/(2\*I2SDIV+ODD) and a max of (I2SDIV+ODD)/(2\*I2SDIV+ODD). Fs max is supported for each mode/condition.

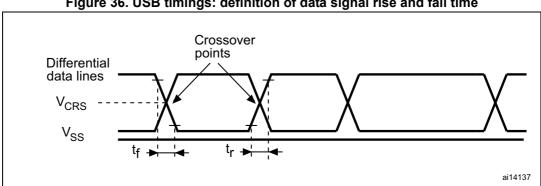

#### Figure 36. USB timings: definition of data signal rise and fall time

#### Table 79. USB: full speed electrical characteristics

| Driver characteristics <sup>(1)</sup> |                                 |                                |     |     |      |  |  |

|---------------------------------------|---------------------------------|--------------------------------|-----|-----|------|--|--|

| Symbol                                | Parameter                       | Conditions                     | Min | Max | Unit |  |  |

| t <sub>r</sub>                        | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |

| t <sub>f</sub>                        | Fall Time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |  |  |

| t <sub>rfm</sub>                      | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |  |  |

| V <sub>CRS</sub>                      | Output signal crossover voltage |                                | 1.3 | 2.0 | V    |  |  |

1. Guaranteed by design.

Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0). 2.

#### 6.3.21 LCD controller

The devices embed a built-in step-up converter to provide a constant LCD reference voltage independently from the  $V_{DD}$  voltage. An external capacitor  $C_{ext}$  must be connected to the V<sub>LCD</sub> pin to decouple this converter.

| Symbol            | Parameter                             | Min | Тур  | Max | Unit |

|-------------------|---------------------------------------|-----|------|-----|------|

| V <sub>LCD</sub>  | LCD external voltage                  | -   | -    | 3.6 |      |

| V <sub>LCD0</sub> | LCD internal reference voltage 0      | -   | 2.6  | -   |      |

| V <sub>LCD1</sub> | LCD internal reference voltage 1      | -   | 2.73 | -   |      |

| V <sub>LCD2</sub> | LCD internal reference voltage 2      | -   | 2.86 | -   |      |

| V <sub>LCD3</sub> | LCD internal reference voltage 3      | -   | 2.98 | -   | V    |

| V <sub>LCD4</sub> | LCD internal reference voltage 4      | -   | 3.12 | -   |      |

| V <sub>LCD5</sub> | LCD internal reference voltage 5      | -   | 3.26 | -   |      |

| V <sub>LCD6</sub> | LCD internal reference voltage 6      | -   | 3.4  | -   |      |

| V <sub>LCD7</sub> | LCD internal reference voltage 7      | -   | 3.55 | -   |      |

| C <sub>ext</sub>  | V <sub>LCD</sub> external capacitance | 0.1 | -    | 2   | μF   |

Table 80. LCD controller characteristics

# Table 82. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ballgrid array package mechanical data (continued)

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| F      | -           | 0.750 | -     | -                     | 0.0295 | -      |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |

| eee    | -           | -     | 0.150 | -                     | -      | 0.0059 |

| fff    | -           | -     | 0.050 | -                     | -      | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

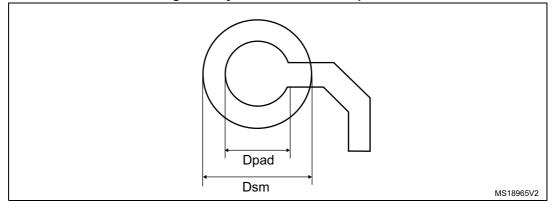

# Figure 41. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball ,grid array recommended footprint

#### Table 83. TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension    | Recommended values                                              |

|--------------|-----------------------------------------------------------------|

| Pitch        | 0.5                                                             |

| Dpad         | 0.27 mm                                                         |

| Dsm          | 0.35 mm typ. (depends on the soldermask registration tolerance) |

| Solder paste | 0.27 mm aperture diameter.                                      |

Note:Non solder mask defined (NSMD) pads are recommended.4 to 6 mils solder paste screen printing process.

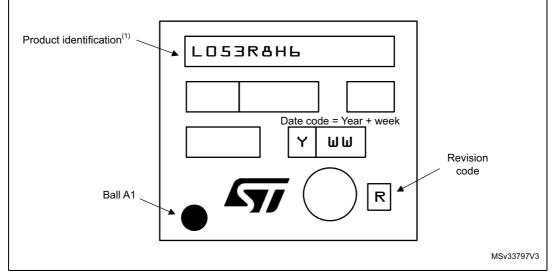

#### **Device marking for TFBGA64**

The following figure gives an example of topside marking versus ball A 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

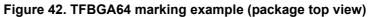

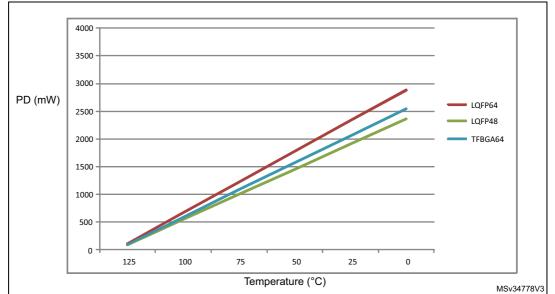

## 7.4 Thermal characteristics

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max \times \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                       | Value | Unit |

|---------------|---------------------------------------------------------------------------------|-------|------|

|               | <b>Thermal resistance junction-ambient</b><br>TFBGA64 - 5 x 5 mm / 0.5 mm pitch | 61    |      |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP64 - 10 x 10 mm / 0.5 mm pitch       | 45    | °C/W |

|               | <b>Thermal resistance junction-ambient</b><br>LQFP48 - 7 x 7 mm / 0.5 mm pitch  | 55    |      |

|  | Table | 85. | Thermal | characteristics |

|--|-------|-----|---------|-----------------|

|--|-------|-----|---------|-----------------|

#### Figure 46. Thermal resistance

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID025844 Rev 7