Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                      |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 2K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l053r8t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |            | 3.18.3                                                                                                               | Basic timer (TIM6)                                                                                                                                                                                                                                                                                                                                                                                                       | . 32                                                                                                 |

|---|------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

|   |            | 3.18.4                                                                                                               | SysTick timer                                                                                                                                                                                                                                                                                                                                                                                                            | . 32                                                                                                 |

|   |            | 3.18.5                                                                                                               | Independent watchdog (IWDG)                                                                                                                                                                                                                                                                                                                                                                                              | . 32                                                                                                 |

|   |            | 3.18.6                                                                                                               | Window watchdog (WWDG)                                                                                                                                                                                                                                                                                                                                                                                                   | . 33                                                                                                 |

|   | 3.19       | Comm                                                                                                                 | unication interfaces                                                                                                                                                                                                                                                                                                                                                                                                     | 33                                                                                                   |

|   |            | 3.19.1                                                                                                               | I2C bus                                                                                                                                                                                                                                                                                                                                                                                                                  | . 33                                                                                                 |

|   |            | 3.19.2                                                                                                               | Universal synchronous/asynchronous receiver transmitter (USART) .                                                                                                                                                                                                                                                                                                                                                        | . 34                                                                                                 |

|   |            | 3.19.3                                                                                                               | Low-power universal asynchronous receiver transmitter (LPUART)                                                                                                                                                                                                                                                                                                                                                           | . 34                                                                                                 |

|   |            | 3.19.4                                                                                                               | Serial peripheral interface (SPI)/Inter-integrated sound (I2S)                                                                                                                                                                                                                                                                                                                                                           | . 35                                                                                                 |

|   |            | 3.19.5                                                                                                               | Universal serial bus (USB)                                                                                                                                                                                                                                                                                                                                                                                               | . 36                                                                                                 |

|   | 3.20       | Clock r                                                                                                              | ecovery system (CRS)                                                                                                                                                                                                                                                                                                                                                                                                     | 36                                                                                                   |

|   | 3.21       | Cyclic ı                                                                                                             | redundancy check (CRC) calculation unit                                                                                                                                                                                                                                                                                                                                                                                  | 36                                                                                                   |

|   | 3.22       | Serial v                                                                                                             | vire debug port (SW-DP)                                                                                                                                                                                                                                                                                                                                                                                                  | 36                                                                                                   |

|   |            |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                      |

| 4 | Pin d      | lescript                                                                                                             | ions                                                                                                                                                                                                                                                                                                                                                                                                                     | 37                                                                                                   |

| _ |            |                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                      |

| 5 | Mem        | ory map                                                                                                              | oping                                                                                                                                                                                                                                                                                                                                                                                                                    | 49                                                                                                   |

| 6 | Elect      | rical ch                                                                                                             | aracteristics                                                                                                                                                                                                                                                                                                                                                                                                            | 50                                                                                                   |

|   | 6.1        | Parame                                                                                                               | eter conditions                                                                                                                                                                                                                                                                                                                                                                                                          | 50                                                                                                   |

|   |            | 6.1.1                                                                                                                | Minimum and maximum values                                                                                                                                                                                                                                                                                                                                                                                               | . 50                                                                                                 |

|   |            | 6.1.2                                                                                                                | Typical values                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                      |

|   |            | 0.1.2                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                          | . 50                                                                                                 |

|   |            | 6.1.3                                                                                                                | Typical curves                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                      |

|   |            |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                          | . 50                                                                                                 |

|   |            | 6.1.3                                                                                                                | Typical curves                                                                                                                                                                                                                                                                                                                                                                                                           | . 50<br>. 50                                                                                         |

|   |            | 6.1.3<br>6.1.4                                                                                                       | Typical curves                                                                                                                                                                                                                                                                                                                                                                                                           | . 50<br>. 50<br>. 50                                                                                 |

|   |            | 6.1.3<br>6.1.4<br>6.1.5                                                                                              | Typical curves          Loading capacitor          Pin input voltage                                                                                                                                                                                                                                                                                                                                                     | . 50<br>. 50<br>. 50<br>. 51                                                                         |

|   |            | 6.1.3<br>6.1.4<br>6.1.5<br>6.1.6                                                                                     | Typical curves         Loading capacitor         Pin input voltage         Power supply scheme                                                                                                                                                                                                                                                                                                                           | . 50<br>. 50<br>. 50<br>. 51<br>. 52                                                                 |

|   | 6.2        | <ul> <li>6.1.3</li> <li>6.1.4</li> <li>6.1.5</li> <li>6.1.6</li> <li>6.1.7</li> <li>6.1.8</li> </ul>                 | Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Optional LCD power supply scheme                                                                                                                                                                                                                                                                                  | . 50<br>. 50<br>. 50<br>. 51<br>. 52<br>. 52                                                         |

|   | 6.2<br>6.3 | 6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolu                                                         | Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Optional LCD power supply scheme         Current consumption measurement                                                                                                                                                                                                                                          | . 50<br>. 50<br>. 50<br>. 51<br>. 52<br>. 52<br>. 52                                                 |

|   |            | 6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolu                                                         | Typical curves<br>Loading capacitor<br>Pin input voltage<br>Power supply scheme<br>Optional LCD power supply scheme<br>Current consumption measurement<br>te maximum ratings                                                                                                                                                                                                                                             | . 50<br>. 50<br>. 51<br>. 52<br>. 52<br>53<br>55                                                     |

|   |            | 6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolut<br>Operat                                              | Typical curves<br>Loading capacitor<br>Pin input voltage<br>Power supply scheme<br>Optional LCD power supply scheme<br>Current consumption measurement<br>te maximum ratings<br>ing conditions                                                                                                                                                                                                                           | . 50<br>. 50<br>. 51<br>. 52<br>. 52<br>. 52<br>. 53<br>. 55                                         |

|   |            | 6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolut<br>Operat<br>6.3.1                                     | Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Optional LCD power supply scheme         Current consumption measurement         te maximum ratings         ing conditions         General operating conditions                                                                                                                                                   | . 50<br>. 50<br>. 51<br>. 52<br>. 52<br>. 53<br>. 55<br>. 55<br>. 57                                 |

|   |            | 6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolut<br>Operat<br>6.3.1<br>6.3.2                            | Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Optional LCD power supply scheme         Current consumption measurement         te maximum ratings         ing conditions         General operating conditions         Embedded reset and power control block characteristics                                                                                    | . 50<br>. 50<br>. 50<br>. 51<br>. 52<br>. 52<br>. 53<br>. 55<br>. 55<br>. 57<br>. 58                 |

|   |            | 6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolu<br>Operat<br>6.3.1<br>6.3.2<br>6.3.3                    | Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Optional LCD power supply scheme         Current consumption measurement         te maximum ratings         ing conditions         General operating conditions         Embedded reset and power control block characteristics         Embedded internal reference voltage                                        | . 50<br>. 50<br>. 51<br>. 52<br>. 52<br>. 55<br>. 55<br>. 55<br>. 57<br>. 58<br>. 59                 |

|   |            | 6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolut<br>Operat<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4          | Typical curves         Loading capacitor         Pin input voltage         Power supply scheme         Optional LCD power supply scheme         Current consumption measurement         te maximum ratings         ing conditions         General operating conditions         Embedded reset and power control block characteristics         Embedded internal reference voltage         Supply current characteristics | . 50<br>. 50<br>. 50<br>. 51<br>. 52<br>. 52<br>. 55<br>. 55<br>. 55<br>. 57<br>. 58<br>. 59<br>. 70 |

|   |            | 6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolut<br>Operat<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>6.3.5 | Typical curves<br>Loading capacitor<br>Pin input voltage<br>Power supply scheme<br>Optional LCD power supply scheme<br>Current consumption measurement<br>te maximum ratings<br>ing conditions<br>General operating conditions<br>Embedded reset and power control block characteristics<br>Embedded internal reference voltage<br>Supply current characteristics<br>Wakeup time from low-power mode                     | . 50<br>. 50<br>. 51<br>. 52<br>. 52<br>. 55<br>. 55<br>. 55<br>. 57<br>. 58<br>. 59<br>. 70<br>. 71 |

# 2.1 Device overview

| Table 1. Ultra-low-power STM32L053x6/x8 device features ar | d paripharal counts    |

|------------------------------------------------------------|------------------------|

| Table 1. Ultra-low-power STWS2L055X6/X6 device realures an | iu periprierai courits |

| Peripheral                                |                      | STM32L053C6                                                                                         | STM32L053R6                      | STM32L053C8 | STM32L053R8                      |

|-------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------|----------------------------------|-------------|----------------------------------|

| Flash (Kbytes)                            |                      | 32                                                                                                  |                                  | 64          |                                  |

| Data EEPROM (Kby                          | Data EEPROM (Kbytes) |                                                                                                     | 2                                | 2           |                                  |

| RAM (Kbytes)                              |                      | 8                                                                                                   | 8                                | 8           | 3                                |

|                                           | General-purpose      | ;                                                                                                   | 3                                | :           | 3                                |

| Timers                                    | Basic                |                                                                                                     | 1                                |             | 1                                |

|                                           | LPTIMER              |                                                                                                     | 1                                |             | 1                                |

| RTC/SYSTIC                                | K/IWDG/WWDG          | 1/1                                                                                                 | /1/1                             | 1/1         | /1/1                             |

|                                           | SPI/I2S              | 4(2)                                                                                                | <sup>(1)</sup> /1                | 4(2)        | <sup>(1)</sup> /1                |

|                                           | l <sup>2</sup> C     | :                                                                                                   | 2                                | :           | 2                                |

| Communication interfaces                  | USART                | :                                                                                                   | 2                                | :           | 2                                |

|                                           | LPUART               |                                                                                                     | 1                                |             | 1                                |

|                                           | USB/(VDD_USB)        | 1/(1)                                                                                               |                                  | 1/(1)       |                                  |

| GPIOs                                     |                      | 37                                                                                                  | 51 <sup>(2)</sup>                | 37          | 51 <sup>(2)</sup>                |

| Clocks: HSE/LSE/H                         | SI/MSI/LSI           | 1/1/1/1                                                                                             |                                  | 1/1/1/1     |                                  |

| 12-bit synchronized<br>Number of channels |                      | 1<br>10                                                                                             | 1<br>16 <sup>(2)</sup>           | 1<br>10     | 1<br>16 <sup>(2)</sup>           |

| 12-bit DAC<br>Number of channels          | 5                    | 1                                                                                                   |                                  | 1           |                                  |

| LCD<br>COM x SEG                          |                      | 1<br>4x18                                                                                           | 1<br>4x32 or 8x28 <sup>(2)</sup> | 1<br>4x18   | 1<br>4x32 or 8x28 <sup>(2)</sup> |

| Comparators                               |                      | 2                                                                                                   |                                  | 2           |                                  |

| Capacitive sensing                        | channels             | 17                                                                                                  | 24 <sup>(2)</sup>                | 17          | 24 <sup>(2)</sup>                |

| Max. CPU frequency                        |                      | 32 MHz                                                                                              |                                  |             |                                  |

| Operating voltage                         |                      | 1.8 V to 3.6 V (down to 1.65 V at power-down) with BOR option<br>1.65 V to 3.6 V without BOR option |                                  |             |                                  |

| Operating temperatures                    |                      | Ambient temperature: -40 to +125 °C<br>Junction temperature: -40 to +130 °C                         |                                  |             |                                  |

| Packages                                  |                      | LQFP48 LQFP64,<br>TFBGA64                                                                           |                                  | LQFP48      | LQFP64,<br>TFBGA64               |

1. 2 SPI interfaces are USARTs operating in SPI master mode.

2. TFBGA64 has one GPIO, one LCD COM x SEG, one ADC input and one capacitive sensing channel less than LQFP64.

### • Stop mode without RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are disabled.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 3.5  $\mu$ s, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB/USART/I2C/LPUART/LPTIMER wakeup events.

### • Standby mode with RTC

The Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSE crystal and HSI RC oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

## Standby mode without RTC

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

Note: The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode. The LCD is not stopped automatically by entering Stop mode.

|                                                | Functionalities depending on the operating power supply range |                                     |                            |                           |  |

|------------------------------------------------|---------------------------------------------------------------|-------------------------------------|----------------------------|---------------------------|--|

| Operating power<br>supply range                | DAC and ADC operation                                         | Dynamic<br>voltage scaling<br>range | I/O operation              | USB                       |  |

| V <sub>DD</sub> = 1.65 to 1.71 V               | ADC only,<br>conversion time<br>up to 570 ksps                | Range 2 or<br>range 3               | Degraded speed performance | Not functional            |  |

| V <sub>DD</sub> = 1.71 to 1.8 V <sup>(1)</sup> | ADC only,<br>conversion time<br>up to 1.14 Msps               | Range 1, range 2<br>or range 3      | Degraded speed performance | Functional <sup>(2)</sup> |  |

| $V_{DD}$ = 1.8 to 2.0 V <sup>(1)</sup>         | Conversion time<br>up to 1.14 Msps                            | Range1, range 2<br>or range 3       | Degraded speed performance | Functional <sup>(2)</sup> |  |

| V <sub>DD</sub> = 2.0 to 2.4 V                 | Conversion time<br>up to<br>1.14 Msps                         | Range 1, range 2<br>or range 3      | Full speed operation       | Functional <sup>(2)</sup> |  |

| V <sub>DD</sub> = 2.4 to 3.6 V                 | Conversion time<br>up to<br>1.14 Msps                         | Range 1, range 2<br>or range 3      | Full speed operation       | Functional <sup>(2)</sup> |  |

| Table O Free discould    |             |                 |                    |

|--------------------------|-------------|-----------------|--------------------|

| Table 2. Functionalities | aepenaing o | n the operating | power supply range |

CPU frequency changes from initial to final must respect "fcpu initial <4\*fcpu final". It must also respect 5

µs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2

MHz to 16 MHz, wait 5 µs, then switch from 16 MHz to 32 MHz.</li>

2. To be USB compliant from the I/O voltage standpoint, the minimum  $V_{\text{DD\_USB}}$  is 3.0 V.

## Table 3. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                              | Dynamic voltage scaling range |

|--------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws) | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)   | Range 2                       |

| 32 kHz to 4.2 MHz (0ws)                          | Range 3                       |

### • Startup clock

After reset, the microcontroller restarts by default with an internal 2 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

## • Clock security system (CSS)

This feature can be enabled by software. If an HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

Another clock security system can be enabled, in case of failure of the LSE it provides an interrupt or wakeup event which is generated if enabled.

## • Clock-out capability (MCO: microcontroller clock output)

It outputs one of the internal clocks for external use by the application.

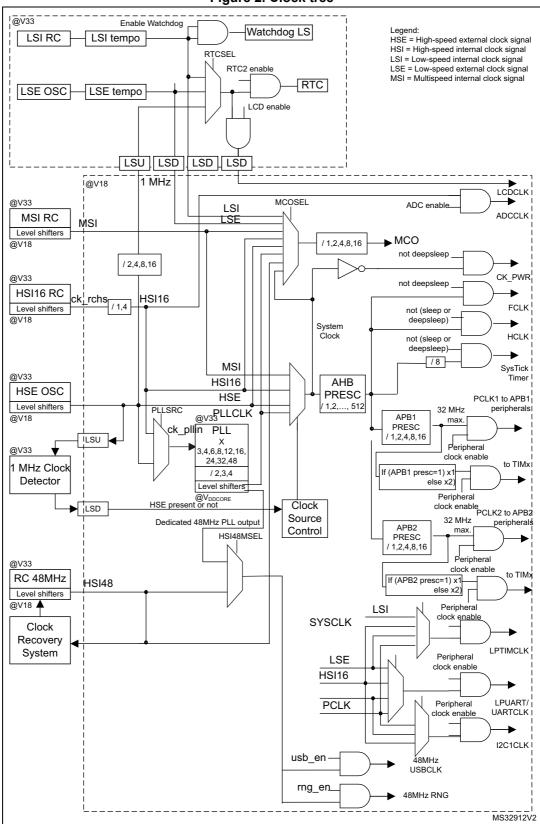

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

Figure 2. Clock tree

DocID025844 Rev 7

# 3.16 System configuration controller

The system configuration controller provides the capability to remap some alternate functions on different I/O ports.

The highly flexible routing interface allows the application firmware to control the routing of different I/Os to the TIM2, TIM21, TIM22 and LPTIM timer input captures. It also controls the routing of internal analog signals to the USB internal oscillator, ADC, COMP1 and COMP2 and the internal reference voltage  $V_{\mathsf{REFINT}}$ .

# 3.17 Touch sensing controller (TSC)

The STM32L053x6/8 provide a simple solution for adding capacitive sensing functionality to any application. These devices offer up to 24 capacitive sensing channels distributed over 8 analog I/O groups.

Capacitive sensing technology is able to detect the presence of a finger near a sensor which is protected from direct touch by a dielectric (such as glass, plastic). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle. It consists of charging the sensor capacitance and then transferring a part of the accumulated charges into a sampling capacitor until the voltage across this capacitor has reached a specific threshold. To limit the CPU bandwidth usage, this acquisition is directly managed by the hardware touch sensing controller and only requires few external components to operate.

The touch sensing controller is fully supported by the STMTouch touch sensing firmware library, which is free to use and allows touch sensing functionality to be implemented reliably in the end application.

| Group | Capacitive sensing signal name | Pin<br>name        | Group      | Capacitive sensing signal name | Pin<br>name |

|-------|--------------------------------|--------------------|------------|--------------------------------|-------------|

|       | TSC_G1_IO1                     | PA0                |            | TSC_G5_IO1                     | PB3         |

| 1     | TSC_G1_IO2                     | PA1                | 5          | TSC_G5_IO2                     | PB4         |

| 1     | TSC_G1_IO3                     | PA2                | 5          | TSC_G5_IO3                     | PB6         |

|       | TSC_G1_IO4                     | PA3                |            | TSC_G5_IO4                     | PB7         |

|       | TSC_G2_IO1                     | PA4 <sup>(1)</sup> |            | TSC_G6_IO1                     | PB11        |

| 2     | TSC_G2_IO2                     | PA5                | 6          | TSC_G6_IO2                     | PB12        |

| 2     | 2 <u> </u>                     | 0                  | TSC_G6_IO3 | PB13                           |             |

|       | TSC_G2_IO4                     | PA7                |            | TSC_G6_IO4                     | PB14        |

|       | TSC_G3_IO1                     | PC5                |            | TSC_G7_IO1                     | PC0         |

| 3     | TSC_G3_IO2                     | PB0                | 7          | TSC_G7_IO2                     | PC1         |

| 3     | TSC_G3_IO3                     | PB1                | /          | TSC_G7_IO3                     | PC2         |

|       | TSC_G3_IO4                     | PB2                |            | TSC_G7_IO4                     | PC3         |

| Table 9 Canaditive consinu  | CDIOs available on STM221 052x6/9 daviage |

|-----------------------------|-------------------------------------------|

| Table 6. Capacitive Sensing | GPIOs available on STM32L053x6/8 devices  |

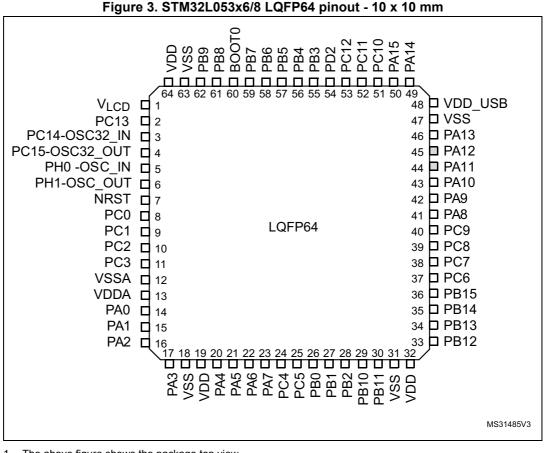

# 4 Pin descriptions

1. The above figure shows the package top view.

2. I/O pin supplied by VDD\_USB.

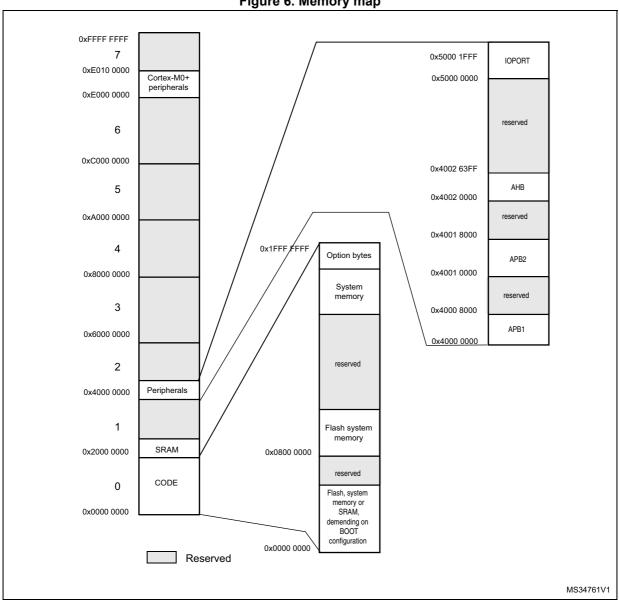

# 5 Memory mapping

Figure 6. Memory map

| Symbol                 | Ratings                                                                                          | Max.                 | Unit |

|------------------------|--------------------------------------------------------------------------------------------------|----------------------|------|

| $\Sigma I_{VDD}^{(2)}$ | Total current into sum of all $V_{DD}$ power lines (source) <sup>(1)</sup>                       | 105                  |      |

| $\Sigma I_{VSS}^{(2)}$ | Total current out of sum of all $V_{SS}$ ground lines (sink) <sup>(1)</sup>                      | 105                  |      |

| $\Sigma I_{VDD_USB}$   | Total current into V <sub>DD_USB</sub> power lines (source)                                      | 25                   |      |

| I <sub>VDD(PIN)</sub>  | Maximum current into each V <sub>DD</sub> power pin (source) <sup>(1)</sup>                      | 100                  |      |

| I <sub>VSS(PIN)</sub>  | Maximum current out of each $V_{SS}$ ground pin (sink) <sup>(1)</sup>                            | 100                  |      |

| _                      | Output current sunk by any I/O and control pin except FTf pins                                   | 16                   |      |

| Ι <sub>ΙΟ</sub>        | Output current sunk by FTf pins                                                                  | 22                   |      |

|                        | Output current sourced by any I/O and control pin                                                | -16                  | mA   |

|                        | Total output current sunk by sum of all IOs and control pins except PA11 and PA12 <sup>(2)</sup> | 90                   |      |

| ΣΙ <sub>ΙΟ(ΡΙΝ)</sub>  | Total output current sunk by PA11 and PA12                                                       | 25                   |      |

|                        | Total output current sourced by sum of all IOs and control $\ensuremath{pins}^{(2)}$             | -90                  |      |

| 1                      | Injected current on FT, FTf, RST and B pins                                                      | -5/+0 <sup>(3)</sup> |      |

| I <sub>INJ(PIN)</sub>  | Injected current on TC pin                                                                       | ± 5 <sup>(4)</sup>   |      |

| ΣΙ <sub>INJ(PIN)</sub> | Total injected current (sum of all I/O and control pins) <sup>(5)</sup>                          | ± 25                 |      |

### Table 22. Current characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

Positive current injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 21* for maximum allowed input voltage values.

A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 21: Voltage characteristics* for the maximum allowed input voltage values.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

### Table 23. Thermal characteristics

| Symbol                          | Parameter Conditions |                                           | Min  | Тур  | Max  | Unit |

|---------------------------------|----------------------|-------------------------------------------|------|------|------|------|

| V <sub>PVD6</sub> PVD threshold | DVD throshold 6      | Falling edge                              | 2.97 | 3.05 | 3.09 | V    |

|                                 |                      | Rising edge                               | 3.08 | 3.15 | 3.20 | v    |

| V <sub>hyst</sub>               |                      | BOR0 threshold                            | -    | 40   | -    |      |

|                                 | Hysteresis voltage   | All BOR and PVD thresholds excepting BOR0 | -    | 100  | -    | mV   |

Table 25. Embedded reset and power control block characteristics (continued)

1. Guaranteed by characterization results.

2. Valid for device version without BOR at power up. Please see option "D" in Ordering information scheme for more details.

# 6.3.3 Embedded internal reference voltage

The parameters given in *Table 27* are based on characterization results, unless otherwise specified.

| Table 26. Embedde | ed internal ref | ference vo | ltage o | calibration values |

|-------------------|-----------------|------------|---------|--------------------|

|                   |                 |            |         |                    |

| Calibration value name | Description                                                            | Memory address            |

|------------------------|------------------------------------------------------------------------|---------------------------|

| VREFINT_CAL            | Raw data acquired at<br>temperature of 25 °C<br>V <sub>DDA</sub> = 3 V | 0x1FF8 0078 - 0x1FF8 0079 |

| Symbol                                   | Parameter                                                                                    | Conditions                                                                              | Min   | Тур   | Max   | Unit   |

|------------------------------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|--------|

| V <sub>REFINT out</sub> <sup>(2)</sup>   | Internal reference voltage                                                                   | – 40 °C < T <sub>J</sub> < +125 °C                                                      | 1.202 | 1.224 | 1.242 | V      |

| T <sub>VREFINT</sub>                     | Internal reference startup time                                                              | -                                                                                       | -     | 2     | 3     | ms     |

| V <sub>VREF_MEAS</sub>                   | V <sub>DDA</sub> and V <sub>REF+</sub> voltage during<br>V <sub>REFINT</sub> factory measure | -                                                                                       | 2.99  | 3     | 3.01  | V      |

| A <sub>VREF_MEAS</sub>                   | Accuracy of factory-measured $V_{REFINT}$ value <sup>(3)</sup>                               | Including uncertainties<br>due to ADC and<br>V <sub>DDA</sub> /V <sub>REF+</sub> values | -     | -     | ±5    | mV     |

| T <sub>Coeff</sub> <sup>(4)</sup>        | Temperature coefficient                                                                      | –40 °C < T <sub>J</sub> < +125 °C                                                       | -     | 25    | 100   | ppm/°C |

| A <sub>Coeff</sub> <sup>(4)</sup>        | Long-term stability                                                                          | 1000 hours, T= 25 °C                                                                    | -     | -     | 1000  | ppm    |

| V <sub>DDCoeff</sub> <sup>(4)</sup>      | Voltage coefficient                                                                          | 3.0 V < V <sub>DDA</sub> < 3.6 V                                                        | -     | -     | 2000  | ppm/V  |

| T <sub>S_vrefint</sub> <sup>(4)(5)</sup> | ADC sampling time when<br>reading the internal reference<br>voltage                          | -                                                                                       | 5     | 10    | -     | μs     |

| T <sub>ADC_BUF</sub> <sup>(4)</sup>      | Startup time of reference voltage buffer for ADC                                             | -                                                                                       | -     | -     | 10    | μs     |

| I <sub>BUF_ADC</sub> <sup>(4)</sup>      | Consumption of reference voltage buffer for ADC                                              | -                                                                                       | -     | 13.5  | 25    | μA     |

| I <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output current <sup>(6)</sup>                                                       | -                                                                                       | -     | -     | 1     | μA     |

| C <sub>VREF_OUT</sub> <sup>(4)</sup>     | VREF_OUT output load                                                                         | -                                                                                       | -     | -     | 50    | pF     |

# Table 27. Embedded internal reference voltage<sup>(1)</sup>

| Symbol                                                              | Parameter                                  | Conditions                                                        |                                                    | f <sub>HCLK</sub> | Тур  | Max <sup>(1)</sup> | Unit |

|---------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------|-------------------|------|--------------------|------|

|                                                                     |                                            |                                                                   |                                                    | 1 MHz             | 165  | 230                |      |

|                                                                     |                                            |                                                                   | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0]=11   | 2 MHz             | 290  | 360                | μA   |

|                                                                     |                                            |                                                                   | 4 MHz                                              | 555               | 630  |                    |      |

|                                                                     | f <sub>HSE</sub> = f <sub>HCLK</sub> up to |                                                                   | 4 MHz                                              | 0.665             | 0.74 |                    |      |

|                                                                     |                                            | 16 MHz included,<br>f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above | Range 2, V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10, | 8 MHz             | 1.3  | 1.4                |      |

| Supply<br>I <sub>DD</sub> current in<br>(Run Run mode,<br>from code | 16 MHz (PLL ON) <sup>(2)</sup>             |                                                                   | 16 MHz                                             | 2.6               | 2.8  | mA                 |      |

|                                                                     |                                            | Range 1, V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01                 | 8 MHz                                              | 1.55              | 1.7  |                    |      |

|                                                                     |                                            |                                                                   | 16 MHz                                             | 3.1               | 3.4  |                    |      |

| Flash)                                                              | executed                                   |                                                                   |                                                    | 32 MHz            | 6.3  | 6.8                |      |

|                                                                     | from Flash                                 |                                                                   |                                                    | 65 kHz            | 36.5 | 110                |      |

|                                                                     | MSI clock                                  | Range 3, V <sub>CORE</sub> =1.2 V,<br>VOS[1:0]=11                 | 524 kHz                                            | 99.5              | 190  | μA                 |      |

|                                                                     |                                            |                                                                   | 4.2 MHz                                            | 620               | 700  |                    |      |

|                                                                     |                                            | Range 2, V <sub>CORE</sub> =1.5 V,<br>VOS[1:0]=10,                | 16 MHz                                             | 2.6               | 2.9  | mA                 |      |

|                                                                     |                                            |                                                                   | Range 1, V <sub>CORE</sub> =1.8 V,<br>VOS[1:0]=01  | 32 MHz            | 6.25 | 7                  |      |

1. Guaranteed by characterization results at 125 °C, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

| Table 29. Current consumption in Run mode vs code type, |  |

|---------------------------------------------------------|--|

| code with data processing running from Flash            |  |

| Symbol                  | Parameter                       |             | Conditions                            |           | f <sub>HCLK</sub> | Тур         | Unit     |         |     |

|-------------------------|---------------------------------|-------------|---------------------------------------|-----------|-------------------|-------------|----------|---------|-----|

|                         |                                 |             |                                       | Dhrystone |                   | 555         |          |         |     |

|                         |                                 |             |                                       | CoreMark  |                   | 585         |          |         |     |

|                         |                                 | ,           | Range 3,<br>V <sub>CORE</sub> =1.2 V, | Fibonacci | 4 MHz             | 440         | μA       |         |     |

|                         | Cumulu                          |             |                                       |           |                   | VOS[1:0]=11 | while(1) | 1 10112 | 355 |

| l <sub>DD</sub><br>(Run | (Run Run mode, 16 MHz included, |             | while(1), prefetch<br>OFF             |           | 353               |             |          |         |     |

| from<br>Flash)          |                                 |             | Dhrystone                             |           | 6.3               |             |          |         |     |

| 1 (0.511)               |                                 |             | Range 1,<br>V <sub>CORE</sub> =1.8 V, | CoreMark  | 32 MHz            | 6.3         | mA       |         |     |

|                         |                                 |             |                                       | Fibonacci |                   | 6.55        |          |         |     |

|                         |                                 | VOS[1:0]=01 | while(1)                              | -         | 5.4               |             |          |         |     |

|                         |                                 |             | while(1), prefetch<br>OFF             |           | 5.2               |             |          |         |     |

1. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

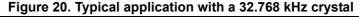

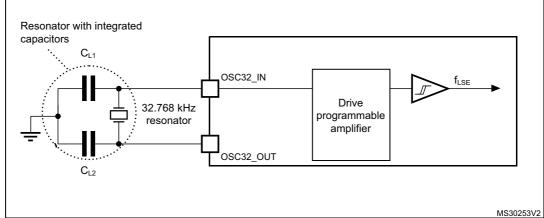

## Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 44*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                  | Parameter                                                   | Conditions <sup>(2)</sup>                          | Min <sup>(2)</sup> | Тур    | Max  | Unit   |

|-------------------------|-------------------------------------------------------------|----------------------------------------------------|--------------------|--------|------|--------|

| f <sub>LSE</sub>        | LSE oscillator frequency                                    |                                                    | -                  | 32.768 | -    | kHz    |

|                         | G <sub>m</sub> Maximum critical crystal<br>transconductance | LSEDRV[1:0]=00<br>lower driving capability         | -                  | -      | 0.5  |        |

| G <sub>m</sub>          |                                                             | LSEDRV[1:0]= 01<br>medium low driving capability   | -                  | -      | 0.75 | - μΑ/V |

|                         |                                                             | LSEDRV[1:0] = 10<br>medium high driving capability | -                  | -      | 1.7  |        |

|                         |                                                             | LSEDRV[1:0]=11<br>higher driving capability        | -                  | -      | 2.7  |        |

| $t_{\rm SU(LSE)}^{(3)}$ | Startup time                                                | V <sub>DD</sub> is stabilized                      | -                  | 2      | -    | S      |

| Table 44. LSE oscillator characteristics <sup>(1)</sup> |

|---------------------------------------------------------|

|---------------------------------------------------------|

1. Guaranteed by design.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

3. Guaranteed by characterization results. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer. To increase speed, address a lower-drive quartz with a high- driver mode.

# *Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Note:

An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

### STM32L053x6 STM32L053x8

| Symbol | Parameter                    | Conditions                                                                         | Min  | Тур  | Мах | Unit |

|--------|------------------------------|------------------------------------------------------------------------------------|------|------|-----|------|

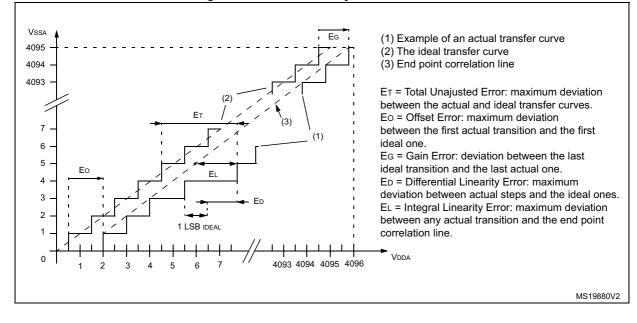

| ET     | Total unadjusted error       |                                                                                    | -    | 2    | 5   |      |

| EO     | Offset error                 |                                                                                    | -    | 1    | 2.5 |      |

| EG     | Gain error                   |                                                                                    | -    | 1    | 2   | LSB  |

| EL     | Integral linearity error     | 1.65 V < V <sub>REF+</sub> < V <sub>DDA</sub> < 3.6 V, <sup>-</sup><br>range 1/2/3 | -    | 1.5  | 3   |      |

| ED     | Differential linearity error |                                                                                    | -    | 1    | 2   |      |

| ENOB   | Effective number of bits     |                                                                                    | 10.0 | 11.0 | -   | bits |

| SINAD  | Signal-to-noise distortion   |                                                                                    | 62   | 69   | -   |      |

| SNR    | Signal-to-noise ratio        |                                                                                    | 61   | 69   | -   | dB   |

| THD    | Total harmonic distortion    |                                                                                    | -    | -85  | -65 |      |

# Table 64. ADC accuracy<sup>(1)(2)(3)</sup> (continued)

1. ADC DC accuracy values are measured after internal calibration.

ADC Accuracy vs. Negative Injection Current: Injecting negative current on any of the standard (non-robust) analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 6.3.12 does not affect the ADC accuracy.

3. Better performance may be achieved in restricted V<sub>DDA</sub>, frequency and temperature ranges.

4. This number is obtained by the test board without additional noise, resulting in non-optimized value for oversampling mode.

### Figure 26. ADC accuracy characteristics

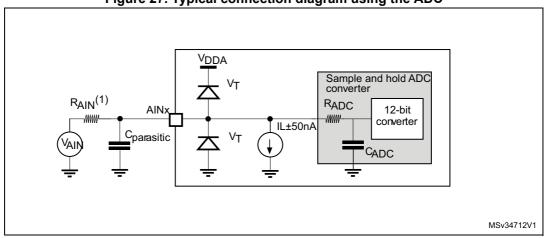

Figure 27. Typical connection diagram using the ADC

- 1. Refer to Table 62: ADC characteristics for the values of RAIN, RADC and CADC.

- C<sub>parasitic</sub> represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high C<sub>parasitic</sub> value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

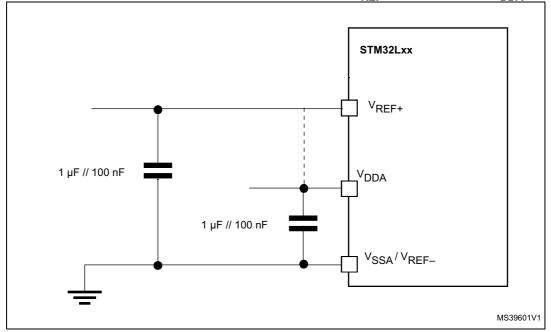

# **General PCB design guidelines**

Power supply decoupling should be performed as shown in *Figure 28* or *Figure 29*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed as close as possible to the chip.

Figure 28. Power supply and reference decoupling (V<sub>REF+</sub> not connected to V<sub>DDA</sub>)

| Symbol              | Parameter                                     | Conditions                                                                                                                                                                 | Min  | Тур | Max <sup>(1)</sup> | Unit       |

|---------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------|------------|

| V <sub>DDA</sub>    | Analog supply voltage                         | -                                                                                                                                                                          | 1.65 | -   | 3.6                | V          |

| V <sub>IN</sub>     | Comparator 2 input voltage range              | -                                                                                                                                                                          | 0    | -   | V <sub>DDA</sub>   | V          |

| +                   | Comparator startup time                       | Fast mode                                                                                                                                                                  | -    | 15  | 20                 |            |

| t <sub>start</sub>  |                                               | Slow mode                                                                                                                                                                  | -    | 20  | 25                 |            |

| +                   | Propagation delay <sup>(2)</sup> in slow mode | 1.65 V ⊴V <sub>DDA</sub> ⊴2.7 V                                                                                                                                            | -    | 1.8 | 3.5                |            |

| t <sub>d slow</sub> | Fropagation delay Air slow mode               | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                                                             | -    | 2.5 | 6                  | μs         |

| +                   | Propagation delay <sup>(2)</sup> in fast mode | 1.65 V ⊴V <sub>DDA</sub> ⊴2.7 V                                                                                                                                            | -    | 0.8 | 2                  |            |

| t <sub>d fast</sub> | riopagation delay. An last mode               | 2.7 V ≤V <sub>DDA</sub> ≤3.6 V                                                                                                                                             | -    | 1.2 | 4                  |            |

| V <sub>offset</sub> | Comparator offset error                       |                                                                                                                                                                            | -    | ±4  | <u>+</u> 20        | mV         |

| dThreshold/<br>dt   | Threshold voltage temperature coefficient     | V <sub>DDA</sub> = 3.3V, T <sub>A</sub> = 0 to 50 °C,<br>V- = V <sub>REFINT</sub> ,<br>3/4 V <sub>REFINT</sub> ,<br>1/2 V <sub>REFINT</sub> ,<br>1/4 V <sub>REFINT</sub> . | -    | 15  | 30                 | ppm<br>/°C |

|                     | Current consumption <sup>(3)</sup>            | Fast mode                                                                                                                                                                  | -    | 3.5 | 5                  |            |

| I <sub>COMP2</sub>  |                                               | Slow mode                                                                                                                                                                  | -    | 0.5 | 2                  | μA         |

Table 69. Comparator 2 characteristics

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the non-inverting input set to the reference.

3. Comparator consumption only. Internal reference voltage (required for comparator operation) is not included.

## **SPI characteristics**

Unless otherwise specified, the parameters given in the following tables are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

Refer to *Section 6.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                       | Parameter                            | Conditions                                                  | Min     | Тур   | Max               | Unit |

|----------------------------------------------|--------------------------------------|-------------------------------------------------------------|---------|-------|-------------------|------|

|                                              |                                      | Master mode                                                 |         |       | 16                |      |

|                                              |                                      | Slave mode<br>receiver                                      | -       | -     | 16                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency                  | Slave mode<br>Transmitter<br>1.71 <v<sub>DD&lt;3.6V</v<sub> | -       | -     | 12 <sup>(2)</sup> | MHz  |

|                                              |                                      | Slave mode<br>Transmitter<br>2.7 <v<sub>DD&lt;3.6V</v<sub>  | -       | -     | 16 <sup>(2)</sup> |      |

| Duty <sub>(SCK)</sub>                        | Duty cycle of SPI clock<br>frequency | Slave mode                                                  | 30      | 50    | 70                | %    |

| t <sub>su(NSS)</sub>                         | NSS setup time                       | Slave mode, SPI<br>presc = 2                                | 4*Tpclk | -     | -                 |      |

| t <sub>h(NSS)</sub>                          | NSS hold time                        | Slave mode, SPI<br>presc = 2                                | 2*Tpclk | -     | -                 |      |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time                | Master mode                                                 | Tpclk-2 | Tpclk | Tpclk+<br>2       |      |

| t <sub>su(MI)</sub>                          | Data input setup time                | Master mode                                                 | 0       | -     | -                 |      |

| t <sub>su(SI)</sub>                          |                                      | Slave mode                                                  | 3       | -     | -                 |      |

| t <sub>h(MI)</sub>                           | Data input hold time                 | Master mode                                                 | 7       | -     | -                 |      |

| t <sub>h(SI)</sub>                           |                                      | Slave mode                                                  | 3.5     | -     | -                 | ns   |

| t <sub>a(SO</sub>                            | Data output access time              | Slave mode                                                  | 15      | -     | 36                |      |

| t <sub>dis(SO)</sub>                         | Data output disable time             | Slave mode                                                  | 10      | -     | 30                |      |

| t <sub>v(SO)</sub>                           |                                      | Slave mode<br>1.65 V <v<sub>DD&lt;3.6 V</v<sub>             | -       | 18    | 41                |      |

|                                              | Data output valid time               | Slave mode<br>2.7 V <v<sub>DD&lt;3.6 V</v<sub>              | -       | 18    | 25                |      |

| t <sub>v(MO)</sub>                           |                                      | Master mode                                                 | -       | 4     | 7                 |      |

| t <sub>h(SO)</sub>                           | Data output hold time                | Slave mode                                                  | 10      | -     | -                 |      |

| t <sub>h(MO)</sub>                           |                                      | Master mode                                                 | 0       | -     | -                 |      |

| Table 73. SPI characteristics in | n voltage Range 1 <sup>(1)</sup> |

|----------------------------------|----------------------------------|

|----------------------------------|----------------------------------|

1. Guaranteed by characterization results.

2. The maximum SPI clock frequency in slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while  $Duty_{(SCK)} = 50\%$ .

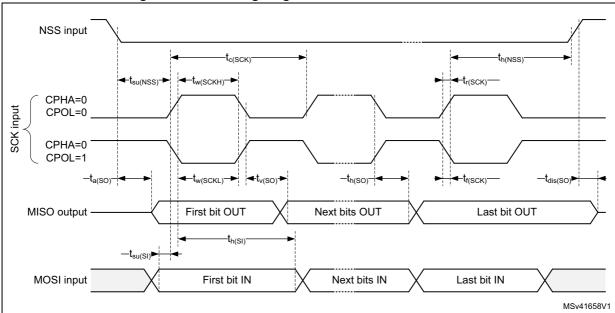

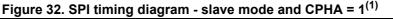

Figure 31. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}.}$

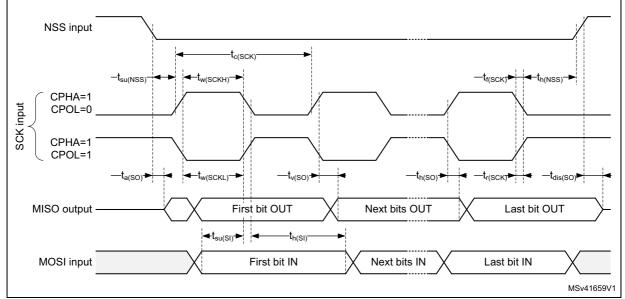

Figure 33. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

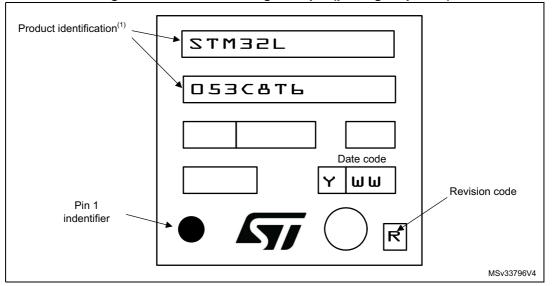

## **Device marking for LQFP48**

The following figure gives an example of topside marking versus pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.