Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M0+                                                        |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                            |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT       |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l053r8t6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 42. | TFBGA64 marking example (package top view)                            | 119 |

|------------|-----------------------------------------------------------------------|-----|

| Figure 43. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline       | 120 |

| Figure 44. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint | 121 |

| Figure 45. | LQFP48 marking example (package top view)                             | 122 |

| Figure 46. | Thermal resistance                                                    | 123 |

57

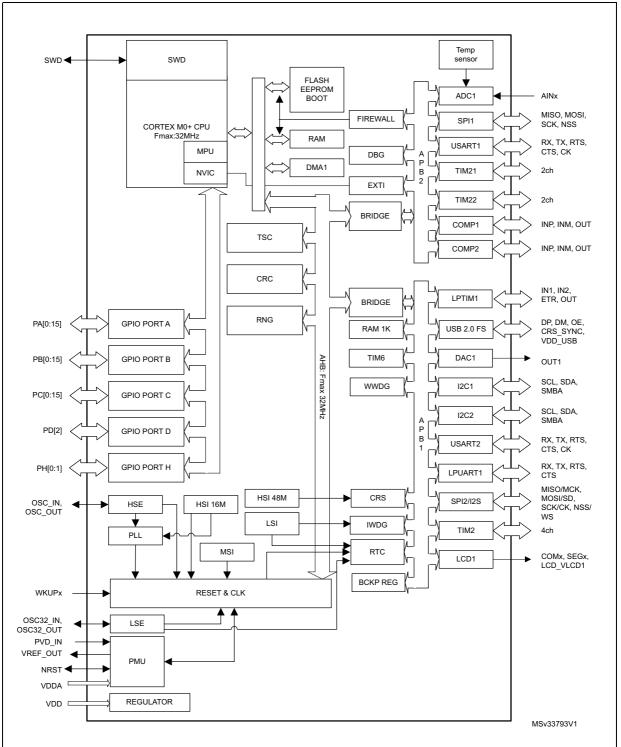

Figure 1. STM32L053x6/8 block diagram

#### • Stop mode without RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are disabled.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 3.5  $\mu$ s, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB/USART/I2C/LPUART/LPTIMER wakeup events.

#### • Standby mode with RTC

The Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSE crystal and HSI RC oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

### Standby mode without RTC

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60  $\mu$ s when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

Note: The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode. The LCD is not stopped automatically by entering Stop mode.

#### • Startup clock

After reset, the microcontroller restarts by default with an internal 2 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

### • Clock security system (CSS)

This feature can be enabled by software. If an HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled.

Another clock security system can be enabled, in case of failure of the LSE it provides an interrupt or wakeup event which is generated if enabled.

### • Clock-out capability (MCO: microcontroller clock output)

It outputs one of the internal clocks for external use by the application.

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

# 3.6 Low-power real-time clock and backup registers

The real time clock (RTC) and the 5 backup registers are supplied in all modes including standby mode. The backup registers are five 32-bit registers used to store 20 bytes of user application data. They are not reset by a system reset, or when the device wakes up from Standby mode.

The RTC is an independent BCD timer/counter. Its main features are the following:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- Automatically correction for 28, 29 (leap year), 30, and 31 day of the month

- Two programmable alarms with wake up from Stop and Standby mode capability

- Periodic wakeup from Stop and Standby with programmable resolution and period

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- 2 anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection.

The RTC clock sources can be:

- A 32.768 kHz external crystal

- A resonator or oscillator

- The internal low-power RC oscillator (typical frequency of 37 kHz)

- The high-speed external clock

# 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions, and can be individually remapped using dedicated alternate function registers. All GPIOs are high current capable. Each GPIO output, speed can be slowed (40 MHz, 10 MHz, 2 MHz, 400 kHz). The alternate function configuration of I/Os can be locked if needed following a specific sequence in order to avoid spurious writing to the I/O registers. The I/O controller is connected to a dedicated IO bus with a toggling speed of up to 32 MHz.

### Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 28 edge detector lines used to generate interrupt/event requests. Each line can be individually configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 51 GPIOs can be connected to the 16 configurable interrupt/event lines. The 12 other lines are connected to PVD, RTC, USB, USARTS, LPUART, LPTIMER or comparator events.

DocID025844 Rev 7

# 3.19.5 Universal serial bus (USB)

The STM32L053x6/8 embed a full-speed USB device peripheral compliant with the USB specification version 2.0. The internal USB PHY supports USB FS signaling, embedded DP pull-up and also battery charging detection according to Battery Charging Specification Revision 1.2. The USB interface implements a full-speed (12 Mbit/s) function interface with added support for USB 2.0 Link Power Management. It has software-configurable endpoint setting with packet memory up to 1 KB and suspend/resume support. It requires a precise 48 MHz clock which can be generated from the internal main PLL (the clock source must use a HSE crystal oscillator) or by the internal 48 MHz oscillator in automatic trimming mode. The synchronization for this oscillator can be taken from the USB data stream itself (SOF signalization) which allows crystal-less operation.

# 3.20 Clock recovery system (CRS)

The STM32L053x6/8 embed a special block which allows automatic trimming of the internal 48 MHz oscillator to guarantee its optimal accuracy over the whole device operational range. This automatic trimming is based on the external synchronization signal, which could be either derived from USB SOF signalization, from LSE oscillator, from an external signal on CRS\_SYNC pin or generated by user software. For faster lock-in during startup it is also possible to combine automatic trimming with manual trimming action.

# 3.21 Cyclic redundancy check (CRC) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at linktime and stored at a given memory location.

# 3.22 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

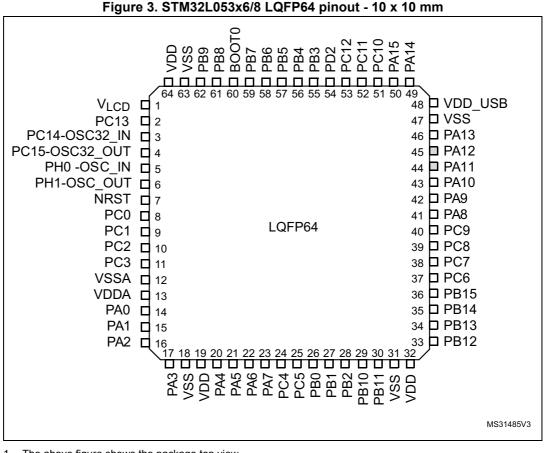

# 4 Pin descriptions

1. The above figure shows the package top view.

2. I/O pin supplied by VDD\_USB.

|   | 1                         | 2      | 3     | 4     | 5      | 6      | 7      | 8      |

|---|---------------------------|--------|-------|-------|--------|--------|--------|--------|

| А | PC14,<br>(DSC32)<br>`_!N^ | (PC13) | (PB9) | (PB4) | (PB3)  | (PA15) | (PA14) | (PA13) |

| В | PC75<br>OSC32<br>_OUT     | (VLCD) | (PB8) |       | (PD2)  | (PC11) | (PC10) | (PA12) |

| С | PHO-<br>OSC_IN            | (vss)  | (PB7) | (PB5) | (PC12) | (PA10) | (PA9)  | (PA11) |

| D |                           |        | (PB6) | (vss) | (vss)  | (vss)  | (PA8)  | (PC9)  |

| E |                           | (PC1)  | (PC0) | (VDD) | (VDD)  |        | (PC7)  | (PC8)  |

| F | (VSSA)                    | (PC2)  | (PA2) | (PA5) | (PB0)  | (PC6)  | (PB15) | (PB14) |

| G |                           | (PA0)  | (PA3) | (PA6) | (PB1)  | (PB2)  | (PB10) | (PB13) |

| Н | (VDDA)                    | (PA1)  | (PA4) | (PA7) | (PC4)  | (PC5)  | (PB11) | (PB12) |

|   |                           |        |       |       |        |        |        |        |

Figure 4. STM32L053x6/8 TFBGA64 ballout - 5x 5 mm

1. The above figure shows the package top view.

2. I/O pin supplied by VDD\_USB.

| Table 15. STM32L053x6/8 pin definitions (continued) | Table 15 | STM32L053x6/8 | pin definitions | (continued) |

|-----------------------------------------------------|----------|---------------|-----------------|-------------|

|-----------------------------------------------------|----------|---------------|-----------------|-------------|

| Pin    | num    | ber     |                                       |          |               |       |                                                                    |                      |

|--------|--------|---------|---------------------------------------|----------|---------------|-------|--------------------------------------------------------------------|----------------------|

| LQFP48 | LQFP64 | TFBGA64 | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                | Additional functions |

| -      | 37     | F6      | PC6                                   | I/O      | FT            | -     | TIM22_CH1,LCD_SEG24,<br>TSC_G8_IO1                                 | -                    |

| -      | 38     | E7      | PC7                                   | I/O      | FT            | -     | TIM22_CH2, LCD_SEG25,<br>TSC_G8_IO2                                | -                    |

| -      | 39     | E8      | PC8                                   | I/O      | FT            | -     | TIM22_ETR, LCD_SEG26,<br>TSC_G8_IO3                                | -                    |

| -      | 40     | D8      | PC9                                   | I/O      | FT            | -     | TIM21_ETR, LCD_SEG27,<br>USB_NOE, TSC_G8_IO4                       | -                    |

| 29     | 41     | D7      | PA8                                   | I/O      | FT            | -     | MCO, LCD_COM0,<br>USB_CRS_SYNC,<br>EVENTOUT, USART1_CK             | -                    |

| 30     | 42     | C7      | PA9                                   | I/O      | FT            | -     | MCO, LCD_COM1,<br>TSC_G4_IO1,<br>USART1_TX                         | -                    |

| 31     | 43     | C6      | PA10                                  | I/O      | FT            | -     | LCD_COM2,<br>TSC_G4_IO2,<br>USART1_RX                              | -                    |

| 32     | 44     | C8      | PA11                                  | I/O      | FT            | (2)   | SPI1_MISO, EVENTOUT,<br>TSC_G4_IO3,<br>USART1_CTS,<br>COMP1_OUT    | USB_DM               |

| 33     | 45     | B8      | PA12                                  | I/O      | FT            | (2)   | SPI1_MOSI, EVENTOUT,<br>TSC_G4_IO4,<br>USART1_RTS_DE,<br>COMP2_OUT | USB_DP               |

| 34     | 46     | A8      | PA13                                  | I/O      | FT            | -     | SWDIO, USB_NOE                                                     | -                    |

| 35     | 47     | D5      | VSS                                   | S        |               | -     | -                                                                  | -                    |

| 36     | 48     | E6      | VDD_USB                               | S        |               | -     | -                                                                  | -                    |

| 37     | 49     | A7      | PA14                                  | I/O      | FT            | -     | SWCLK, USART2_TX                                                   | -                    |

| 38     | 50     | A6      | PA15                                  | I/O      | FT            | -     | SPI1_NSS, LCD_SEG17,<br>TIM2_ETR, EVENTOUT,<br>USART2_RX, TIM2_CH1 | -                    |

| -      | 51     | B7      | PC10                                  | I/O      | FT            | -     | LPUART1_TX,<br>LCD_COM4/LCD_SEG28/<br>LCD_SEG40                    | -                    |

DocID025844 Rev 7

| ۰<br>۱ |                 |   | I                                       | Table 18. Alternate function p | ort C                                  |            |

|--------|-----------------|---|-----------------------------------------|--------------------------------|----------------------------------------|------------|

|        |                 |   | AF0                                     | AF1                            | AF2                                    | AF3        |

|        | Port            |   | PUART1/LPTIM/<br>TIM21/12/<br>EVENTOUT/ | LCD                            | SPI2/I2S2/USB/<br>LPUART1/<br>EVENTOUT | TSC        |

|        | PC              | C | LPTIM1_IN1                              | LCD_SEG18                      | EVENTOUT                               | TSC_G7_IO1 |

|        | PC              | 1 | LPTIM1_OUT                              | LCD_SEG19                      | EVENTOUT                               | TSC_G7_IO2 |

|        | PC              | 2 | LPTIM1_IN2                              | LCD_SEG20                      | SPI2_MISO/I2S2_MCK                     | TSC_G7_IO3 |

|        | PC              | 3 | LPTIM1_ETR                              | LCD_SEG21                      | SPI2_MOSI/I2S2_SD                      | TSC_G7_IO4 |

|        | PC              | 4 | EVENTOUT                                | LCD_SEG22                      | LPUART1_TX                             | -          |

|        | PC              | 5 | -                                       | LCD_SEG23                      | LPUART1_RX                             | TSC_G3_IO1 |

|        | PC              | 6 | TIM22_CH1                               | LCD_SEG24                      | -                                      | TSC_G8_IO1 |

| Port   | PC              | 7 | TIM22_CH2                               | LCD_SEG25                      | -                                      | TSC_G8_IO2 |

| POIL   | PC              | 8 | TIM22_ETR                               | LCD_SEG26                      | -                                      | TSC_G8_IO3 |

|        | PC              | 9 | TIM21_ETR                               | LCD_SEG27                      | USB_NOE                                | TSC_G8_IO4 |

|        | PC              | 0 | LPUART1_TX                              | LCD_COM4/LCD_SEG28             | -                                      | -          |

|        | PC <sup>2</sup> | 1 | LPUART1_RX                              | LCD_COM5/LCD_SEG29             | -                                      | -          |

|        | PC              | 2 | -                                       | LCD_COM6/LCD_SEG30             | -                                      | -          |

|        | PC              | 3 | -                                       | -                              | -                                      | -          |

|        | PC              | 4 | -                                       | -                              | -                                      | -          |

|        | PC              | 5 | -                                       | -                              | -                                      | -          |

Table 19. Alternate function port D

| Port   |     | AF0            | AF1                |

|--------|-----|----------------|--------------------|

| F      | on  | LPUART1        | LCD                |

| Port D | PD2 | LPUART1_RTS_DE | LCD_COM7/LCD_SEG31 |

|        |     |                |                    |

STM32L053x6 STM32L053x8

|  | Table 20. Alternate function port H |     |              |  |     |  |  |

|--|-------------------------------------|-----|--------------|--|-----|--|--|

|  | Port                                |     | Port         |  | AF0 |  |  |

|  |                                     |     | USB          |  |     |  |  |

|  | Port H                              | PH0 | USB_CRS_SYNC |  |     |  |  |

|  | FUILE                               | PH1 | _            |  |     |  |  |

STM32L053x6 STM32L053x8

# 6 Electrical characteristics

# 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_Amax$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

### 6.1.2 Typical values

Unless otherwise specified, typical data are based on T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.6 V (for the 1.65 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

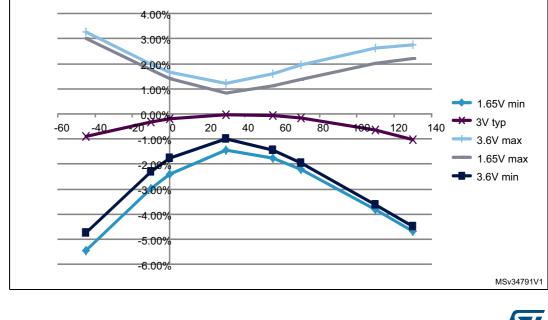

### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

### 6.1.4 Loading capacitor

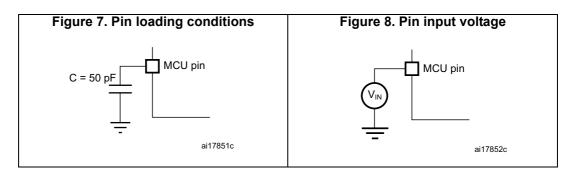

The loading conditions used for pin parameter measurement are shown in *Figure 7*.

### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 8.

| Symbol                                  | Parameter                                                           | Conditions | Min | Тур | Max  | Unit                     |

|-----------------------------------------|---------------------------------------------------------------------|------------|-----|-----|------|--------------------------|

| I <sub>LPBUF</sub> <sup>(4)</sup>       | Consumption of reference<br>voltage buffer for VREF_OUT<br>and COMP | -          | -   | 730 | 1200 | nA                       |

| V <sub>REFINT_DIV1</sub> <sup>(4)</sup> | 1/4 reference voltage                                               | -          | 24  | 25  | 26   |                          |

| V <sub>REFINT_DIV2</sub> <sup>(4)</sup> | 1/2 reference voltage                                               | -          | 49  | 50  | 51   | %<br>V <sub>REFINT</sub> |

| V <sub>REFINT_DIV3</sub> <sup>(4)</sup> | 3/4 reference voltage                                               | -          | 74  | 75  | 76   |                          |

Table 27. Embedded internal reference voltage<sup>(1)</sup> (continued)

1. Refer to *Table 39: Peripheral current consumption in Stop and Standby mode* for the value of the internal reference current consumption (I<sub>REFINT</sub>).

2. Guaranteed by test in production.

3. The internal V<sub>REF</sub> value is individually measured in production and stored in dedicated EEPROM bytes.

4. Guaranteed by design.

5. Shortest sampling time can be determined in the application by multiple iterations.

6. To guarantee less than 1% VREF\_OUT deviation.

## 6.3.4 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code. The current consumption is measured as described in *Figure 11: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code if not specified otherwise.

The current consumption values are derived from the tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24: General operating conditions* unless otherwise specified.

The MCU is placed under the following conditions:

- All I/O pins are configured in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time and prefetch is adjusted depending on fHCLK frequency and voltage range to provide the best CPU performance unless otherwise specified.

- When the peripherals are enabled  $f_{APB1} = f_{APB2} = f_{APB}$

- When PLL is ON, the PLL inputs are equal to HSI = 16 MHz (if internal clock is used) or HSE = 16 MHz (if HSE bypass mode is used)

- The HSE user clock applied to OSCI\_IN input follows the characteristic specified in *Table 41: High-speed external user clock characteristics*

- For maximum current consumption  $V_{DD} = V_{DDA} = 3.6$  V is applied to all supply pins

- For typical current consumption  $V_{DD} = V_{DDA} = 3.0$  V is applied to all supply pins if not specified otherwise

The parameters given in *Table 49*, *Table 24* and *Table 25* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

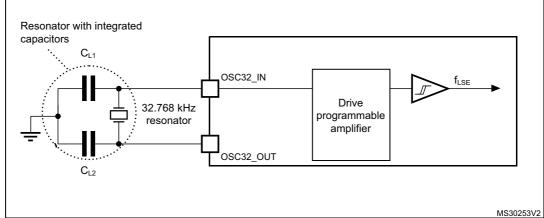

### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 44*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                  | Parameter                                    | Conditions <sup>(2)</sup>                          | Min <sup>(2)</sup> | Тур    | Max  | Unit |  |

|-------------------------|----------------------------------------------|----------------------------------------------------|--------------------|--------|------|------|--|

| f <sub>LSE</sub>        | LSE oscillator frequency                     |                                                    | -                  | 32.768 | -    | kHz  |  |

| ( -                     |                                              | LSEDRV[1:0]=00<br>lower driving capability         | -                  | -      | 0.5  |      |  |

|                         | Maximum critical crystal<br>transconductance | LSEDRV[1:0]= 01<br>medium low driving capability   | -                  | -      | 0.75 |      |  |

|                         |                                              | LSEDRV[1:0] = 10<br>medium high driving capability | -                  | -      | 1.7  | μΑ/V |  |

|                         |                                              | LSEDRV[1:0]=11<br>higher driving capability        | -                  | -      | 2.7  |      |  |

| $t_{\rm SU(LSE)}^{(3)}$ | Startup time                                 | V <sub>DD</sub> is stabilized                      | -                  | 2      | -    | S    |  |

| Table 44. LSE oscillator characteristics <sup>(1)</sup> |

|---------------------------------------------------------|

|---------------------------------------------------------|

1. Guaranteed by design.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

3. Guaranteed by characterization results. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer. To increase speed, address a lower-drive quartz with a high- driver mode.

# *Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Note:

An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

### 6.3.7 Internal clock source characteristics

The parameters given in *Table 45* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

### High-speed internal 16 MHz (HSI16) RC oscillator

| Symbol                                | Parameter                                           | Conditions                                                            | Min               | Тур  | Max              | Unit |

|---------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------|-------------------|------|------------------|------|

| f <sub>HSI16</sub>                    | Frequency                                           | V <sub>DD</sub> = 3.0 V                                               | -                 | 16   | -                | MHz  |

| TRIM <sup>(1)(2)</sup>                | HSI16 user-                                         | Trimming code is not a multiple of 16                                 | -                 | ±0.4 | 0.7              | %    |

| TRIM                                  | trimmed resolution                                  | Trimming code is a multiple of 16                                     | -                 | -    | ±1.5             | %    |

|                                       |                                                     | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = 25 °C                      | -1 <sup>(3)</sup> | -    | 1 <sup>(3)</sup> | %    |

| 400                                   | Accuracy of the factory-calibrated HSI16 oscillator | $V_{DDA}$ = 3.0 V, $T_A$ = 0 to 55 °C                                 | -1.5              | -    | 1.5              | %    |

|                                       |                                                     | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 70 °C                               | -2                | -    | 2                | %    |

| ACC <sub>HSI16</sub>                  |                                                     | $V_{DDA}$ = 3.0 V, $T_A$ = -10 to 85 °C                               | -2.5              | -    | 2                | %    |

|                                       |                                                     | V <sub>DDA</sub> = 3.0 V, T <sub>A</sub> = -10 to 105 °C              | -4                | -    | 2                | %    |

|                                       |                                                     | V <sub>DDA</sub> = 1.65 V to 3.6 V<br>T <sub>A</sub> = - 40 to 125 °C | -5.45             | -    | 3.25             | %    |

| t <sub>SU(HSI16)</sub> <sup>(2)</sup> | HSI16 oscillator<br>startup time                    | -                                                                     | -                 | 3.7  | 6                | μs   |

| I <sub>DD(HSI16)</sub> <sup>(2)</sup> | HSI16 oscillator<br>power consumption               | -                                                                     | -                 | 100  | 140              | μA   |

#### Table 45. 16 MHz HSI16 oscillator characteristics

1. The trimming step differs depending on the trimming code. It is usually negative on the codes which are multiples of 16 (0x00, 0x10, 0x20, 0x30...0xE0).

2. Guaranteed by characterization results.

3. Guaranteed by test in production.

### Figure 21. HSI16 minimum and maximum value versus temperature

DocID025844 Rev 7

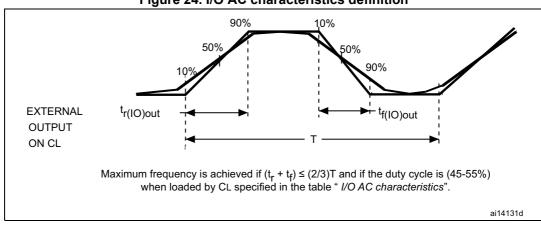

### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 24* and *Table 60*, respectively.

Unless otherwise specified, the parameters given in *Table 60* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

| OSPEEDRx[1:0]<br>bit value <sup>(1)</sup> | Symbol                  | Parameter                                                              | Conditions                                                |     | Max <sup>(2)</sup> | Unit  |  |

|-------------------------------------------|-------------------------|------------------------------------------------------------------------|-----------------------------------------------------------|-----|--------------------|-------|--|

| 00                                        | f                       | Maximum frequency <sup>(3)</sup>                                       | $C_L$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                  | -   | 400                | - kHz |  |

|                                           | f <sub>max(IO)out</sub> |                                                                        | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               | -   | 100                | KIIZ  |  |

|                                           | t <sub>f(IO)out</sub>   | Output rise and fall time                                              | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                | -   | 125                | ns    |  |

|                                           | t <sub>r(IO)out</sub>   |                                                                        | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               | -   | 320                | 115   |  |

|                                           | £                       | Maximum frequency <sup>(3)</sup>                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                | -   | 2                  | - MHz |  |

| 01                                        | f <sub>max(IO)out</sub> |                                                                        | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               | -   | 0.6                |       |  |

| 01                                        | t <sub>f(IO)out</sub>   |                                                                        | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                | -   | 30                 | - ns  |  |

|                                           | t <sub>r(IO)out</sub>   | Output rise and fall time                                              | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               | -   | 65                 |       |  |

| 10                                        | E                       | Maximum frequency <sup>(3)</sup>                                       | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                | -   | 10                 | MHz   |  |

|                                           | F <sub>max(IO)out</sub> |                                                                        | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               | -   | 2                  |       |  |

|                                           | t <sub>f(IO)out</sub>   | Output rise and fall time                                              | $C_{L}$ = 50 pF, $V_{DD}$ = 2.7 V to 3.6 V                | -   | 13                 |       |  |

|                                           | t <sub>r(IO)out</sub>   |                                                                        | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               | -   | 28                 | ns    |  |

|                                           | F <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                       | $C_{L}$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                | -   | 35                 | MHz   |  |

| 11                                        |                         |                                                                        | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               | -   | 10                 |       |  |

|                                           | t <sub>f(IO)out</sub>   | Output rise and fall time                                              | $C_{L}$ = 30 pF, $V_{DD}$ = 2.7 V to 3.6 V                | -   | 6                  |       |  |

|                                           | t <sub>r(IO)out</sub>   | Output rise and fall time                                              | $C_{L}$ = 50 pF, $V_{DD}$ = 1.65 V to 2.7 V               | / - | 17                 | ns    |  |

|                                           | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                       |                                                           | -   | 1                  | MHz   |  |

| Fm+<br>configuration <sup>(4)</sup>       | t <sub>f(IO)out</sub>   | Output fall time $C_L = 50 \text{ pF}, V_{DD} = 2.5 \text{ V to } 3.6$ |                                                           | -   | 10                 |       |  |

|                                           | t <sub>r(IO)out</sub>   | Output rise time                                                       |                                                           | -   | 30                 | ns    |  |

|                                           | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup>                                       |                                                           |     | 350                | KHz   |  |

|                                           | t <sub>f(IO)out</sub>   | Output fall time                                                       | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.65 V to 3.6 V | -   | 15                 |       |  |

|                                           | t <sub>r(IO)out</sub>   | Output rise time                                                       |                                                           | -   | 60                 | ns    |  |

| -                                         | t <sub>EXTIpw</sub>     | Pulse width of external<br>signals detected by the<br>EXTI controller  | -                                                         | 8   | -                  | ns    |  |

Table 60. I/O AC characteristics<sup>(1)</sup>

1. The I/O speed is configured using the OSPEEDRx[1:0] bits. Refer to the line reference manual for a description of GPIO Port configuration register.

2. Guaranteed by design.

3. The maximum frequency is defined in *Figure* 24.

4. When Fm+ configuration is set, the I/O speed control is bypassed. Refer to the line reference manual for a detailed description of Fm+ I/O configuration.

### 6.3.14 NRST pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$ , except when it is internally driven low (see *Table 61*).

Unless otherwise specified, the parameters given in *Table 61* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 24*.

| Symbol                                | Parameter                                       | Conditions                                                   | Min      | Тур                               | Max      | Unit |

|---------------------------------------|-------------------------------------------------|--------------------------------------------------------------|----------|-----------------------------------|----------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup>  | NRST input low level voltage                    | -                                                            | $V_{SS}$ | -                                 | 0.8      |      |

| V <sub>IH(NRST)</sub> <sup>(1)</sup>  | NRST input high level voltage                   | -                                                            | 1.4      | -                                 | $V_{DD}$ |      |

| V <sub>OL(NRST)</sub> <sup>(1)</sup>  | NRST output low level                           | I <sub>OL</sub> = 2 mA<br>2.7 V < V <sub>DD</sub> < 3.6 V    | -        | - 0.4                             |          | V    |

|                                       | voltage                                         | I <sub>OL</sub> = 1.5 mA<br>1.65 V < V <sub>DD</sub> < 2.7 V | -        | -                                 | 0.7      |      |

| V <sub>hys(NRST)</sub> <sup>(1)</sup> | NRST Schmitt trigger voltage<br>hysteresis      | -                                                            | -        | 10%V <sub>DD</sub> <sup>(2)</sup> | -        | mV   |

| R <sub>PU</sub>                       | Weak pull-up equivalent resistor <sup>(3)</sup> | $V_{IN} = V_{SS}$                                            | 30       | 45                                | 60       | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>   | NRST input filtered pulse                       | -                                                            | -        | -                                 | 50       | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup>  | NRST input not filtered pulse                   | -                                                            | 350      | -                                 | -        | ns   |

Table 61. NRST pin characteristics

1. Guaranteed by design.

2. 200 mV minimum value

3. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is around 10%.

| Symbol                                | Parameter                          | Conditions                                      | Min                                                                        | Тур | Max                                               | Unit                       |

|---------------------------------------|------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------|-----|---------------------------------------------------|----------------------------|

| C <sub>ADC</sub> <sup>(3)</sup>       | Internal sample and hold capacitor | -                                               | -                                                                          | -   | 8                                                 | pF                         |

| t <sub>CAL</sub> <sup>(3)(5)</sup>    | Calibration time                   | f <sub>ADC</sub> = 16 MHz                       | 5.2                                                                        |     |                                                   | μs                         |

|                                       |                                    | -                                               | 83                                                                         |     |                                                   | 1/f <sub>ADC</sub>         |

| W <sub>LATENCY</sub> <sup>(6)</sup>   |                                    | ADC clock = HSI16                               | 1.5 ADC<br>cycles + 2<br>f <sub>PCLK</sub> cycles                          | -   | 1.5 ADC<br>cycles + 3<br>f <sub>PCLK</sub> cycles | -                          |

|                                       | ADC_DR register write<br>latency   | ADC clock = PCLK/2                              | -                                                                          | 4.5 | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                       |                                    | ADC clock = PCLK/4                              | -                                                                          | 8.5 | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                       | Trigger conversion latency         | $f_{ADC} = f_{PCLK}/2 = 16 \text{ MHz}$         | 0.266                                                                      |     |                                                   | μs                         |

|                                       |                                    | $f_{ADC} = f_{PCLK}/2$                          | 8.5                                                                        |     |                                                   | 1/f <sub>PCLK</sub>        |

| t <sub>latr</sub> <sup>(3)</sup>      |                                    | $f_{ADC} = f_{PCLK}/4 = 8 \text{ MHz}$          | 0.516                                                                      |     |                                                   | μs                         |

|                                       |                                    | $f_{ADC} = f_{PCLK}/4$                          | 16.5                                                                       |     | 1/f <sub>PCLK</sub>                               |                            |

|                                       |                                    | f <sub>ADC</sub> = f <sub>HSI16</sub> = 16 MHz  | 0.252                                                                      | -   | 0.260                                             | μs                         |

| Jitter <sub>ADC</sub>                 | ADC jitter on trigger conversion   | f <sub>ADC</sub> = f <sub>HSI16</sub>           | -                                                                          | 1   | -                                                 | 1/f <sub>HSI16</sub>       |

| $t_{S}^{(3)}$                         | Sampling time                      | f <sub>ADC</sub> = 16 MHz                       | 0.093                                                                      | -   | 10.03                                             | μs                         |

|                                       |                                    | -                                               | 1.5                                                                        | -   | 160.5                                             | 1/f <sub>ADC</sub>         |

| t <sub>UP_LDO</sub> <sup>(3)(5)</sup> | Internal LDO power-up time         | -                                               | -                                                                          | -   | 10                                                | μs                         |

| t <sub>STAB</sub> <sup>(3)(5)</sup>   | ADC stabilization time             | -                                               | 14                                                                         |     | 1/f <sub>ADC</sub>                                |                            |

| t <sub>ConV</sub> <sup>(3)</sup>      | Total conversion time              | f <sub>ADC</sub> = 16 MHz,<br>12-bit resolution | 0.875                                                                      | -   | 10.81                                             | μs                         |

|                                       | (including sampling time)          | 12-bit resolution                               | 14 to 173 (t <sub>S</sub> for sampling +12.5 for successive approximation) |     |                                                   | 1/f <sub>ADC</sub>         |

1. V<sub>DDA</sub> minimum value can be decreased in specific temperature conditions. Refer to Table 63: RAIN max for fADC = 16 MHz.

2. A current consumption proportional to the APB clock frequency has to be added (see *Table 38: Peripheral current consumption in Run or Sleep mode*).

3. Guaranteed by design.

4. Standard channels have an extra protection resistance which depends on supply voltage. Refer to *Table 63: RAIN max for fADC = 16 MHz*.

5. This parameter only includes the ADC timing. It does not take into account register access latency.

6. This parameter specifies the latency to transfer the conversion result into the ADC\_DR register. EOC bit is set to indicate the conversion is complete and has the same latency.

| Symbol                           | Parameter                                                | Min                      | Тур                  | Мах       | Unit |

|----------------------------------|----------------------------------------------------------|--------------------------|----------------------|-----------|------|

| I <sub>LCD</sub> <sup>(1)</sup>  | Supply current at $V_{DD}$ = 2.2 V                       | -                        | 3.3                  | -         |      |

|                                  | Supply current at V <sub>DD</sub> = 3.0 V                | -                        | 3.1                  | -         | μA   |

| R <sub>Htot</sub> <sup>(2)</sup> | Low drive resistive network overall value                | 5.28                     | 6.6                  | 7.92      | MΩ   |

| R <sub>L</sub> <sup>(2)</sup>    | High drive resistive network total value                 |                          | 240                  | 288       | kΩ   |

| V <sub>44</sub>                  | Segment/Common highest level voltage                     | -                        | -                    | $V_{LCD}$ | V    |

| V <sub>34</sub>                  | Segment/Common 3/4 level voltage                         | -                        | 3/4 V <sub>LCD</sub> | -         |      |

| V <sub>23</sub>                  | Segment/Common 2/3 level voltage                         | -                        | 2/3 V <sub>LCD</sub> | -         |      |

| V <sub>12</sub>                  | Segment/Common 1/2 level voltage                         | -                        | 1/2 V <sub>LCD</sub> | -         | v    |

| V <sub>13</sub>                  | Segment/Common 1/3 level voltage                         | -                        | 1/3 V <sub>LCD</sub> | -         | v    |

| V <sub>14</sub>                  | Segment/Common 1/4 level voltage                         | - 1/4 V <sub>LCD</sub> - |                      |           |      |

| V <sub>0</sub>                   | Segment/Common lowest level voltage                      | 0                        | -                    | -         |      |

| ΔVxx <sup>(3)</sup>              | Segment/Common level voltage error $T_A$ = -40 to 85 ° C | -                        | -                    | ±50       | mV   |

| Table 80, LCD | controller  | characteristics | (continued) |

|---------------|-------------|-----------------|-------------|

|               | 00110101101 | onunuotoristios | (continued) |

LCD enabled with 3 V internal step-up active, 1/8 duty, 1/4 bias, division ratio= 64, all pixels active, no LCD connected.

2. Guaranteed by design.

3. Guaranteed by characterization results.

# 7.4.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.