Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betalls                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

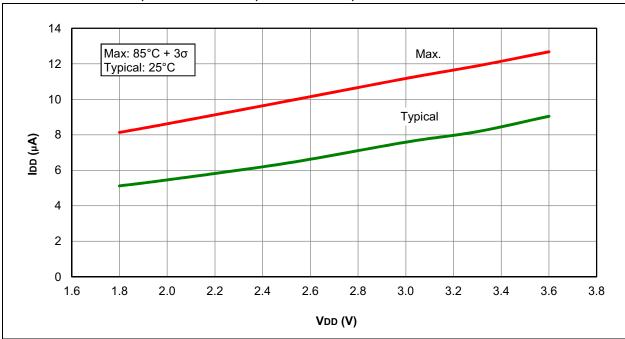

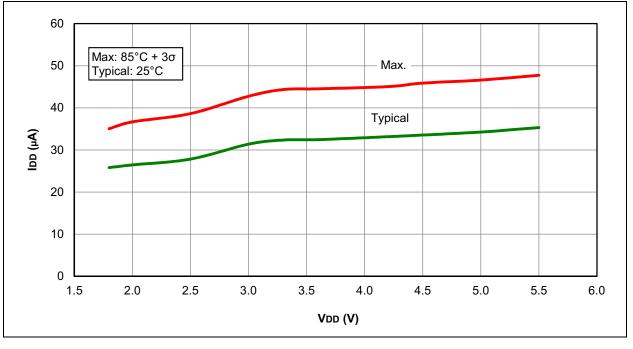

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1938-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.0 ENHANCED MID-RANGE CPU

This family of devices contain an enhanced mid-range 8-bit CPU core. The CPU has 49 instructions. Interrupt capability includes automatic context saving. The hardware stack is 16 levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

- · Automatic Interrupt Context Saving

- 16-level Stack with Overflow and Underflow

- File Select Registers

- Instruction Set

#### 2.1 Automatic Interrupt Context Saving

During interrupts, certain registers are automatically saved in shadow registers and restored when returning from the interrupt. This saves stack space and user code. See **Section 7.5 "Automatic Context Saving"**, for more information.

#### 2.2 16-Level Stack with Overflow and Underflow

These devices have a hardware stack memory 15 bits wide and 16 words deep. A Stack Overflow or Underflow will set the appropriate bit (STKOVF or STKUNF) in the PCON register, and if enabled will cause a software Reset. See section **Section 3.5 "Stack**" for more details.

#### 2.3 File Select Registers

There are two 16-bit File Select Registers (FSR). FSRs can access all file registers and program memory, which allows one Data Pointer for all memory. When an FSR points to program memory, there is one additional instruction cycle in instructions using INDF to allow the data to be fetched. General purpose memory can now also be addressed linearly, providing the ability to access contiguous data larger than 80 bytes. There are also new instructions to support the FSRs. See **Section 3.6 "Indirect Addressing"** for more details.

#### 2.4 Instruction Set

There are 49 instructions for the enhanced mid-range CPU to support the features of the CPU. See **Section 29.0 "Instruction Set Summary"** for more details.

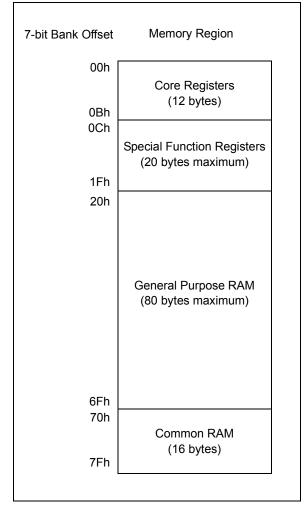

#### 3.3.1 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 3.3.2 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank.

#### 3.3.2.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See Section 3.6.2 "Linear Data Memory" for more information.

#### 3.3.3 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### FIGURE 3-2: BANKED MEMORY PARTITIONING

#### 3.3.4 DEVICE MEMORY MAPS

The memory maps for the device family are as shown in Table 3-2.

#### TABLE 3-2: MEMORY MAP TABLES

| Device      | Banks | Table No.            |

|-------------|-------|----------------------|

| PIC16F1938  | 0-7   | Table 3-3            |

| PIC16LF1938 | 8-15  | Table 3-4, Table 3-7 |

|             | 16-23 | Table 3-5            |

|             | 23-31 | Table 3-6, Table 3-9 |

| PIC16F1939  | 0-7   | Table 3-3            |

| PIC16LF1939 | 8-15  | Table 3-4, Table 3-8 |

|             | 16-23 | Table 3-5            |

|             | 23-31 | Table 3-6, Table 3-9 |

| Address                | Name       | Bit 7                         | Bit 6                       | Bit 5          | Bit 4           | Bit 3        | Bit 2                 | Bit 1     | Bit 0                 | Valu<br>POR, |      | oti  | on all<br>her<br>sets |

|------------------------|------------|-------------------------------|-----------------------------|----------------|-----------------|--------------|-----------------------|-----------|-----------------------|--------------|------|------|-----------------------|

| Bank 1                 |            |                               |                             |                |                 |              |                       |           |                       |              |      |      |                       |

| 080h <sup>(2)</sup>    | INDF0      |                               | this location cal register) | uses contents  | s of FSR0H/F    | SR0L to addr | ess data me           | mory      |                       | XXXX         | XXXX | XXXX | XXXX                  |

| 081h <sup>(2)</sup>    | INDF1      |                               | this location cal register) | uses contents  | s of FSR1H/F    | SR1L to addr | ess data me           | mory      |                       | XXXX         | XXXX | XXXX | XXXX                  |

| 082h <sup>(2)</sup>    | PCL        | Program Co                    | ounter (PC) L               | east Significa | nt Byte         |              |                       |           |                       | 0000         | 0000 | 0000 | 0000                  |

| 083h <sup>(2)</sup>    | STATUS     |                               |                             | _              | TO              | PD           | Z                     | DC        | С                     | 1            | 1000 | q    | quuu                  |

| 084h <sup>(2)</sup>    | FSR0L      | Indirect Dat                  | a Memory Ad                 | Idress 0 Low   | Pointer         |              |                       |           |                       | 0000         | 0000 | uuuu | uuuv                  |

| 085h <sup>(2)</sup>    | FSR0H      | Indirect Dat                  | a Memory Ad                 | ldress 0 High  | Pointer         |              |                       |           |                       | 0000         | 0000 | 0000 | 0000                  |

| 086h <sup>(2)</sup>    | FSR1L      | Indirect Dat                  | a Memory Ad                 | Idress 1 Low   | Pointer         |              |                       |           |                       | 0000         | 0000 | uuuu | uuuv                  |

| 087h <sup>(2)</sup>    | FSR1H      | Indirect Dat                  | a Memory Ad                 | ldress 1 High  | Pointer         |              |                       |           |                       | 0000         | 0000 | 0000 | 0000                  |

| 088h <sup>(2)</sup>    | BSR        | _                             | _                           | _              |                 |              | BSR<4:0>              |           |                       | 0            | 0000 | 0    | 0000                  |

| 089h <sup>(2)</sup>    | WREG       | Working Re                    | gister                      |                |                 |              |                       |           |                       | 0000         | 0000 | uuuu | uuuv                  |

| 08Ah <sup>(1, 2)</sup> | PCLATH     | _                             | Write Buffer                | for the upper  | 7 bits of the F | rogram Cour  | nter                  |           |                       | -000         | 0000 | -000 | 0000                  |

| 08Bh <sup>(2)</sup>    | INTCON     | GIE                           | PEIE                        | TMR0IE         | INTE            | IOCIE        | TMR0IF                | INTF      | IOCIF                 | 0000         | 0000 | 0000 | 0000                  |

| 08Ch                   | TRISA      | PORTA Dat                     | a Direction R               | egister        |                 |              |                       |           |                       | 1111         | 1111 | 1111 | 1111                  |

| 08Dh                   | TRISB      | PORTB Data Direction Register |                             |                |                 |              |                       |           | 1111                  | 1111         | 1111 | 1111 |                       |

| 08Eh                   | TRISC      | PORTC Da                      | ta Direction R              | Register       |                 |              |                       |           |                       | 1111         | 1111 | 1111 | 1111                  |

| 08Fh <sup>(3)</sup>    | TRISD      | PORTD Da                      | ta Direction R              | Register       |                 |              |                       |           |                       | 1111         | 1111 | 1111 | 1111                  |

| 090h                   | TRISE      | _                             | _                           | _              | _               | (4)          | TRISE2 <sup>(3)</sup> | TRISE1(3) | TRISE0 <sup>(3)</sup> |              | 1111 |      | 1111                  |

| 091h                   | PIE1       | TMR1GIE                       | ADIE                        | RCIE           | TXIE            | SSPIE        | CCP1IE                | TMR2IE    | TMR1IE                | 0000         | 0000 | 0000 | 0000                  |

| 092h                   | PIE2       | OSFIE                         | C2IE                        | C1IE           | EEIE            | BCLIE        | LCDIE                 | _         | CCP2IE                | 0000         | 00-0 | 0000 | 00-0                  |

| 093h                   | PIE3       | _                             | CCP5IE                      | CCP4IE         | CCP3IE          | TMR6IE       | _                     | TMR4IE    | _                     | -000         | 0-0- | -000 | 0-0-                  |

| 094h                   | _          | Unimpleme                     | nted                        |                |                 |              |                       |           |                       | _            | _    | -    | _                     |

| 095h                   | OPTION_REG | WPUEN                         | INTEDG                      | TMROCS         | TMROSE          | PSA          |                       | PS<2:0>   |                       | 1111         | 1111 | 1111 | 1111                  |

| 096h                   | PCON       | STKOVF                        | STKUNF                      | _              | _               | RMCLR        | RI                    | POR       | BOR                   | 00           | 11qq | qq   | qquv                  |

| 097h                   | WDTCON     | _                             | _                           |                | W               | /DTPS<4:0>   |                       |           | SWDTEN                | 01           | 0110 | 01   | 0110                  |

| 098h                   | OSCTUNE    | _                             | _                           |                |                 | TUN<5        | 5:0>                  |           |                       | 00           | 0000 | 00   | 0000                  |

| 099h                   | OSCCON     | SPLLEN                        |                             | IRCF           | <3:0>           |              | _                     | SCS       | <1:0>                 | 0011         | 1-00 | 0011 | 1-00                  |

| 09Ah                   | OSCSTAT    | T10SCR                        | PLLR                        | OSTS           | HFIOFR          | HFIOFL       | MFIOFR                | LFIOFR    | HFIOFS                | 00q0         | 0q0- | dddd | qq0-                  |

| 09Bh                   | ADRESL     | A/D Result                    | Register Low                |                |                 |              | •                     |           |                       | XXXX         |      | uuuu |                       |

| 09Ch                   | ADRESH     |                               | Register High               |                |                 |              |                       |           |                       | XXXX         | xxxx |      |                       |

| 09Dh                   | ADCON0     | _                             | 2 0                         |                | CHS<4:0>        |              |                       | GO/DONE   | ADON                  |              | 0000 |      | 0000                  |

| 09Eh                   | ADCON1     | ADFM                          |                             | ADCS<2:0>      |                 | _            | ADNREF                | ADPREF1   |                       |              |      | 0000 |                       |

| 09Fh                   |            | Unimpleme                     | nted                        |                |                 |              |                       | 1         |                       |              | _    |      | _                     |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-10.

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16(L)F1938 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

| Address                | Name   | Bit 7        | Bit 6                                                                                                     | Bit 5          | Bit 4           | Bit 3        | Bit 2        | Bit 1 | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|--------|--------------|-----------------------------------------------------------------------------------------------------------|----------------|-----------------|--------------|--------------|-------|---------|----------------------|---------------------------------|

| Bank 8                 |        |              |                                                                                                           |                |                 |              |              |       |         |                      |                                 |

| 400h <sup>(2)</sup>    | INDF0  |              | Addressing this location uses contents of FSR0H/FSR0L to address data memory<br>(not a physical register) |                |                 |              |              |       |         | XXXX XXXX            | ****                            |

| 401h <sup>(2)</sup>    | INDF1  |              | this location cal register)                                                                               | uses contents  | s of FSR1H/F    | SR1L to addr | ess data men | nory  |         | ****                 | XXXX XXXX                       |

| 402h <sup>(2)</sup>    | PCL    | Program Co   | ounter (PC) L                                                                                             | east Significa | nt Byte         |              |              |       |         | 0000 0000            | 0000 0000                       |

| 403h <sup>(2)</sup>    | STATUS | _            | _                                                                                                         | _              | TO              | PD           | Z            | DC    | С       | 1 1000               | q quuu                          |

| 404h <sup>(2)</sup>    | FSR0L  | Indirect Dat | a Memory Ac                                                                                               | Idress 0 Low   | Pointer         |              |              |       |         | 0000 0000            | uuuu uuuu                       |

| 405h <sup>(2)</sup>    | FSR0H  | Indirect Dat | a Memory Ac                                                                                               | ldress 0 High  | Pointer         |              |              |       |         | 0000 0000            | 0000 0000                       |

| 406h <sup>(2)</sup>    | FSR1L  | Indirect Dat | a Memory Ac                                                                                               | Idress 1 Low   | Pointer         |              |              |       |         | 0000 0000            | uuuu uuuu                       |

| 407h <sup>(2)</sup>    | FSR1H  | Indirect Dat | a Memory Ac                                                                                               | ldress 1 High  | Pointer         |              |              |       |         | 0000 0000            | 0000 0000                       |

| 408h <sup>(2)</sup>    | BSR    | _            | _                                                                                                         | —              |                 |              | BSR<4:0>     |       |         | 0 0000               | 0 0000                          |

| 409h <sup>(2)</sup>    | WREG   | Working Re   | gister                                                                                                    |                |                 |              |              |       |         | 0000 0000            | uuuu uuuu                       |

| 40Ah <sup>(1, 2)</sup> | PCLATH | _            | Write Buffer                                                                                              | for the upper  | 7 bits of the I | Program Cour | nter         |       |         | -000 0000            | -000 0000                       |

| 40Bh <sup>(2)</sup>    | INTCON | GIE          | PEIE                                                                                                      | TMR0IE         | INTE            | IOCIE        | TMR0IF       | INTF  | IOCIF   | 0000 0000            | 0000 0000                       |

| 40Ch                   | _      | Unimpleme    | nted                                                                                                      |                |                 |              |              |       |         | _                    | _                               |

| 40Dh                   | —      | Unimpleme    | nted                                                                                                      |                |                 |              |              |       |         | _                    | _                               |

| 40Eh                   | —      | Unimpleme    | nted                                                                                                      |                |                 |              |              |       |         | _                    | _                               |

| 40Fh                   | —      | Unimpleme    | nted                                                                                                      |                |                 |              |              |       |         | _                    | _                               |

| 410h                   | —      | Unimpleme    | nted                                                                                                      |                |                 |              |              |       |         | _                    | _                               |

| 411h                   | —      | Unimpleme    | nted                                                                                                      |                |                 |              |              |       |         | _                    | _                               |

| 412h                   | —      | Unimpleme    | nted                                                                                                      |                |                 |              |              |       |         | _                    | _                               |

| 413h                   | —      | Unimpleme    | nted                                                                                                      |                |                 |              |              |       |         | _                    | _                               |

| 414h                   | —      | Unimpleme    | nted                                                                                                      |                |                 |              |              |       |         | _                    | _                               |

| 415h                   | TMR4   | Timer 4 Mo   | dule Register                                                                                             |                |                 |              |              |       |         | 0000 0000            | 0000 0000                       |

| 416h                   | PR4    | Timer 4 Per  | iod Register                                                                                              |                |                 |              |              |       |         | 1111 1111            | 1111 1111                       |

| 417h                   | T4CON  | _            |                                                                                                           | T4OUT          | PS<3:0>         |              | TMR40N       | T4CK  | PS<1:0> | -000 0000            | -000 0000                       |

| 418h                   | —      | Unimpleme    | nted                                                                                                      |                |                 |              |              |       |         | _                    | _                               |

| 419h                   | —      | Unimpleme    | nted                                                                                                      |                |                 |              |              |       |         | _                    | _                               |

| 41Ah                   | —      | Unimpleme    | nted                                                                                                      |                |                 |              |              |       |         | _                    | _                               |

| 41Bh                   | —      | Unimpleme    | nted                                                                                                      |                |                 |              |              |       |         | _                    | _                               |

| 41Ch                   | TMR6   | Timer 6 Mo   | dule Register                                                                                             |                |                 |              |              |       |         | 0000 0000            | 0000 0000                       |

| 41Dh                   | PR6    | Timer 6 Per  | iod Register                                                                                              |                |                 |              |              |       |         | 1111 1111            | 1111 1111                       |

| 41Eh                   | T6CON  | —            |                                                                                                           | T6OUT          | PS<3:0>         |              | TMR6ON       | T6CK  | PS<1:0> | -000 0000            | -000 0000                       |

| 41Fh                   | _      | Unimpleme    | nted                                                                                                      |                |                 |              |              |       |         | _                    | _                               |

#### TABLE 3-10: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: These registers/bits are not implemented on PIC16(L)F1938 devices, read as '0'.

4: Unimplemented, read as '1'.

DS40001574C-page 40

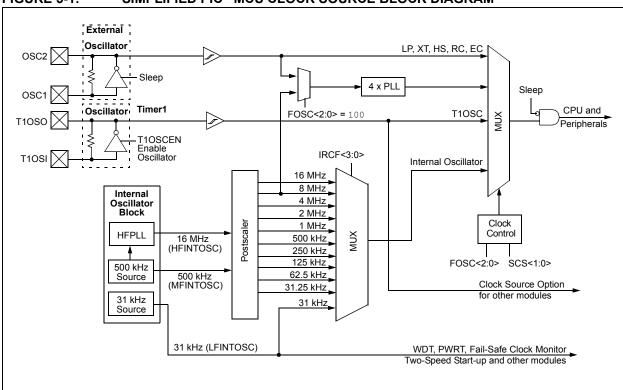

#### FIGURE 5-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

#### 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT, or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | the oscillator start-up time and will cause |  |  |  |  |  |

|       | the OSTS bit of the OSCSTAT register to     |  |  |  |  |  |

|       | remain clear.                               |  |  |  |  |  |

#### 5.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Words) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Words configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

| TABLE 5-1: O | SCILLATOR SWITCHING DELAYS |

|--------------|----------------------------|

|--------------|----------------------------|

| Switch From      | Switch To                                                                     | Frequency                                       | Oscillator Delay        |

|------------------|-------------------------------------------------------------------------------|-------------------------------------------------|-------------------------|

| Sleep/POR        | LFINTOSC <sup>(1)</sup><br>MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup> | 31 kHz<br>31.25 kHz-500 kHz<br>31.25 kHz-16 MHz | 2 cycles                |

| Sleep/POR        | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 2 cycles                |

| LFINTOSC         | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 1 cycle of each         |

| Sleep/POR        | Timer1 Oscillator<br>LP, XT, HS <sup>(1)</sup>                                | 32 kHz-20 MHz                                   | 1024 Clock Cycles (OST) |

| Any clock source | MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup>                            | 31.25 kHz-500 kHz<br>31.25 kHz-16 MHz           | 2 μs (approx.)          |

| Any clock source | LFINTOSC <sup>(1)</sup>                                                       | 31 kHz                                          | 1 cycle of each         |

| Any clock source | Timer1 Oscillator                                                             | 32 kHz                                          | 1024 Clock Cycles (OST) |

| PLL inactive     | PLL active                                                                    | 16-32 MHz                                       | 2 ms (approx.)          |

Note 1: PLL inactive.

#### 6.4 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 6-2).

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| Х     | 1   | Enabled  |

#### 6.4.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

**Note:** A Reset does not drive the MCLR pin low.

#### 6.4.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See Section 12.11 "PORTE Registers" for more information.

#### 6.5 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the WDT Reset. See **Section 10.0** "**Watchdog Timer**" for more information.

#### 6.6 RESET Instruction

A RESET instruction will cause a device Reset. The RI bit in the PCON register will be set to '0'. See Table 6-4 for default conditions after a RESET instruction has occurred.

#### 6.7 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section 3.5.2** "**Overflow/Underflow Reset**" for more information.

#### 6.8 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR had just occurred.

#### 6.9 Power-Up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the PWRTE bit of Configuration Words.

#### 6.10 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. Oscillator start-up timer runs to completion (if required for oscillator source).

- 3. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for more information.

The Power-up Timer and oscillator start-up timer run independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer and oscillator start-up timer will expire. Upon bringing MCLR high, the device will begin execution immediately (see Figure 6-3). This is useful for testing purposes or to synchronize more than one device operating in parallel.

| R/W-0/0         | R/W-0/0           | R/W-0/0                            | R/W-0/0         | R/W-0/0         | R/W-0/0          | R/W-0/0 | R/W-0/0     |

|-----------------|-------------------|------------------------------------|-----------------|-----------------|------------------|---------|-------------|

| TMR1GIE         | ADIE              | RCIE                               | TXIE            | SSPIE           | CCP1IE           | TMR2IE  | TMR1IE      |

| bit 7           |                   |                                    |                 |                 |                  |         | bit (       |

| Legend:         |                   |                                    |                 |                 |                  |         |             |

| R = Readab      | le bit            | W = Writable                       | bit             | U = Unimpler    | nented bit, read | as '0'  |             |

| u = Bit is und  |                   | x = Bit is unkr                    | nown            | •               | at POR and BO    |         | ther Resets |

| '1' = Bit is se | •                 | '0' = Bit is cle                   | ared            |                 |                  |         |             |

| <b>L:4 7</b>    |                   | iment Cata Inte                    | www.wt Enchlau  | .:4             |                  |         |             |

| bit 7           |                   | imer1 Gate Inte<br>the Timer1 Gate |                 |                 |                  |         |             |

|                 |                   | the Timer1 Gat                     |                 |                 |                  |         |             |

| bit 6           | ADIE: A/D C       | onverter (ADC)                     | Interrupt Ena   | ble bit         |                  |         |             |

|                 |                   | the ADC interru                    |                 |                 |                  |         |             |

|                 |                   | the ADC interru                    | •               |                 |                  |         |             |

| bit 5           |                   | T Receive Inter                    | •               | it              |                  |         |             |

|                 |                   | the USART rec<br>the USART rec     |                 |                 |                  |         |             |

| bit 4           |                   | T Transmit Inter                   | •               |                 |                  |         |             |

|                 |                   | the USART trar                     | •               |                 |                  |         |             |

|                 | 0 = Disables      | the USART tra                      | nsmit interrup  | t               |                  |         |             |

| bit 3           | SSPIE: Sync       | hronous Serial                     | Port (MSSP)     | Interrupt Enabl | e bit            |         |             |

|                 |                   | the MSSP inter the MSSP inter      |                 |                 |                  |         |             |

| bit 2           | CCP1IE: CC        | P1 Interrupt En                    | able bit        |                 |                  |         |             |

|                 |                   | the CCP1 interr                    |                 |                 |                  |         |             |

| bit 1           |                   | R2 to PR2 Mate                     | •               | nable bit       |                  |         |             |

|                 | 1 = Enables       | the Timer2 to P<br>the Timer2 to F | R2 match inte   | errupt          |                  |         |             |

| bit 0           |                   | ner1 Overflow Ir                   |                 | •               |                  |         |             |

|                 |                   | the Timer1 over                    |                 |                 |                  |         |             |

|                 | 0 = Disables      | the Timer1 ove                     | rflow interrupt | :               |                  |         |             |

| Note: B         | it PEIE of the IN |                                    | must bo         |                 |                  |         |             |

|                 | et to enable any  |                                    |                 |                 |                  |         |             |

#### REGISTER 7-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

#### 12.10 Register Definitions: PORTD Control

#### REGISTER 12-14: PORTD: PORTD REGISTER<sup>(1)</sup>

| R/W-x/u                                 | R/W-x/u                           | R/W-x/u           | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-----------------------------------------|-----------------------------------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| RD7                                     | RD6                               | RD5               | RD4     | RD3                                                   | RD2     | RD1     | RD0     |  |

| bit 7                                   |                                   |                   |         |                                                       |         |         | bit 0   |  |

|                                         |                                   |                   |         |                                                       |         |         |         |  |

| Legend:                                 |                                   |                   |         |                                                       |         |         |         |  |

| R = Readable I                          | R = Readable bit W = Writable bit |                   |         | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |                                   |                   | iown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set                        |                                   | '0' = Bit is clea | ared    |                                                       |         |         |         |  |

bit 7-0 **RD<7:0>**: PORTD General Purpose I/O Pin bits 1 = Port pin is > VIH 0 = Port pin is < VIL

Note 1: PORTD is not implemented on PIC16(L)F1938 devices, read as '0'.

#### REGISTER 12-15: TRISD: PORTD TRI-STATE REGISTER<sup>(1)</sup>

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2  | TRISD1  | TRISD0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **TRISD<7:0>:** PORTD Tri-State Control bits

- 1 = PORTD pin configured as an input (tri-stated)

- 0 = PORTD pin configured as an output

- Note 1: TRISD is not implemented on PIC16(L)F1938 devices, read as '0'.

- 2: PORTD implemented on PIC16(L)F1939 devices only.

#### 12.12 Register Definitions: PORTE Control

#### REGISTER 12-18: PORTE: PORTE REGISTER

| U-0              | U-0   | U-0               | U-0  | R-x/u          | R/W-x/u            | R/W-x/u            | R/W-x/u            |

|------------------|-------|-------------------|------|----------------|--------------------|--------------------|--------------------|

| —                | _     | —                 | _    | RE3            | RE2 <sup>(1)</sup> | RE1 <sup>(1)</sup> | RE0 <sup>(1)</sup> |

| bit 7            |       |                   |      | ·              | ·                  |                    | bit 0              |

|                  |       |                   |      |                |                    |                    |                    |

| Legend:          |       |                   |      |                |                    |                    |                    |

| R = Readable b   | bit   | W = Writable b    | bit  | U = Unimpler   | mented bit, read   | as '0'             |                    |

| u = Bit is uncha | inged | x = Bit is unkn   | own  | -n/n = Value a | at POR and BO      | R/Value at all o   | ther Resets        |

| '1' = Bit is set |       | '0' = Bit is clea | ared |                |                    |                    |                    |

bit 7-4 Unimplemented: Read as '0' bit 3-0 RE<3:0>: PORTE I/O Pin bits<sup>(1)</sup> 1 = Port pin is > VIH 0 = Port pin is < VIL

Note 1: RE<2:0> are not implemented on the PIC16(L)F1938. Read as '0'.

#### REGISTER 12-19: TRISE: PORTE TRI-STATE REGISTER

| U-0   | U-0 | U-0 | U-0 | U-1 <sup>(2)</sup> | R/W-1 R/W-1           |                       | R/W-1                 |

|-------|-----|-----|-----|--------------------|-----------------------|-----------------------|-----------------------|

| _     | —   | _   | _   | _                  | TRISE2 <sup>(1)</sup> | TRISE1 <sup>(1)</sup> | TRISE0 <sup>(1)</sup> |

| bit 7 |     |     |     |                    |                       |                       | bit 0                 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 3 Unimplemented: Read as '1'

bit 2-0 **TRISE<2:0>:** RE<2:0> Tri-State Control bits<sup>(1)</sup> 1 = PORTE pin configured as an input (tri-stated) 0 = PORTE pin configured as an output

**Note 1:** TRISE<2:0> are not implemented on the PIC16(L)F1938. Read as '0'.

**2:** Unimplemented, read as '1'.

#### 15.3 Register Definitions: ADC Control

#### REGISTER 15-1: ADCON0: A/D CONTROL REGISTER 0

| U-0                          | R/W-0/0                                 | R/W-0/0                             | R/W-0/0              | R/W-0/0                      | R/W-0/0         | R/W-0/0           | R/W-0/0      |  |  |

|------------------------------|-----------------------------------------|-------------------------------------|----------------------|------------------------------|-----------------|-------------------|--------------|--|--|

| _                            |                                         |                                     | CHS<4:0>             |                              |                 | GO/DONE           | ADON         |  |  |

| oit 7                        |                                         |                                     |                      |                              |                 |                   | bit          |  |  |

|                              |                                         |                                     |                      |                              |                 |                   |              |  |  |

| Legend:                      |                                         |                                     |                      |                              |                 |                   |              |  |  |

| R = Readable bit W = Writabl |                                         |                                     | bit                  | U = Unimpler                 | nented bit, rea | ad as '0'         |              |  |  |

| u = Bit is und               | hanged                                  | x = Bit is unknown                  |                      | -n/n = Value a               | at POR and B    | OR/Value at all o | other Resets |  |  |

| '1' = Bit is set             |                                         | '0' = Bit is cle                    | '0' = Bit is cleared |                              |                 |                   |              |  |  |

|                              |                                         |                                     |                      |                              |                 |                   |              |  |  |

| bit 7                        | -                                       | nted: Read as '                     |                      |                              |                 |                   |              |  |  |

| bit 6-2                      |                                         | Analog Channe                       |                      |                              |                 |                   |              |  |  |

|                              |                                         | R (Fixed Voltage                    | e Reference) E       | Buffer 1 Output <sup>(</sup> | 2)              |                   |              |  |  |

|                              | 11110 <b>= DA</b>                       |                                     | (3)                  |                              |                 |                   |              |  |  |

|                              |                                         | mperature Indica<br>served. No char |                      | 4                            |                 |                   |              |  |  |

|                              | 11100 <b>= Re</b>                       | served. No char                     | nnel connecte        | <b>J</b> .                   |                 |                   |              |  |  |

|                              | •                                       |                                     |                      |                              |                 |                   |              |  |  |

|                              | •                                       |                                     |                      |                              |                 |                   |              |  |  |

|                              | 01110 = Reserved. No channel connected. |                                     |                      |                              |                 |                   |              |  |  |

|                              | 01101 <b>= AN</b>                       | 113                                 |                      |                              |                 |                   |              |  |  |

|                              | 01100 <b>= AN</b>                       | 112                                 |                      |                              |                 |                   |              |  |  |

|                              | 01011 <b>= AN</b>                       | 111                                 |                      |                              |                 |                   |              |  |  |

|                              | 01010 <b>= AN</b>                       |                                     |                      |                              |                 |                   |              |  |  |

|                              | 01001 <b>= AN</b>                       |                                     |                      |                              |                 |                   |              |  |  |

|                              | 01000 = AN<br>00111 = AN                |                                     |                      |                              |                 |                   |              |  |  |

|                              | 00111 = AN<br>00110 = AN                |                                     |                      |                              |                 |                   |              |  |  |

|                              | 00110 <b>–</b> AN                       |                                     |                      |                              |                 |                   |              |  |  |

|                              | 00100 <b>= AN</b>                       |                                     |                      |                              |                 |                   |              |  |  |

|                              | 00011 <b>= AN</b>                       |                                     |                      |                              |                 |                   |              |  |  |

|                              | 00010 <b>= AN</b>                       | 12                                  |                      |                              |                 |                   |              |  |  |

|                              | 00001 <b>= AN</b>                       | 11                                  |                      |                              |                 |                   |              |  |  |

|                              | 00000 <b>= AN</b>                       | 10                                  |                      |                              |                 |                   |              |  |  |

| bit 1                        | GO/DONE:                                | A/D Conversion                      | Status bit           |                              |                 |                   |              |  |  |

|                              | 1 = A/D con                             | version cycle in                    | progress. Set        | ting this bit star           | ts an A/D con   | version cycle.    |              |  |  |

|                              |                                         | is automatically                    |                      |                              | e A/D convers   | ion has complet   | ted.         |  |  |

|                              | $0 = A/D con^2$                         | version complet                     | ed/not in prog       | ress                         |                 |                   |              |  |  |

| bit 0                        | ADON: ADO                               | C Enable bit                        |                      |                              |                 |                   |              |  |  |

|                              | 1 = ADC is e                            |                                     |                      |                              |                 |                   |              |  |  |

|                              | 0 = ADC is 0                            | disabled and cor                    | nsumes no op         | erating current              |                 |                   |              |  |  |

| Note 1: Se                   | ee Section 17.                          | 0 "Digital-to-Ar                    | nalog Convert        | ter (DAC) Mod                | ule" for more   | information.      |              |  |  |

| <b>2</b> : Se                | ee Section 14.                          | 0 "Fixed Voltag                     | e Reference          | (FVR)" for more              | e information.  |                   |              |  |  |

| <b>3</b> : Se                | ee Section 16.                          | 0 "Temperature                      | e Indicator Mo       | odule" for more              | information.    |                   |              |  |  |

| 4. N                         | ot available on                         | the PIC16(L)E1                      | 933/1936/193         | 3                            |                 |                   |              |  |  |

**4:** Not available on the PIC16(L)F1933/1936/1938.

#### 18.3 Comparator Hysteresis

A selectable amount of separation voltage can be added to the input pins of each comparator to provide a hysteresis function to the overall operation. Hysteresis is enabled by setting the CxHYS bit of the CMxCON0 register.

See **Section 30.0 "Electrical Specifications"** for more information.

#### 18.4 Timer1 Gate Operation

The output resulting from a comparator operation can be used as a source for gate control of Timer1. See **Section 21.6 "Timer1 Gate"** for more information. This feature is useful for timing the duration or interval of an analog event.

It is recommended that the comparator output be synchronized to Timer1. This ensures that Timer1 does not increment while a change in the comparator is occurring.

#### 18.4.1 COMPARATOR OUTPUT SYNCHRONIZATION

The output from either comparator, C1 or C2, can be synchronized with Timer1 by setting the CxSYNC bit of the CMxCON0 register.

Once enabled, the comparator output is latched on the falling edge of the Timer1 source clock. If a prescaler is used with Timer1, the comparator output is latched after the prescaling function. To prevent a race condition, the comparator output is latched on the falling edge of the Timer1 clock source and Timer1 increments on the rising edge of its clock source. See the Comparator Block Diagram (Figure 18-2) and the Timer1 Block Diagram (Figure 21-1) for more information.

#### **18.5** Comparator Interrupt

An interrupt can be generated upon a change in the output value of the comparator for each comparator, a rising edge detector and a Falling edge detector are present.

When either edge detector is triggered and its associated enable bit is set (CxINTP and/or CxINTN bits of the CMxCON1 register), the Corresponding Interrupt Flag bit (CxIF bit of the PIR2 register) will be set.

To enable the interrupt, you must set the following bits:

- CxON, CxPOL and CxSP bits of the CMxCON0 register

- CxIE bit of the PIE2 register

- CxINTP bit of the CMxCON1 register (for a rising edge detection)

- CxINTN bit of the CMxCON1 register (for a falling edge detection)

- · PEIE and GIE bits of the INTCON register

The associated interrupt flag bit, CxIF bit of the PIR2 register, must be cleared in software. If another edge is detected while this flag is being cleared, the flag will still be set at the end of the sequence.

### 18.6 Comparator Positive Input Selection

Configuring the CxPCH<1:0> bits of the CMxCON1 register directs an internal voltage reference or an analog pin to the non-inverting input of the comparator:

- · CxIN+ analog pin

- DAC Output

- FVR (Fixed Voltage Reference)

- Vss (Ground)

See Section 14.0 "Fixed Voltage Reference (FVR)" for more information on the Fixed Voltage Reference module.

See Section 17.0 "Digital-to-Analog Converter (DAC) Module" for more information on the DAC input signal.

Any time the comparator is disabled (CxON = 0), all comparator inputs are disabled.

**Note:** Although a comparator is disabled, an interrupt can be generated by changing the output polarity with the CxPOL bit of the CMxCON0 register, or by switching the comparator on or off with the CxON bit of the CMxCON0 register.

| R/W-0/0        | R/W-0/0                                               | R/W-0/0                                                                                    | R/W-0/0              | R/W-0/0        | R/W-0/0                 | R/W-0/0 | R/W-0/0      |

|----------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------|----------------|-------------------------|---------|--------------|

| CCPxASE        | CCPxAS2                                               | CCPxAS1                                                                                    | CCPxAS0              | PSSxA          | .C<1:0>                 | PSSxB   | D<1:0>       |

| bit 7          |                                                       |                                                                                            |                      |                |                         |         | bit 0        |

| <u> </u>       |                                                       |                                                                                            |                      |                |                         |         |              |

| Legend:        |                                                       |                                                                                            |                      |                |                         |         |              |

| R = Readat     |                                                       | W = Writable                                                                               |                      | •              | nented bit, read        |         |              |

| u = Bit is ur  | •                                                     | -                                                                                          |                      |                |                         |         | other Resets |

| '1' = Bit is s | et                                                    | '0' = Bit is cle                                                                           | ared                 |                |                         |         |              |

| bit 7          | CCPxASE: (                                            | CPx Auto-Shu                                                                               | tdown Event S        | tatus bit      |                         |         |              |

|                |                                                       | wn event has o<br>tputs are opera                                                          |                      | outputs are in | shutdown state          | e       |              |

| bit 6          | 1 = Auto-shu                                          | CPx Auto-Shu<br>utdown 2 sourc<br>utdown 2 sourc                                           | e is enabled, V      |                |                         |         |              |

| bit 5          | 1 = Auto-shu                                          | CPx Auto-Shu<br>utdown 1 sourc<br>utdown 1 sourc                                           | e is enabled, a      |                | ),(2) output low        |         |              |

| bit 4          | 1 = Auto-shu                                          | CPx Auto-Shu<br>utdown 0 sourc<br>utdown 0 sourc                                           | e is enabled, a      |                | <sup>)</sup> output low |         |              |

| bit 3-2        | 00 <b>= Drive pi</b><br>01 <b>= Drive pi</b>          | D>: Pins PxA and<br>ns PxA and Px<br>ns PxA and Px<br>A and PxC tri-s                      | C to '0'<br>C to '1' | wn State Contr | ol bits                 |         |              |

| bit 1-0        | 00 <b>= Drive pi</b><br>01 <b>= Drive pi</b>          | D>: Pins PxB and PxD tri-s | D to '0'<br>D to '1' | wn State Contr | ol bits                 |         |              |

| <b>2</b> : a   | f CxSYNC is ena<br>async_CxOUT = a<br>async_CxOUT = a | async_C2OUT                                                                                | (for CCP1 and        |                | I.                      |         |              |

#### REGISTER 23-4: CCPxAS: CCPX AUTO-SHUTDOWN CONTROL REGISTER

#### 24.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK line. The master determines when the slave (Processor 2, Figure 24-5) is to broadcast data by the software protocol.

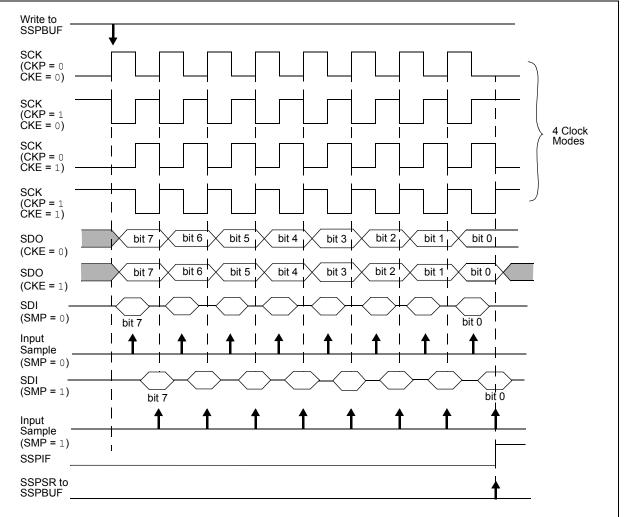

In Master mode, the data is transmitted/received as soon as the SSPBUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPBUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSPCON1 register and the CKE bit of the SSPSTAT register. This then, would give waveforms for SPI communication as shown in Figure 24-6, Figure 24-8 and Figure 24-9, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSPADD + 1))

Figure 24-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPBUF is loaded with the received data is shown.

FIGURE 24-6: SPI MODE WAVEFORM (MASTER MODE)

#### 25.5.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are unread characters in the receive FIFO.

#### 25.5.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

#### 25.5.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is

set then the error condition is cleared by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### 25.5.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

### 25.5.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SPBRGH, SPBRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit which resets the EUSART.

#### REGISTER 27-4: LCDCST: LCD CONTRAST CONTROL REGISTER

| U-0          | U-0 | U-0          | U-0 | U-0          | R/W-0/0          | R/W-0/0     | R/W-0/0 |

|--------------|-----|--------------|-----|--------------|------------------|-------------|---------|

| —            | —   | —            | —   | —            | I                | _CDCST<2:0> |         |

| bit 7        |     |              |     |              |                  |             | bit 0   |

|              |     |              |     |              |                  |             |         |

| Lagandi      |     |              |     |              |                  |             |         |

| Legend:      |     |              |     |              |                  |             |         |

| R = Readable | bit | W = Writable | bit | U = Unimplen | nented bit, read | as '0'      |         |

C = Only clearable bit

bit 7-3 Unimplemented: Read as '0'

'1' = Bit is set

bit 2-0 LCDCST<2:0>: LCD Contrast Control bits Selects the resistance of the LCD contrast control resistor ladder

'0' = Bit is cleared

Bit Value = Resistor ladder

000 = Minimum Resistance (maximum contrast). Resistor ladder is shorted.

001 = Resistor ladder is at 1/7th of maximum resistance

010 = Resistor ladder is at 2/7th of maximum resistance

011 = Resistor ladder is at 3/7th of maximum resistance

100 = Resistor ladder is at 4/7th of maximum resistance

101 = Resistor ladder is at 5/7th of maximum resistance

110 = Resistor ladder is at 6/7th of maximum resistance

111 = Resistor ladder is at maximum resistance (minimum contrast).

#### TABLE 30-16: I<sup>2</sup>C<sup>™</sup> BUS DATA REQUIREMENTS

| Param.<br>No. | Symbol  | Characteristic        |              | Min.       | Max. | Units | Conditions                                  |

|---------------|---------|-----------------------|--------------|------------|------|-------|---------------------------------------------|

| SP100*        | Тнідн   | Clock high time       | 100 kHz mode | 4.0        |      | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                       | 400 kHz mode | 0.6        |      | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                       | SSP module   | 1.5Tcy     | _    |       |                                             |

| SP101*        | TLOW    | Clock low time        | 100 kHz mode | 4.7        |      | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                       | 400 kHz mode | 1.3        |      | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                       | SSP module   | 1.5Tcy     | —    |       |                                             |

| SP102*        | Tr      | SDA and SCL rise      | 100 kHz mode | —          | 1000 | ns    |                                             |

|               | time    | time                  | 400 kHz mode | 20 + 0.1Св | 300  | ns    | CB is specified to be from 10-400 pF        |

| SP103*        | TF      | SDA and SCL fall      | 100 kHz mode | —          | 250  | ns    |                                             |

|               |         | time                  | 400 kHz mode | 20 + 0.1Св | 250  | ns    | CB is specified to be from 10-400 pF        |

| SP106*        | THD:DAT | Data input hold time  | 100 kHz mode | 0          | _    | ns    |                                             |

|               |         |                       | 400 kHz mode | 0          | 0.9  | μS    |                                             |

| SP107*        | TSU:DAT | Data input setup      | 100 kHz mode | 250        |      | ns    | (Note 2)                                    |

|               |         | time                  | 400 kHz mode | 100        | _    | ns    |                                             |

| SP109*        | ΤΑΑ     | Output valid from     | 100 kHz mode | _          | 3500 | ns    | (Note 1)                                    |

|               |         | clock                 | 400 kHz mode | _          | _    | ns    |                                             |

| SP110*        | TBUF    | Bus free time         | 100 kHz mode | 4.7        | _    | μS    | Time the bus must be free                   |

|               |         |                       | 400 kHz mode | 1.3        | —    | μS    | before a new transmission<br>can start      |

| SP111         | Св      | Bus capacitive loadir | ng           | —          | 400  | pF    |                                             |

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

2: A Fast mode (400 kHz) I<sup>2</sup>C <sup>™</sup> bus device can be used in a Standard mode (100 kHz) I<sup>2</sup>C bus system, but the requirement TsU:DAT ≥ 250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TsU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode I<sup>2</sup>C bus specification), before the SCL line is released.