#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1938-e-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

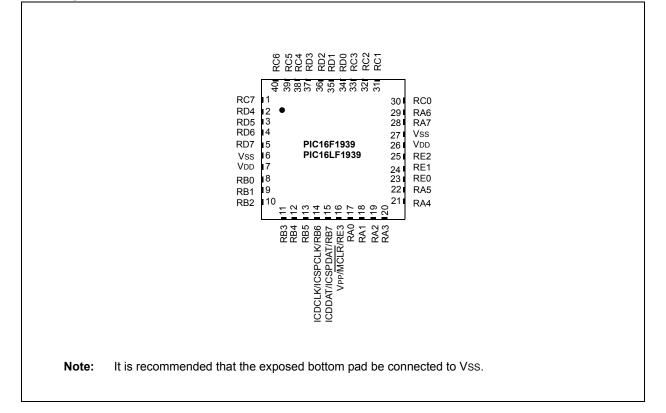

# Pin Diagram – 40-Pin PDIP

| VPP/MCLR/RE3 | 1          |                                              |

|--------------|------------|----------------------------------------------|

| RA0          | 2          |                                              |

| RA1          | 3          | 38 RB5                                       |

| RA2          | 4          | 37 RB4                                       |

| RA3          | 5          | 36 RB3                                       |

| RA4          | 6          | 35 RB2                                       |

| RA5          | 7          | 34 RB1                                       |

| RE0          | 8          | 33 RB0                                       |

| RE1          | 939 6      | 32     VDD       31     Vss       30     RD7 |

| RE2          | PIC16F1939 | 31 □ Vss                                     |

| VDD          | 11 5       | 30 RD7                                       |

| Vss          | 12 6       | • 29 RD6                                     |

| RA7          | 13         | 28 RD5                                       |

| RA6          | 14         | 27 RD4                                       |

| RC0          | 15         | 26 RC7                                       |

| RC1          | 16         | 25 RC6                                       |

| RC2          | 17         | 24 RC5                                       |

| RC3          | 18         | 23 RC4                                       |

| RD0          | 19         | 22 RD3                                       |

| RD1          | 20         | 21 RD2                                       |

|              | L          |                                              |

|              |            |                                              |

Pin Diagram – 40-Pin UQFN 5x5

|                                                                            | Function            | Input<br>Type | Output<br>Type | Description                                                 |

|----------------------------------------------------------------------------|---------------------|---------------|----------------|-------------------------------------------------------------|

| RA0/AN0/C12IN0-/C2OUT <sup>(1)</sup> /                                     | RA0                 | TTL           | CMOS           | General purpose I/O.                                        |

| SRNQ <sup>(1)</sup> / <del>SS<sup>(1)</sup>/VCAP<sup>(2)</sup>/SEG12</del> | AN0                 | AN            | _              | A/D Channel 0 input.                                        |

|                                                                            | C12IN0-             | AN            |                | Comparator C1 or C2 negative input.                         |

|                                                                            | C2OUT               | —             | CMOS           | Comparator C2 output.                                       |

|                                                                            | SRNQ                | _             | CMOS           | SR Latch inverting output.                                  |

|                                                                            | SS                  | ST            | _              | Slave Select input.                                         |

|                                                                            | VCAP                | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F1938/9 only). |

|                                                                            | SEG12               | _             | AN             | LCD Analog output.                                          |

| RA1/AN1/C12IN1-/SEG7                                                       | RA1                 | TTL           | CMOS           | General purpose I/O.                                        |

|                                                                            | AN1                 | AN            | —              | A/D Channel 1 input.                                        |

|                                                                            | C12IN1-             | AN            | —              | Comparator C1 or C2 negative input.                         |

|                                                                            | SEG7                | _             | AN             | LCD Analog output.                                          |

| RA2/AN2/C2IN+/VREF-/                                                       | RA2                 | TTL           | CMOS           | General purpose I/O.                                        |

| DACOUT/COM2                                                                | AN2                 | AN            | —              | A/D Channel 2 input.                                        |

|                                                                            | C2IN+               | AN            | —              | Comparator C2 positive input.                               |

|                                                                            | VREF-               | AN            | —              | A/D Negative Voltage Reference input.                       |

|                                                                            | DACOUT              | —             | AN             | Voltage Reference output.                                   |

|                                                                            | COM2                | —             | AN             | LCD Analog output.                                          |

| RA3/AN3/C1IN+/VREF+/                                                       | RA3                 | TTL           | CMOS           | General purpose I/O.                                        |

| COM3 <sup>(3)</sup> /SEG15                                                 | AN3                 | AN            | —              | A/D Channel 3 input.                                        |

|                                                                            | C1IN+               | AN            | _              | Comparator C1 positive input.                               |

|                                                                            | VREF+               | AN            | —              | A/D Voltage Reference input.                                |

|                                                                            | COM3 <sup>(3)</sup> | —             | AN             | LCD Analog output.                                          |

|                                                                            | SEG15               | —             | AN             | LCD Analog output.                                          |

| RA4/C1OUT/CPS6/T0CKI/SRQ/                                                  | RA4                 | TTL           | CMOS           | General purpose I/O.                                        |

| CCP5/SEG4                                                                  | C10UT               | —             | CMOS           | Comparator C1 output.                                       |

|                                                                            | CPS6                | AN            | _              | Capacitive sensing input 6.                                 |

|                                                                            | TOCKI               | ST            | _              | Timer0 clock input.                                         |

|                                                                            | SRQ                 |               | CMOS           | SR Latch non-inverting output.                              |

|                                                                            | CCP5                | ST            | CMOS           | Capture/Compare/PWM5.                                       |

|                                                                            | SEG4                | _             | AN             | LCD Analog output.                                          |

| RA5/AN4/C2OUT <sup>(1)</sup> /CPS7/                                        | RA5                 | TTL           | CMOS           | General purpose I/O.                                        |

| SRNQ <sup>(1)</sup> /SS <sup>(1)</sup> /VCAP <sup>(2)</sup> /SEG5          | AN4                 | AN            | _              | A/D Channel 4 input.                                        |

|                                                                            | C2OUT               |               | CMOS           | Comparator C2 output.                                       |

|                                                                            | CPS7                | AN            | _              | Capacitive sensing input 7.                                 |

|                                                                            | SRNQ                | _             | CMOS           | SR Latch inverting output.                                  |

|                                                                            | SS                  | ST            | _              | Slave Select input.                                         |

|                                                                            | VCAP                | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F1938/9 only). |

|                                                                            | SEG5                | _             | AN             | LCD Analog output.                                          |

TABLE 1-2: PIC16(L)F1938/9 PINOUT DESCRIPTION

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels XTAL = Crystal

HV = High Voltage  $I^2C^{TM}$  = Schmitt Trigger input with I<sup>2</sup>C levels

**Note 1:** Pin function is selectable via the APFCON register.

- 2: PIC16F1938/9 devices only.

- 3: PIC16(L)F1938 devices only.

- 4: PORTD is available on PIC16(L)F1939 devices only.

- 5: RE<2:0> are available on PIC16(L)F1939 devices only.

| Address                | Name                              | Bit 7                                                                                                     | Bit 6                          | Bit 5          | Bit 4           | Bit 3        | Bit 2                | Bit 1                | Bit 0                | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------|----------------|-----------------|--------------|----------------------|----------------------|----------------------|----------------------|---------------------------------|

| Bank 2                 | Bank 2                            |                                                                                                           |                                |                |                 |              |                      |                      |                      |                      |                                 |

| 100h <sup>(2)</sup>    | INDF0                             | Addressing this location uses contents of FSR0H/FSR0L to address data memory<br>(not a physical register) |                                |                |                 |              |                      |                      |                      | ****                 | ****                            |

| 101h <sup>(2)</sup>    | INDF1                             |                                                                                                           | this location<br>cal register) | uses contents  | s of FSR1H/F    | SR1L to addr | ess data mei         | mory                 |                      | ****                 | ****                            |

| 102h <sup>(2)</sup>    | PCL                               | Program Co                                                                                                | ounter (PC) L                  | east Significa | nt Byte         |              |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 103h <sup>(2)</sup>    | STATUS                            | _                                                                                                         | _                              | _              | TO              | PD           | Z                    | DC                   | С                    | 1 1000               | q quuu                          |

| 104h <sup>(2)</sup>    | FSR0L                             | Indirect Dat                                                                                              | a Memory Ac                    | Idress 0 Low   | Pointer         |              |                      |                      |                      | 0000 0000            | uuuu uuuu                       |

| 105h <sup>(2)</sup>    | FSR0H                             | Indirect Dat                                                                                              | a Memory Ac                    | ldress 0 High  | Pointer         |              |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 106h <sup>(2)</sup>    | FSR1L                             | Indirect Dat                                                                                              | a Memory Ac                    | Idress 1 Low   | Pointer         |              |                      |                      |                      | 0000 0000            | uuuu uuuu                       |

| 107h <sup>(2)</sup>    | FSR1H                             | Indirect Dat                                                                                              | a Memory Ac                    | ldress 1 High  | Pointer         |              |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 108h <sup>(2)</sup>    | BSR                               | _                                                                                                         | —                              | —              |                 | I            | BSR<4:0>             |                      |                      | 0 0000               | 0 0000                          |

| 109h <sup>(2)</sup>    | WREG                              | Working Re                                                                                                | gister                         |                |                 |              |                      |                      |                      | 0000 0000            | uuuu uuuu                       |

| 10Ah <sup>(1, 2)</sup> | PCLATH                            | _                                                                                                         | Write Buffer                   | for the upper  | 7 bits of the F | Program Cour | nter                 |                      |                      | -000 0000            | -000 0000                       |

| 10Bh <sup>(2)</sup>    | INTCON                            | GIE                                                                                                       | PEIE                           | TMR0IE         | INTE            | IOCIE        | TMR0IF               | INTF                 | IOCIF                | 0000 0000            | 0000 0000                       |

| 10Ch                   | LATA                              | PORTA Dat                                                                                                 | PORTA Data Latch               |                |                 |              |                      |                      |                      | XXXX XXXX            | uuuu uuuu                       |

| 10Dh                   | LATB                              | PORTB Da                                                                                                  | PORTB Data Latch               |                |                 |              |                      |                      |                      | XXXX XXXX            | uuuu uuuu                       |

| 10Eh                   | LATC                              | PORTC Da                                                                                                  | PORTC Data Latch               |                |                 |              |                      |                      |                      | XXXX XXXX            | uuuu uuuu                       |

| 10Fh <sup>(3)</sup>    | LATD                              | PORTD Da                                                                                                  | ta Latch                       |                |                 |              |                      |                      |                      | XXXX XXXX            | uuuu uuuu                       |

| 110h                   | LATE                              | _                                                                                                         | —                              | —              | —               | —            | LATE2 <sup>(3)</sup> | LATE1 <sup>(3)</sup> | LATE0 <sup>(3)</sup> | xxx                  | uuu                             |

| 111h                   | CM1CON0                           | C10N                                                                                                      | C10UT                          | C10E           | C1POL           | _            | C1SP                 | C1HYS                | C1SYNC               | 0000 -100            | 0000 -100                       |

| 112h                   | CM1CON1                           | C1INTP                                                                                                    | C1INTN                         | C1PCH1         | C1PCH0          | _            | _                    | C1NC                 | H<1:0>               | 000000               | 000000                          |

| 113h                   | CM2CON0                           | C2ON                                                                                                      | C2OUT                          | C2OE           | C2POL           | _            | C2SP                 | C2HYS                | C2SYNC               | 0000 -100            | 0000 -100                       |

| 114h                   | CM2CON1                           | C2INTP                                                                                                    | C2INTN                         | C2PCH1         | C2PCH0          | _            | _                    | C2NC                 | H<1:0>               | 000000               | 000000                          |

| 115h                   | CMOUT                             | _                                                                                                         | _                              | _              | _               | _            | _                    | MC2OUT               | MC1OUT               | 00                   | 00                              |

| 116h                   | BORCON                            | SBOREN                                                                                                    | _                              | _              | _               | _            | _                    |                      | BORRDY               | 1 q                  | u u                             |

| 117h                   | FVRCON                            | FVREN                                                                                                     | FVRRDY                         | TSEN           | TSRNG           | CDAFVR1      | CDAFVR0              | ADFV                 | R<1:0>               | 0q00 00p0            | 0q00 0000                       |

| 118h                   | DACCON0                           | DACEN                                                                                                     | DACLPS                         | DACOE          |                 | DACPS        | S<1:0>               |                      | DACNSS               | 000- 00-0            | 000- 00-0                       |

| 119h                   | DACCON1                           |                                                                                                           |                                |                |                 | D            | ACR<4:0>             |                      | •                    | 0 0000               | 0 0000                          |

| 11Ah                   | SRCON0                            | SRLEN                                                                                                     | SRCLK2                         | SRCLK1         | SRCLK0          | SRQEN        | SRNQEN               | SRPS                 | SRPR                 | 0000 0000            | 0000 0000                       |

| 11Bh                   | SRCON1                            | SRSPE                                                                                                     | SRSCKE                         | SRSC2E         | SRSC1E          | SRRPE        | SRRCKE               | SRRC2E               | SRRC1E               | 0000 0000            | 0000 0000                       |

| 11Ch                   | _                                 | Unimpleme                                                                                                 | nted                           |                |                 |              |                      | •                    | •                    | _                    | _                               |

| 11Dh                   | APFCON                            | _                                                                                                         | CCP3SEL                        | T1GSEL         | P2BSEL          | SRNQSEL      | C2OUTSEL             | SSSEL                | CCP2SEL              | -000 0000            | -000 0000                       |

| 11Eh                   | _                                 | Unimpleme                                                                                                 | nted                           |                | I               |              |                      | 1                    | 1                    | _                    | _                               |

| 11Fh                   | Unimplemented       Unimplemented |                                                                                                           |                                |                |                 |              |                      |                      |                      |                      |                                 |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-10.

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16(L)F1938 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

| Address                | Name    | Bit 7        | Bit 6                           | Bit 5          | Bit 4           | Bit 3         | Bit 2        | Bit 1     | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|---------|--------------|---------------------------------|----------------|-----------------|---------------|--------------|-----------|-------|----------------------|---------------------------------|

| Bank 3                 |         |              |                                 |                |                 |               |              |           |       |                      |                                 |

| 180h <sup>(2)</sup>    | INDF0   |              | this location<br>ical register) | uses contents  | s of FSR0H/F    | SR0L to addre | ess data me  | mory      |       | XXXX XXXX            | XXXX XXXX                       |

| 181h <sup>(2)</sup>    | INDF1   |              | this location<br>ical register) | uses contents  | s of FSR1H/F    | SR1L to addre | ess data me  | mory      |       | XXXX XXXX            | XXXX XXXX                       |

| 182h <sup>(2)</sup>    | PCL     | Program Co   | ounter (PC) L                   | east Significa | int Byte        |               |              |           |       | 0000 0000            | 0000 0000                       |

| 183h <sup>(2)</sup>    | STATUS  | _            | _                               | _              | TO              | PD            | Z            | DC        | С     | 1 1000               | q quuu                          |

| 184h <sup>(2)</sup>    | FSR0L   | Indirect Dat | ta Memory Ad                    | dress 0 Low    | Pointer         | •             | •            |           | •     | 0000 0000            | uuuu uuuu                       |

| 185h <sup>(2)</sup>    | FSR0H   | Indirect Dat | ta Memory Ad                    | ldress 0 High  | Pointer         |               |              |           |       | 0000 0000            | 0000 0000                       |

| 186h <sup>(2)</sup>    | FSR1L   | Indirect Dat | ta Memory Ad                    | dress 1 Low    | Pointer         |               |              |           |       | 0000 0000            | uuuu uuuu                       |

| 187h <sup>(2)</sup>    | FSR1H   | Indirect Dat | ta Memory Ad                    | Idress 1 High  | Pointer         |               |              |           |       | 0000 0000            | 0000 0000                       |

| 188h <sup>(2)</sup>    | BSR     | _            | _                               | _              |                 | E             | BSR<4:0>     |           |       | 0 0000               | 0 0000                          |

| 189h <sup>(2)</sup>    | WREG    | Working Re   | egister                         |                |                 |               |              |           |       | 0000 0000            | սսսս սսսս                       |

| 18Ah <sup>(1, 2)</sup> | PCLATH  | _            | Write Buffer                    | for the upper  | 7 bits of the F | Program Coun  | iter         |           |       | -000 0000            | -000 0000                       |

| 18Bh <sup>(2)</sup>    | INTCON  | GIE          | PEIE                            | TMR0IE         | INTE            | IOCIE         | TMR0IF       | INTF      | IOCIF | 0000 0000            | 0000 0000                       |

| 18Ch                   | ANSELA  | _            | _                               | ANSA5          | ANSA4           | ANSA3         | ANSA2        | ANSA1     | ANSA0 | 11 1111              |                                 |

| 18Dh                   | ANSELB  | _            | _                               | ANSB5          | ANSB4           | ANSB3         | ANSB2        | ANSB1     | ANSB0 | 11 1111              | 11 1111                         |

| 18Eh                   | _       | Unimpleme    | nted                            | L              |                 | 1             | 1            | 1         |       | _                    | _                               |

| 18Fh <sup>(3)</sup>    | ANSELD  | ANSD7        | ANSD6                           | ANSD5          | ANSD4           | ANSD3         | ANSD2        | ANSD1     | ANSD0 | 1111 1111            | 1111 1111                       |

| 190h <sup>(3)</sup>    | ANSELE  | _            | _                               | _              |                 | _             | ANSE2        | ANSE1     | ANSE0 | 111                  | 111                             |

| 191h                   | EEADRL  | EEPROM /     | Program Me                      | mory Address   | Register Lov    | v Byte        |              | 1         |       | 0000 0000            | 0000 0000                       |

| 192h                   | EEADRH  | (4)          | EEPROM / F                      | Program Mem    | ory Address     | Register High | Byte         |           |       | 1000 0000            | 1000 0000                       |

| 193h                   | EEDATL  | EEPROM /     |                                 |                | ata Register L  | <b>v</b> v    | ,            |           |       | XXXX XXXX            | uuuu uuuu                       |

| 194h                   | EEDATH  | _            | _                               |                |                 | ory Read Dat  | a Register H | liah Byte |       | xx xxxx              | uu uuuu                         |

| 195h                   | EECON1  | EEPGD        | CFGS                            | LWLO           | FREE            | WRERR         | WREN         | WR        | RD    |                      | 0000 q000                       |

| 196h                   | EECON2  | EEPROM of    | control registe                 | r 2            | l               | l             | l            | 1         |       |                      | 0000 0000                       |

| 197h                   | _       | -            | Unimplemented                   |                |                 |               |              |           |       | _                    | _                               |

| 198h                   | _       | Unimpleme    |                                 |                |                 |               |              |           |       | _                    | _                               |

| 199h                   | RCREG   |              | ceive Data R                    | eaister        |                 |               |              |           |       | 0000 0000            | 0000 0000                       |

| 19Ah                   | TXREG   | -            | insmit Data R                   | •              |                 |               |              |           |       |                      | 0000 0000                       |

| 19Bh                   | SPBRGL  |              |                                 | 0              | BRG<            | 7:0>          |              |           |       |                      | 0000 0000                       |

| 19Ch                   | SPBRGH  |              |                                 |                | BRG<1           | -             |              |           |       | 0000 0000            |                                 |

| 19Dh                   | RCSTA   | SPEN         | RX9                             | SREN           | CREN            | ADDEN         | FERR         | OERR      | RX9D  |                      | 0000 000x                       |

| 19Eh                   | TXSTA   | CSRC         | TX9                             | TXEN           | SYNC            | SENDB         | BRGH         | TRMT      | TX9D  |                      | 0000 0010                       |

| 19Fh                   | BAUDCON | ABDOVF       | RCIDL                           |                | SCKP            | BRG16         | 2            | WUE       | ABDEN |                      | 01-0 0-00                       |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-10.

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16(L)F1938 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

# 4.2 Register Definitions: Configuration

# REGISTER 4-1: CONFIGURATION WORD 1

|                      |                                                                                                                                                                                                                                                                                                                                                           | R/P-1/1                                                                                                                                         | R/P-1/1  | R/P-1/1         | R/P-1/1         | R/P-1/1    | R/P-1/1 |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------|-----------------|------------|---------|--|--|

|                      |                                                                                                                                                                                                                                                                                                                                                           | FCMEN                                                                                                                                           | IESO     | CLKOUTEN        | BORE            | N<1:0>     | CPD     |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                                           | bit 13                                                                                                                                          |          |                 |                 |            | bit     |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                 |          |                 |                 |            |         |  |  |

| R/P-1/1              | R/P-1/1                                                                                                                                                                                                                                                                                                                                                   | R/P-1/1                                                                                                                                         | R/P-1/1  | R/P-1/1         | R/P-1/1         | R/P-1/1    | R/P-1/1 |  |  |

| CP                   | MCLRE                                                                                                                                                                                                                                                                                                                                                     | PWRTE                                                                                                                                           | WDT      | E<1:0>          |                 | FOSC<2:0>  |         |  |  |

| bit7                 |                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                 |          |                 |                 |            | bit     |  |  |

| Legend:              |                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                 |          |                 |                 |            |         |  |  |

| R = Readable bit     |                                                                                                                                                                                                                                                                                                                                                           | P = Programma                                                                                                                                   | able bit | U = Unimpleme   | nted hit read a | s '1'      |         |  |  |

| '0' = Bit is cleared |                                                                                                                                                                                                                                                                                                                                                           | '1' = Bit is set                                                                                                                                |          | -n = Value wher |                 |            |         |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                 |          |                 |                 | Duik Llase |         |  |  |

| bit 13               | 1 = Fail-Safe Cl                                                                                                                                                                                                                                                                                                                                          | afe Clock Monitor E<br>ock Monitor is ena<br>ock Monitor is disa                                                                                | bled     |                 |                 |            |         |  |  |

| bit 12               | 1 = Internal/Exte                                                                                                                                                                                                                                                                                                                                         | IESO: Internal External Switchover bit<br>1 = Internal/External Switchover mode is enabled<br>0 = Internal/External Switchover mode is disabled |          |                 |                 |            |         |  |  |

| bit 11               | CLKOUTEN: Clock Out Enable bit<br>1 = CLKOUT function is disabled. I/O or oscillator function on RA6/CLKOUT<br>0 = CLKOUT function is enabled on RA6/CLKOUT                                                                                                                                                                                               |                                                                                                                                                 |          |                 |                 |            |         |  |  |

| bit 10-9             | BOREN<1:0>: Brown-out Reset Enable bits <sup>(1)</sup><br>11 = BOR enabled<br>10 = BOR enabled during operation and disabled in Sleep<br>01 = BOR controlled by SBOREN bit of the PCON register<br>00 = BOR disabled                                                                                                                                      |                                                                                                                                                 |          |                 |                 |            |         |  |  |

| bit 8                | 1 = Data memor                                                                                                                                                                                                                                                                                                                                            | e Protection bit <sup>(2)</sup><br>ry code protection<br>ry code protection                                                                     |          |                 |                 |            |         |  |  |

|                      |                                                                                                                                                                                                                                                                                                                                                           | emory code protect                                                                                                                              |          |                 |                 |            |         |  |  |

| bit 6                | <ul> <li>0 = Program memory code protection is enabled</li> <li>MCLRE: RE3/MCLR/VPP Pin Function Select bit If LVP bit = 1: This bit is ignored. If LVP bit = 0: 1 = RE3/MCLR/VPP pin function is MCLR; Weak pull-up enabled. 0 = RE3/MCLR/VPP pin function is digital input; MCLR internally disabled; Weak pull-up under control of WPUE3 bit</li></ul> |                                                                                                                                                 |          |                 |                 |            |         |  |  |

| bit 5                | bit.<br><b>PWRTE:</b> Power-up Timer Enable bit <sup>(1)</sup><br>1 = PWRT disabled<br>0 = PWRT enabled                                                                                                                                                                                                                                                   |                                                                                                                                                 |          |                 |                 |            |         |  |  |

|                      | WDTE<1:0>: Watchdog Timer Enable bit<br>11 = WDT enabled<br>10 = WDT enabled while running and disabled in Sleep<br>01 = WDT controlled by the SWDTEN bit in the WDTCON register<br>00 = WDT disabled                                                                                                                                                     |                                                                                                                                                 |          |                 |                 |            |         |  |  |

- 2: The entire data EEPROM will be erased when the code protection is turned off during an erase.

- **3:** The entire program memory will be erased when the code protection is turned off.

# 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Program memory protection and data EEPROM protection are controlled independently. Internal access to the program memory and data EEPROM are unaffected by any code protection setting.

#### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See Section 4.4 "Write Protection" for more information.

# 4.3.2 DATA EEPROM PROTECTION

The entire data EEPROM is protected from external reads and writes by the CPD bit. When CPD = 0, external reads and writes of data EEPROM are inhibited. The CPU can continue to read and write data EEPROM regardless of the protection bit settings.

# 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

# 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 4.6 "Device ID and Revision ID**" for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC16F193X/LF193X/PIC16F194X/LF194X/PIC16LF 190X Memory Programming Specification*" (DS41397).

### 5.4 Two-Speed Clock Start-up Mode

Two-Speed Start-up mode provides additional power savings by minimizing the latency between external oscillator start-up and code execution. In applications that make heavy use of the Sleep mode, Two-Speed Start-up will remove the external oscillator start-up time from the time spent awake and can reduce the overall power consumption of the device. This mode allows the application to wake-up from Sleep, perform a few instructions using the INTOSC internal oscillator block as the clock source and go back to Sleep without waiting for the external oscillator to become stable.

Two-Speed Start-up provides benefits when the oscillator module is configured for LP, XT, or HS modes. The Oscillator Start-up Timer (OST) is enabled for these modes and must count 1024 oscillations before the oscillator can be used as the system clock source.

If the oscillator module is configured for any mode other than LP, XT or HS mode, then Two-Speed Start-up is disabled. This is because the external clock oscillator does not require any stabilization time after POR or an exit from Sleep.

If the OST count reaches 1024 before the device enters Sleep mode, the OSTS bit of the OSCSTAT register is set and program execution switches to the external oscillator. However, the system may never operate from the external oscillator if the time spent awake is very short.

| Note: | Executing a SLEEP instruction will abort    |

|-------|---------------------------------------------|

|       | the oscillator start-up time and will cause |

|       | the OSTS bit of the OSCSTAT register to     |

|       | remain clear.                               |

#### 5.4.1 TWO-SPEED START-UP MODE CONFIGURATION

Two-Speed Start-up mode is configured by the following settings:

- IESO (of the Configuration Words) = 1; Internal/External Switchover bit (Two-Speed Start-up mode enabled).

- SCS (of the OSCCON register) = 00.

- FOSC<2:0> bits in the Configuration Words configured for LP, XT or HS mode.

Two-Speed Start-up mode is entered after:

- Power-on Reset (POR) and, if enabled, after Power-up Timer (PWRT) has expired, or

- Wake-up from Sleep.

| TABLE 5-1: O | SCILLATOR SWITCHING DELAYS |

|--------------|----------------------------|

|--------------|----------------------------|

| Switch From      | Switch To                                                                     | Frequency                                       | Oscillator Delay        |

|------------------|-------------------------------------------------------------------------------|-------------------------------------------------|-------------------------|

| Sleep/POR        | LFINTOSC <sup>(1)</sup><br>MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup> | 31 kHz<br>31.25 kHz-500 kHz<br>31.25 kHz-16 MHz | 2 cycles                |

| Sleep/POR        | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 2 cycles                |

| LFINTOSC         | EC, RC <sup>(1)</sup>                                                         | DC – 32 MHz                                     | 1 cycle of each         |

| Sleep/POR        | Timer1 Oscillator<br>LP, XT, HS <sup>(1)</sup>                                | 32 kHz-20 MHz                                   | 1024 Clock Cycles (OST) |

| Any clock source | MFINTOSC <sup>(1)</sup><br>HFINTOSC <sup>(1)</sup>                            | 31.25 kHz-500 kHz<br>31.25 kHz-16 MHz           | 2 μs (approx.)          |

| Any clock source | LFINTOSC <sup>(1)</sup>                                                       | 31 kHz                                          | 1 cycle of each         |

| Any clock source | Timer1 Oscillator                                                             | 32 kHz                                          | 1024 Clock Cycles (OST) |

| PLL inactive     | PLL active                                                                    | 16-32 MHz                                       | 2 ms (approx.)          |

Note 1: PLL inactive.

| FIGURE 7         | '-2: II       | NTERRUPT      | LATENCY           |                  |             |             |             |             |

|------------------|---------------|---------------|-------------------|------------------|-------------|-------------|-------------|-------------|

|                  |               |               |                   |                  |             |             |             |             |

| OSC1             |               |               |                   |                  |             |             |             |             |

|                  | Q1 Q2 Q3 Q4   | Q1 Q2 Q3 Q4   | Q1 Q2 Q3 Q4       | Q1 Q2 Q3 Q4      | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 | Q1 Q2 Q3 Q4 |

| CLKOUT           |               |               | Interru<br>during | pt Sampled<br>Q1 |             |             |             |             |

| Interrupt        |               |               |                   |                  |             |             |             |             |

| GIE              |               |               |                   |                  |             |             |             |             |

| PC               | PC-1          | PC            | PC                | +1               | 0004h       | 0005h       |             |             |

| Execute          | 1 Cycle Instr | uction at PC  | Inst(PC)          | NOP              | NOP         | Inst(0004h) |             |             |

|                  |               |               | /                 |                  |             |             |             |             |

| Interrupt<br>GIE |               | I             |                   |                  |             |             |             |             |

| PC               | PC-1          | PC            | PC+1/FSR<br>ADDR  | New PC/<br>PC+1  | 0004h       | 0005h       |             |             |

| Execute-         | 2 Cycle Instr | uction at PC  | Inst(PC)          | NOP              | NOP         | Inst(0004h) | L           |             |

|                  |               | /             |                   | 1                |             |             |             |             |

| Interrupt        |               |               |                   |                  |             |             |             |             |

| GIE              |               |               |                   |                  |             |             |             |             |

| PC               | PC-1          | PC            | FSR ADDR          | PC+1             | PC+2        | 0004h       | 0005h       |             |

| Execute          | 3 Cycle Instr | ruction at PC | INST(PC)          | NOP              | NOP         | NOP         | Inst(0004h) | Inst(0005h) |

| Interrupt        |               |               |                   |                  |             |             |             |             |

| GIE              |               |               |                   |                  |             |             |             |             |

| PC               | PC-1          | PC            | FSR ADDR          | PC+1             | PC          | +2          | 0004h       | 0005h       |

| Execute          | 3 Cycle Instr | ruction at PC | INST(PC)          | NOP              | NOP         | NOP         | NOP         | Inst(0004h) |

|                  |               |               |                   |                  |             |             |             |             |

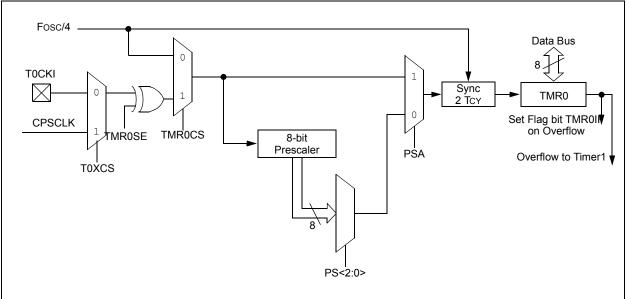

# 20.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (independent of Watchdog Timer)

- · Programmable internal or external clock source

- · Programmable external clock edge selection

- · Interrupt on overflow

- TMR0 can be used to gate Timer1

Figure 20-1 is a block diagram of the Timer0 module.

# 20.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 20.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION\_REG register.

FIGURE 20-1: BLOCK DIAGRAM OF THE TIMER0

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

Note: The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### 20.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin or the Capacitive Sensing Oscillator (CPSCLK) signal.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1' and resetting the T0XCS bit in the CPSCON0 register to '0'.

8-Bit Counter mode using the Capacitive Sensing Oscillator (CPSCLK) signal is selected by setting the TMR0CS bit in the OPTION\_REG register to '1' and setting the T0XCS bit in the CPSCON0 register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION\_REG register.

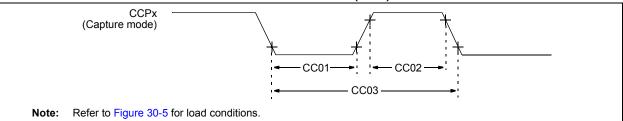

### 23.1 Capture Mode

The Capture mode function described in this section is available and identical for CCP modules ECCP1, ECCP2, ECCP3, CCP4 and CCP5.

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the CCPx pin, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMR1H:TMR1L register pair, respectively. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- · Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

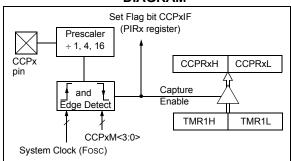

Figure 23-1 shows a simplified diagram of the Capture operation.

#### 23.1.1 CCP PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Also, the CCPx pin function can be moved to alternative pins using the APFCON register. Refer to **Section 12.1 "Alternate Pin Function**" for more details.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 23-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

### 23.1.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 21.0 "Timer1 Module with Gate Control" for more information on configuring Timer1.

#### 23.1.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in Operating mode.

| Note: | Clocking Timer1 from the system clock   |

|-------|-----------------------------------------|

|       | (Fosc) should not be used in Capture    |

|       | mode. In order for Capture mode to      |

|       | recognize the trigger event on the CCPx |

|       | pin, Timer1 must be clocked from the    |

|       | instruction clock (Fosc/4) or from an   |

|       | external clock source.                  |

#### 23.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 23-1 demonstrates the code to perform this function.

#### EXAMPLE 23-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCPxCON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCPxCON             |

| CLRF    | CCPxCON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ;the new prescaler      |

|         |             | ;move value and CCP ON  |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this |

|         |             | ;value                  |

### 23.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

When Timer1 is clocked by Fosc/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state. Capture mode will operate during Sleep when Timer1 is clocked by an external clock source.

| R/W-0/0       | ) R/W-0/0                                              | R/W-0/0                                                                                    | R/W-0/0              | R/W-0/0        | R/W-0/0                 | R/W-0/0        | R/W-0/0      |

|---------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------|----------------|-------------------------|----------------|--------------|

| CCPxAS        |                                                        | CCPxAS1                                                                                    | CCPxAS0              | 1              | .C<1:0>                 |                | D<1:0>       |

| bit 7         |                                                        |                                                                                            |                      |                |                         |                | bit 0        |

|               |                                                        |                                                                                            |                      |                |                         |                |              |

| Legend:       |                                                        |                                                                                            |                      |                |                         |                |              |

| R = Reada     | able bit                                               | W = Writable                                                                               | bit                  | U = Unimplen   | nented bit, read        | d as '0'       |              |

| u = Bit is u  | inchanged                                              | x = Bit is unki                                                                            | nown                 | -n/n = Value a | at POR and BO           | R/Value at all | other Resets |

| '1' = Bit is  | set                                                    | '0' = Bit is cle                                                                           | ared                 |                |                         |                |              |

| bit 7         | CCPxASE: (                                             | CPx Auto-Shu                                                                               | tdown Event S        | tatus bit      |                         |                |              |

|               |                                                        | wn event has o<br>tputs are opera                                                          |                      | outputs are in | shutdown state          | 9              |              |

| bit 6         | 1 = Auto-shu                                           | CPx Auto-Shu<br>utdown 2 sourc<br>utdown 2 sourc                                           | e is enabled, V      |                |                         |                |              |

| bit 5         | 1 = Auto-shu                                           | CPx Auto-Shu<br>utdown 1 sourc<br>utdown 1 sourc                                           | e is enabled, a      |                | ),(2) output low        |                |              |

| bit 4         | 1 = Auto-shi                                           | CPx Auto-Shu<br>utdown 0 source<br>utdown 0 source                                         | e is enabled, a      |                | <sup>)</sup> output low |                |              |

| bit 3-2       | 00 = Drive pi<br>01 = Drive pi                         | )>: Pins PxA and PxC tri-s | C to '0'<br>C to '1' | wn State Contr | ol bits                 |                |              |

| bit 1-0       | 00 <b>= Drive pi</b><br>01 <b>= Drive pi</b>           | D>: Pins PxB ar<br>ns PxB and Px<br>ns PxB and Px<br>B and PxD tri-s                       | D to '0'<br>D to '1' | wn State Contr | ol bits                 |                |              |

| Note 1:<br>2: | If CxSYNC is ena<br>async_CxOUT = a<br>async_CxOUT = a | async_C2OUT                                                                                | (for CCP1 and        |                | I.                      |                |              |

### REGISTER 23-4: CCPxAS: CCPX AUTO-SHUTDOWN CONTROL REGISTER

When one device is transmitting a logical one, or letting the line float, and a second device is transmitting a logical zero, or holding the line low, the first device can detect that the line is not a logical one. This detection, when used on the SCL line, is called clock stretching. Clock stretching gives slave devices a mechanism to control the flow of data. When this detection is used on the SDA line, it is called arbitration. Arbitration ensures that there is only one master device communicating at any single time.

# 24.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of Clock Stretching. An addressed slave device may hold the SCL clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCL line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCL connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

# 24.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission. It can do so without any complications, because so far, the transmission appears exactly as expected with no other transmitter disturbing the message. Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

If two master devices are sending a message to two different slave devices at the address stage, the master sending the lower slave address always wins arbitration. When two master devices send messages to the same slave address, and addresses can sometimes refer to multiple slaves, the arbitration process must continue into the data stage.

Arbitration usually occurs very rarely, but it is a necessary process for proper multi-master support.

# 24.4 I<sup>2</sup>C<sup>™</sup> Mode Operation

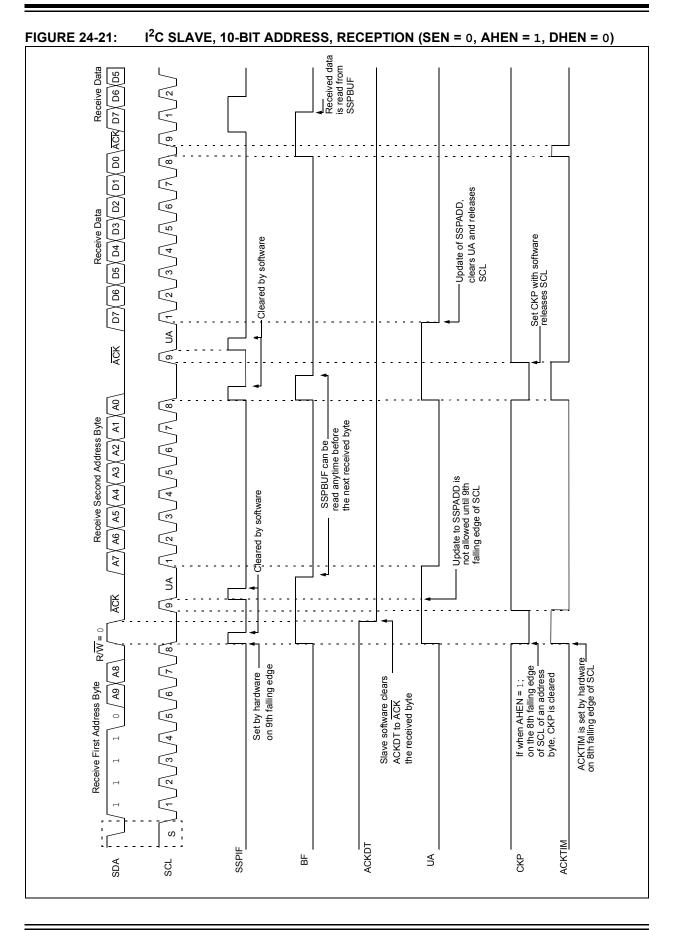

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and 2 interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

### 24.4.1 BYTE FORMAT

All communication in  $1^2$ C is done in 9-bit segments. A byte is sent from a Master to a Slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

# 24.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

### 24.4.3 SDA AND SCL PINS

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

**Note:** Data is tied to output zero when an I<sup>2</sup>C mode is enabled.

# 27.1 LCD Registers

The module contains the following registers:

- LCD Control register (LCDCON)

- LCD Phase register (LCDPS)

- LCD Reference Ladder register (LCDRL)

- LCD Contrast Control register (LCDCST)

- LCD Reference Voltage Control register (LCDREF)

- Up to three LCD Segment Enable registers (LCDSEn)

- Up to 12 LCD data registers (LCDDATAn)

# TABLE 27-1:LCD SEGMENT AND DATAREGISTERS

|               | # of LCD Registers |      |  |  |

|---------------|--------------------|------|--|--|

| Device        | Segment<br>Enable  | Data |  |  |

| PIC16(L)F1938 | 2                  | 8    |  |  |

| PIC16(L)F1939 | 3                  | 12   |  |  |

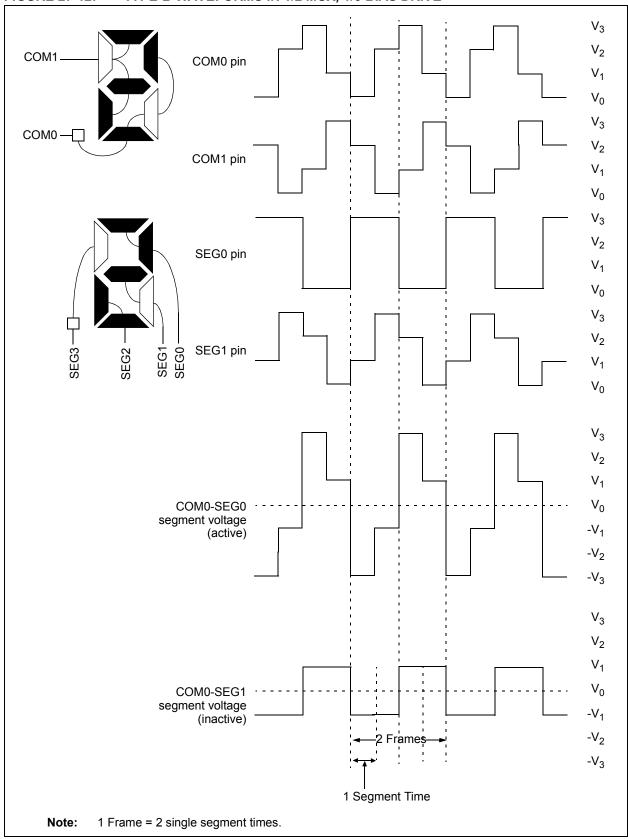

The LCDCON register (Register 27-1) controls the operation of the LCD Driver module. The LCDPS register (Register 27-2) configures the LCD clock source prescaler and the type of waveform; Type-A or Type-B. The LCDSEn registers (Register 27-5) configure the functions of the port pins.

The following LCDSEn registers are available:

- LCDSE0 SE<7:0>

- LCDSE1 SE<15:8>

- LCDSE2 SE<23:16>(1)

Note 1: PIC16(L)F1939 only.

Once the module is initialized for the LCD panel, the individual bits of the LCDDATAn registers are cleared/set to represent a clear/dark pixel, respectively:

- LCDDATA0 SEG<7:0>COM0

- LCDDATA1 SEG<15:8>COM0

- LCDDATA2 SEG<23:16>COM0<sup>(1)</sup>

- LCDDATA3 SEG<7:0>COM1

- LCDDATA4 SEG<15:8>COM1

- LCDDATA5 SEG<23:16>COM1<sup>(1)</sup>

- LCDDATA6 SEG<7:0>COM2

- LCDDATA7 SEG<15:8>COM2

- LCDDATA8 SEG<23:16>COM2<sup>(1)</sup>

- LCDDATA9 SEG<7:0>COM3

- LCDDATA10 SEG<15:8>COM3

- LCDDATA11 SEG<23:16>COM3<sup>(1)</sup>

| N   | lote 1  | 1: PIC16(L) | F1939 only. |    |          |

|-----|---------|-------------|-------------|----|----------|

| As  | an      | example,    | LCDDATAn    | is | detailed |

| Reg | ister 2 | 27-6.       |             |    |          |

in

Once the module is configured, the LCDEN bit of the LCDCON register is used to enable or disable the LCD module. The LCD panel can also operate during Sleep by clearing the SLPEN bit of the LCDCON register.

### REGISTER 27-2: LCDPS: LCD PHASE REGISTER

| R/W-0/0          | R/W-0/0                                                | R-0/0                      | R-0/0         | R/W-0/0        | R/W-0/0          | R/W-1/1          | R/W-1/1      |  |  |  |

|------------------|--------------------------------------------------------|----------------------------|---------------|----------------|------------------|------------------|--------------|--|--|--|

| WFT              | BIASMD                                                 | LCDA                       | WA            |                | LP<              | :3:0>            |              |  |  |  |

| bit 7            | •                                                      |                            |               |                |                  |                  | bit 0        |  |  |  |

|                  |                                                        |                            |               |                |                  |                  |              |  |  |  |

| Legend:          |                                                        |                            |               |                |                  |                  |              |  |  |  |

| R = Readable     | bit                                                    | W = Writable bit           |               | U = Unimpler   | nented bit, read | 1 as '0'         |              |  |  |  |

| u = Bit is unch  | anged                                                  | x = Bit is unk             | nown          | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is set |                                                        | '0' = Bit is cleared       |               | C = Only clea  | rable bit        |                  |              |  |  |  |