Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

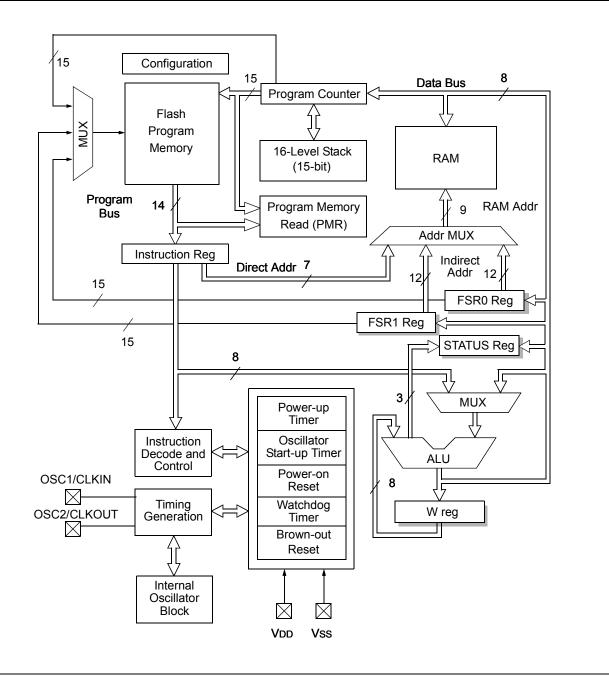

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1938-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0/0        | R/W-0/0                             | R/W-0/0                   | R/W-0/0         | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|----------------|-------------------------------------|---------------------------|-----------------|----------------|------------------|------------------|-------------|

|                | CCP5IF                              | CCP4IF                    | CCP3IF          | TMR6IF         | —                | TMR4IF           | _           |

| bit 7          |                                     |                           |                 |                |                  |                  | bit 0       |

|                |                                     |                           |                 |                |                  |                  |             |

| Legend:        |                                     |                           |                 |                |                  |                  |             |

| R = Readab     | ole bit                             | W = Writable              | bit             | U = Unimpler   | mented bit, read | l as '0'         |             |

| u = Bit is un  | changed                             | x = Bit is unki           | nown            | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is s | et                                  | '0' = Bit is cle          | ared            |                |                  |                  |             |

|                |                                     |                           |                 |                |                  |                  |             |

| bit 7          | -                                   | nted: Read as '           |                 |                |                  |                  |             |

| bit 6          |                                     | P5 Interrupt Fla          | ıg bit          |                |                  |                  |             |

|                | 1 = Interrupt                       | is pending is not pending |                 |                |                  |                  |             |

| bit 5          | •                                   | P4 Interrupt Fla          | a hit           |                |                  |                  |             |

| DIL D          | 1 = Interrupt                       | -                         |                 |                |                  |                  |             |

|                |                                     | is not pending            |                 |                |                  |                  |             |

| bit 4          | CCP3IF: CC                          | P3 Interrupt Fla          | ıg bit          |                |                  |                  |             |

|                | 1 = Interrupt                       |                           |                 |                |                  |                  |             |

|                |                                     | is not pending            |                 |                |                  |                  |             |

| bit 3          |                                     | R6 to PR6 Mat             | ch Interrupt FI | ag bit         |                  |                  |             |

|                | 1 = Interrupt                       | is pending is not pending |                 |                |                  |                  |             |

| bit 2          | •                                   | nted: Read as '           | 0'              |                |                  |                  |             |

| bit 1          | •                                   | R4 to PR4 Mat             |                 | aq bit         |                  |                  |             |

|                | 1 = Interrupt                       |                           |                 |                |                  |                  |             |

|                |                                     | is not pending            |                 |                |                  |                  |             |

| bit 0          | Unimplemer                          | nted: Read as '           | 0'              |                |                  |                  |             |

|                |                                     |                           |                 |                |                  |                  |             |

| Note:          | nterrupt flag bits a                | are set when an           | interrupt       |                |                  |                  |             |

|                | condition occurs, r                 |                           |                 |                |                  |                  |             |

|                | ts corresponding                    |                           |                 |                |                  |                  |             |

|                | Enable bit, GIE, d<br>Jser software |                           | -               |                |                  |                  |             |

|                | noropriate interru                  |                           |                 |                |                  |                  |             |

#### **REGISTER 7-7: PIR3: PERIPHERAL INTERRUPT REQUEST REGISTER 3**

appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### **10.1** Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See the Electrical Specifications Chapters for the LFINTOSC tolerances.

#### 10.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 10-1.

#### 10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 10.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 10-1 for more details.

| TABLE 10-1: | WDT OPERATING MODES |

|-------------|---------------------|

|-------------|---------------------|

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 10        | 37     | Awake          | Active      |

| 10        | Х      | Sleep          | Disabled    |

| 0.1       | 1      | х              | Active      |

| 01        | 0      | ~              | Disabled    |

| 00        | Х      | Х              | Disabled    |

#### TABLE 10-2: WDT CLEARING CONDITIONS

#### 10.3 Time-Out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is 2 seconds.

#### 10.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- · Oscillator fail

- WDT is disabled

- Oscillator Start-up TImer (OST) is running

See Table 10-2 for more information.

#### 10.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See Section 5.0 "Oscillator Module (With Fail-Safe Clock Monitor)" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. See **Section 3.0** "Memory Organization" and STATUS register (Register 3-1) for more information.

| Conditions                                               | WDT                          |

|----------------------------------------------------------|------------------------------|

| WDTE<1:0> = 00                                           |                              |

| WDTE<1:0> = 01 and SWDTEN = 0                            |                              |

| WDTE<1:0> = 10 and enter Sleep                           | Cleared                      |

| CLRWDT Command                                           | Cleared                      |

| Oscillator Fail Detected                                 |                              |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |

| Change INTOSC divider (IRCF bits)                        | Unaffected                   |

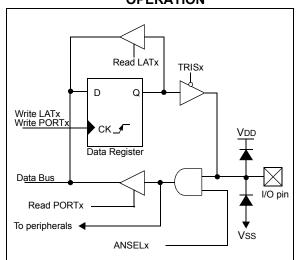

#### 12.0 I/O PORTS

Each port has three standard registers for its operation. These registers are:

- TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- · LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- ANSELx (analog select)

- WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

## TABLE 12-1: PORT AVAILABILITY PER DEVICE

| Device     | PORTA | PORTB | PORTC |

|------------|-------|-------|-------|

| PIC16F1933 | ٠     | ٠     |       |

| PIC16F1934 | •     | •     | •     |

#### TABLE 12-2: PORT AVAILABILITY PER DEVICE

| Device        | PORTA | PORTB | PORTC | PORTD | PORTE |

|---------------|-------|-------|-------|-------|-------|

| PIC16(L)F1938 | ٠     | ٠     | ٠     |       | ٠     |

| PIC16(L)F1939 | ٠     | ٠     | •     | •     | •     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 12-1.

#### FIGURE 12-1: GENERIC I/O PORT OPERATION

#### EXAMPLE 12-1: INITIALIZING PORTA

| ; | This | code | example | illustrates |  |

|---|------|------|---------|-------------|--|

| ; | This | coae | examp⊥e | lllustrates |  |

- ; initializing the PORTA register. The

- ; other ports are initialized in the same

- ; manner.

| BANKSEL | PORTA       | ;                      |

|---------|-------------|------------------------|

| CLRF    | PORTA       | ;Init PORTA            |

| BANKSEL | LATA        | ;Data Latch            |

| CLRF    | LATA        | ;                      |

| BANKSEL | ANSELA      | ;                      |

| CLRF    | ANSELA      | ;digital I/O           |

| BANKSEL | TRISA       | ;                      |

| MOVLW   | B'00111000' | ;Set RA<5:3> as inputs |

| MOVWF   | TRISA       | ;and set RA<2:0> as    |

|         |             | ;outputs               |

|         |             |                        |

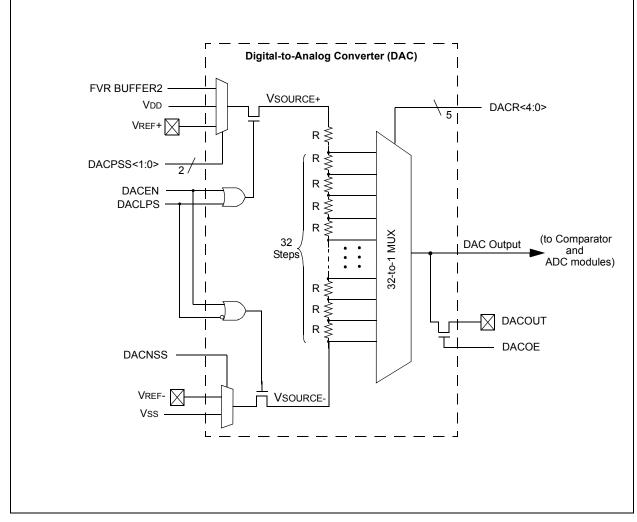

#### 17.0 DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The input of the DAC can be connected to:

- External VREF pins

- VDD supply voltage

- FVR (Fixed Voltage Reference)

The output of the DAC can be configured to supply a reference voltage to the following:

- Comparator positive input

- ADC input channel

- DACOUT pin

- Capacitive Sensing module (CPS)

The Digital-to-Analog Converter (DAC) can be enabled by setting the DACEN bit of the DACCON0 register.

#### EQUATION 17-1: DAC OUTPUT VOLTAGE

# $\frac{IF DACEN = 1}{VOUT} = \left( (VSOURCE+ - VSOURCE-) \times \frac{DACR[4:0]}{2^5} \right) + VSOURCE \frac{IF DACEN = 0 \& DACLPS = 1 \& DACR[4:0] = 11111}{VOUT} = VSOURCE +$

#### <u>IF DACEN = 0 & DACLPS = 0 & DACR[4:0] = 00000</u>

VOUT = VSOURCE -

VSOURCE+ = VDD, VREF, or FVR BUFFER 2

VSOURCE - = VSS

#### 17.2 Ratiometric Output Level

The DAC output value is derived using a resistor ladder with each end of the ladder tied to a positive and negative voltage reference input source. If the voltage of either input source fluctuates, a similar fluctuation will result in the DAC output value.

The value of the individual resistors within the ladder can be found in Section 30.0 "Electrical Specifications".

#### 17.1 Output Voltage Selection

The DAC has 32 voltage level ranges. The 32 levels are set with the DACR<4:0> bits of the DACCON1 register.

The DAC output voltage is determined by the following equations:

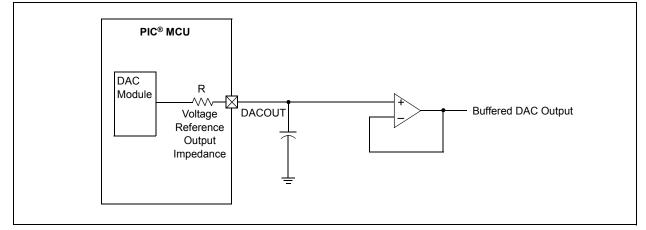

#### 17.3 DAC Voltage Reference Output

The DAC can be output to the DACOUT pin by setting the DACOE bit of the DACCON0 register to '1'. Selecting the DAC reference voltage for output on the DACOUT pin automatically overrides the digital output buffer and digital input threshold detector functions of that pin. Reading the DACOUT pin when it has been configured for DAC reference voltage output will always return a '0'.

Due to the limited current drive capability, a buffer must be used on the DAC voltage reference output for external connections to DACOUT. Figure 17-2 shows an example buffering technique.

#### FIGURE 17-1: DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM

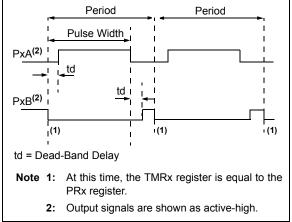

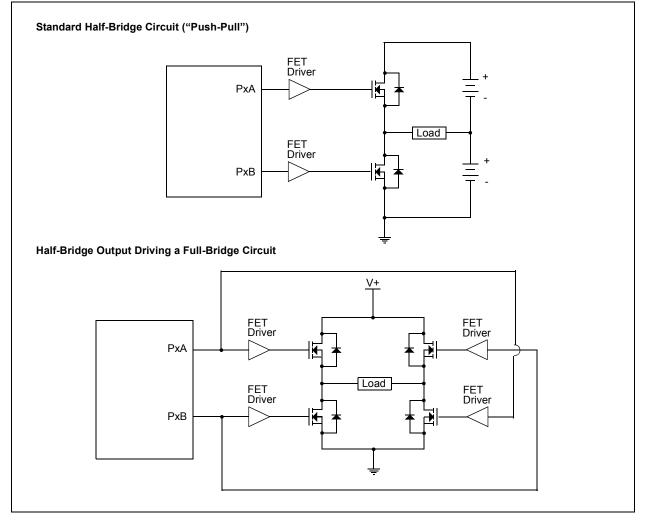

#### 23.4.1 HALF-BRIDGE MODE

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCPx/PxA pin, while the complementary PWM output signal is output on the PxB pin (see Figure 23-9). This mode can be used for Half-Bridge applications, as shown in Figure 23-9, or for Full-Bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in Half-Bridge power devices. The value of the PDC<6:0> bits of the PWMxCON register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See Section 23.4.5 "Programmable Dead-Band Delay Mode" for more details of the dead-band delay operations. Since the PxA and PxB outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure PxA and PxB as outputs.

#### FIGURE 23-8: EXAMPLE OF HALF-BRIDGE PWM OUTPUT

#### FIGURE 23-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

| U-0             | U-0        | U-0               | U-0       | U-0            | U-0              | R/W-0/0          | R/W-0/0      |

|-----------------|------------|-------------------|-----------|----------------|------------------|------------------|--------------|

| _               | —          | —                 | _         | —              | —                | C5TSE            | L<1:0>       |

| bit 7           |            |                   |           |                |                  |                  | bit 0        |

|                 |            |                   |           |                |                  |                  |              |

| Legend:         |            |                   |           |                |                  |                  |              |

| R = Readab      | le bit     | W = Writable      | bit       | U = Unimplen   | nented bit, read | l as '0'         |              |

| u = Bit is und  | changed    | x = Bit is unkr   | nown      | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is se | et         | '0' = Bit is clea | ared      |                |                  |                  |              |

|                 |            |                   |           |                |                  |                  |              |

| bit 7-2         | Unimplemen | ted: Read as '    | 0'        |                |                  |                  |              |

| bit 1-0         | C5TSEL<1:0 | >: CCP5 Timer     | Selection |                |                  |                  |              |

#### REGISTER 23-3: CCPTMRS1: PWM TIMER SELECTION CONTROL REGISTER 1

DIT 1-0 00 = CCP5 is based off Timer2 in PWM mode

01 = CCP5 is based off Timer4 in PWM mode

10 = CCP5 is based off Timer6 in PWM mode

11 = Reserved

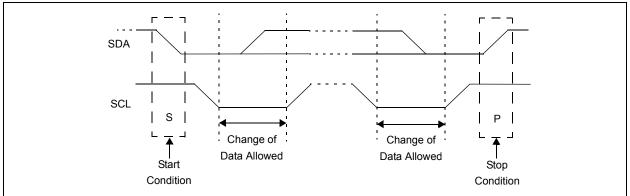

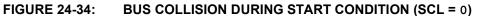

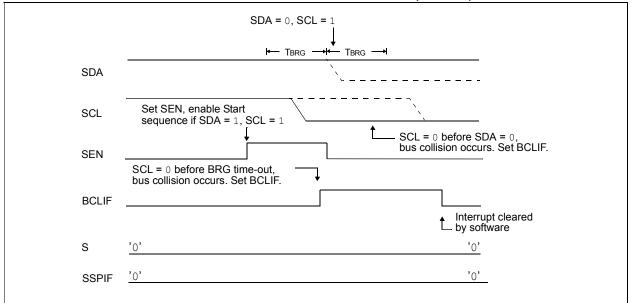

#### 24.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDA from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 24-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDA line low before asserting it low. This does not conform to the  $I^2C$  Specification that states no bus collision can occur on a Start.

#### 24.4.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low-to-high state while the SCL line is high.

Note: At least one SCL low time must appear before a Stop is valid, therefore, if the SDA line goes low then high again while the SCL line stays high, only the Start condition is detected.

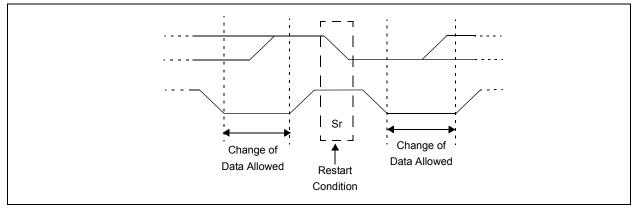

#### 24.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart

#### FIGURE 24-12: I<sup>2</sup>C START AND STOP CONDITIONS

has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the  $R/\overline{W}$  bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with  $R/\overline{W}$  clear in 10-bit mode, a prior match flag is set and maintained. Until a Stop condition, a high address with  $R/\overline{W}$  clear, or high address match fails.

#### 24.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

#### FIGURE 24-13: I<sup>2</sup>C RESTART CONDITION

#### FIGURE 24-35: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

#### 25.1.2 EUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 25-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the EUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 25.1.2.1 Enabling the Receiver

The EUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other EUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the EUSART. Clearing the SYNC bit of the TXSTA register configures the EUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the EUSART. The programmer must set the corresponding TRIS bit to configure the RX/DT I/O pin as an input.

**Note 1:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

#### 25.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. See Section 25.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the EUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| Note: | If the receive FIFO is overrun, no additi<br>characters will be received until the over<br>condition is cleared. See Section 25.1 | errun |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|-------|

|       | "Receive Overrun Error" for r                                                                                                     |       |

|       | information on overrun errors.                                                                                                    |       |

#### 25.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the EUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- · RCIE interrupt enable bit of the PIE1 register

- PEIE peripheral interrupt enable bit of the INTCON register

- GIE global interrupt enable bit of the INTCON register

The RCIF interrupt flag bit will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

#### 27.2 Register Definitions: LCD Control

#### REGISTER 27-1: LCDCON: LIQUID CRYSTAL DISPLAY (LCD) CONTROL REGISTER

| R/W-0/0                              | R/W-0/0                                                                                                                               | R/C-0/0                                                                                                                                                           | U-0                  | R/W-0/0                                                                                                         | R/W-0/0          | R/W-1/1                | R/W-1/1        |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------|------------------|------------------------|----------------|

| LCDEN                                | SLPEN                                                                                                                                 | WERR                                                                                                                                                              |                      | CS<                                                                                                             | <1:0>            | LMU                    | X<1:0>         |

| bit 7                                |                                                                                                                                       |                                                                                                                                                                   |                      |                                                                                                                 |                  | 1                      | bit            |

|                                      |                                                                                                                                       |                                                                                                                                                                   |                      |                                                                                                                 |                  |                        |                |

| Legend:                              |                                                                                                                                       |                                                                                                                                                                   |                      |                                                                                                                 |                  |                        |                |

| R = Readab                           | le bit                                                                                                                                | W = Writable bit                                                                                                                                                  | U                    | = Unimplen                                                                                                      | nented bit, read | d as '0'               |                |

| u = Bit is un                        | •                                                                                                                                     | x = Bit is unknow                                                                                                                                                 | vn -n                | /n = Value a                                                                                                    | t POR and BO     | R/Value at all         | other Resets   |

| '1' = Bit is se                      | et                                                                                                                                    | '0' = Bit is cleare                                                                                                                                               | ed C                 | = Only clea                                                                                                     | rable bit        |                        |                |

| h:+ 7                                |                                                                                                                                       | ) Driver Enable bi                                                                                                                                                |                      |                                                                                                                 |                  |                        |                |

| bit 7                                | -                                                                                                                                     | er module is enab                                                                                                                                                 |                      |                                                                                                                 |                  |                        |                |

|                                      | -                                                                                                                                     | er module is disal                                                                                                                                                |                      |                                                                                                                 |                  |                        |                |

| bit 6                                | SLPEN: LCD                                                                                                                            | Driver Enable in                                                                                                                                                  | Sleep Mode bi        | t                                                                                                               |                  |                        |                |

|                                      |                                                                                                                                       | er module is disal                                                                                                                                                |                      |                                                                                                                 |                  |                        |                |

|                                      | 0 = LCD Driv                                                                                                                          | er module is enab                                                                                                                                                 | oled in Sleep m      | ode                                                                                                             |                  |                        |                |

|                                      |                                                                                                                                       |                                                                                                                                                                   |                      |                                                                                                                 |                  |                        |                |

| bit 5                                | -                                                                                                                                     | Write Failed Error                                                                                                                                                |                      |                                                                                                                 |                  |                        |                |

| bit 5                                | 1 = LCDDAT                                                                                                                            | An register writte                                                                                                                                                |                      | /A bit of the                                                                                                   | e LCDPS regis    | ster = 0 (must         | be cleared i   |

| bit 5                                | -                                                                                                                                     | An register writte                                                                                                                                                |                      | /A bit of the                                                                                                   | e LCDPS regis    | ster = 0 (must         | be cleared i   |

|                                      | 1 = LCDDAT<br>software<br>0 = No LCD v                                                                                                | An register writte                                                                                                                                                |                      | /A bit of the                                                                                                   | e LCDPS regis    | ster = 0 (must         | be cleared i   |

| bit 4                                | 1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen                                                                                  | An register writte<br>)<br>write error                                                                                                                            | en while the W       | /A bit of the                                                                                                   | e LCDPS regis    | ster = 0 (must         | be cleared in  |

| bit 4                                | 1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clo<br>00 = Fosc/25                                                  | An register writte<br>)<br>write error<br>nted: Read as '0'<br>ock Source Select                                                                                  | en while the W       | /A bit of the                                                                                                   | e LCDPS regis    | ster = 0 (must         | be cleared in  |

| bit 4                                | 1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clo<br>00 = Fosc/25<br>01 = T1OSC                                    | An register writte<br>)<br>write error<br>nted: Read as '0'<br>nck Source Select<br>56<br>(Timer1)                                                                | en while the W       | /A bit of the                                                                                                   | e LCDPS regis    | ster = 0 (must         | be cleared in  |

| bit 4<br>bit 3-2                     | 1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clo<br>00 = Fosc/25<br>01 = T1OSC<br>1x = LFINTO                     | An register writte<br>)<br>write error<br>hted: Read as '0'<br>ock Source Select<br>56<br>(Timer1)<br>SC (31 kHz)                                                 | en while the W       | /A bit of the                                                                                                   | e LCDPS regis    | ster = 0 (must         | be cleared in  |

| bit 5<br>bit 4<br>bit 3-2<br>bit 1-0 | 1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clo<br>00 = Fosc/25<br>01 = T1OSC<br>1x = LFINTO                     | An register writte<br>)<br>write error<br>nted: Read as '0'<br>nck Source Select<br>56<br>(Timer1)                                                                | en while the W       |                                                                                                                 |                  |                        | be cleared in  |

| bit 4<br>bit 3-2                     | 1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clo<br>00 = Fosc/25<br>01 = T1OSC<br>1x = LFINTO<br>LMUX<1:0>:       | An register writte<br>)<br>write error<br>nted: Read as '0'<br>ock Source Select<br>56<br>(Timer1)<br>SC (31 kHz)<br>Commons Select                               | en while the W       |                                                                                                                 | e LCDPS regis    |                        |                |

| bit 4<br>bit 3-2                     | 1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clo<br>00 = Fosc/25<br>01 = T1OSC<br>1x = LFINTO                     | An register writte<br>)<br>write error<br>hted: Read as '0'<br>ock Source Select<br>56<br>(Timer1)<br>SC (31 kHz)                                                 | bits                 |                                                                                                                 | Number of Pixe   |                        | be cleared in  |

| bit 4<br>bit 3-2                     | 1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clo<br>00 = Fosc/25<br>01 = T1OSC<br>1x = LFINTO<br>LMUX<1:0>:       | An register writte<br>)<br>write error<br>nted: Read as '0'<br>ock Source Select<br>56<br>(Timer1)<br>SC (31 kHz)<br>Commons Select                               | bits                 | Maximum 1                                                                                                       | Number of Pixe   | ls                     |                |

| bit 4<br>bit 3-2                     | 1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clo<br>00 = Fosc/25<br>01 = T1OSC<br>1x = LFINTO<br>LMUX<1:0>:       | An register writte<br>)<br>write error<br>hted: Read as '0'<br>ock Source Select<br>(Timer1)<br>SC (31 kHz)<br>Commons Select<br>Multiplex                        | bits PIC16(I 1       | Maximum | Number of Pixe   | els<br>6(L)F1939       | – Bias         |

| bit 4<br>bit 3-2                     | 1 = LCDDAT<br>software<br>0 = No LCD v<br>Unimplemen<br>CS<1:0>: Clo<br>00 = Fosc/25<br>01 = T1OSC<br>1x = LFINTO<br>LMUX<1:0>:<br>00 | An register writte<br>)<br>write error<br>nted: Read as '0'<br>ock Source Select<br>56<br>(Timer1)<br>SC (31 kHz)<br>Commons Select<br>Multiplex<br>Static (COM0) | t bits PIC16(I 1 3 4 | Maximum M<br>_)F1938                                                                                            | Number of Pixe   | els<br>6(L)F1939<br>24 | Bias<br>Static |

Note 1: On these devices, COM3 and SEG15 are shared on one pin, limiting the device from driving 64 pixels.

#### REGISTER 27-2: LCDPS: LCD PHASE REGISTER

| R/W-0/0          | R/W-0/0                     | R-0/0                                      | R-0/0             | R/W-0/0        | R/W-0/0          | R/W-1/1          | R/W-1/1      |  |  |  |

|------------------|-----------------------------|--------------------------------------------|-------------------|----------------|------------------|------------------|--------------|--|--|--|

| WFT              | BIASMD                      | LCDA                                       | WA                |                | LP<              | :3:0>            |              |  |  |  |

| bit 7            |                             |                                            |                   |                |                  |                  | bit 0        |  |  |  |

|                  |                             |                                            |                   |                |                  |                  |              |  |  |  |

| Legend:          |                             |                                            |                   |                |                  |                  |              |  |  |  |

| R = Readable     | bit                         | W = Writable                               | bit               | U = Unimpler   | nented bit, read | 1 as '0'         |              |  |  |  |

| u = Bit is unch  | nanged                      | x = Bit is unknown<br>'0' = Bit is cleared |                   | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is set |                             |                                            |                   | C = Only clea  | rable bit        |                  |              |  |  |  |

|                  |                             |                                            |                   |                |                  |                  |              |  |  |  |

| bit 7            | WFT: Wavefo                 | orm Type bit                               |                   |                |                  |                  |              |  |  |  |

|                  |                             | phase changes                              |                   |                |                  |                  |              |  |  |  |

|                  | • • • •                     | bhase changes                              |                   | common type    |                  |                  |              |  |  |  |

| bit 6            |                             | as Mode Select                             | bit               |                |                  |                  |              |  |  |  |

|                  | When LMUX                   |                                            | t a at this hit t | - (1 )         |                  |                  |              |  |  |  |

|                  | When LMUX                   | as mode (do no<br><1:0> = 01:              |                   | J⊥)            |                  |                  |              |  |  |  |

|                  | 1 = 1/2 Bias I              |                                            |                   |                |                  |                  |              |  |  |  |

|                  | 0 = 1/3 Bias I              | mode                                       |                   |                |                  |                  |              |  |  |  |

|                  | When LMUX                   |                                            |                   |                |                  |                  |              |  |  |  |

|                  |                             | = 1/2 Bias mode                            |                   |                |                  |                  |              |  |  |  |

|                  | 0 = 1/3 Bias i<br>When LMUX |                                            |                   |                |                  |                  |              |  |  |  |

|                  |                             | mode (do not s                             | et this bit to '  | 1')            |                  |                  |              |  |  |  |

| bit 5            |                             | Active Status b                            |                   | ,              |                  |                  |              |  |  |  |

|                  |                             | er module is a                             | ctive             |                |                  |                  |              |  |  |  |

|                  | 0 = LCD Driv                | er module is in                            | active            |                |                  |                  |              |  |  |  |

| bit 4            | WA: LCD Wr                  | ite Allow Status                           | s bit             |                |                  |                  |              |  |  |  |

|                  |                             | the LCDDATA<br>the LCDDATA                 |                   |                |                  |                  |              |  |  |  |

| bit 3-0          | LP<3:0>: LC                 | D Prescaler Se                             | election bits     |                |                  |                  |              |  |  |  |

|                  | 1111 <b>= 1:16</b>          |                                            |                   |                |                  |                  |              |  |  |  |

|                  | 1110 = 1:15                 |                                            |                   |                |                  |                  |              |  |  |  |

|                  | 1101 = 1:14<br>1100 = 1:13  |                                            |                   |                |                  |                  |              |  |  |  |

|                  | 1011 = 1:12                 |                                            |                   |                |                  |                  |              |  |  |  |

|                  | 1010 <b>= 1:11</b>          |                                            |                   |                |                  |                  |              |  |  |  |

|                  | 1001 = 1:10                 |                                            |                   |                |                  |                  |              |  |  |  |

|                  | 1000 = 1:9<br>0111 = 1:8    |                                            |                   |                |                  |                  |              |  |  |  |

|                  | 0110 = 1:7                  |                                            |                   |                |                  |                  |              |  |  |  |

|                  | 0101 = 1:6                  |                                            |                   |                |                  |                  |              |  |  |  |

|                  | 0100 = 1:5<br>0011 = 1:4    |                                            |                   |                |                  |                  |              |  |  |  |

|                  | 0011 = 1.4<br>0010 = 1:3    |                                            |                   |                |                  |                  |              |  |  |  |

|                  | 0001 = 1:2                  |                                            |                   |                |                  |                  |              |  |  |  |

|                  | 0000 = 1:1                  |                                            |                   |                |                  |                  |              |  |  |  |

#### 27.12 Operation During Sleep

The LCD module can operate during Sleep. The selection is controlled by bit SLPEN of the LCDCON register. Setting the SLPEN bit allows the LCD module to go to Sleep. Clearing the SLPEN bit allows the module to continue to operate during Sleep.

If a SLEEP instruction is executed and SLPEN = 1, the LCD module will cease all functions and go into a very low-current consumption mode. The module will stop operation immediately and drive the minimum LCD voltage on both segment and common lines. Figure 27-20 shows this operation.

The LCD module can be configured to operate during Sleep. The selection is controlled by bit SLPEN of the LCDCON register. Clearing SLPEN and correctly configuring the LCD module clock will allow the LCD module to operate during Sleep. Setting SLPEN and correctly executing the LCD module shutdown will disable the LCD module during Sleep and save power.

If a SLEEP instruction is executed and SLPEN = 1, the LCD module will immediately cease all functions, drive the outputs to Vss and go into a very low-current mode. The SLEEP instruction should only be executed after the LCD module has been disabled and the current cycle completed, thus ensuring that there are no DC voltages on the glass. To disable the LCD module, clear the LCDEN bit. The LCD module will complete the disabling process after the current frame, clear the LCDA bit and optionally cause an interrupt.

The steps required to properly enter Sleep with the LCD disabled are:

- Clear LCDEN

- Wait for LCDA = 0 either by polling or by interrupt

- Execute SLEEP

If SLPEN = 0 and SLEEP is executed while the LCD module clock source is FOSC/4, then the LCD module will halt with the pin driving the last LCD voltage pattern. Prolonged exposure to a fixed LCD voltage pattern will cause damage to the LCD glass. To prevent LCD glass damage, either perform the proper LCD module shutdown prior to Sleep, or change the LCD module clock to allow the LCD module to continue operation during Sleep.

If a SLEEP instruction is executed and SLPEN = 0 and the LCD module clock is either T1OSC or LFINTOSC, the module will continue to display the current contents of the LCDDATA registers. While in Sleep, the LCD data cannot be changed. If the LCDIE bit is set, the device will wake from Sleep on the next LCD frame boundary. The LCD module current consumption will not decrease in this mode; however, the overall device power consumption will be lower due to the shutdown of the CPU and other peripherals. Table 27-8 shows the status of the LCD module during a Sleep while using each of the three available clock sources.

| Note: | When the LCDEN bit is cleared, the LCD       |

|-------|----------------------------------------------|

|       | module will be disabled at the completion    |

|       | of frame. At this time, the port pins will   |

|       | revert to digital functionality. To minimize |

|       | power consumption due to floating digital    |

|       | inputs, the LCD pins should be driven low    |

|       | using the PORT and TRIS registers.           |

|       |                                              |

If a SLEEP instruction is executed and SLPEN = 0, the module will continue to display the current contents of the LCDDATA registers. To allow the module to continue operation while in Sleep, the clock source must be either the LFINTOSC or T1OSC external oscillator. While in Sleep, the LCD data cannot be changed. The LCD module current consumption will not decrease in this mode; however, the overall consumption of the device will be lower due to shut down of the core and other peripheral functions.

Table 27-8 shows the status of the LCD module during Sleep while using each of the three available clock sources:

| TABLE 27-8: | LCD MODULE STATUS |

|-------------|-------------------|

|             | DURING SLEEP      |

| Clock Source | SLPEN | Operational<br>During Sleep |

|--------------|-------|-----------------------------|

| T1OSC        | 0     | Yes                         |

| 11030        | 1     | No                          |

| LFINTOSC     | 0     | Yes                         |

| LEINTOSC     | 1     | No                          |

| Fosc/4       | 0     | No                          |

| F05C/4       | 1     | No                          |

| Note: | The LFINTOSC or external T1OSC         |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|

|       | oscillator must be used to operate the |  |  |  |  |  |

|       | LCD module during Sleep.               |  |  |  |  |  |

If LCD interrupts are being generated (Type-B waveform with a multiplex mode not static) and LCDIE = 1, the device will awaken from Sleep on the next frame boundary.

## FIGURE 29-1: GENERAL FORMAT FOR INSTRUCTIONS

| Byte-oriented file register operations 13 8 7 6 0                                     |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------|--|--|--|--|--|--|

| OPCODE d f (FILE #)                                                                   |  |  |  |  |  |  |

| d = 0 for destination W<br>d = 1 for destination f<br>f = 7-bit file register address |  |  |  |  |  |  |

| Bit-oriented file register operations                                                 |  |  |  |  |  |  |

| OPCODE b (BIT #) f (FILE #)                                                           |  |  |  |  |  |  |

| b = 3-bit bit address<br>f = 7-bit file register address                              |  |  |  |  |  |  |

| Literal and control operations                                                        |  |  |  |  |  |  |

| General                                                                               |  |  |  |  |  |  |

| 13 8 7 0<br>OPCODE k (literal)                                                        |  |  |  |  |  |  |

| k = 8-bit immediate value                                                             |  |  |  |  |  |  |

| CALL and GOTO instructions only                                                       |  |  |  |  |  |  |

| 13 11 10 0                                                                            |  |  |  |  |  |  |

| OPCODE k (literal)                                                                    |  |  |  |  |  |  |

| k = 11-bit immediate value                                                            |  |  |  |  |  |  |

| MOVLP instruction only<br>13 7 6 0                                                    |  |  |  |  |  |  |

| OPCODE k (literal)                                                                    |  |  |  |  |  |  |

| k = 7-bit immediate value                                                             |  |  |  |  |  |  |

| MOVLB instruction only                                                                |  |  |  |  |  |  |

| <u>13</u> 54 0                                                                        |  |  |  |  |  |  |

| OPCODE k (literal)                                                                    |  |  |  |  |  |  |

| k = 5-bit immediate value                                                             |  |  |  |  |  |  |

| BRA instruction only<br>13 9 8 0                                                      |  |  |  |  |  |  |

| OPCODE k (literal)                                                                    |  |  |  |  |  |  |

| k = 9-bit immediate value                                                             |  |  |  |  |  |  |

| FSR Offset instructions                                                               |  |  |  |  |  |  |

| 13 7 6 5 0<br>OPCODE n k (literal)                                                    |  |  |  |  |  |  |

| n = appropriate FSR<br>k = 6-bit immediate value                                      |  |  |  |  |  |  |

| FSR Increment instructions<br>13                                                      |  |  |  |  |  |  |

| OPCODE n m (mode)                                                                     |  |  |  |  |  |  |

| n = appropriate FSR<br>m = 2-bit mode value                                           |  |  |  |  |  |  |

| OPCODE only<br>13 0                                                                   |  |  |  |  |  |  |

| OPCODE                                                                                |  |  |  |  |  |  |

|                                                                                       |  |  |  |  |  |  |

| LSLF             | Logical Left Shift                                                                                                                                                                                                                  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]LSLF f{,d}                                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in \left[ 0,1 \right] \end{array}$                                                                                                                                                       |

| Operation:       | $(f<7>) \rightarrow C$<br>$(f<6:0>) \rightarrow dest<7:1>$<br>$0 \rightarrow dest<0>$                                                                                                                                               |

| Status Affected: | C, Z                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are shifted<br>one bit to the left through the Carry flag.<br>A '0' is shifted into the LSb. If 'd' is '0',<br>the result is placed in W. If 'd' is '1', the<br>result is stored back in register 'f'. |

|                  | C ← register f ←0                                                                                                                                                                                                                   |

| LSRF             | Logical Right Shift                                                                                                                                                                    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]LSRF f{,d}                                                                                                                                                             |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                     |

| Operation:       | 0 → dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                                                                                    |

| Status Affected: | C, Z                                                                                                                                                                                   |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. A '0' is shifted into the MSb. If 'd' is<br>'0', the result is placed in W. If 'd' is '1', |

| the result i | s stored back i | n register 'f'. |

|--------------|-----------------|-----------------|

| 0→           | register f      | → C             |

| MOVF             | Move f                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                   |  |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Description:     | The contents of register f is moved to<br>a destination dependent upon the<br>status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ , the<br>destination is file register f itself. $d = 1$<br>is useful to test a file register since<br>status flag Z is affected. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                  | After Instruction<br>W = value in FSR register<br>Z = $1$                                                                                                                                                                                                                         |  |  |  |  |  |

#### TABLE 30-8: PIC16(L)F1938/39 A/D CONVERTER (ADC) CHARACTERISTICS:<sup>(1),(2),(3)</sup>

Standard Operating Conditions (unless otherwise stated)

|              | Operating temperature Tested at 25°C |                                                   |      |      |      |       |                                                                     |

|--------------|--------------------------------------|---------------------------------------------------|------|------|------|-------|---------------------------------------------------------------------|

| Param<br>No. | Sym.                                 | Characteristic                                    | Min. | Тур† | Max. | Units | Conditions                                                          |

| AD01         | NR                                   | Resolution                                        | —    | _    | 10   | bit   |                                                                     |

| AD02         | EIL                                  | Integral Error                                    | —    | ±1   | ±1.7 | LSb   | VREF = 3.0V                                                         |

| AD03         | Edl                                  | Differential Error                                | —    | ±1   | ±1   | LSb   | No missing codes<br>VREF = 3.0V                                     |

| AD04         | EOFF                                 | Offset Error                                      | _    | ±1   | ±2.5 | LSb   | VREF = 3.0V                                                         |

| AD05         | Egn                                  | Gain Error                                        |      | ±1   | ±2.0 | LSb   | VREF = 3.0V                                                         |

| AD06         | VREF                                 | Reference Voltage <sup>(4)</sup>                  | 1.8  | _    | Vdd  | V     | VREF = (VREF+ minus VREF-)                                          |

| AD07         | VAIN                                 | Full-Scale Range                                  | Vss  | _    | VREF | V     |                                                                     |

| AD08         | Zain                                 | Recommended Impedance of<br>Analog Voltage Source |      | _    | 10   | kΩ    | Can go higher if external 0.01µF capacitor is present on input pin. |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Total Absolute Error includes integral, differential, offset and gain errors.

2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

**3:** When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

4: ADC Reference Voltage (Ref+) is the selected reference input, VREF+ pin, VDD pin or the FVR Buffer1. When the FVR is selected as the reference input, the FVR Buffer1 output selection must be 2.048V or 4.096V, (ADFVR<1:0> = 1x).

#### TABLE 30-9: PIC16(L)F1938/39 A/D CONVERSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |                       |                                       |  |   |  |  |  |

|---------------------------------------------------------|-----------------------|---------------------------------------|--|---|--|--|--|

|                                                         | Operating temperature | $-40^\circ C \le TA \le +125^\circ C$ |  | - |  |  |  |

|                                                         |                       |                                       |  |   |  |  |  |

| Param<br>No. | Sym. | Characteristic                                                  | Min. | Тур† | Max. | Units | Conditions                                |

|--------------|------|-----------------------------------------------------------------|------|------|------|-------|-------------------------------------------|

| AD130*       | Tad  | A/D Clock Period                                                | 1.0  |      | 9.0  | μS    | Tosc-based                                |

|              |      | A/D Internal RC Oscillator<br>Period                            | 1.0  | 2.5  | 6.0  | μS    | ADCS<1:0> = 11 (ADRC mode)                |

| AD131        | TCNV | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | _    | 11   | _    | TAD   | Set GO/DONE bit to conversion<br>complete |

| AD132*       | TACQ | Acquisition Time                                                | —    | 5.0  | —    | μS    |                                           |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The ADRES register may be read on the following TCY cycle.

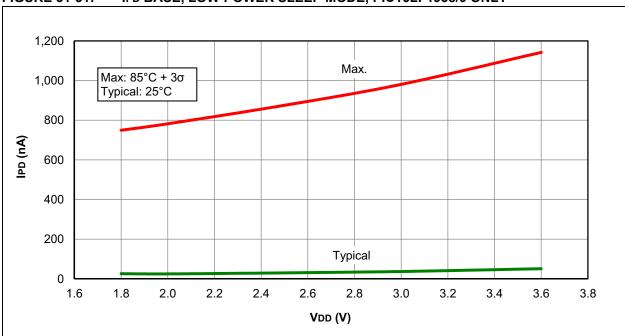

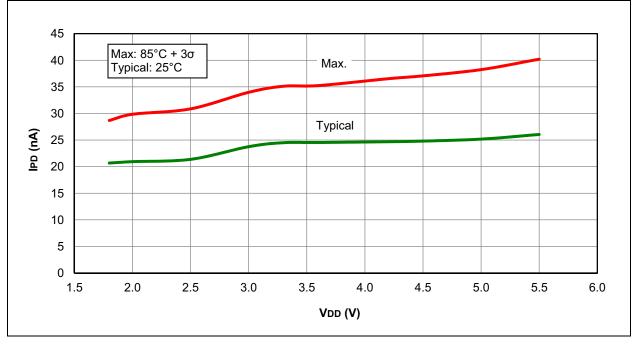

FIGURE 31-31: IPD BASE, LOW-POWER SLEEP MODE, PIC16LF1938/9 ONLY

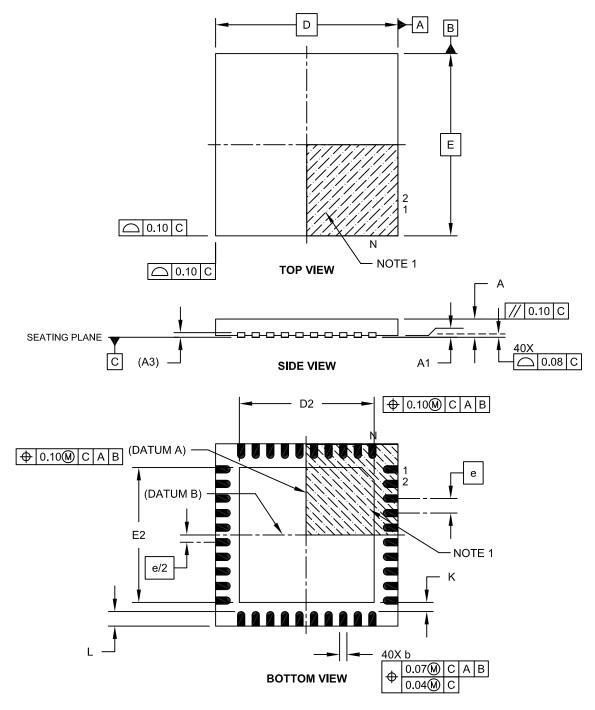

#### 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-156A Sheet 1 of 2

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820