Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1938t-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

The PIC16(L)F1938/9 are described within this data sheet. They are available in 28/40/44-pin packages. Figure 1-1 shows a block diagram of the PIC16(L)F1938/9 devices. Table 1-2 shows the pin out descriptions.

Reference Table 1-1 for peripherals available per device.

TABLE 1-1:DEVICE PERIPHERALSUMMARY

| Peripheral              |             | PIC16F1938/9 | PIC16LF1938/9 |

|-------------------------|-------------|--------------|---------------|

| ADC                     |             | •            | •             |

| Capacitive Sensing Mod  | dule        | •            | •             |

| Digital-to-Analog Conve | erter (DAC) | •            | •             |

| EUSART                  |             | •            | •             |

| Fixed Voltage Reference | e (FVR)     | •            | •             |

| LCD                     |             | ٠            | •             |

| SR Latch                |             | ٠            | •             |

| Temperature Indicator   |             | ٠            | •             |

| Capture/Compare/PWN     | 1 Modules   |              |               |

|                         | ECCP1       | •            | •             |

|                         | ECCP2       | ٠            | •             |

|                         | ECCP3       | •            | •             |

|                         | CCP4        | •            | •             |

|                         | CCP5        | •            | •             |

| Comparators             |             |              |               |

|                         | C1          | •            | •             |

|                         | C2          | ٠            | •             |

| Master Synchronous Se   | erial Ports |              |               |

|                         | MSSP1       | ٠            | •             |

| Timers                  |             |              |               |

|                         | Timer0      | •            | •             |

|                         | Timer1      | •            | •             |

|                         | Timer2      | •            | •             |

|                         | Timer4      | •            | •             |

|                         | Timer6      | •            | •             |

| Address                | Name   | Bit 7        | Bit 6                        | Bit 5          | Bit 4           | Bit 3        | Bit 2        | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|--------|--------------|------------------------------|----------------|-----------------|--------------|--------------|--------|--------|----------------------|---------------------------------|

| Bank 7                 |        |              |                              |                |                 |              |              |        |        |                      |                                 |

| 380h <sup>(2)</sup>    | INDF0  |              | this location ical register) | uses contents  | s of FSR0H/F    | SR0L to addr | ess data mei | mory   |        | ****                 | ****                            |

| 381h <sup>(2)</sup>    | INDF1  |              | this location ical register) | uses contents  | s of FSR1H/F    | SR1L to addr | ess data mei | mory   |        | XXXX XXXX            | XXXX XXXX                       |

| 382h <sup>(2)</sup>    | PCL    | Program Co   | ounter (PC) L                | east Significa | nt Byte         |              |              |        |        | 0000 0000            | 0000 0000                       |

| 383h <sup>(2)</sup>    | STATUS | _            | _                            | —              | TO              | PD           | Z            | DC     | С      | 1 1000               | q quuu                          |

| 384h <sup>(2)</sup>    | FSR0L  | Indirect Dat | a Memory Ad                  | dress 0 Low    | Pointer         |              |              | •      |        | 0000 0000            | uuuu uuuu                       |

| 385h <sup>(2)</sup>    | FSR0H  | Indirect Dat | a Memory Ad                  | ldress 0 High  | Pointer         |              |              |        |        | 0000 0000            | 0000 0000                       |

| 386h <sup>(2)</sup>    | FSR1L  | Indirect Dat | a Memory Ac                  | dress 1 Low    | Pointer         |              |              |        |        | 0000 0000            | uuuu uuuu                       |

| 387h <sup>(2)</sup>    | FSR1H  | Indirect Dat | a Memory Ac                  | Idress 1 High  | Pointer         |              |              |        |        | 0000 0000            | 0000 0000                       |

| 388h <sup>(2)</sup>    | BSR    | _            | _                            | _              |                 |              | BSR<4:0>     |        |        | 0 0000               | 0 0000                          |

| 389h <sup>(2)</sup>    | WREG   | Working Re   | gister                       |                |                 |              |              |        |        | 0000 0000            | uuuu uuuu                       |

| 38Ah <sup>(1, 2)</sup> | PCLATH | _            | Write Buffer                 | for the upper  | 7 bits of the F | Program Cour | iter         |        |        | -000 0000            | -000 0000                       |

| 38Bh <sup>(2)</sup>    | INTCON | GIE          | PEIE                         | TMR0IE         | INTE            | IOCIE        | TMR0IF       | INTF   | IOCIF  | 0000 0000            | 0000 0000                       |

| 38Ch                   | _      | Unimpleme    | nted                         |                |                 |              |              |        |        | _                    | _                               |

| 38Dh                   | _      | Unimpleme    | nted                         |                |                 |              |              |        |        | _                    | _                               |

| 38Eh                   | _      | Unimpleme    | nted                         |                |                 |              |              |        |        | _                    | _                               |

| 38Fh                   | _      | Unimpleme    | nted                         |                |                 |              |              |        |        | _                    | _                               |

| 390h                   | _      | Unimpleme    | nted                         |                |                 |              |              |        |        | _                    | _                               |

| 391h                   | _      | Unimpleme    | nted                         |                |                 |              |              |        |        | _                    | _                               |

| 392h                   | _      | Unimpleme    | nted                         |                |                 |              |              |        |        | _                    | _                               |

| 393h                   | _      | Unimpleme    | nted                         |                |                 |              |              |        |        | _                    | _                               |

| 394h                   | IOCBP  | IOCBP7       | IOCBP6                       | IOCBP5         | IOCBP4          | IOCBP3       | IOCBP2       | IOCBP1 | IOCBP0 | 0000 0000            | 0000 0000                       |

| 395h                   | IOCBN  | IOCBN7       | IOCBN6                       | IOCBN5         | IOCBN4          | IOCBN3       | IOCBN2       | IOCBN1 | IOCBN0 | 0000 0000            | 0000 0000                       |

| 396h                   | IOCBF  | IOCBF7       | IOCBF6                       | IOCBF5         | IOCBF4          | IOCBF3       | IOCBF2       | IOCBF1 | IOCBF0 | 0000 0000            | 0000 0000                       |

| 397h                   | _      | Unimpleme    | nted                         |                |                 |              |              |        |        | _                    | _                               |

| 398h                   | _      | Unimpleme    | nted                         |                |                 |              |              |        |        | _                    | _                               |

| 399h                   | _      | Unimpleme    | Unimplemented —              |                |                 |              |              |        |        | _                    | _                               |

| 39Ah                   | —      | Unimpleme    | Unimplemented                |                |                 |              |              |        |        | _                    | _                               |

| 39Bh                   | _      | Unimpleme    | Unimplemented                |                |                 |              |              |        |        | _                    | _                               |

| 39Ch                   | _      | Unimpleme    | Unimplemented                |                |                 |              |              |        |        | _                    | _                               |

| 39Dh                   | _      | -            | Jnimplemented — — —          |                |                 |              |              |        |        |                      |                                 |

| 39Eh                   | _      | Unimpleme    |                              |                |                 |              |              |        |        | _                    | _                               |

| 39Fh                   |        | Unimpleme    |                              |                |                 |              |              |        |        | <u> </u>             |                                 |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-10.

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16(L)F1938 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

| Address                          | Name   | Bit 7        | Bit 6                                                                                                    | Bit 5          | Bit 4           | Bit 3        | Bit 2       | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|----------------------------------|--------|--------------|----------------------------------------------------------------------------------------------------------|----------------|-----------------|--------------|-------------|-------|-------|----------------------|---------------------------------|

| Banks 9                          | -14    |              |                                                                                                          |                |                 |              |             |       |       |                      |                                 |

| x00h/<br>x80h <sup>(2)</sup>     | INDF0  |              | addressing this location uses contents of FSR0H/FSR0L to address data memory<br>not a physical register) |                |                 |              |             |       |       | XXXX XXX             | * ****                          |

| x00h/<br>x81h <sup>(2)</sup>     | INDF1  |              | this location<br>ical register)                                                                          | uses contents  | s of FSR1H/F    | SR1L to addr | ess data me | mory  |       | XXXX XXXX            | * ****                          |

| x02h/<br>x82h <sup>(2)</sup>     | PCL    | Program Co   | ounter (PC) L                                                                                            | east Significa | nt Byte         |              |             |       |       | 0000 0000            | 0000 0000                       |

| x03h/<br>x83h <sup>(2)</sup>     | STATUS | _            | _                                                                                                        | _              | TO              | PD           | Z           | DC    | С     | 1 1000               | )q quuu                         |

| x04h/<br>x84h <sup>(2)</sup>     | FSR0L  | Indirect Dat | ta Memory Ac                                                                                             | Idress 0 Low   | Pointer         |              |             |       |       | 0000 0000            | ) uuuu uuuu                     |

| x05h/<br>x85h <sup>(2)</sup>     | FSR0H  | Indirect Dat | Indirect Data Memory Address 0 High Pointer                                                              |                |                 |              |             |       |       | 0000 0000            | 0000 0000                       |

| x06h/<br>x86h <sup>(2)</sup>     | FSR1L  | Indirect Dat | ta Memory Ac                                                                                             | Idress 1 Low   | Pointer         |              |             |       |       | 0000 0000            | ) uuuu uuuu                     |

| x07h/<br>x87h <sup>(2)</sup>     | FSR1H  | Indirect Dat | ta Memory Ac                                                                                             | ldress 1 High  | Pointer         |              |             |       |       | 0000 0000            | 0000 0000                       |

| x08h/<br>x88h <sup>(2)</sup>     | BSR    | —            | —                                                                                                        | —              |                 | I            | BSR<4:0>    |       |       | 0 0000               | 00 0000                         |

| x09h/<br>x89h <sup>(2)</sup>     | WREG   | Working Re   | egister                                                                                                  |                |                 |              |             |       |       | 0000 0000            | ) uuuu uuuu                     |

| x0Ah/<br>x8Ah <sup>(1),(2)</sup> | PCLATH | —            | Write Buffer                                                                                             | for the upper  | 7 bits of the F | Program Cour | iter        |       |       | -000 0000            | 0 -000 0000                     |

| x0Bh/<br>x8Bh <sup>(2)</sup>     | INTCON | GIE          | PEIE                                                                                                     | TMR0IE         | INTE            | IOCIE        | TMR0IF      | INTF  | IOCIF | 0000 0000            | 0000 0000                       |

| x0Ch/<br>x8Ch                    | —      | Unimpleme    | Unimplemented                                                                                            |                |                 |              |             |       | —     | -                    |                                 |

| x1Fh/<br>x9Fh                    |        |              |                                                                                                          |                |                 |              |             |       |       |                      |                                 |

#### TABLE 3-10: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: These registers/bits are not implemented on PIC16(L)F1938 devices, read as '0'.

4: Unimplemented, read as '1'.

#### 5.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- Timer1 32 kHz crystal oscillator

- Internal Oscillator Block (INTOSC)

#### 5.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by value of the FOSC<2:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the Timer1 oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0> bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

| Note: | Any automatic clock switch, which may     |

|-------|-------------------------------------------|

|       | occur from Two-Speed Start-up or          |

|       | Fail-Safe Clock Monitor, does not update  |

|       | the SCS bits of the OSCCON register. The  |

|       | user can monitor the OSTS bit of the      |

|       | OSCSTAT register to determine the current |

|       | system clock source.                      |

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 5-1.

#### 5.3.2 OSCILLATOR START-UP TIME-OUT STATUS (OSTS) BIT

The Oscillator Start-up Time-out Status (OSTS) bit of the OSCSTAT register indicates whether the system clock is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Words, or from the internal clock source. In particular, OSTS indicates that the Oscillator Start-up Timer (OST) has timed out for LP, XT or HS modes. The OST does not reflect the status of the Timer1 oscillator.

#### 5.3.3 TIMER1 OSCILLATOR

The Timer1 oscillator is a separate crystal oscillator associated with the Timer1 peripheral. It is optimized for timekeeping operations with a 32.768 kHz crystal connected between the T1OSO and T1OSI device pins.

The Timer1 oscillator is enabled using the T1OSCEN control bit in the T1CON register. See Section 21.0 "Timer1 Module with Gate Control" for more information about the Timer1 peripheral.

#### 5.3.4 TIMER1 OSCILLATOR READY (T1OSCR) BIT

The user must ensure that the Timer1 Oscillator is ready to be used before it is selected as a system clock source. The Timer1 Oscillator Ready (T1OSCR) bit of the OSCSTAT register indicates whether the Timer1 oscillator is ready to be used. After the T1OSCR bit is set, the SCS bits can be configured to select the Timer1 oscillator.

| R-1/q                                                                                                                                      | R-0/q                                                              | R-q/q                                                    | R-0/q            | R-0/q           | R-q/q                    | R-0/q            | R-0/q        |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------|------------------|-----------------|--------------------------|------------------|--------------|

| T10SCR                                                                                                                                     | PLLR                                                               | OSTS                                                     | HFIOFR           | HFIOFL          | MFIOFR                   | LFIOFR           | HFIOFS       |

| bit 7                                                                                                                                      |                                                                    |                                                          | 1                | 1               |                          | 1                | bit 0        |

| <u> </u>                                                                                                                                   |                                                                    |                                                          |                  |                 |                          |                  |              |

| Legend:                                                                                                                                    |                                                                    |                                                          |                  |                 |                          |                  |              |

| R = Readable                                                                                                                               | bit                                                                | W = Writable                                             | bit              | U = Unimpler    | mented bit, read         | d as '0'         |              |

| u = Bit is unch                                                                                                                            | anged                                                              | x = Bit is unk                                           | nown             | -n/n = Value    | at POR and BO            | R/Value at all o | other Resets |

| '1' = Bit is set                                                                                                                           |                                                                    | '0' = Bit is cle                                         | ared             | q = Condition   | nal                      |                  |              |

| bit 7                                                                                                                                      | <u>If T1OSCEN</u><br>1 = Timer1<br>0 = Timer1<br><u>If T1OSCEN</u> | oscillator is rea                                        | dy<br>ready      |                 |                          |                  |              |

| bit 6                                                                                                                                      | PLLR 4x PLL<br>1 = 4x PLL<br>0 = 4x PLL                            | ₋ Ready bit<br>is ready                                  |                  |                 |                          |                  |              |

| bit 5                                                                                                                                      | 1 = Running                                                        | lator Start-up T<br>g from the clocl<br>g from an interr | c defined by the | e FOSC<2:0>     | bits of the Confi<br>00) | guration Word    | S            |

| bit 4                                                                                                                                      | 1 = HFINTO                                                         | h-Frequency lı<br>SC is ready<br>SC is not ready         |                  | or Ready bit    |                          |                  |              |

| bit 3                                                                                                                                      | 1 = HFINTO                                                         | h-Frequency Ir<br>SC is at least 2<br>SC is not 2% a     | 2% accurate      | or Locked bit   |                          |                  |              |

| bit 2                                                                                                                                      | 1 = MFINTO                                                         | edium-Frequen<br>ISC is ready<br>ISC is not read         | -                | illator Ready b | it                       |                  |              |

| bit 1                                                                                                                                      | 1 = LFINTO                                                         | v-Frequency In<br>SC is ready<br>SC is not ready         |                  | or Ready bit    |                          |                  |              |

| bit 0 HFIOFS: High-Frequency Internal Oscillator Stable bit<br>1 = HFINTOSC is at least 0.5% accurate<br>0 = HFINTOSC is not 0.5% accurate |                                                                    |                                                          |                  |                 |                          |                  |              |

#### REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

#### 11.2 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). When variables in one section change frequently, while variables in another section do not change, it is possible to exceed the total number of write cycles to the EEPROM without exceeding the total number of write cycles to a single byte. Refer to **Section 30.0 "Electrical Specifications"**. If this is the case, then a refresh of the array must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

#### 11.2.1 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the EEADRL register, clear the EEPGD and CFGS control bits of the EECON1 register, and then set control bit RD. The data is available at the very next cycle, in the EEDATL register; therefore, it can be read in the next instruction. EEDATL will hold this value until another read or until it is written to by the user (during a write operation).

#### EXAMPLE 11-1: DATA EEPROM READ

| BANKSEL | EEADRL  |       | ;                      |

|---------|---------|-------|------------------------|

| MOVLW   | DATA_EE | ADDR  | ;                      |

| MOVWF   | EEADRL  |       | ;Data Memory           |

|         |         |       | ;Address to read       |

| BCF     | EECON1, | CFGS  | ;Deselect Config space |

| BCF     | EECON1, | EEPGI | ;Point to DATA memory  |

| BSF     | EECON1, | RD    | ;EE Read               |

| MOVF    | EEDATL, | W     | ;W = EEDATL            |

|         |         |       |                        |

### Note: Data EEPROM can be read regardless of the setting of the CPD bit.

### 11.2.2 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the user must first write the address to the EEADRL register and the data to the EEDATL register. Then the user must follow a specific sequence to initiate the write for each byte.

The write will not initiate if the above sequence is not followed exactly (write 55h to EECON2, write AAh to EECON2, then set the WR bit) for each byte. Interrupts should be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

### 11.2.3 PROTECTION AGAINST SPURIOUS WRITE

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, WREN is cleared. Also, the Power-up Timer (64 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during:

- Brown-out

- Power Glitch

- Software Malfunction

#### 11.2.4 DATA EEPROM OPERATION DURING CODE-PROTECT

Data memory can be code-protected by programming the  $\overline{CPD}$  bit in the Configuration Words to '0'.

When the data memory is code-protected, only the CPU is able to read and write data to the data EEPROM. It is recommended to code-protect the program memory when code-protecting data memory. This prevents anyone from replacing your program with a program that will access the contents of the data EEPROM.

#### EXAMPLE 11-3: FLASH PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG ADDR HI: PROG ADDR LO

data will be returned in the variables;

*

PROG_DATA_HI, PROG_DATA_LO

BANKSELEEADRL; Select Bank for EEPROM registersMOVLWPROG_ADDR_LO;MOVWFEEADRL; Store LSB of addressMOVLWPROG_ADDR_HI;MOVWLEEADRH; Store MSB of address

EECON1,CFGS ; Do not select Configuration Space

EECON1,EEPGD ; Select Program Memory

BCF

EECON1,CFGS

BSF

INTCON,GIE ; Disable interrupts

BCF

; Initiate read

BSF

EECON1,RD

NOP

; Executed (Figure 11-1)

NOP

; Ignored (Figure 11-1)

BSF

INTCON, GIE

; Restore interrupts

EEDATL,W

MOVF

; Get LSB of word

MOVWF

PROG_DATA_LO ; Store in user location

EEDATH,W ; Get MSB of word

PROG_DATA_HI ; Store in user location

MOVE

MOVWF

```

#### 15.2 ADC Operation

#### 15.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 15.2.6 "A/D Conver-     |

|       | sion Procedure".                         |

#### 15.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 15.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

#### 15.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 15.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx/ECCPX module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

#### TABLE 15-2: SPECIAL EVENT TRIGGER

| Device        | CCPx/ECCPx |

|---------------|------------|

| PIC16(L)F193X | CCP5       |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 23.0 "Capture/Compare/PWM Modules" for more information.

| Name    | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |

|---------|--------|--------|--------|--------|--------|-----------|--------|--------|---------------------|

| CM1CON0 | C10N   | C10UT  | C10E   | C1POL  |        | C1SP      | C1HYS  | C1SYNC | 175                 |

| CM2CON0 | C2ON   | C2OUT  | C2OE   | C2POL  | _      | C2SP      | C2HYS  | C2SYNC | 175                 |

| CM1CON1 | C1NTP  | C1INTN | C1PCI  | H<1:0> | _      | _         | C1NCI  | H<1:0> | 176                 |

| CM2CON1 | C2NTP  | C2INTN | C2PCI  | H<1:0> | —      | —         | C2NCI  | H<1:0> | 176                 |

| CMOUT   | —      | _      | _      | _      | _      | _         | MC2OUT | MC1OUT | 176                 |

| FVRCON  | FVREN  | FVRRDY | TSEN   | TSRNG  | CDAFV  | ′R<1:0>   | ADFV   | R<1:0> | 148                 |

| DACCON0 | DACEN  | DACLPS | DACOE  | _      | DACPS  | SS<1:0>   | _      | DACNSS | 168                 |

| DACCON1 | —      | _      | _      |        |        | DACR<4:0> |        |        | 168                 |

| INTCON  | GIE    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF    | INTF   | IOCIF  | 90                  |

| PIE2    | OSFIE  | C2IE   | C1IE   | EEIE   | BCLIE  | LCDIE     | _      | CCP2IE | 92                  |

| PIR2    | OSFIF  | C2IF   | C1IF   | EEIF   | BCLIF  | LCDIF     | _      | CCP2IF | 95                  |

| TRISA   | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2    | TRISA1 | TRISA0 | 125                 |

| TRISB   | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2    | TRISB1 | TRISB0 | 130                 |

| ANSELA  | —      | _      | ANSA5  | ANSA4  | ANSA3  | ANSA2     | ANSA1  | ANSA0  | 126                 |

| ANSELB  | _      | _      | ANSB5  | ANSB4  | ANSB3  | ANSB2     | ANSB1  | ANSB0  | 131                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are unused by the comparator module.

### 20.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A software programmable prescaler is available for exclusive use with Timer0. The prescaler is enabled by clearing the PSA bit of the OPTION\_REG register.

| Note: | The Watchdog Timer (WDT) uses its own |

|-------|---------------------------------------|

|       | independent prescaler.                |

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION\_REG register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be disabled by setting the PSA bit of the OPTION\_REG register.

The prescaler is not readable or writable. All instructions writing to the TMR0 register will clear the prescaler.

#### 20.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |  |  |  |

|-------|-----------------------------------------|--|--|--|

|       | processor from Sleep since the timer is |  |  |  |

|       | frozen during Sleep.                    |  |  |  |

#### 20.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in Section 30.0 "Electrical Specifications".

#### 20.1.6 OPERATION DURING SLEEP

Timer0 cannot operate while the processor is in Sleep mode. The contents of the TMR0 register will remain unchanged while the processor is in Sleep mode.

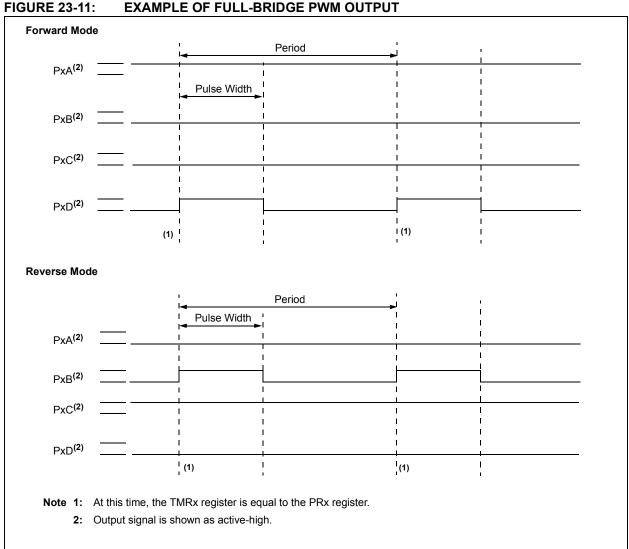

FIGURE 23-11: **EXAMPLE OF FULL-BRIDGE PWM OUTPUT**

NOTES:

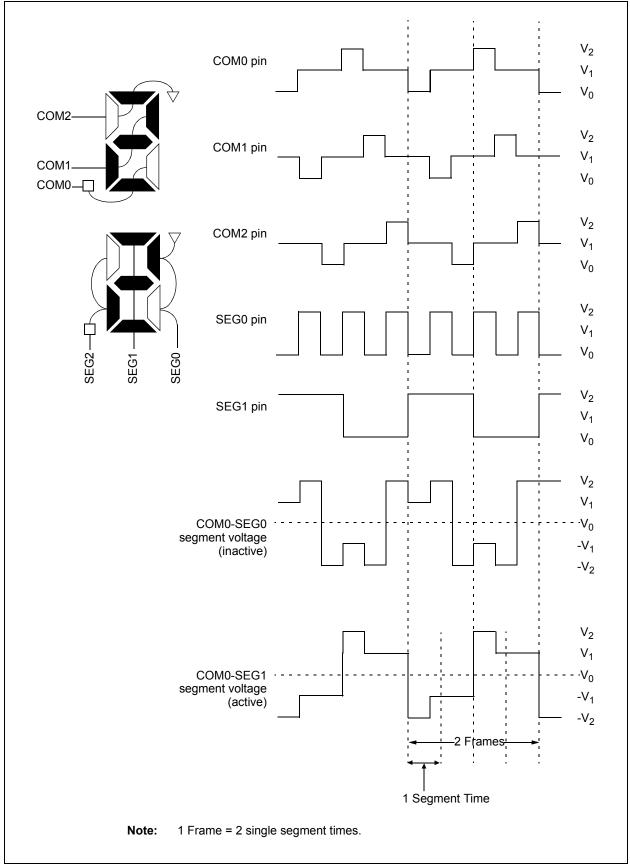

#### FIGURE 27-14: TYPE-B WAVEFORMS IN 1/3 MUX, 1/2 BIAS DRIVE

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                          |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                                   |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |  |  |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                        |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                     |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                        |  |  |

| Operation:       | k → PC<10:0><br>PCLATH<6:3> → PC<14:11>                                                                                                                                                     |  |  |

| Status Affected: | None                                                                                                                                                                                        |  |  |

| Description:     | GOTO is an unconditional branch. The<br>eleven-bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a 2-cycle instruction. |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                          |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                     |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                               |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                      |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                            |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |  |  |

| IORLW            | Inclusive OR literal with W                                                                                        |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                           |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                       |  |  |

| Status Affected: | Z                                                                                                                  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |  |

| INCF             | Increment f                                                                                                                                                               | IORWF            | Inclusive OR W with f                                                                                                                                                      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                          | Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                 |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                        | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                          |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                       | Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                         | Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'. | Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

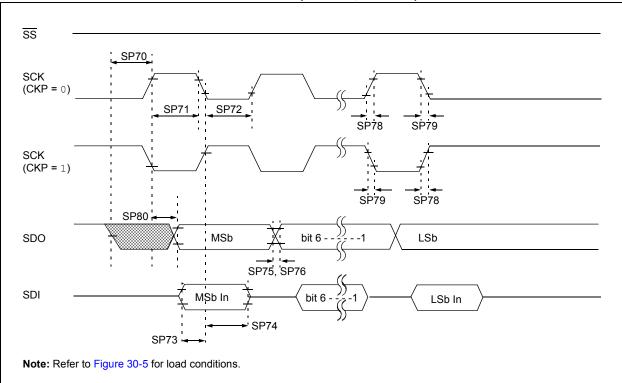

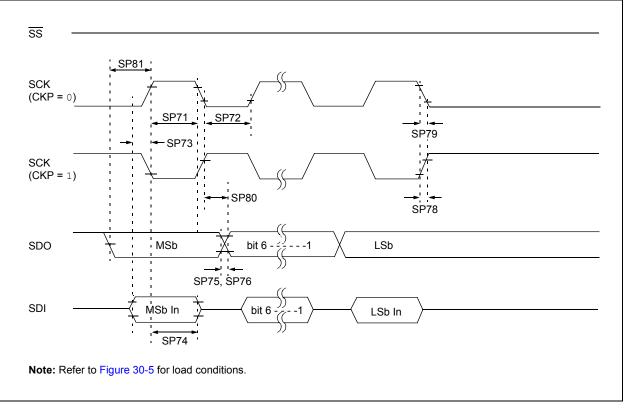

#### FIGURE 30-16: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

NOTES:

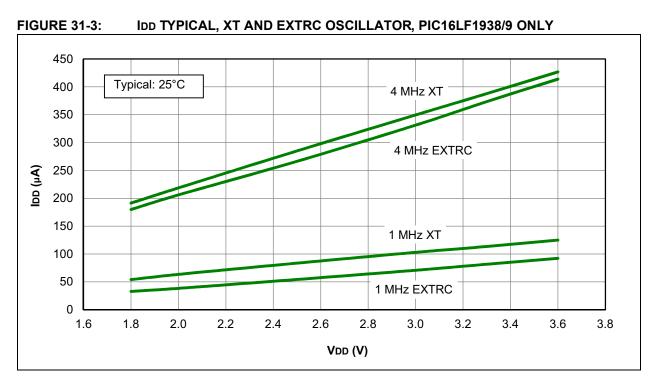

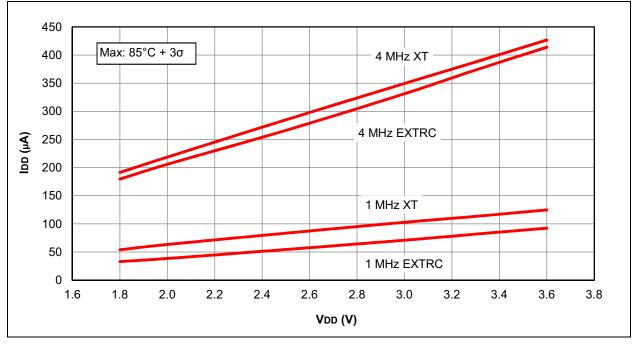

FIGURE 31-4: IDD MAXIMUM, XT AND EXTRC OSCILLATOR, PIC16LF1938/9 ONLY

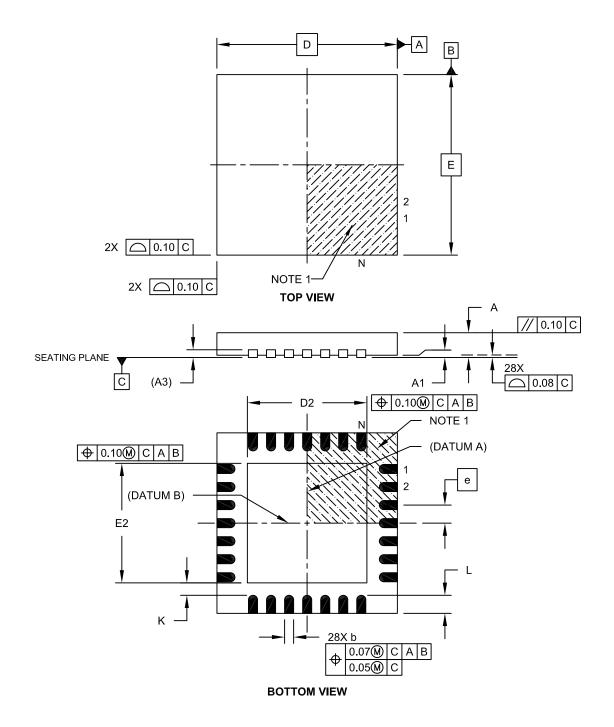

#### 28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-152A Sheet 1 of 2