Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 44-QFN (8x8)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1939-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                              | Function | Input<br>Type | Output<br>Type | Description                         |

|-------------------------------------------------------------------|----------|---------------|----------------|-------------------------------------|

| RD6 <sup>(4)</sup> /CPS14/P1C/SEG19                               | RD6      | ST            | CMOS           | General purpose I/O.                |

|                                                                   | CPS14    | AN            | _              | Capacitive sensing input 14.        |

|                                                                   | P1C      |               | CMOS           | PWM output.                         |

|                                                                   | SEG19    | _             | AN             | LCD analog output.                  |

| RD7 <sup>(4)</sup> /CPS15/P1D/SEG20                               | RD7      | ST            | CMOS           | General purpose I/O.                |

|                                                                   | CPS15    | AN            |                | Capacitive sensing input 15.        |

|                                                                   | P1D      | _             | CMOS           | PWM output.                         |

|                                                                   | SEG20    | _             | AN             | LCD analog output.                  |

| RE0 <sup>(5)</sup> /AN5/P3A <sup>(1)</sup> /CCP3 <sup>(1)</sup> / | RE0      | ST            | CMOS           | General purpose I/O.                |

| SEG21                                                             | AN5      | AN            | —              | A/D Channel 5 input.                |

|                                                                   | P3A      | _             | CMOS           | PWM output.                         |

|                                                                   | CCP3     | ST            | CMOS           | Capture/Compare/PWM3.               |

|                                                                   | SEG21    | _             | AN             | LCD analog output.                  |

| RE1 <sup>(5)</sup> /AN6/P3B/SEG22                                 | RE1      | ST            | CMOS           | General purpose I/O.                |

|                                                                   | AN6      | AN            | _              | A/D Channel 6 input.                |

|                                                                   | P3B      | —             | CMOS           | PWM output.                         |

|                                                                   | SEG22    | _             | AN             | LCD analog output.                  |

| RE2 <sup>(5)</sup> /AN7/CCP5/SEG23                                | RE2      | ST            | CMOS           | General purpose I/O.                |

|                                                                   | AN7      | AN            | _              | A/D Channel 7 input.                |

|                                                                   | CCP5     | ST            | CMOS           | Capture/Compare/PWM5.               |

|                                                                   | SEG23    | _             | AN             | LCD analog output.                  |

| RE3/MCLR/VPP                                                      | RE3      | TTL           | —              | General purpose input.              |

|                                                                   | MCLR     | ST            | —              | Master Clear with internal pull-up. |

|                                                                   | VPP      | HV            | —              | Programming voltage.                |

| Vdd                                                               | Vdd      | Power         | —              | Positive supply.                    |

| Vss                                                               | Vss      | Power         | —              | Ground reference.                   |

|  | TABLE 1-2: | PIC16(L)F1938/ | 9 PINOUT DESCRIPTION | (CONTINUED) |  |

|--|------------|----------------|----------------------|-------------|--|

|--|------------|----------------|----------------------|-------------|--|

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels XTAL = Crystal

HV = High Voltage  $I^2C^{TM}$  = Schmitt Trigger input with I<sup>2</sup>C levels

**Note 1:** Pin function is selectable via the APFCON register.

2: PIC16F1938/9 devices only.

3: PIC16(L)F1938 devices only.

4: PORTD is available on PIC16(L)F1939 devices only.

5: RE<2:0> are available on PIC16(L)F1939 devices only.

## TABLE 3-4: PIC16(L)F1938/9 MEMORY MAP, BANKS 8-15

|      | BANK 8               | -    | BANK 9               |      | BANK 10              |      | BANK 11              |      | BANK 12              |      | BANK 13       |      | BANK 14       |      | BANK 15          |

|------|----------------------|------|----------------------|------|----------------------|------|----------------------|------|----------------------|------|---------------|------|---------------|------|------------------|

| 400h | INDF0                | 480h | INDF0                | 500h | INDF0                | 580h | INDF0                | 600h | INDF0                | 680h | INDF0         | 700h | INDF0         | 780h | INDF0            |

| 401h | INDF1                | 481h | INDF1                | 501h | INDF1                | 581h | INDF1                | 601h | INDF1                | 681h | INDF1         | 701h | INDF1         | 781h | INDF1            |

| 402h | PCL                  | 482h | PCL                  | 502h | PCL                  | 582h | PCL                  | 602h | PCL                  | 682h | PCL           | 702h | PCL           | 782h | PCL              |

| 403h | STATUS               | 483h | STATUS               | 503h | STATUS               | 583h | STATUS               | 603h | STATUS               | 683h | STATUS        | 703h | STATUS        | 783h | STATUS           |

| 404h | FSR0L                | 484h | FSR0L                | 504h | FSR0L                | 584h | FSR0L                | 604h | FSR0L                | 684h | FSR0L         | 704h | FSR0L         | 784h | FSR0L            |

| 405h | FSR0H                | 485h | FSR0H                | 505h | FSR0H                | 585h | FSR0H                | 605h | FSR0H                | 685h | FSR0H         | 705h | FSR0H         | 785h | FSR0H            |

| 406h | FSR1L                | 486h | FSR1L                | 506h | FSR1L                | 586h | FSR1L                | 606h | FSR1L                | 686h | FSR1L         | 706h | FSR1L         | 786h | FSR1L            |

| 407h | FSR1H                | 487h | FSR1H                | 507h | FSR1H                | 587h | FSR1H                | 607h | FSR1H                | 687h | FSR1H         | 707h | FSR1H         | 787h | FSR1H            |

| 408h | BSR                  | 488h | BSR                  | 508h | BSR                  | 588h | BSR                  | 608h | BSR                  | 688h | BSR           | 708h | BSR           | 788h | BSR              |

| 409h | WREG                 | 489h | WREG                 | 509h | WREG                 | 589h | WREG                 | 609h | WREG                 | 689h | WREG          | 709h | WREG          | 789h | WREG             |

| 40Ah | PCLATH               | 48Ah | PCLATH               | 50Ah | PCLATH               | 58Ah | PCLATH               | 60Ah | PCLATH               | 68Ah | PCLATH        | 70Ah | PCLATH        | 78Ah | PCLATH           |

| 40Bh | INTCON               | 48Bh | INTCON               | 50Bh | INTCON               | 58Bh | INTCON               | 60Bh | INTCON               | 68Bh | INTCON        | 70Bh | INTCON        | 78Bh | INTCON           |

| 40Ch | _                    | 48Ch | _                    | 50Ch |                      | 58Ch |                      | 60Ch |                      | 68Ch | —             | 70Ch | _             | 78Ch | —                |

| 40Dh | —                    | 48Dh | _                    | 50Dh | _                    | 58Dh | —                    | 60Dh |                      | 68Dh | —             | 70Dh |               | 78Dh | —                |

| 40Eh | —                    | 48Eh | _                    | 50Eh | _                    | 58Eh | _                    | 60Eh |                      | 68Eh | —             | 70Eh | _             | 78Eh | —                |

| 40Fh | —                    | 48Fh | —                    | 50Fh | —                    | 58Fh | —                    | 60Fh | _                    | 68Fh | —             | 70Fh | —             | 78Fh | —                |

| 410h | —                    | 490h | —                    | 510h | —                    | 590h | —                    | 610h | —                    | 690h | —             | 710h | —             | 790h | —                |

| 411h | —                    | 491h | —                    | 511h | —                    | 591h | —                    | 611h | _                    | 691h | —             | 711h | —             | 791h |                  |

| 412h | —                    | 492h | —                    | 512h | —                    | 592h | —                    | 612h | —                    | 692h | —             | 712h | —             | 792h |                  |

| 413h | —                    | 493h | —                    | 513h | —                    | 593h | —                    | 613h | —                    | 693h | —             | 713h |               | 793h |                  |

| 414h | —                    | 494h | _                    | 514h | _                    | 594h | _                    | 614h | _                    | 694h | _             | 714h |               | 794h |                  |

| 415h | TMR4                 | 495h | —                    | 515h | —                    | 595h | —                    | 615h | _                    | 695h | _             | 715h | _             | 795h |                  |

| 416h | PR4                  | 496h | —                    | 516h | _                    | 596h | _                    | 616h | _                    | 696h |               | 716h |               | 796h |                  |

| 417h | T4CON                | 497h | _                    | 517h | _                    | 597h | _                    | 617h | _                    | 697h | _             | 717h | _             | 797h |                  |

| 418h | _                    | 498h | _                    | 518h | _                    | 598h | _                    | 618h | _                    | 698h | _             | 718h | _             | 798h |                  |

| 419h | _                    | 499h | _                    | 519h | _                    | 599h | _                    | 619h | _                    | 699h | _             | 719h | _             | 799h |                  |

| 41Ah | —                    | 49Ah | —                    | 51Ah | _                    | 59Ah |                      | 61Ah |                      | 69Ah | _             | 71Ah |               | 79Ah | See Table 3-7 or |

| 41Bh |                      | 49Bh | _                    | 51Bh | _                    | 59Bh |                      | 61Bh |                      | 69Bh | _             | 71Bh |               | 79Bh | Table 3-8        |

| 41Ch | TMR6                 | 49Ch |                      | 51Ch |                      | 59Ch |                      | 61Ch |                      | 69Ch | _             | 71Ch |               | 79Ch |                  |

| 41Dh | PR6                  | 49Dh | _                    | 51Dh |                      | 59Dh |                      | 61Dh |                      | 69Dh | _             | 71Dh | _             | 79Dh |                  |

| 41Eh | T6CON                | 49Eh | _                    | 51Eh | —                    | 59Eh | —                    | 61Eh |                      | 69Eh |               | 71Eh |               | 79Eh |                  |

| 41Fh | —                    | 49Fh | —                    | 51Fh | —                    | 59Fh | —                    | 61Fh | —                    | 69Fh | —             | 71Fh | _             | 79Fh |                  |

| 420h |                      | 4A0h |                      | 520h |                      | 5A0h |                      | 620h | General Purpose      | 6A0h |               | 720h |               | 7A0h |                  |

|      | General              |      | General              |      | General              |      | General              |      | Register<br>48 Bytes |      |               |      |               |      |                  |

|      | Purpose              |      | Purpose              |      | Purpose              |      | Purpose              |      | 40 Byles             |      | Unimplemented |      | Unimplemented |      |                  |

|      | Register<br>80 Bytes |      | Register<br>80 Bytes |      | Register<br>80 Bytes |      | Register<br>80 Bytes |      | Unimplemented        |      | Read as '0'   |      | Read as '0'   |      |                  |

|      | of Bytes             |      | 00 Dytes             |      | 00 Dytes             |      | 00 Dytes             |      | Read as '0'          |      |               |      |               |      |                  |

| 46Fh |                      | 4EFh |                      | 56Fh |                      | 5EFh |                      | 66Fh |                      | 6EFh |               | 76Fh |               | 7EFh |                  |

| 470h |                      | 4F0h |                      | 570h |                      | 5F0h |                      | 670h |                      | 6F0h |               | 770h |               | 7F0h |                  |

|      | Accesses             |      | Accesses      |      | Accesses      |      | Accesses         |

|      | 70h – 7Fh            |      | 70h – 7Fh     |      | 70h – 7Fh     |      | 70h – 7Fh        |

| 47Fh |                      | 4FFh |                      | 57Fh |                      | 5FFh |                      | 67Fh |                      | 6FFh |               | 77Fh |               | 7FFh |                  |

Legend: = Unimplemented data memory locations, read as '0'.

## 5.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the FOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to the internal oscillator during run-time. See Section 5.3 "Clock Switching"for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators and a dedicated Phase-Lock Loop, HFPLL that can produce one of three internal system clock sources.

- The HFINTOSC (High-Frequency Internal Oscillator) is factory calibrated and operates at 16 MHz. The HFINTOSC source is generated from the 500 kHz MFINTOSC source and the dedicated Phase-Lock Loop, HFPLL. The frequency of the HFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- The MFINTOSC (Medium-Frequency Internal Oscillator) is factory calibrated and operates at 500 kHz. The frequency of the MFINTOSC can be user-adjusted via software using the OSCTUNE register (Register 5-3).

- 3. The **LFINTOSC** (Low-Frequency Internal Oscillator) is uncalibrated and operates at 31 kHz.

## 5.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a factory calibrated 16 MHz internal clock source. The frequency of the HFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the HFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of multiple frequencies derived from the HFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See Section 5.2.2.7 "Internal Oscillator Clock Switch Timing" for more information.

The HFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'.

A fast startup oscillator allows internal circuits to power up and stabilize before switching to HFINTOSC.

The High Frequency Internal Oscillator Ready bit (HFIOFR) of the OSCSTAT register indicates when the HFINTOSC is running.

The High Frequency Internal Oscillator Status Locked bit (HFIOFL) of the OSCSTAT register indicates when the HFINTOSC is running within 2% of its final value.

The High Frequency Internal Oscillator Stable bit (HFIOFS) of the OSCSTAT register indicates when the HFINTOSC is running within 0.5% of its final value.

### 5.2.2.2 MFINTOSC

The Medium-Frequency Internal Oscillator (MFINTOSC) is a factory calibrated 500 kHz internal clock source. The frequency of the MFINTOSC can be altered via software using the OSCTUNE register (Register 5-3).

The output of the MFINTOSC connects to a postscaler and multiplexer (see Figure 5-1). One of nine frequencies derived from the MFINTOSC can be selected via software using the IRCF<3:0> bits of the OSCCON register. See Section 5.2.2.7 "Internal Oscillator Clock Switch Timing" for more information.

The MFINTOSC is enabled by:

- Configure the IRCF<3:0> bits of the OSCCON register for the desired HF frequency, and

- FOSC<2:0> = 100, or

- Set the System Clock Source (SCS) bits of the OSCCON register to '1x'

The Medium Frequency Internal Oscillator Ready bit (MFIOFR) of the OSCSTAT register indicates when the MFINTOSC is running.

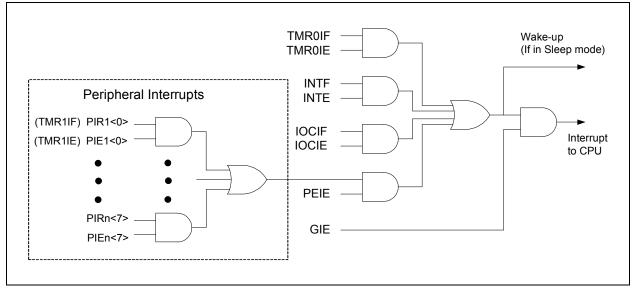

## 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce Interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 7-1.

#### FIGURE 7-1: INTERRUPT LOGIC

| R/W-0/0        | R/W-0/0                                  | R-0/0                        | R-0/0                                 | R/W-0/0          | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|----------------|------------------------------------------|------------------------------|---------------------------------------|------------------|------------------|------------------|--------------|

| TMR1GI         | = ADIF                                   | RCIF                         | TXIF                                  | SSPIF            | CCP1IF           | TMR2IF           | TMR1IF       |

| bit 7          |                                          |                              |                                       |                  |                  |                  | bit          |

|                |                                          |                              |                                       |                  |                  |                  |              |

| Legend:        |                                          |                              |                                       |                  |                  |                  |              |

| R = Reada      | ble bit                                  | W = Writable                 | bit                                   | U = Unimpler     | mented bit, read | l as '0'         |              |

| u = Bit is ur  | nchanged                                 | x = Bit is unk               | nown                                  | -n/n = Value     | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is s | set                                      | '0' = Bit is cle             | ared                                  |                  |                  |                  |              |

| bit 7          | TMR1GIF: Ti                              | imer1 Gate Inte              | errupt Flag bit                       |                  |                  |                  |              |

|                | 1 = Interrupt                            |                              |                                       |                  |                  |                  |              |

|                | 0 = Interrupt                            | is not pending               |                                       |                  |                  |                  |              |

| bit 6          | ADIF: A/D C                              | onverter Interru             | ıpt Flag bit                          |                  |                  |                  |              |

|                | 1 = Interrupt<br>0 = Interrupt           | is pending<br>is not pending |                                       |                  |                  |                  |              |

| bit 5          | RCIF: USAR                               | T Receive Inte               | rrupt Flag bit                        |                  |                  |                  |              |

|                | 1 = Interrupt                            |                              | 1 0                                   |                  |                  |                  |              |

|                | 0 = Interrupt                            | is not pending               |                                       |                  |                  |                  |              |

| bit 4          | TXIF: USAR                               | T Transmit Inte              | rrupt Flag bit                        |                  |                  |                  |              |

|                | 1 = Interrupt<br>0 = Interrupt           | is pending<br>is not pending |                                       |                  |                  |                  |              |

| bit 3          | SSPIF: Sync                              | hronous Serial               | Port (MSSP)                           | Interrupt Flag b | oit              |                  |              |

|                | 1 = Interrupt                            |                              | , , , , , , , , , , , , , , , , , , , |                  |                  |                  |              |

|                | 0 = Interrupt                            | is not pending               |                                       |                  |                  |                  |              |

| bit 2          | CCP1IF: CC                               | P1 Interrupt Fla             | ag bit                                |                  |                  |                  |              |

|                | 1 = Interrupt                            |                              |                                       |                  |                  |                  |              |

|                | •                                        | is not pending               |                                       |                  |                  |                  |              |

| bit 1          |                                          | er2 to PR2 Inte              | errupt Flag bit                       |                  |                  |                  |              |

|                | 1 = Interrupt                            |                              |                                       |                  |                  |                  |              |

| hit O          | -                                        | is not pending               | atorrupt Flog I                       | -:+              |                  |                  |              |

| bit 0          | 1 = Interrupt                            | er1 Overflow I               | nterrupt Flag i                       | JIL              |                  |                  |              |

|                |                                          | is not pending               |                                       |                  |                  |                  |              |

|                | Interrupt flag bits a                    |                              |                                       |                  |                  |                  |              |

|                | condition occurs, r<br>its corresponding |                              |                                       |                  |                  |                  |              |

|                | Enable bit, GIE, o                       |                              |                                       |                  |                  |                  |              |

|                | User software                            | should ens                   | •                                     |                  |                  |                  |              |

|                | appropriate interru                      |                              | clear prior                           |                  |                  |                  |              |

|                | to enabling an inte                      | errupt.                      |                                       |                  |                  |                  |              |

## REGISTER 7-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

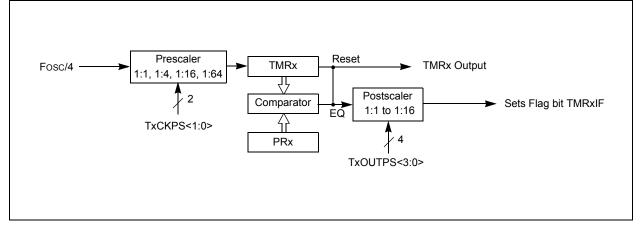

## 22.0 TIMER2/4/6 MODULES

There are up to three identical Timer2-type modules available. To maintain pre-existing naming conventions, the Timers are called Timer2, Timer4 and Timer6 (also Timer2/4/6).

| Note: | The 'x' variable used in this section is used to designate Timer2, Timer4, or |

|-------|-------------------------------------------------------------------------------|

|       | Timer6. For example, TxCON references                                         |

|       | T2CON, T4CON, or T6CON. PRx refer-                                            |

|       | ences PR2, PR4, or PR6.                                                       |

The Timer2/4/6 modules incorporate the following features:

- 8-bit Timer and Period registers (TMRx and PRx, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMRx match with PRx, respectively

- Optional use as the shift clock for the MSSP module (Timer2 only)

See Figure 22-1 for a block diagram of Timer2/4/6.

| U-0             | U-0        | U-0               | U-0       | U-0            | U-0              | R/W-0/0          | R/W-0/0      |

|-----------------|------------|-------------------|-----------|----------------|------------------|------------------|--------------|

| _               | —          | —                 | _         | —              | —                | C5TSE            | L<1:0>       |

| bit 7           |            |                   |           |                |                  |                  | bit 0        |

|                 |            |                   |           |                |                  |                  |              |

| Legend:         |            |                   |           |                |                  |                  |              |

| R = Readab      | le bit     | W = Writable      | bit       | U = Unimplen   | nented bit, read | l as '0'         |              |

| u = Bit is und  | changed    | x = Bit is unkr   | nown      | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is se | et         | '0' = Bit is clea | ared      |                |                  |                  |              |

|                 |            |                   |           |                |                  |                  |              |

| bit 7-2         | Unimplemen | ted: Read as '    | 0'        |                |                  |                  |              |

| bit 1-0         | C5TSEL<1:0 | >: CCP5 Timer     | Selection |                |                  |                  |              |

## REGISTER 23-3: CCPTMRS1: PWM TIMER SELECTION CONTROL REGISTER 1

DIT 1-0 00 = CCP5 is based off Timer2 in PWM mode

01 = CCP5 is based off Timer4 in PWM mode

10 = CCP5 is based off Timer6 in PWM mode

11 = Reserved

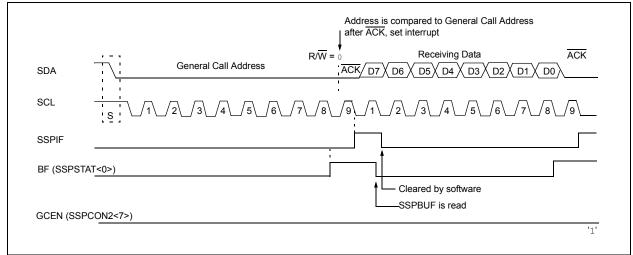

#### 24.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the I<sup>2</sup>C protocol, defined as address 0x00. When the GCEN bit of the SSPCON2 register is set, the Slave module will automatically ACK the reception of this address regardless of the value stored in SSPADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSPBUF and respond. shows a general Figure 24-24 call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSPCON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

#### 24.5.9 SSP MASK REGISTER

An SSP Mask (SSPMSK) register (Register 24-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSPSR register during an address comparison operation. A zero ('0') bit in the SSPMSK register has the effect of making the corresponding bit of the received address a "don't care".

This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

## 24.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPCON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt, if enabled):

- Start condition detected

- · Stop condition detected

- · Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

## 24.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received eight bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCL. See Section 24.7 "Baud Rate Generator" for more detail.

#### 25.1.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error Status bit. A framing error indicates that a Stop bit was not seen at the expected time. The framing error status is accessed via the FERR bit of the RCSTA register. The FERR bit represents the status of the top unread character in the receive FIFO. Therefore, the FERR bit must be read before reading the RCREG.

The FERR bit is read-only and only applies to the top unread character in the receive FIFO. A framing error (FERR = 1) does not preclude reception of additional characters. It is not necessary to clear the FERR bit. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERR bit can be forced clear by clearing the SPEN bit of the RCSTA register which resets the EUSART. Clearing the CREN bit of the RCSTA register does not affect the FERR bit. A framing error by itself does not generate an interrupt.

| Note: | If all receive characters in the receive  |

|-------|-------------------------------------------|

|       | FIFO have framing errors, repeated reads  |

|       | of the RCREG will not clear the FERR bit. |

#### 25.1.2.5 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before the FIFO is accessed. When this happens the OERR bit of the RCSTA register is set. The characters already in the FIFO buffer can be read but no additional characters will be received until the error is cleared. The error must be cleared by either clearing the CREN bit of the RCSTA register or by resetting the EUSART by clearing the SPEN bit of the RCSTA register.

#### 25.1.2.6 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth and Most Significant data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

#### 25.1.2.7 Address Detection

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems. Address detection is enabled by setting the ADDEN bit of the RCSTA register.

Address detection requires 9-bit character reception. When address detection is enabled, only characters with the ninth data bit set will be transferred to the receive FIFO buffer, thereby setting the RCIF interrupt bit. All other characters will be ignored.

Upon receiving an address character, user software determines if the address matches its own. Upon address match, user software must disable address detection by clearing the ADDEN bit before the next Stop bit occurs. When user software detects the end of the message, determined by the message protocol used, software places the receiver back into the Address Detection mode by setting the ADDEN bit.

| R/W-0/0          | R/W-0/0                                                                                                                                                                                                                          | R/W-0/0                              | R/W-0/0           | R/W-0/0         | R-0/0             | R-0/0            | R-x/x       |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------|-----------------|-------------------|------------------|-------------|--|--|--|--|

| SPEN             | RX9                                                                                                                                                                                                                              | SREN                                 | CREN              | ADDEN           | FERR              | OERR             | RX9D        |  |  |  |  |

| bit 7            | ·                                                                                                                                                                                                                                |                                      |                   |                 |                   |                  | bit C       |  |  |  |  |

|                  |                                                                                                                                                                                                                                  |                                      |                   |                 |                   |                  |             |  |  |  |  |

| Legend:          |                                                                                                                                                                                                                                  |                                      |                   |                 |                   |                  |             |  |  |  |  |

| R = Readable     | bit                                                                                                                                                                                                                              | W = Writable                         | bit               | U = Unimpler    | mented bit, read  | as '0'           |             |  |  |  |  |

| u = Bit is unch  | nanged                                                                                                                                                                                                                           | x = Bit is unki                      | nown              | -n/n = Value a  | at POR and BO     | R/Value at all o | ther Resets |  |  |  |  |

| '1' = Bit is set |                                                                                                                                                                                                                                  | '0' = Bit is cle                     | ared              |                 |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                                                                                                                  |                                      |                   |                 |                   |                  |             |  |  |  |  |

| bit 7            |                                                                                                                                                                                                                                  | Port Enable bi                       |                   |                 |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                                                                                                                  | ort enabled (cor<br>ort disabled (he |                   | I and IX/CK p   | ins as serial poi | rt pins)         |             |  |  |  |  |

| bit 6            |                                                                                                                                                                                                                                  | eceive Enable t                      |                   |                 |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                                                                                                                  | -bit reception                       |                   |                 |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                                                                                                                  | B-bit reception                      |                   |                 |                   |                  |             |  |  |  |  |

| bit 5            | SREN: Single                                                                                                                                                                                                                     | e Receive Enal                       | ole bit           |                 |                   |                  |             |  |  |  |  |

|                  | <u>Asynchronou</u>                                                                                                                                                                                                               | <u>s mode</u> :                      |                   |                 |                   |                  |             |  |  |  |  |

|                  | Don't care                                                                                                                                                                                                                       |                                      |                   |                 |                   |                  |             |  |  |  |  |

|                  | •                                                                                                                                                                                                                                | mode – Maste                         | <u>r</u> :        |                 |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                                                                                                                  | single receive                       |                   |                 |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                                                                                                                  | single receive<br>ared after rece    | ntion is compl    | oto             |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                                                                                                                  | mode – Slave                         |                   |                 |                   |                  |             |  |  |  |  |

|                  | Don't care                                                                                                                                                                                                                       |                                      |                   |                 |                   |                  |             |  |  |  |  |

| bit 4            | CREN: Conti                                                                                                                                                                                                                      | nuous Receive                        | Enable bit        |                 |                   |                  |             |  |  |  |  |

|                  | <u>Asynchronou</u>                                                                                                                                                                                                               | <u>s mode</u> :                      |                   |                 |                   |                  |             |  |  |  |  |

|                  | 1 = Enables                                                                                                                                                                                                                      |                                      |                   |                 |                   |                  |             |  |  |  |  |

|                  | 0 = Disables                                                                                                                                                                                                                     |                                      |                   |                 |                   |                  |             |  |  |  |  |

|                  | Synchronous                                                                                                                                                                                                                      |                                      |                   |                 |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                                                                                                                  | continuous rec                       |                   | DIE DIT CREN IS | cleared (CREN     | overrides SR     | EN)         |  |  |  |  |

| bit 3            |                                                                                                                                                                                                                                  | lress Detect Er                      |                   |                 |                   |                  |             |  |  |  |  |

|                  | <u>Asynchronou</u>                                                                                                                                                                                                               | <u>s mode 9-bit (F</u>               | RX9 = 1):         |                 |                   |                  |             |  |  |  |  |

|                  | 1 = Enables                                                                                                                                                                                                                      | address detect                       | ion, enable in    | terrupt and loa | d the receive bu  | uffer when RSR   | <8> is set  |  |  |  |  |

|                  | <ul> <li>1 = Enables address detection, enable interrupt and load the receive buffer when RSR&lt;8&gt; is set</li> <li>0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit</li> </ul> |                                      |                   |                 |                   |                  |             |  |  |  |  |

|                  |                                                                                                                                                                                                                                  | <u>s mode 8-bit (F</u>               | <u>RX9 = 0)</u> : |                 |                   |                  |             |  |  |  |  |

|                  | Don't care                                                                                                                                                                                                                       |                                      |                   |                 |                   |                  |             |  |  |  |  |

| bit 2            | FERR: Frami                                                                                                                                                                                                                      | 0                                    |                   |                 |                   |                  |             |  |  |  |  |

|                  | 1 = Framing<br>0 = No frami                                                                                                                                                                                                      |                                      | pdated by rea     | Iding RCREG I   | register and rec  | eive next valid  | byte)       |  |  |  |  |

| bit 1            | OERR: Over                                                                                                                                                                                                                       | run Error bit                        |                   |                 |                   |                  |             |  |  |  |  |

|                  | 1 = Overrun<br>0 = No overr                                                                                                                                                                                                      | error (can be c<br>un error          | leared by clea    | ring bit CREN   | )                 |                  |             |  |  |  |  |

| bit 0            | RX9D: Ninth                                                                                                                                                                                                                      | bit of Received                      | Data              |                 |                   |                  |             |  |  |  |  |

|                  | This can be a                                                                                                                                                                                                                    | ddrooo/doto bi                       | tor o pority bit  | and must be     | calculated by us  | or firmuoro      |             |  |  |  |  |

## REGISTER 25-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER<sup>(1)</sup>

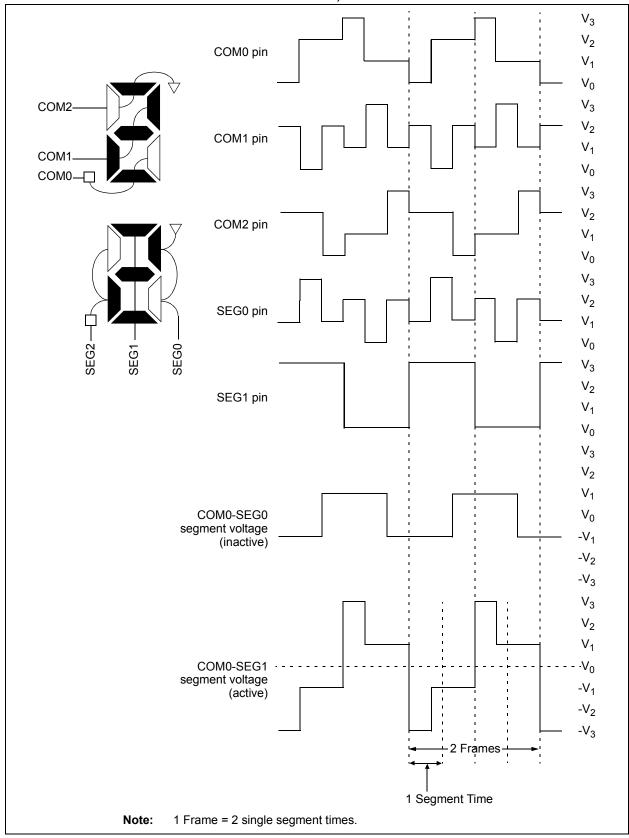

FIGURE 27-16: TYPE-B WAVEFORMS IN 1/3 MUX, 1/3 BIAS DRIVE

#### 30.2 DC Characteristics: PIC16F/LF1938/39-I/E (Industrial, Extended) (Continued)

| PIC16LF      | 1938/9                              |      | rd Operat              |      | -40°C ≤ T | A ≤ +85°                                              | <b>erwise stated)</b><br>C for industrial<br>°C for extended |

|--------------|-------------------------------------|------|------------------------|------|-----------|-------------------------------------------------------|--------------------------------------------------------------|

| PIC16F1938/9 |                                     |      | rd Operat<br>ng temper |      | -40°C ≤ T | erwise stated)<br>C for industrial<br>°C for extended |                                                              |

| Param        | Device                              | Min. | Тур†                   | Max. | Units     |                                                       | Conditions                                                   |

| No.          | Characteristics                     |      | <b>,</b> ,,,           | -    |           | VDD                                                   | Note                                                         |

| D017         | Supply Current (IDD) <sup>(1,</sup> | 2)   |                        |      |           |                                                       |                                                              |

| D017         |                                     | —    | 90                     | 160  | μA        | 1.8                                                   | Fosc = 500 kHz                                               |

|              |                                     | —    | 120                    | 190  | μA        | 3.0                                                   | MFINTOSC mode                                                |

| D017         |                                     | —    | 120                    | 190  | μA        | 1.8                                                   | Fosc = 500 kHz                                               |

|              |                                     | —    | 150                    | 240  | μA        | 3.0                                                   | MFINTOSC mode (Note 5)                                       |

|              |                                     | —    | 190                    | 320  | μA        | 5.0                                                   |                                                              |

| D018         |                                     | —    | 0.6                    | 0.8  | mA        | 1.8                                                   | Fosc = 8 MHz                                                 |

|              |                                     | —    | 1.0                    | 1.3  | mA        | 3.0                                                   | HFINTOSC mode                                                |

| D018         |                                     | —    | 0.7                    | 0.9  | mA        | 1.8                                                   | Fosc = 8 MHz                                                 |

|              |                                     | —    | 1.0                    | 1.4  | mA        | 3.0                                                   | HFINTOSC mode (Note 5)                                       |

|              |                                     | —    | 1.2                    | 1.5  | mA        | 5.0                                                   |                                                              |

| D019         |                                     | —    | 1.0                    | 1.2  | mA        | 1.8                                                   | Fosc = 16 MHz                                                |

|              |                                     | —    | 1.6                    | 2.0  | mA        | 3.0                                                   | HFINTOSC mode                                                |

| D019         |                                     | —    | 1.0                    | 1.3  | mA        | 1.8                                                   | Fosc = 16 MHz                                                |

|              |                                     | —    | 1.6                    | 2.0  | mA        | 3.0                                                   | HFINTOSC mode (Note 5)                                       |

|              |                                     | —    | 1.8                    | 2.2  | mA        | 5.0                                                   |                                                              |

| D020         |                                     | —    | 3.0                    | 3.9  | mA        | 3.0                                                   | Fosc = 32 MHz                                                |

|              |                                     | —    | 3.7                    | 4.6  | mA        | 3.6                                                   | HFINTOSC mode                                                |

| D020         |                                     |      | 3.0                    | 3.9  | mA        | 3.0                                                   | Fosc = 32 MHz                                                |

|              |                                     | —    | 3.3                    | 4.1  | mA        | 5.0                                                   | HFINTOSC mode                                                |

| D021         |                                     | —    | 200                    | 300  | μA        | 1.8                                                   | Fosc = 4 MHz                                                 |

|              |                                     | —    | 350                    | 490  | μA        | 3.0                                                   | EXTRC mode (Note 3)                                          |

| D021         |                                     | —    | 210                    | 300  | μA        | 1.8                                                   | Fosc = 4 MHz                                                 |

|              |                                     |      | 370                    | 500  | μA        | 3.0                                                   | EXTRC mode (Note 3, Note 5)                                  |

|              |                                     | —    | 460                    | 590  | μA        | 5.0                                                   |                                                              |

| D022         |                                     | _    | 3.0                    | 3.9  | mA        | 3.0                                                   | Fosc = 32 MHz                                                |

|              |                                     | —    | 3.7                    | 4.6  | mA        | 3.6                                                   | HS Oscillator mode (Note 6)                                  |

| D022         |                                     | —    | 3.0                    | 3.9  | mA        | 3.0                                                   | Fosc = 32 MHz                                                |

|              |                                     | _    | 3.3                    | 4.1  | mA        | 5.0                                                   | HS Oscillator mode (Note 5, Note 6)                          |

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

- 4: FVR and BOR are disabled.

- 5: 0.1 μF capacitor on VCAP (RA0).

6: 8 MHz crystal oscillator with 4x PLL enabled.

|              | DC C | HARACTERISTICS                            | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |          |       |                                                                         |  |  |  |

|--------------|------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|-------------------------------------------------------------------------|--|--|--|

| Param<br>No. | Sym. | Characteristic                            | Min.                                                                                                                                                                                    | Тур† | Max.     | Units | Conditions                                                              |  |  |  |

|              | VIL  | Input Low Voltage                         |                                                                                                                                                                                         |      |          |       |                                                                         |  |  |  |

|              |      | I/O PORT:                                 |                                                                                                                                                                                         |      |          |       |                                                                         |  |  |  |

| D032         |      | with TTL buffer                           | —                                                                                                                                                                                       | _    | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                        |  |  |  |

| D032A        |      |                                           | —                                                                                                                                                                                       | _    | 0.15 VDD | V     | $1.8V \le V\text{DD} \le 4.5V$                                          |  |  |  |

| D033         |      | with Schmitt Trigger buffer               | _                                                                                                                                                                                       | _    | 0.2 VDD  | V     | $2.0V \le V\text{DD} \le 5.5V$                                          |  |  |  |

|              |      | with I <sup>2</sup> C <sup>™</sup> levels | _                                                                                                                                                                                       | _    | 0.3 VDD  | V     |                                                                         |  |  |  |

|              |      | with SMBus levels                         |                                                                                                                                                                                         | _    | 0.8      | V     | $2.7V \le V\text{DD} \le 5.5V$                                          |  |  |  |

| D034         |      | MCLR, OSC1 (RC mode) <sup>(1)</sup>       | _                                                                                                                                                                                       | _    | 0.2 VDD  | V     |                                                                         |  |  |  |

| D034A        |      | OSC1 (HS mode)                            | _                                                                                                                                                                                       |      | 0.3 VDD  | V     |                                                                         |  |  |  |

|              | VIH  | Input High Voltage                        | ,I                                                                                                                                                                                      |      |          |       |                                                                         |  |  |  |

|              |      | I/O ports:                                |                                                                                                                                                                                         |      |          |       |                                                                         |  |  |  |

| D040         |      | with TTL buffer                           | 2.0                                                                                                                                                                                     |      |          | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                        |  |  |  |

| D040A        |      |                                           | 0.25 VDD +<br>0.8                                                                                                                                                                       | _    | _        | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                        |  |  |  |

| D041         |      | with Schmitt Trigger buffer               | 0.8 VDD                                                                                                                                                                                 | _    | _        | V     | $2.0V \le VDD \le 5.5V$                                                 |  |  |  |

|              |      | with I <sup>2</sup> C <sup>™</sup> levels | 0.7 Vdd                                                                                                                                                                                 |      | _        | V     |                                                                         |  |  |  |

|              |      | with SMBus levels                         | 2.1                                                                                                                                                                                     |      | _        | V     | $2.7V \le VDD \le 5.5V$                                                 |  |  |  |

| D042         |      | MCLR                                      | 0.8 VDD                                                                                                                                                                                 |      | _        | V     |                                                                         |  |  |  |

| D043A        |      | OSC1 (HS mode)                            | 0.7 VDD                                                                                                                                                                                 | _    | _        | V     |                                                                         |  |  |  |

| D043B        |      | OSC1 (RC mode)                            | 0.9 Vdd                                                                                                                                                                                 |      | _        | V     | (Note 1) VDD > 2.0V                                                     |  |  |  |

|              | lı∟  | Input Leakage Current <sup>(2)</sup>      |                                                                                                                                                                                         |      |          |       |                                                                         |  |  |  |

| D060         |      | I/O ports                                 | —                                                                                                                                                                                       | ± 5  | ± 125    | nA    | $Vss \le VPIN \le VDD$ , Pin at high-impedance @ 85°C                   |  |  |  |

|              |      |                                           |                                                                                                                                                                                         | ± 5  | ± 1000   | nA    | 125°C                                                                   |  |  |  |

| D061         |      | MCLR <sup>(3)</sup>                       | —                                                                                                                                                                                       | ± 50 | ± 200    | nA    | $Vss \le V \text{PIN} \le V \text{DD} \ \textcircled{0} \ 85^\circ C$   |  |  |  |

|              | IPUR | Weak Pull-up Current                      |                                                                                                                                                                                         |      |          |       |                                                                         |  |  |  |

| D070*        |      |                                           | 25                                                                                                                                                                                      | 100  | 200      |       | VDD = 3.3V, VPIN = VSS                                                  |  |  |  |

|              |      |                                           | 25                                                                                                                                                                                      | 140  | 300      | μA    | VDD = 5.0V, VPIN = VSS                                                  |  |  |  |

|              | VOL  | Output Low Voltage <sup>(4)</sup>         |                                                                                                                                                                                         |      |          |       | 1                                                                       |  |  |  |

| D080         |      | I/O ports                                 | _                                                                                                                                                                                       | _    | 0.6      | v     | IOL = 8mA, VDD = 5V<br>IOL = 6mA, VDD = 3.3V<br>IOL = 1.8mA, VDD = 1.8V |  |  |  |

|              | Voн  | Output High Voltage <sup>(4)</sup>        | 11                                                                                                                                                                                      |      | 1        | 1     | <u>ı</u>                                                                |  |  |  |

| D090         |      | I/O ports                                 | Vdd - 0.7                                                                                                                                                                               |      | _        | v     | ІОН = 3.5mA, VDD = 5V<br>ІОН = 3mA, VDD = 3.3V<br>ІОН = 1mA, VDD = 1.8V |  |  |  |

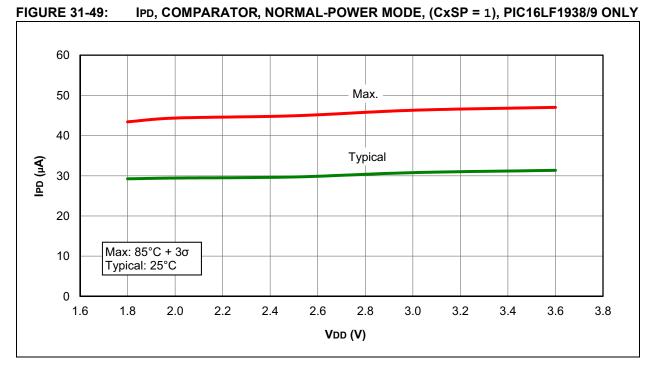

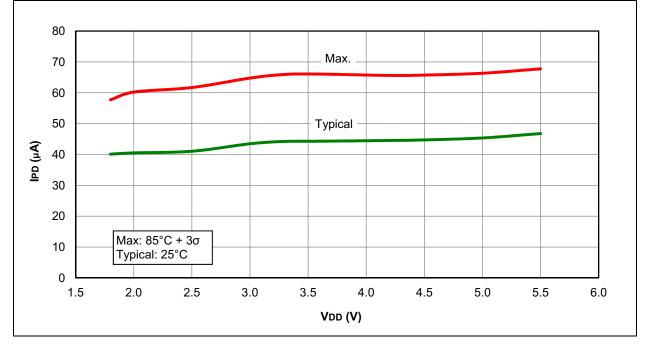

### 30.4 DC Characteristics: PIC16(L)F1938/39-I/E

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.