Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 28KB (16K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 1K x 8                                                                    |

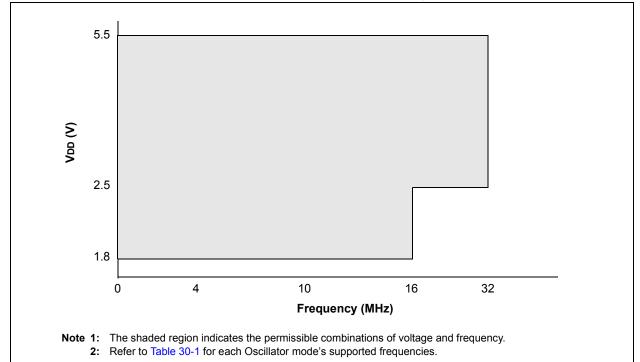

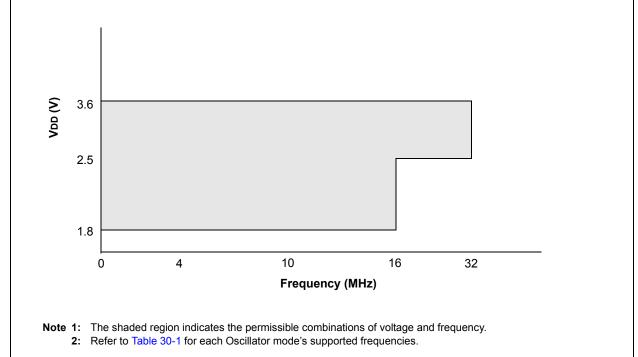

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 14x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1939-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address                | Name    | Bit 7                                   | Bit 6                                                    | Bit 5          | Bit 4         | Bit 3        | Bit 2       | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|---------|-----------------------------------------|----------------------------------------------------------|----------------|---------------|--------------|-------------|-------|-------|----------------------|---------------------------------|

| Bank 4                 |         |                                         |                                                          |                |               |              |             |       |       |                      |                                 |

| 200h <sup>(2)</sup>    | INDF0   |                                         | this location ical register)                             | uses contents  | s of FSR0H/F  | SR0L to addr | ess data me | mory  |       | XXXX XXXX            | XXXX XXXX                       |

| 201h <sup>(2)</sup>    | INDF1   |                                         | this location ical register)                             | uses contents  | s of FSR1H/F  | SR1L to addr | ess data me | mory  |       | XXXX XXXX            | XXXX XXXX                       |

| 202h <sup>(2)</sup>    | PCL     | Program Co                              | ounter (PC) L                                            | east Significa | int Byte      |              |             |       |       | 0000 0000            | 0000 0000                       |

| 203h <sup>(2)</sup>    | STATUS  | —                                       | _                                                        | _              | TO            | PD           | Z           | DC    | С     | 1 1000               | q quuu                          |

| 204h <sup>(2)</sup>    | FSR0L   | Indirect Dat                            | ta Memory Ac                                             | Idress 0 Low   | Pointer       |              |             |       |       | 0000 0000            | uuuu uuuu                       |

| 205h <sup>(2)</sup>    | FSR0H   | Indirect Dat                            | ta Memory Ac                                             | ldress 0 High  | Pointer       |              |             |       |       | 0000 0000            | 0000 0000                       |

| 206h <sup>(2)</sup>    | FSR1L   | Indirect Dat                            | ta Memory Ac                                             | Idress 1 Low   | Pointer       |              |             |       |       | 0000 0000            | uuuu uuuu                       |

| 207h <sup>(2)</sup>    | FSR1H   | Indirect Dat                            | ta Memory Ac                                             | ldress 1 High  | Pointer       |              |             |       |       | 0000 0000            | 0000 0000                       |

| 208h <sup>(2)</sup>    | BSR     | _                                       | _                                                        | —              |               |              | BSR<4:0>    |       |       | 0 0000               | 0 0000                          |

| 209h <sup>(2)</sup>    | WREG    | Working Re                              | egister                                                  |                |               |              |             |       |       | 0000 0000            | uuuu uuuu                       |

| 20Ah <sup>(1, 2)</sup> | PCLATH  | _                                       | Write Buffer for the upper 7 bits of the Program Counter |                |               |              |             |       |       | -000 0000            | -000 0000                       |

| 20Bh <sup>(2)</sup>    | INTCON  | GIE                                     | PEIE                                                     | TMR0IE         | INTE          | IOCIE        | TMR0IF      | INTF  | IOCIF | 0000 0000            | 0000 0000                       |

| 20Ch                   | —       | Unimpleme                               | nted                                                     |                |               |              |             |       |       | _                    | _                               |

| 20Dh                   | WPUB    | WPUB7                                   | WPUB6                                                    | WPUB5          | WPUB4         | WPUB3        | WPUB2       | WPUB1 | WPUB0 | 1111 1111            | 1111 1111                       |

| 20Eh                   | —       | Unimpleme                               | nted                                                     |                | •             | •            |             | •     | •     | _                    | _                               |

| 20Fh                   | —       | Unimpleme                               | nted                                                     |                |               |              |             |       |       | _                    | _                               |

| 210h                   | WPUE    | —                                       | _                                                        | _              | _             | WPUE3        | _           | —     | —     | 1                    | 1                               |

| 211h                   | SSPBUF  | Synchronou                              | us Serial Port                                           | Receive Buff   | er/Transmit R | legister     |             |       |       | XXXX XXXX            | uuuu uuuu                       |

| 212h                   | SSPADD  |                                         |                                                          |                | ADD<          | 7:0>         |             |       |       | 0000 0000            | 0000 0000                       |

| 213h                   | SSPMSK  |                                         |                                                          |                | MSK<          | 7:0>         |             |       |       | 1111 1111            | 1111 1111                       |

| 214h                   | SSPSTAT | SMP                                     | CKE                                                      | D/A            | Р             | S            | R/W         | UA    | BF    | 0000 0000            | 0000 0000                       |

| 215h                   | SSPCON1 | WCOL                                    | SSPOV                                                    | SSPEN          | СКР           |              | SSPM        | <3:0> |       | 0000 0000            | 0000 0000                       |

| 216h                   | SSPCON2 | GCEN                                    | ACKSTAT                                                  | ACKDT          | ACKEN         | RCEN         | PEN         | RSEN  | SEN   | 0000 0000            | 0000 0000                       |

| 217h                   | SSPCON3 | ACKTIM                                  | PCIE                                                     | SCIE           | BOEN          | SDAHT        | SBCDE       | AHEN  | DHEN  | 0000 0000            | 0000 0000                       |

| 218h                   | _       | Unimpleme                               | nted                                                     |                | I             | I            | 1           |       |       | _                    | _                               |

| 219h                   | _       | · · ·                                   | Unimplemented                                            |                |               |              |             |       |       | _                    | _                               |

| 21Ah                   | _       | · · ·                                   | Unimplemented                                            |                |               |              |             |       |       | _                    | _                               |

| 21Bh                   | _       | · · ·                                   | Unimplemented                                            |                |               |              |             |       |       | _                    | _                               |

| 21Ch                   | _       | - ·                                     | Unimplemented                                            |                |               |              |             |       |       | _                    | _                               |

| 21Dh                   | _       | · · ·                                   | Jnimplemented                                            |                |               |              |             |       |       | _                    | _                               |

| 21Eh                   | _       | · · ·                                   | nimplemented                                             |                |               |              |             |       |       | _                    | _                               |

| 21Fh                   | _       | - · · · · · · · · · · · · · · · · · · · | Jnimplemented                                            |                |               |              |             |       |       | _                    | _                               |

### TABLE 3-10: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

**Note** 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: These registers/bits are not implemented on PIC16(L)F1938 devices, read as '0'.

4: Unimplemented, read as '1'.

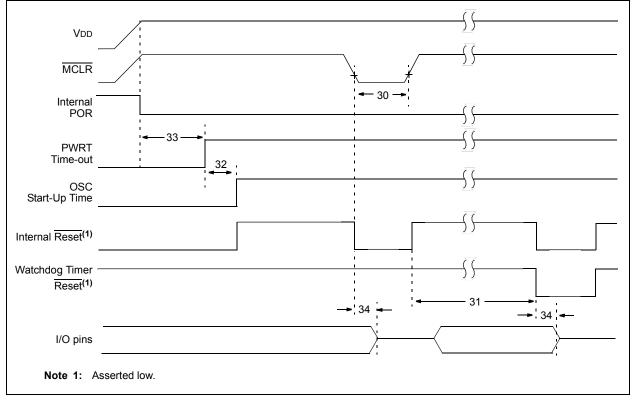

### 6.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

### 6.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms timeout on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

### 6.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 6-3 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 6-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Device<br>Operation upon<br>release of POR | Device<br>Operation upon<br>wake- up from<br>Sleep |  |

|------------|--------|-------------|----------|--------------------------------------------|----------------------------------------------------|--|

| 11         | Х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup>         |                                                    |  |

| 1.0        |        | Awake       | Active   | Waits for BOR ready                        |                                                    |  |

| 10         | Х      | Sleep       | Disabled |                                            |                                                    |  |

| 0.1        | 1      | х           | Active   | Begins immediately                         |                                                    |  |

| 01         | 0      | ^           | Disabled | Begins immediately                         |                                                    |  |

| 00         | Х      | х           | Disabled | Begins immediately                         |                                                    |  |

### TABLE 6-1:BOR OPERATING MODES

Note 1: In these specific cases, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold. BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device startup is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

### 7.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to the Section 9.0 "Power-Down Mode (Sleep)" for more details.

### 7.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. This interrupt is enabled by setting the INTE bit of the INTCON register. The INTEDG bit of the OPTION\_REG register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

### 7.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|---------|--------|--------|--------|--------|--------|---------|--------|---------------------|

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF    | IOCIF  | 90                  |

| OPTION_REG | WPUEN   | INTEDG | TMROCS | TMROSE | PSA    |        | PS<2:0> |        | 187                 |

| PIE1       | TMR1GIE | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE  | TMR1IE | 91                  |

| PIE2       | OSFIE   | C2IE   | C1IE   | EEIE   | BCLIE  | LCDIE  | _       | CCP2IE | 92                  |

| PIE3       | _       | CCP5IE | CCP4IE | CCP3IE | TMR6IE | _      | TMR4IE  | _      | 93                  |

| PIR1       | TMR1GIF | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF  | TMR1IF | 94                  |

| PIR2       | OSFIF   | C2IF   | C1IF   | EEIF   | BCLIF  | LCDIF  |         | CCP2IF | 95                  |

| PIR3       | —       | CCP5IF | CCP4IF | CCP3IF | TMR6IF | _      | TMR4IF  |        | 96                  |

TABLE 7-1:

SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Interrupts.

### 11.2 Using the Data EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). When variables in one section change frequently, while variables in another section do not change, it is possible to exceed the total number of write cycles to the EEPROM without exceeding the total number of write cycles to a single byte. Refer to **Section 30.0 "Electrical Specifications"**. If this is the case, then a refresh of the array must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

### 11.2.1 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the EEADRL register, clear the EEPGD and CFGS control bits of the EECON1 register, and then set control bit RD. The data is available at the very next cycle, in the EEDATL register; therefore, it can be read in the next instruction. EEDATL will hold this value until another read or until it is written to by the user (during a write operation).

### EXAMPLE 11-1: DATA EEPROM READ

| BANKSEL | EEADRL  |       | ;                      |

|---------|---------|-------|------------------------|

| MOVLW   | DATA_EE | ADDR  | ;                      |

| MOVWF   | EEADRL  |       | ;Data Memory           |

|         |         |       | ;Address to read       |

| BCF     | EECON1, | CFGS  | ;Deselect Config space |

| BCF     | EECON1, | EEPGI | ;Point to DATA memory  |

| BSF     | EECON1, | RD    | ;EE Read               |

| MOVF    | EEDATL, | W     | ;W = EEDATL            |

|         |         |       |                        |

### Note: Data EEPROM can be read regardless of the setting of the CPD bit.

## 11.2.2 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the user must first write the address to the EEADRL register and the data to the EEDATL register. Then the user must follow a specific sequence to initiate the write for each byte.

The write will not initiate if the above sequence is not followed exactly (write 55h to EECON2, write AAh to EECON2, then set the WR bit) for each byte. Interrupts should be disabled during this code segment.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. EEIF must be cleared by software.

### 11.2.3 PROTECTION AGAINST SPURIOUS WRITE

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, WREN is cleared. Also, the Power-up Timer (64 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during:

- Brown-out

- Power Glitch

- Software Malfunction

### 11.2.4 DATA EEPROM OPERATION DURING CODE-PROTECT

Data memory can be code-protected by programming the  $\overline{CPD}$  bit in the Configuration Words to '0'.

When the data memory is code-protected, only the CPU is able to read and write data to the data EEPROM. It is recommended to code-protect the program memory when code-protecting data memory. This prevents anyone from replacing your program with a program that will access the contents of the data EEPROM.

| TABLE 10-1. | 0000   |        |        |        |        |        |        |        |                     |

|-------------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| Name        | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

| ANSELB      |        |        | ANSB5  | ANSB4  | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 131                 |

| INTCON      | GIE    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 90                  |

| IOCBF       | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3 | IOCBF2 | IOCBF1 | IOCBF0 | 145                 |

| IOCBN       | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3 | IOCBN2 | IOCBN1 | IOCBN0 | 145                 |

| IOCBP       | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3 | IOCBP2 | IOCBP1 | IOCBP0 | 145                 |

| TRISB       | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 130                 |

### TABLE 13-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Interrupt-on-Change.

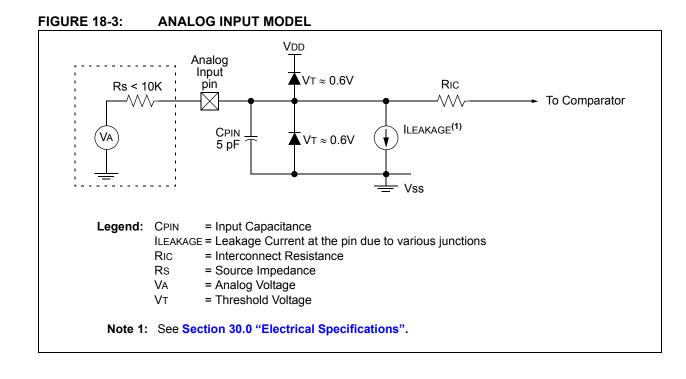

### 15.4 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 15-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 15-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the

source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 15-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

### EQUATION 15-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V VDD$

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} ; [1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{CHOLD} ; [2] V_{CHOLD} charge response to V_{APPLIED} (1 - e^{\frac{-Tc}{RC}}) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) ; combining [1] and [2]$$

*Note: Where* n = number *of bits of the ADC.*

Solving for TC:

$$T_{C} = -C_{HOLD}(R_{IC} + R_{SS} + R_{S}) \ln(1/2047)$$

= -13.5pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)

= 1.20\mu\_{S}

Therefore:

$$TACQ = 2\mu s + 1.20\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.45\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

### 21.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 21-1 displays the Timer1 enable selections.

| TABLE 21-1: | TIMER1 ENABLE |

|-------------|---------------|

|             | SELECTIONS    |

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

### 21.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 21-2 displays the clock source selections.

### 21.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1 gate

- C1 or C2 comparator input to Timer1 gate

### 21.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI or the capacitive sensing oscillator signal. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

- **Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

| TMR1CS<1:0> | T1OSCEN | Clock Source                          |

|-------------|---------|---------------------------------------|

| 11          | х       | Capacitive Sensing Oscillator, CPSCLK |

| 10          | 0       | External Clocking on T1CKI Pin        |

| 01          | х       | System Clock (Fosc)                   |

| 00          | Х       | Instruction Clock (Fosc/4)            |

### TABLE 21-2: CLOCK SOURCE SELECTIONS

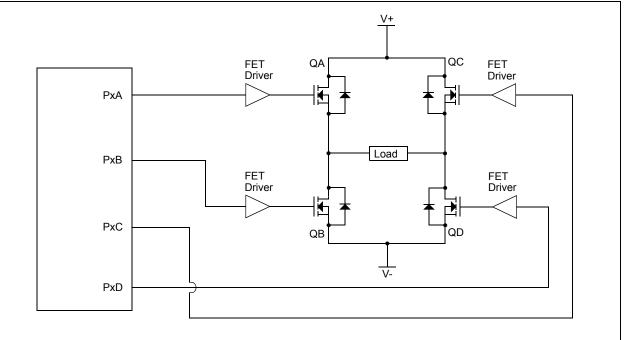

### 23.4.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of Full-Bridge application is shown in Figure 23-10.

In the Forward mode, pin CCPx/PxA is driven to its active state, pin PxD is modulated, while PxB and PxC will be driven to their inactive state as shown in Figure 23-11.

In the Reverse mode, PxC is driven to its active state, pin PxB is modulated, while PxA and PxD will be driven to their inactive state as shown Figure 23-11.

PxA, PxB, PxC and PxD outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the PxA, PxB, PxC and PxD pins as outputs.

### FIGURE 23-10: EXAMPLE OF FULL-BRIDGE APPLICATION

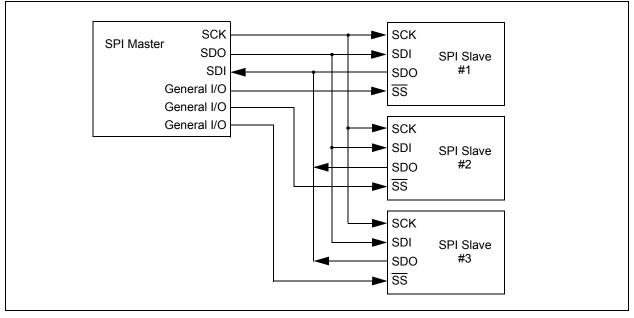

### 24.2.1 SPI MODE REGISTERS

The MSSP module has five registers for SPI mode operation. These are:

- MSSP STATUS register (SSPSTAT)

- MSSP Control Register 1 (SSPCON1)

- MSSP Control Register 3 (SSPCON3)

- MSSP Data Buffer register (SSPBUF)

- MSSP Address register (SSPADD)

- MSSP Shift register (SSPSR) (Not directly accessible)

SSPCON1 and SSPSTAT are the control and STATUS registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower six bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

In one SPI Master mode, SSPADD can be loaded with a value used in the Baud Rate Generator. More information on the Baud Rate Generator is available in Section 24.7 "Baud Rate Generator".

SSPSR is the shift register used for shifting data in and out. SSPBUF provides indirect access to the SSPSR register. SSPBUF is the buffer register to which data bytes are written, and from which data bytes are read.

In receive operations, SSPSR and SSPBUF together create a buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

| FIGURE 25-12:                            | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                   |

|------------------------------------------|-----------------------------------------------------------------------------|

| RX/DT<br>pin<br>TX/CK pin<br>(SCKP = 0)  |                                                                             |

| TX/CK pin                                |                                                                             |

| SREN bit                                 | ·0'                                                                         |

| RCIF bit<br>(Interrupt)<br>Read<br>RXREG |                                                                             |

| Note: Timing dia                         | gram demonstrates Sync Master mode with bit SREN = $1$ and bit BRGH = $0$ . |

### TABLE 25-8:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>RECEPTION

| Name    | Bit 7     | Bit 6      | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-----------|------------|------------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF    | RCIDL      | —          | SCKP   | BRG16  | —      | WUE    | ABDEN  | 298                 |

| INTCON  | GIE       | PEIE       | TMR0IE     | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 90                  |

| PIE1    | TMR1GIE   | ADIE       | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 91                  |

| PIR1    | TMR1GIF   | ADIF       | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 94                  |

| RCREG   | EUSART R  | eceive Dat | a Register |        |        |        |        |        | 292*                |

| RCSTA   | SPEN      | RX9        | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 297                 |

| SPBRGL  | BRG<7:0>  |            |            |        |        |        |        | 299*   |                     |

| SPBRGH  | BRG<15:8> |            |            |        |        |        |        | 299*   |                     |

| TRISC   | TRISC7    | TRISC6     | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 134                 |

| TXSTA   | CSRC      | TX9        | TXEN       | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 296                 |

**Legend:** — = unimplemented location read as '0'. Shaded cells are not used for synchronous master reception.

\* Page provides register information.

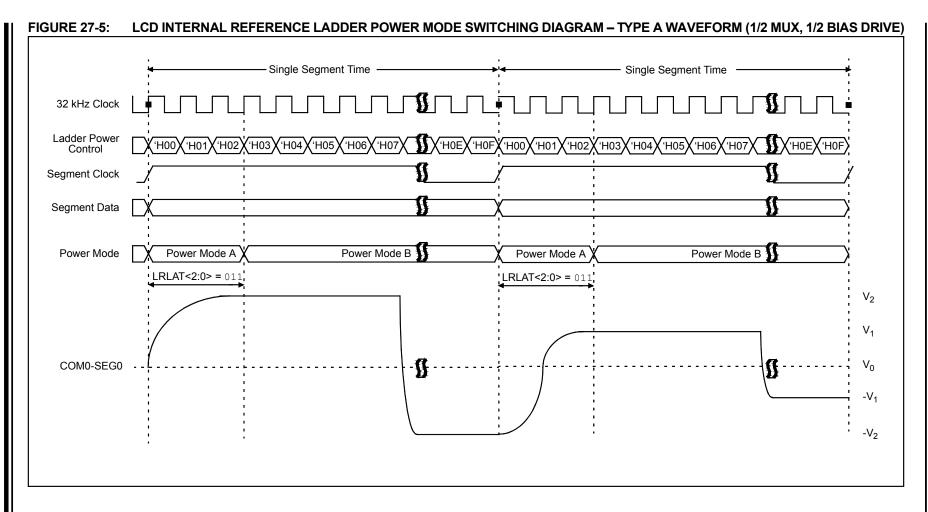

### 27.11 LCD Interrupts

The LCD module provides an interrupt in two cases. An interrupt when the LCD controller goes from active to inactive controller. An interrupt also provides unframed boundaries for Type B waveform. The LCD timing generation provides an interrupt that defines the LCD frame timing.

### 27.11.1 LCD INTERRUPT ON MODULE SHUTDOWN

An LCD interrupt is generated when the module completes shutting down (LCDA goes from '1' to '0').

### 27.11.2 LCD FRAME INTERRUPTS

A new frame is defined to begin at the leading edge of the COM0 common signal. The interrupt will be set immediately after the LCD controller completes accessing all pixel data required for a frame. This will occur at a fixed interval before the frame boundary (TFINT), as shown in Figure 27-19. The LCD controller will begin to access data for the next frame within the interval from the interrupt to when the controller begins to access data after the interrupt (TFWR). New data must be written within TFWR, as this is when the LCD controller will begin to access the data for the next frame.

When the LCD driver is running with Type-B waveforms and the LMUX<1:0> bits are not equal to '00' (static drive), there are some additional issues that must be addressed. Since the DC voltage on the pixel takes two frames to maintain zero volts, the pixel data must not change between subsequent frames. If the pixel data were allowed to change, the waveform for the odd frames would not necessarily be the complement of the waveform generated in the even frames and a DC component would be introduced into the panel. Therefore, when using Type-B waveforms, the user must synchronize the LCD pixel updates to occur within a subframe after the frame interrupt.

To correctly sequence writing while in Type-B, the interrupt will only occur on complete phase intervals. If the user attempts to write when the write is disabled, the WERR bit of the LCDCON register is set and the write does not occur.

| Note: | The LCD frame interrupt is not generated |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|

|       | when the Type-A waveform is selected     |  |  |  |  |  |

|       | and when the Type-B with no multiplex    |  |  |  |  |  |

|       | (static) is selected.                    |  |  |  |  |  |

#### **TABLE 30-4**: **CLKOUT AND I/O TIMING PARAMETERS**

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature -40°C $\leq$ TA $\leq$ +125°C |          |                                                              |               |          |          |       |                              |

|----------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------|---------------|----------|----------|-------|------------------------------|

| Param<br>No.                                                                                                   | Sym.     | Characteristic                                               | Min.          | Тур†     | Max.     | Units | Conditions                   |

| OS11                                                                                                           | TosH2ckL | Fosc↑ to CLKOUT↓ <sup>(1)</sup>                              |               | _        | 70       | ns    | VDD = 3.3-5.0V               |

| OS12                                                                                                           | TosH2ckH | Fosc↑ to CLKOUT↑ <sup>(1)</sup>                              | _             | _        | 72       | ns    | VDD = 3.3-5.0V               |

| OS13                                                                                                           | TckL2ioV | CLKOUT↓ to Port out valid <sup>(1)</sup>                     | —             | _        | 20       | ns    |                              |

| OS14                                                                                                           | TioV2ckH | Port input valid before CLKOUT↑ <sup>(1)</sup>               | Tosc + 200 ns | _        | _        | ns    |                              |

| OS15                                                                                                           | TosH2ioV | Fosc↑ (Q1 cycle) to Port out valid                           | —             | 50       | 70*      | ns    | VDD = 3.3-5.0V               |

| OS16                                                                                                           | TosH2iol | Fosc↑ (Q2 cycle) to Port input invalid<br>(I/O in hold time) | 50            |          | _        | ns    | VDD = 3.3-5.0V               |

| OS17                                                                                                           | TioV2osH | Port input valid to Fosc↑ (Q2 cycle)<br>(I/O in setup time)  | 20            | _        |          | ns    |                              |

| OS18                                                                                                           | TioR     | Port output rise time                                        | _             | 40<br>15 | 72<br>32 | ns    | VDD = 1.8V<br>VDD = 3.3-5.0V |

| OS19                                                                                                           | TioF     | Port output fall time                                        |               | 28<br>15 | 55<br>30 | ns    | VDD = 1.8V<br>VDD = 3.3-5.0V |

| OS20*                                                                                                          | Tinp     | INT pin input high or low time                               | 25            | _        | _        | ns    |                              |

| OS21*                                                                                                          | Tioc     | Interrupt-on-change new input level time                     | 25            |          | _        | ns    |                              |

|                                                                                                                | Tioc     | Interrupt-on-change new input level                          | _             |          | _        |       |                              |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. t

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

#### **FIGURE 30-8:** RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

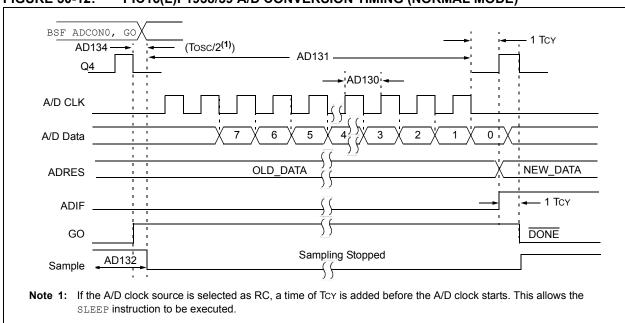

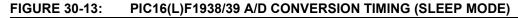

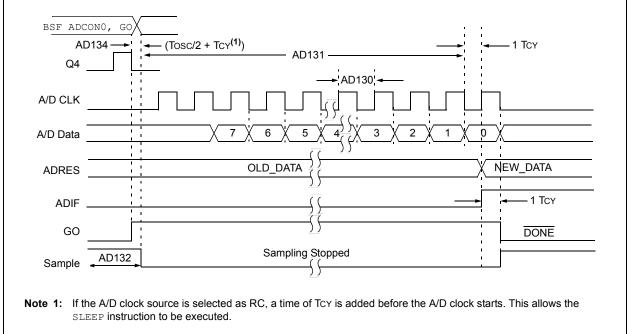

### FIGURE 30-12: PIC16(L)F1938/39 A/D CONVERSION TIMING (NORMAL MODE)

NOTES:

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620772690

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.