Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 14x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1939t-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 7.6 Register Definitions: Interrupt Control

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0/0          | R/W-0/0                       | R/W-0/0                                                    | R/W-0/0          | R/W-0/0        | R/W-0/0          | R/W-0/0           | R-0/0      |

|------------------|-------------------------------|------------------------------------------------------------|------------------|----------------|------------------|-------------------|------------|

| GIE              | PEIE                          | TMR0IE                                                     | INTE             | IOCIE          | TMR0IF           | INTF              | IOCIF      |

| bit 7            |                               |                                                            |                  |                |                  |                   | bit        |

|                  |                               |                                                            |                  |                |                  |                   |            |

| Legend:          |                               |                                                            |                  |                |                  |                   |            |

| R = Readable     |                               | W = Writable                                               |                  | -              | nented bit, read |                   |            |

| u = Bit is uncl  | 0                             | x = Bit is unki                                            |                  | -n/n = Value a | at POR and BO    | R/Value at all of | her Resets |

| '1' = Bit is set |                               | '0' = Bit is cle                                           | ared             |                |                  |                   |            |

| bit 7            | GIE: Global I                 | Interrupt Enable                                           | e bit            |                |                  |                   |            |

|                  | 1 = Enables a<br>0 = Disables | all active interru<br>all interrupts                       | upts             |                |                  |                   |            |

| bit 6            | 1 = Enables                   | eral Interrupt E<br>all active periph<br>all peripheral ir | neral interrupts | 3              |                  |                   |            |

| bit 5            | 1 = Enables f                 | ner0 Overflow Ir<br>the Timer0 inte<br>the Timer0 inte     | rrupt            | e bit          |                  |                   |            |

| bit 4            | 1 = Enables f                 | kternal Interrupt<br>the INT externa<br>the INT externa    | al interrupt     |                |                  |                   |            |

| bit 3            | 1 = Enables f                 | upt-on-Change<br>the interrupt-on<br>the interrupt-or      | -change          |                |                  |                   |            |

| bit 2            | 1 = TMR0 reg                  | ner0 Overflow Ir<br>gister has over<br>gister did not o    | flowed           | it             |                  |                   |            |

| bit 1            | 1 = The INT                   | kternal Interrupt<br>external interru<br>external interru  | pt occurred      | ır             |                  |                   |            |

| bit 0            |                               | upt-on-Change<br>least one of the                          | e interrupt-on-o | change pins ch |                  |                   |            |

**Note 1:** The IOCIF Flag bit is read-only and cleared when all the Interrupt-on-Change flags in the IOCBF register have been cleared by software.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

| R/W-0/0        | ) R/W-0/0                         | R/W-0/0                                                  | R/W-0/0        | R/W-0/0        | R/W-0/0          | U-0            | R/W-0/0      |  |  |  |  |

|----------------|-----------------------------------|----------------------------------------------------------|----------------|----------------|------------------|----------------|--------------|--|--|--|--|

| OSFIF          | C2IF                              | C1IF                                                     | EEIF           | BCLIF          | LCDIF            | _              | CCP2IF       |  |  |  |  |

| bit 7          | ·                                 |                                                          |                |                |                  |                | bit 0        |  |  |  |  |

|                |                                   |                                                          |                |                |                  |                |              |  |  |  |  |

| Legend:        |                                   |                                                          |                |                |                  |                |              |  |  |  |  |

| R = Reada      | ble bit                           | W = Writable                                             | bit            | U = Unimpler   | mented bit, read | as '0'         |              |  |  |  |  |

| u = Bit is u   | 0                                 | x = Bit is unk                                           |                | -n/n = Value a | at POR and BOF   | R/Value at all | other Resets |  |  |  |  |

| '1' = Bit is : | set                               | '0' = Bit is cle                                         | ared           |                |                  |                |              |  |  |  |  |

| bit 7          | <b>OSFIF:</b> Osci                | llator Fail Interr                                       | upt Flag       |                |                  |                |              |  |  |  |  |

|                | 1 = Interrupt                     |                                                          |                |                |                  |                |              |  |  |  |  |

|                | 0 = Interrupt                     | is not pending                                           |                |                |                  |                |              |  |  |  |  |

| bit 6          | C2IF: Comp                        | arator C2 Interr                                         | upt Flag       |                |                  |                |              |  |  |  |  |

|                | 1 = Interrupt                     |                                                          |                |                |                  |                |              |  |  |  |  |

| 6.4 F          | •                                 | is not pending                                           |                |                |                  |                |              |  |  |  |  |

| bit 5          | •                                 | C1IF: Comparator C1 Interrupt Flag                       |                |                |                  |                |              |  |  |  |  |

|                |                                   | 1 = Interrupt is pending<br>0 = Interrupt is not pending |                |                |                  |                |              |  |  |  |  |

| bit 4          | •                                 | EEIF: EEPROM Write Completion Interrupt Flag bit         |                |                |                  |                |              |  |  |  |  |

|                |                                   | 1 = Interrupt is pending                                 |                |                |                  |                |              |  |  |  |  |

|                | 0 = Interrupt                     | is not pending                                           |                |                |                  |                |              |  |  |  |  |

| bit 3          | BCLIF: MSS                        | SP Bus Collision                                         | Interrupt Flag | ) bit          |                  |                |              |  |  |  |  |

|                |                                   | 1 = Interrupt is pending                                 |                |                |                  |                |              |  |  |  |  |

| hit O          |                                   | is not pending                                           | nt Eloa hit    |                |                  |                |              |  |  |  |  |

| bit 2          | 1 = Interrupt                     | Module Interru                                           | pt Flag bit    |                |                  |                |              |  |  |  |  |

|                |                                   | is not pending                                           |                |                |                  |                |              |  |  |  |  |

| bit 1          | Unimpleme                         | nted: Read as                                            | 0'             |                |                  |                |              |  |  |  |  |

| bit 0          | CCP2IF: CC                        | P2 Interrupt Fla                                         | ng bit         |                |                  |                |              |  |  |  |  |

|                | 1 = Interrupt                     |                                                          |                |                |                  |                |              |  |  |  |  |

|                | 0 = Interrupt                     | is not pending                                           |                |                |                  |                |              |  |  |  |  |

| Note:          | Interrupt flag bits               | are set when ar                                          | interrunt      |                |                  |                |              |  |  |  |  |

|                | condition occurs,                 |                                                          |                |                |                  |                |              |  |  |  |  |

|                | its corresponding                 |                                                          |                |                |                  |                |              |  |  |  |  |

|                | Enable bit, GIE,<br>User software | of the INTCON<br>should ens                              | •              |                |                  |                |              |  |  |  |  |

|                | appropriate interru               |                                                          |                |                |                  |                |              |  |  |  |  |

|                | to enabling an inte               |                                                          |                |                |                  |                |              |  |  |  |  |

#### REGISTER 7-6: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

#### 11.3 Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash Program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum block size that can be erased by user software.

Flash program memory may only be written or erased if the destination address is in a segment of memory that is not write-protected, as defined in bits WRT<1:0> of Configuration Words.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the EEDATH:EEDATL register pair.

| Note: | If the user wants to modify only a portion |

|-------|--------------------------------------------|

|       | of a previously programmed row, then the   |

|       | contents of the entire row must be read    |

|       | and saved in RAM prior to the erase.       |

The number of data write latches may not be equivalent to the number of row locations. During programming, user software may need to fill the set of write latches and initiate a programming operation multiple times in order to fully reprogram an erased row. For example, a device with a row size of 32 words and eight write latches will need to load the write latches with data and initiate a programming operation four times.

The size of a program memory row and the number of program memory write latches may vary by device. See Table 11-1 for details.

## 11.3.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the Least and Most Significant address bits to the EEADRH:EEADRL register pair.

- 2. Clear the CFGS bit of the EECON1 register.

- 3. Set the EEPGD control bit of the EECON1 register.

- 4. Then, set control bit RD of the EECON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF EECON1, RD" instruction to be ignored. The data is available in the very next cycle, in the EEDATH:EEDATL register pair; therefore, it can be read as two bytes in the following instructions.

EEDATH:EEDATL register pair will hold this value until another read or until it is written to by the user.

- Note 1: The two instructions following a program memory read are required to be NOPS. This prevents the user from executing a two-cycle instruction on the next instruction after the RD bit is set.

- 2: Flash program memory can be read regardless of the setting of the CP bit.

#### TABLE 11-1: FLASH MEMORY ORGANIZATION BY DEVICE

| Device                         | Erase Block (Row) Size/Boundary | Number of Write Latches/Boundary |

|--------------------------------|---------------------------------|----------------------------------|

| PIC16(L)F1938<br>PIC16(L)F1939 | 32 words, EEADRL<4:0> = 00000   | 32 words, EEADRL<4:0> = 00000    |

#### 12.9 PORTD Registers (PIC16(L)F1939 only)

PORTD is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISD (Register 12-14). Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTD register (Register 12-14) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATD).

| Note: | PORTD is available on PIC16(L)F1939 |

|-------|-------------------------------------|

|       | only.                               |

The TRISD register (Register 12-15) controls the PORTD pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISD register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 12.9.1 ANSELD REGISTER

The ANSELD register (Register 12-17) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELD bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELD bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELD bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

## 12.9.2 PORTD FUNCTIONS AND OUTPUT PRIORITIES

Each PORTD pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-10.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the list below. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in priority list.

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RD0      | COM3 (LCD)<br>RD0                |

| RD1      | CCP4 (CCP)<br>RD1                |

| RD2      | P2B (CCP)<br>RD2                 |

| RD3      | SEG16 (LCD)<br>P2C (CCP)<br>RD3  |

| RD4      | SEG17 (LCD)<br>P2D (CCP)<br>RD4  |

| RD5      | SEG18 (LCD)<br>P1B (CCP)<br>RD5  |

| RD6      | SEG19 (LCD)<br>P1C (CCP)<br>RD6  |

| RD7      | SEG20 (LCD)<br>P1D (CCP)<br>RD7  |

#### TABLE 12-10: PORTD OUTPUT PRIORITY

Note 1: Priority listed from highest to lowest.

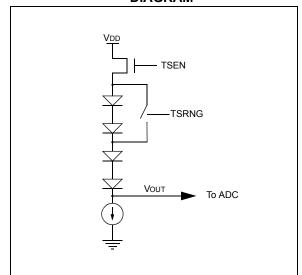

#### 16.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between -40°C and +85°C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, *"Use and Calibration of the Internal Temperature Indicator"* (DS01333) for more details regarding the calibration process.

#### 16.1 Circuit Operation

Figure 16-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 16-1 describes the output characteristics of the temperature indicator.

#### EQUATION 16-1: VOUT RANGES

High Range: VOUT = VDD - 4VT

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See **Section 14.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for low voltage operation.

### FIGURE 16-1: TEMPERATURE CIRCUIT DIAGRAM

### 16.2 Minimum Operating VDD

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 16-1 shows the recommended minimum VDD vs.range setting.

#### TABLE 16-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

#### 16.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to Section 15.0 "Analog-to-Digital Converter (ADC) Module" for detailed information.

### 16.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between sequential conversions of the temperature indicator output.

| Name    | Bit 7                                                                      | Bit 6           | Bit 5          | Bit 4          | Bit 3          | Bit 2    | Bit 1  | Bit 0  | Register<br>on Page |

|---------|----------------------------------------------------------------------------|-----------------|----------------|----------------|----------------|----------|--------|--------|---------------------|

| ANSELB  | —                                                                          | _               | ANSB5          | ANSB4          | ANSB3          | ANSB2    | ANSB1  | ANSB0  | 131                 |

| CCP1CON | P1M·                                                                       | <1:0>           | DC1B           | <1:0>          |                | CCP1N    | 1<3:0> |        | 228                 |

| CCP2CON | P2M·                                                                       | <1:0>           | DC2B           | <1:0>          |                | CCP2N    | 1<3:0> |        | 228                 |

| INTCON  | GIE                                                                        | PEIE            | TMR0IE         | INTE           | IOCIE          | TMR0IF   | INTF   | IOCIF  | 90                  |

| PIE1    | TMR1GIE                                                                    | ADIE            | RCIE           | TXIE           | SSPIE          | CCP1IE   | TMR2IE | TMR1IE | 91                  |

| PIR1    | TMR1GIF                                                                    | ADIF            | RCIF           | TXIF           | SSPIF          | CCP1IF   | TMR2IF | TMR1IF | 94                  |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |                 |                |                |                |          | 193*   |        |                     |

| TMR1L   | Holding Regi                                                               | ster for the Le | east Significa | nt Byte of the | 16-bit TMR1    | Register |        |        | 193*                |

| TRISB   | TRISB7                                                                     | TRISB6          | TRISB5         | TRISB4         | TRISB3         | TRISB2   | TRISB1 | TRISB0 | 130                 |

| TRISC   | TRISC7                                                                     | TRISC6          | TRISC5         | TRISC4         | TRISC3         | TRISC2   | TRISC1 | TRISC0 | 134                 |

| T1CON   | TMR1C                                                                      | S<1:0>          | T1CKP          | S<1:0>         | T1OSCEN        | T1SYNC   | —      | TMR10N | 197                 |

| T1GCON  | TMR1GE                                                                     | T1GPOL          | T1GTM          | T1GSPM         | T1GGO/<br>DONE | T1GVAL   | T1GS   | S<1:0> | 198                 |

| TABLE 21-5: | SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1 |

|-------------|---------------------------------------------|

|-------------|---------------------------------------------|

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the Timer1 module.

\* Page provides register information.

#### 23.1.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see Section 12.1 "Alternate Pin Function" for more information.

| Name                 | Bit 7                                        | Bit 6          | Bit 5        | Bit 4          | Bit 3            | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|----------------------|----------------------------------------------|----------------|--------------|----------------|------------------|-----------------------|-----------------------|-----------------------|---------------------|

| APFCON               | _                                            | CCP3SEL        | T1GSEL       | P2BSEL         | SRNQSEL          | C2OUTSEL              | SSSEL                 | CCP2SEL               | 123                 |

| CCPxCON              | PxM<1:0> <sup>(1)</sup> DCxB<1:0> CCPxM<3:0> |                |              |                |                  |                       |                       |                       | 228                 |

| CCPRxL               | Capture/Co                                   | mpare/PWM      | Register x l | Low Byte (LS   | SB)              |                       |                       |                       | 206                 |

| CCPRxH               | Capture/Co                                   | mpare/PWM      | Register x I | High Byte (M   | ISB)             |                       |                       |                       | 206                 |

| INTCON               | GIE                                          | PEIE           | TMR0IE       | INTE           | IOCIE            | TMR0IF                | INTF                  | IOCIF                 | 90                  |

| PIE1                 | TMR1GIE                                      | ADIE           | RCIE         | TXIE           | SSPIE            | CCP1IE                | TMR2IE                | TMR1IE                | 91                  |

| PIE2                 | OSFIE                                        | C2IE           | C1IE         | EEIE           | BCLIE            | LCDIE                 | _                     | CCP2IE                | 92                  |

| PIE3                 | —                                            | CCP5IE         | CCP4IE       | CCP3IE         | TMR6IE           |                       | TMR4IE                | —                     | 93                  |

| PIR1                 | TMR1GIF                                      | ADIF           | RCIF         | TXIF           | SSPIF            | CCP1IF                | TMR2IF                | TMR1IF                | 94                  |

| PIR2                 | OSFIF                                        | C2IF           | C1IF         | EEIF           | BCLIF            | LCDIF                 | _                     | CCP2IF                | 95                  |

| PIR3                 | —                                            | CCP5IF         | CCP4IF       | CCP3IF         | TMR6IF           | _                     | TMR4IF                | —                     | 95                  |

| T1CON                | TMR1C                                        | S<1:0>         | T1CKP        | S<1:0>         | T1OSCEN          | T1SYNC                | _                     | TMR10N                | 197                 |

| T1GCON               | TMR1GE                                       | T1GPOL         | T1GTM        | T1GSPM         | T1GGO/DONE       | T1GVAL                | T1GS                  | S<1:0>                | 198                 |

| TMR1L                | Holding Reg                                  | gister for the | Least Signif | ficant Byte of | f the 16-bit TMR | 1 Register            |                       |                       | 193                 |

| TMR1H                | Holding Reg                                  | gister for the | Most Signifi | cant Byte of   | the 16-bit TMR1  | Register              |                       |                       | 193                 |

| TRISA                | TRISA7                                       | TRISA6         | TRISA5       | TRISA4         | TRISA3           | TRISA2                | TRISA1                | TRISA0                | 125                 |

| TRISB                | TRISB7                                       | TRISB6         | TRISB5       | TRISB4         | TRISB3           | TRISB2                | TRISB1                | TRISB0                | 130                 |

| TRISC                | TRISC7                                       | TRISC6         | TRISC5       | TRISC4         | TRISC3           | TRISC2                | TRISC1                | TRISC0                | 134                 |

| TRISD <sup>(2)</sup> | TRISD7                                       | TRISD6         | TRISD5       | TRISD4         | TRISD3           | TRISD2                | TRISD1                | TRISD0                | 137                 |

| TRISE                |                                              |                |              | —              | (3)              | TRISE2 <sup>(2)</sup> | TRISE1 <sup>(2)</sup> | TRISE0 <sup>(2)</sup> | 140                 |

TABLE 23-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPTURE

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by Capture mode.

**Note 1:** Applies to ECCP modules only.

2: These registers/bits are not implemented on PIC16(L)F1938 devices, read as '0'.

3: Unimplemented, read as '1'.

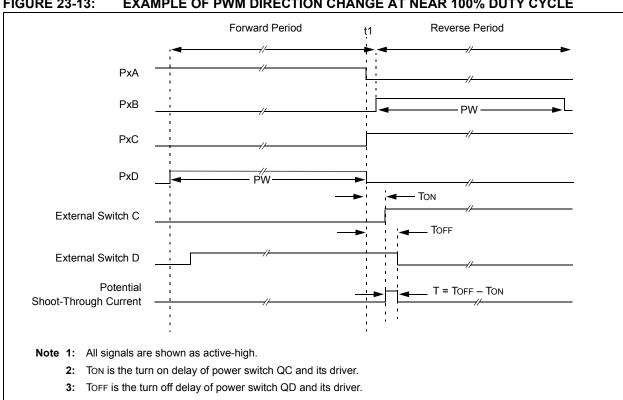

#### FIGURE 23-13: **EXAMPLE OF PWM DIRECTION CHANGE AT NEAR 100% DUTY CYCLE**

NOTES:

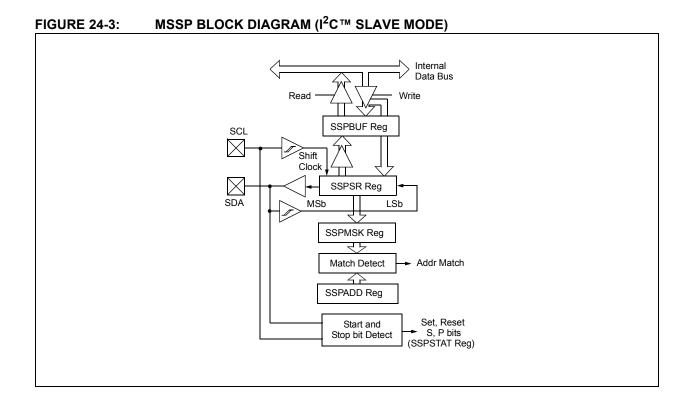

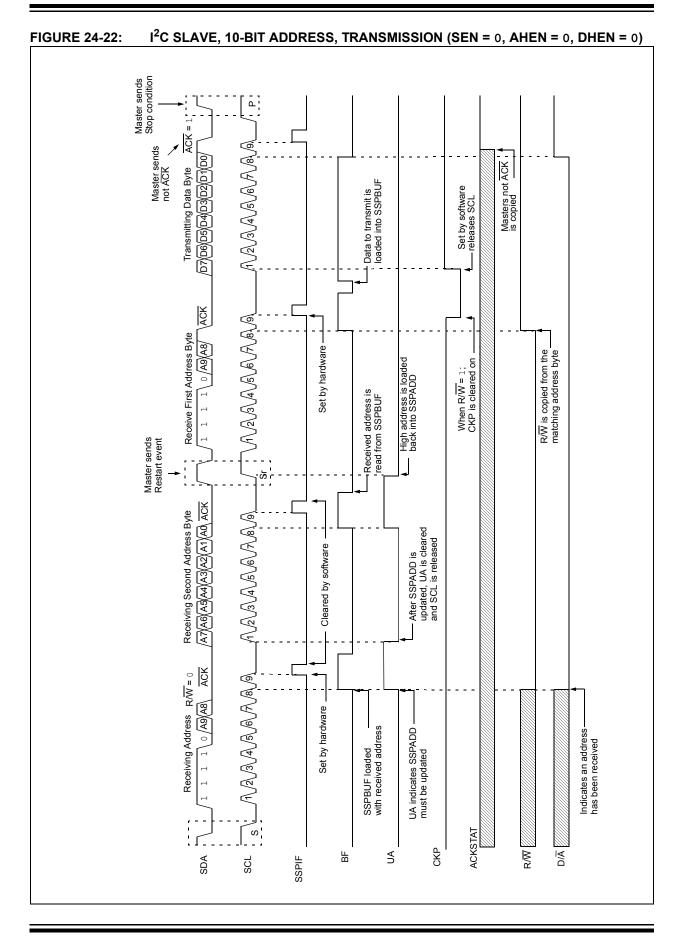

#### 24.5.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of a matching received address byte is clear, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and acknowledged.

When the overflow condition exists for a received address, then not Acknowledge is given. An overflow condition is defined as either bit BF of the SSPSTAT register is set, or bit SSPOV of the SSPCON1 register is set. The BOEN bit of the SSPCON3 register modifies this operation. For more information see Register 24-4.

An MSSP interrupt is generated for each transferred data byte. Flag bit, SSPIF, must be cleared by software.

When the SEN bit of the SSPCON2 register is set, SCL will be held low (clock stretch) following each received byte. The clock must be released by setting the CKP bit of the SSPCON1 register, except sometimes in 10-bit mode. See Section 24.2.3 "SPI Master Mode" for more detail.

#### 24.5.2.1 7-bit Addressing Reception

This section describes a standard sequence of events for the MSSP module configured as an  $I^2C$  Slave in 7-bit Addressing mode. All decisions made by hardware or software and their effect on reception. Figure 24-14 and Figure 24-15 is used as a visual reference for this description.

This is a step by step process of what typically must be done to accomplish  $I^2C$  communication.

- 1. Start bit detected.

- 2. S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- 3. Matching address with  $R/\overline{W}$  bit clear is received.

- 4. The slave pulls SDA low sending an ACK to the master, and sets SSPIF bit.

- 5. Software clears the SSPIF bit.

- 6. Software reads received address from SSPBUF clearing the BF flag.

- 7. If SEN = 1; Slave software sets CKP bit to release the SCL line.

- 8. The master clocks out a data byte.

- 9. Slave drives SDA low sending an ACK to the master, and sets SSPIF bit.

- 10. Software clears SSPIF.

- 11. Software reads the received byte from SSPBUF clearing BF.

- 12. Steps 8-12 are repeated for all received bytes from the Master.

- 13. Master sends Stop condition, setting P bit of SSPSTAT, and the bus goes idle.

## 24.5.2.2 7-bit Reception with AHEN and DHEN

Slave device reception with AHEN and DHEN set operate the same as without these options with extra interrupts and clock stretching added after the eighth falling edge of SCL. These additional interrupts allow the slave software to decide whether it wants to ACK the receive address or data byte, rather than the hardware. This functionality adds support for PMBus<sup>™</sup> that was not present on previous versions of this module.

This list describes the steps that need to be taken by slave software to use these options for  $I^2C$  communication. Figure 24-16 displays a module using both address and data holding. Figure 24-17 includes the operation with the SEN bit of the SSPCON2 register set.

- 1. S bit of SSPSTAT is set; SSPIF is set if interrupt on Start detect is enabled.

- Matching address with R/W bit clear is clocked in. SSPIF is set and CKP cleared after the eighth falling edge of SCL.

- 3. Slave clears the SSPIF.

- Slave can look at the ACKTIM bit of the SSPCON3 register to <u>determine</u> if the SSPIF was after or before the ACK.

- 5. Slave reads the address value from SSPBUF, clearing the BF flag.

- 6. Slave sets ACK value clocked out to the master by setting ACKDT.

- 7. Slave releases the clock by setting CKP.

- 8. SSPIF is set after an ACK, not after a NACK.

- 9. If SEN = 1 the slave hardware will stretch the clock after the ACK.

- 10. Slave clears SSPIF.

Note: SSPIF is still set after the ninth falling edge of SCL even if there is no clock stretching and BF has been cleared. Only if NACK is sent to Master is SSPIF not set

- 11. SSPIF set and CKP cleared after eighth falling edge of SCL for a received data byte.

- 12. Slave looks at ACKTIM bit of SSPCON3 to determine the source of the interrupt.

- 13. Slave reads the received data from SSPBUF clearing BF.

- 14. Steps 7-14 are the same for each received data byte.

- 15. Communication is ended by either the slave sending an ACK = 1, or the master sending a Stop condition. If a Stop is sent and Interrupt on Stop Detect is disabled, the slave will only know by polling the P bit of the SSTSTAT register.

#### R/W-0/0 R-0/0 R/W-0/0 R/S/HS-0/0 R/S/HS-0/0 R/S/HS-0/0 R/S/HS-0/0 R/W/HS-0/0 GCEN ACKSTAT ACKDT ACKEN RCEN PEN RSEN SEN bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets '1' = Bit is set '0' = Bit is cleared HC = Cleared by hardware S = User set **GCEN:** General Call Enable bit (in I<sup>2</sup>C Slave mode only) bit 7 1 = Enable interrupt when a general call address (0x00 or 00h) is received in the SSPSR 0 = General call address disabled ACKSTAT: Acknowledge Status bit (in I<sup>2</sup>C mode only) bit 6 1 = Acknowledge was not received 0 = Acknowledge was received bit 5 **ACKDT:** Acknowledge Data bit (in I<sup>2</sup>C mode only) In Receive mode: Value transmitted when the user initiates an Acknowledge sequence at the end of a receive 1 = Not Acknowledge 0 = Acknowledge ACKEN: Acknowledge Sequence Enable bit (in I<sup>2</sup>C Master mode only) bit 4 In Master Receive mode: 1 = Initiate Acknowledge sequence on SDA and SCL pins, and transmit ACKDT data bit. Automatically cleared by hardware. 0 = Acknowledge sequence idle **RCEN:** Receive Enable bit (in I<sup>2</sup>C Master mode only) bit 3 1 = Enables Receive mode for $I^2C$ 0 = Receive idle bit 2 **PEN:** Stop Condition Enable bit (in I<sup>2</sup>C Master mode only) SCKMSSP Release Control: 1 = Initiate Stop condition on SDA and SCL pins. Automatically cleared by hardware. 0 = Stop condition Idle **RSEN:** Repeated Start Condition Enabled bit (in I<sup>2</sup>C Master mode only) bit 1 1 = Initiate Repeated Start condition on SDA and SCL pins. Automatically cleared by hardware. 0 = Repeated Start condition Idle bit 0 SEN: Start Condition Enable/Stretch Enable bit In Master mode: 1 = Initiate Start condition on SDA and SCL pins. Automatically cleared by hardware. 0 = Start condition Idle In Slave mode: 1 = Clock stretching is enabled for both slave transmit and slave receive (stretch enabled) 0 = Clock stretching is disabled

#### REGISTER 24-3: SSPCON2: SSP CONTROL REGISTER 2

**Note 1:** For bits ACKEN, RCEN, PEN, RSEN, SEN: If the I<sup>2</sup>C module is not in the Idle mode, this bit may not be set (no spooling) and the SSPBUF may not be written (or writes to the SSPBUF are disabled).

### 26.9 Register Definitions: CPS Control

#### REGISTER 26-1: CPSCON0: CAPACITIVE SENSING CONTROL REGISTER 0

| R/W-0/0              | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                            | U-0                                                                                                                | U-0                                               | R/W-0/0                                               | R/W-0/0 | R-0/0  | R/W-0/0 |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------|---------|--------|---------|--|

| CPSON                | CPSRM                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                                                                  | _                                                 | CPSRNG<1:0>                                           |         | CPSOUT | TOXCS   |  |

| bit 7                | ·                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                    |                                                   | •                                                     |         |        | bit C   |  |

|                      |                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                    |                                                   |                                                       |         |        |         |  |

| Legend:              |                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                    |                                                   |                                                       |         |        |         |  |

| R = Readable bit     |                                                                                                                                                                                                                                                                                                                                                                                                    | W = Writable bit                                                                                                   |                                                   | U = Unimplemented bit, read as '0'                    |         |        |         |  |

| u = Bit is unchanged |                                                                                                                                                                                                                                                                                                                                                                                                    | x = Bit is unknown                                                                                                 |                                                   | -n/n = Value at POR and BOR/Value at all other Resets |         |        |         |  |

| '1' = Bit is set     |                                                                                                                                                                                                                                                                                                                                                                                                    | '0' = Bit is clea                                                                                                  | ared                                              |                                                       |         |        |         |  |

| bit 7                | 1 = CPS mo                                                                                                                                                                                                                                                                                                                                                                                         | S Module Enab<br>dule is enabled<br>dule is disablec                                                               |                                                   |                                                       |         |        |         |  |

| bit 6                | 1 = Capacitiv                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                    | lule is in Vari                                   | Mode bit<br>able Voltage Re<br>ed Variable Volta      |         |        |         |  |

| bit 5-4              | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                    |                                                   |                                                       |         |        |         |  |

| bit 3-2              | <u>If CPSRM = 0</u><br>00 = Oscillate<br>01 = Oscillate<br>10 = Oscillate                                                                                                                                                                                                                                                                                                                          | 0>: Capacitive<br><u>o</u> (Fixed Voltage<br>or is off<br>or is in Low-Cut<br>or is in Medium<br>or is in High-Cut | <u>e Reference</u><br>rrent Range<br>-Current Ran | <u>mode)</u> :                                        |         |        |         |  |

|                      | 00 = Oscillate<br>01 = Oscillate<br>10 = Oscillate                                                                                                                                                                                                                                                                                                                                                 | 1 (Variable Volta<br>or is on. Noise l<br>or is in Low-Cul<br>or is in Medium<br>or is in High-Cu                  | Detection mo<br>rent Range.<br>-Current Ran       | ige.                                                  |         |        |         |  |

| bit 1                | <b>CPSOUT:</b> Capacitive Sensing Oscillator Status bit<br>1 = Oscillator is sourcing current (Current flowing out of the pin)<br>0 = Oscillator is sinking current (Current flowing into the pin)                                                                                                                                                                                                 |                                                                                                                    |                                                   |                                                       |         |        |         |  |

| bit 0                | <b>TOXCS:</b> Timer0 External Clock Source Select bit<br><u>If TMR0CS = 1:</u><br>The T0XCS bit controls which clock external to the core/Timer0 module supplies Timer0:<br>1 = Timer0 clock source is the capacitive sensing oscillator, CPSCLK<br>0 = Timer0 clock source is the T0CKI pin<br><u>If TMR0CS = 0:</u><br>Timer0 clock source is controlled by the core/Timer0 module and is Fosc/4 |                                                                                                                    |                                                   |                                                       |         |        |         |  |

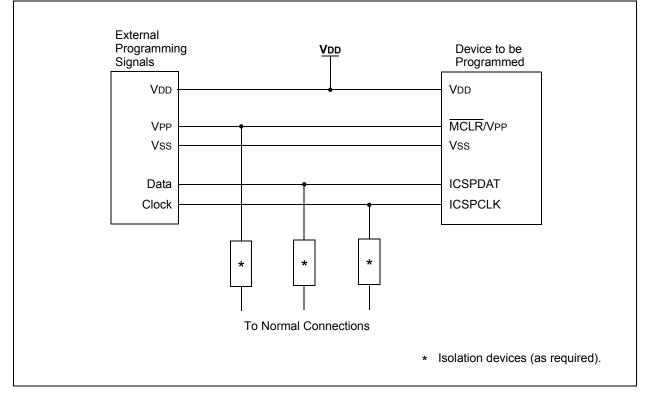

For additional interface recommendations, refer to your specific device programmer manual prior to PCB design.

It is recommended that isolation devices be used to separate the programming pins from other circuitry. The type of isolation is highly dependent on the specific application and may include devices such as resistors, diodes, or even jumpers. See Figure 28-4 for more information.

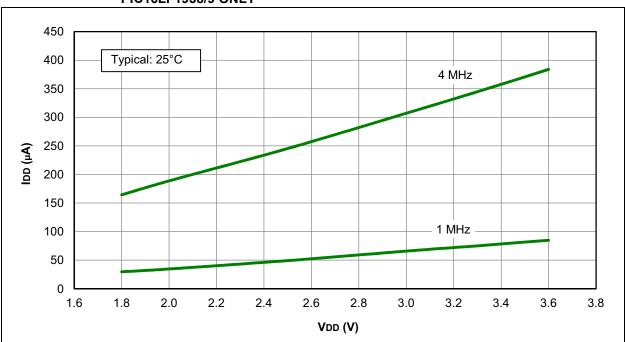

FIGURE 31-11: IDD TYPICAL, EXTERNAL CLOCK (ECM), MEDIUM-POWER MODE, PIC16LF1938/9 ONLY

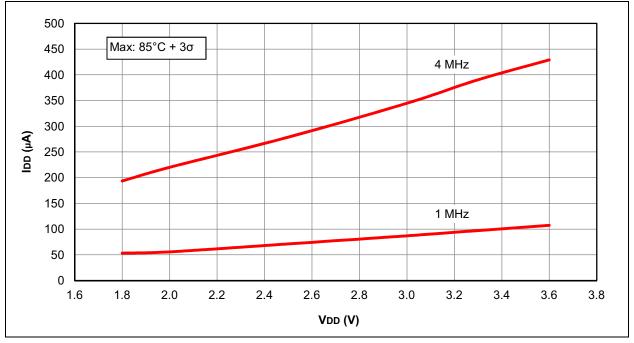

FIGURE 31-12: IDD MAXIMUM, EXTERNAL CLOCK (ECM), MEDIUM-POWER MODE, PIC16LF1938/9 ONLY

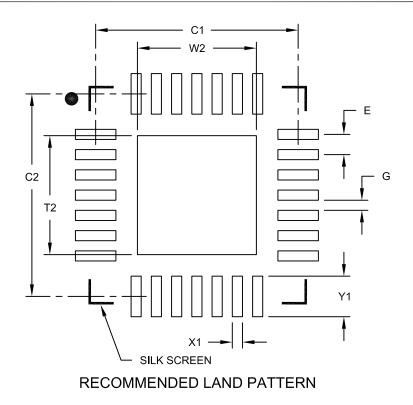

28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 4x4 mm Body [UQFN] With 0.40 mm Contact Length

|                            | MILLIMETERS |          |      |      |

|----------------------------|-------------|----------|------|------|

| Dimension Limits           |             | MIN      | NOM  | MAX  |

| Contact Pitch              | E           | 0.40 BSC |      |      |

| Optional Center Pad Width  | W2          |          |      | 2.35 |

| Optional Center Pad Length | T2          |          |      | 2.35 |

| Contact Pad Spacing        | C1          |          | 4.00 |      |

| Contact Pad Spacing        | C2          |          | 4.00 |      |

| Contact Pad Width (X28)    | X1          |          |      | 0.20 |

| Contact Pad Length (X28)   | Y1          |          |      | 0.80 |

| Distance Between Pads      | G           | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2152A

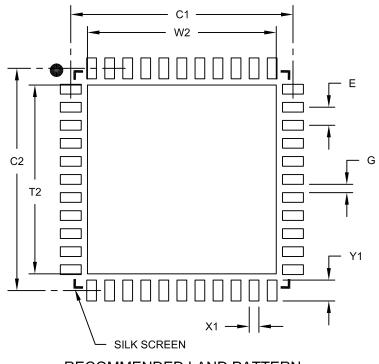

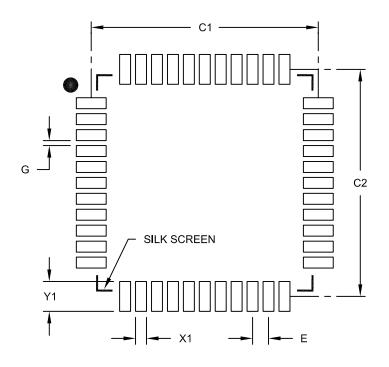

44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |          |      |      |

|----------------------------|-------------|----------|------|------|

| Dimension Limits           |             | MIN      | NOM  | MAX  |

| Contact Pitch              | E           | 0.65 BSC |      |      |

| Optional Center Pad Width  | W2          |          |      | 6.60 |

| Optional Center Pad Length | T2          |          |      | 6.60 |

| Contact Pad Spacing        | C1          |          | 8.00 |      |

| Contact Pad Spacing        | C2          |          | 8.00 |      |

| Contact Pad Width (X44)    | X1          |          |      | 0.35 |

| Contact Pad Length (X44)   | Y1          |          |      | 0.85 |

| Distance Between Pads      | G           | 0.25     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |      |          |      |  |

|--------------------------|-------------|------|----------|------|--|

| Dimension Limits         |             | MIN  | NOM      | MAX  |  |

| Contact Pitch            | E           |      | 0.80 BSC |      |  |

| Contact Pad Spacing      | C1          |      | 11.40    |      |  |

| Contact Pad Spacing      | C2          |      | 11.40    |      |  |

| Contact Pad Width (X44)  | X1          |      |          | 0.55 |  |

| Contact Pad Length (X44) | Y1          |      |          | 1.50 |  |

| Distance Between Pads    | G           | 0.25 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B