Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1938-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.1.1.2 Indirect Read with FSR

The program memory can be accessed as data by setting bit 7 of the FSRxH register and reading the matching INDFx register. The MOVIW instruction will place the lower eight bits of the addressed word in the W register. Writes to the program memory cannot be performed via the INDF registers. Instructions that access the program memory via the FSR require one extra instruction cycle to complete. Example 3-2 demonstrates accessing the program memory via an FSR.

The HIGH directive will set bit<7> if a label points to a location in program memory.

#### EXAMPLE 3-2: ACCESSING PROGRAM MEMORY VIA FSR

| constants   |            |         |      |

|-------------|------------|---------|------|

| RETLW       | DATAO      | ;Index0 | data |

| RETLW       | DATA1      | ;Index1 | data |

| RETLW       | DATA2      |         |      |

| RETLW       | data3      |         |      |

| my_function | on         |         |      |

| ; LOI       | IS OF CODE |         |      |

| MOVLW       | LOW const  | tants   |      |

| MOVWF       | FSR1L      |         |      |

| MOVLW       | HIGH con:  | stants  |      |

| MOVWF       | FSR1H      |         |      |

| MOVIW       | 0[FSR1]    |         |      |

| ; THE PROG  | RAM MEMORY | IS IN W |      |

## 3.2 Data Memory Organization

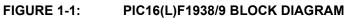

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-2):

- 12 core registers

- · 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- · 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See Section 3.6 "Indirect Addressing" for more information.

Data Memory uses a 12-bit address. The upper seven bits of the address define the Bank address and the lower five bits select the registers/RAM in that bank.

#### 3.2.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation of the PIC16(L)F1938/9. These registers are listed below:

- INDF0

- INDF1

- PCL

- STATUS

- FSR0 Low

- FSR0 High

- FSR1 Low

- FSR1 High

- BSR

- WREG

- PCLATH

- INTCON

Note: The core registers are the first 12 addresses of every data memory bank.

### 4.6 Device ID and Revision ID

The memory location 8006h is where the Device ID and Revision ID are stored. The upper nine bits hold the Device ID. The lower five bits hold the Revision ID. See Section 11.5 "User ID, Device ID and Configuration Word Access" for more information on accessing these memory locations.

Development tools, such as device programmers and debuggers, may be used to read the Device ID and Revision ID.

## 4.7 Register Definitions: Device ID

### **REGISTER 4-3:** DEVICEID: DEVICE ID REGISTER<sup>(1)</sup>

'1' = Bit is set

|       |      | R      | R    | R    | R    | R    | R     |

|-------|------|--------|------|------|------|------|-------|

|       |      |        | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

|       |      | bit 13 |      |      |      |      | bit 8 |

|       |      |        |      |      |      |      |       |

| R     | R    | R      | R    | R    | R    | R    | R     |

| DEV2  | DEV1 | DEV0   | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |        |      |      |      |      | bit 0 |

|       |      |        |      |      |      |      |       |

#### Legend:

R = Readable bit

'0' = Bit is cleared

-n = Value when blank or after Bulk Erase

#### bit 13-5 **DEV<8:0>:** Device ID bits

| DEVICE      | DEVICEID<13:0> |          |  |  |  |  |  |

|-------------|----------------|----------|--|--|--|--|--|

| DEVICE      | DEV<8:0>       | REV<4:0> |  |  |  |  |  |

| PIC16F1938  | 10 0011 101    | X XXXX   |  |  |  |  |  |

| PIC16F1939  | 10 0011 110    | X XXXX   |  |  |  |  |  |

| PIC16LF1938 | 10 0100 101    | X XXXX   |  |  |  |  |  |

| PIC16LF1939 | 10 0100 110    | X XXXX   |  |  |  |  |  |

#### bit 4-0 **REV<4:0>:** Revision ID bits

These bits are used to identify the revision (see the table under DEV<8:0> above).

Note 1: This location cannot be written.

#### 5.2.2.6 32 MHz Internal Oscillator Frequency Selection

The Internal Oscillator Block can be used with the 4X PLL associated with the External Oscillator Block to produce a 32 MHz internal system clock source. The following settings are required to use the 32 MHz internal clock source:

- The FOSC bits in Configuration Words must be set to use the INTOSC source as the device system clock (FOSC<2:0> = 100).

- The SCS bits in the OSCCON register must be cleared to use the clock determined by FOSC<2:0> in Configuration Words (SCS<1:0> = 00).

- The IRCF bits in the OSCCON register must be set to the 8 MHz HFINTOSC set to use (IRCF<3:0> = 1110).

- The SPLLEN bit in the OSCCON register must be set to enable the 4xPLL, or the PLLEN bit of the Configuration Words must be programmed to a '1'.

- Note: When using the PLLEN bit of the Configuration Words, the 4xPLL cannot be disabled by software and the 8 MHz HFINTOSC option will no longer be available.

The 4xPLL is not available for use with the internal oscillator when the SCS bits of the OSCCON register are set to '1x'. The SCS bits must be set to '00' to use the 4xPLL with the internal oscillator.

## 5.2.2.7 Internal Oscillator Clock Switch Timing

When switching between the HFINTOSC, MFINTOSC and the LFINTOSC, the new oscillator may already be shut down to save power (see Figure 5-7). If this is the case, there is a delay after the IRCF<3:0> bits of the OSCCON register are modified before the frequency selection takes place. The OSCSTAT register will reflect the current active status of the HFINTOSC, MFINTOSC and LFINTOSC oscillators. The sequence of a frequency selection is as follows:

- 1. IRCF<3:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. The current clock is held low and the clock switch circuitry waits for a rising edge in the new clock.

- 5. The new clock is now active.

- 6. The OSCSTAT register is updated as required.

- 7. Clock switch is complete.

See Figure 5-7 for more details.

If the internal oscillator speed is switched between two clocks of the same source, there is no start-up delay before the new frequency is selected. Clock switching time delays are shown in Table 5-1.

Start-up delay specifications are located in the oscillator tables in the applicable Electrical Specifications Chapter.

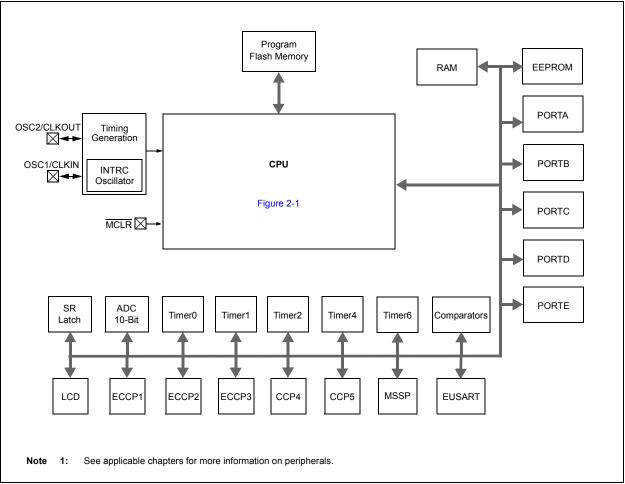

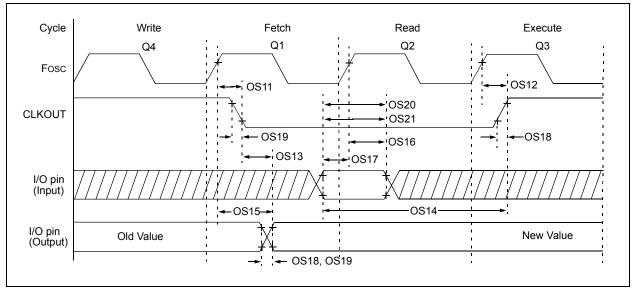

2: Asynchronous interrupt latency = 3-5 Tcy. Synchronous latency = 3-4 Tcy, where Tcy = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

3: CLKOUT not available in all Oscillator modes.

4: For minimum width of INT pulse, refer to AC specifications in the applicable Electrical Specifications Chapter".

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

#### EXAMPLE 11-5: WRITING TO FLASH PROGRAM MEMORY

| <pre>; This write routine assumes the following:<br/>; 1. The 1b tytes of data are loaded, starting at the address in DATA_ADDR<br/>; 2. Rach word of data to be writen is made up of two adjacent bytes in DATA_ADDR<br/>; 3. A valid starting address (the least significant bits - 000) is loaded in ADDRHADDRL<br/>; 4. ADDRH and ADDRL are located in shared data meany 0x7 - 0x7P (common AAR)<br/>;<br/>5. DEF INTCON_GIE ; Disable ints so required sequences will execute properly<br/>DATA_ADDR, is load initial address<br/>MOVWF EDEADRH ;<br/>MOVWF EDEADRH, ;<br/>MOVWF EDEADRH ;<br/>MOVWF</pre>                                                                                                                                          |          | LE 11-5: |              |                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|--------------|------------------------------------------------------------|

| <pre>2 Each word of data to be written is made up of two adjacent bytes in DATA_ADDR,<br/>stored in little endlam format<br/>3 .4 valid starting address (the least significant bits - 000) is loaded in ADDRM.ADDRL<br/>4. ADDRM and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM)<br/>BARKNEL EXAMPH ; biable ints so required sequences will execute properly<br/>EANEXED EXAMPH ; biable ints so required sequences will execute properly<br/>EANEXED EXAMPH ; biable ints as required sequences will execute properly<br/>EANEXED F ;<br/>MOVWF EEADEN ;<br/>MOVWF EADEN ;<br/>MOVWF ADEN ;<br/>MOVWF ADEN ;<br/>MOVWF ADEN ;<br/>MOVWF ADEN ;<br/>MOVWF ADEN ;<br/>MOVWF ;<br/>MOVWF</pre> |          |          |              | -                                                          |

| <pre> stored in little endian format stored in district endian format stored in din district endian stored</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | -        |              |                                                            |

| <pre>3 3. A valid starting address (the least significant bis = 000) is loaded in ADDBH:ADDBL<br/>4. ADDBH and ADDBL are located in shared data memory 0x70 - 0x7F (common RAM)<br/>BANKSEL FEADBH<br/>BANKSEL FEADBL<br/>BANKSEL FEADBL</pre>                                                                                                                                                                                                             |          |          |              |                                                            |

| <pre>; 4. ADDRH and ADDRL are located in shared data memory 0x70 - 0x7F (common RAM) ;  BCF INTCON.GEE ; Disable ints so required sequences will execute properly ADDRH,W ; Dank 3 MOVE ADDRH,W ; Load initial address MOVE ADDRH,W ; Load initial data address NOVE EXECUT, ; NOVIN LOW DATA_ADDR, ; Load initial data address NOVWF FSROM ; NOVIN LOW DATA_ADDR, ; Load initial data address NOVWF FSROM ; NOVIN LOW DATA_ADDR, ; Load initial data address NOVWF FSROM ; NOVIN LOW DATA_ADDR, ; Load initial data address NOVWF FSROM ; NOVIN LOW DATA_ADDR, ; Load initial data address NOVWF FSROM ; NOVIN LOW DATA_ADDR, ; Load initial data address NOVWF FSROM ; NOVIN HIGH DATA_ADDR, ; Load initial data address NOVWF FSROM ; NOVIN HIGH DATA_ADDR, ; Load initial data address NOVWF FSROM ; NOVIW FSROM ; Load first data byte into lower NOVWF EEDATL ; NOVF EEDATL ; NOVF EEDATL ; NOVF EEDATL ; NOVF EEDATL ; NOVWF EEDATL ; NOVF EEDATL ; NOVF EEDATL ; NOVWF EEDATL ; NOVWF EEDATL ; NOVF EEDATL ; N</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |          |              |                                                            |

| <pre>     FOF INTCON,GIE ; Disable ints so required sequences will execute properly     EADEM ; Dank 3     MOVEP ADDEN,W ; Load initial address     MOVUP EADEM,W ; Load initial address     MOVUP EADEM,W ; Load initial address     MOVUP FEADEM ; Load initial data address     MOVUP FEADEM ; Load first data byte into processor     NOVE FEADEM ; Load first data byte into upper     MOVUP FEADEM ; Load second data byte into upper     MOVUP FEADEM ; Load second data byte into upper     MOVUP FEADEM ;     MOVUP EEDEM ;     MOVUP EEDEM ;     NOVE EEDEM ; Load second data byte into upper     MOVUP EEDEM ;     MOVUP EEDEM ;     MOVUP EEDEM ;     NOVUP EADEM ;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |          | -            | -                                                          |

| BANKSEL FRADRI : Bank 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |          |              |                                                            |

| MOVE EADRH ; Load initial address<br>MOVE EADRH ;<br>MOVE EEADRH ;<br>MOVE EEADRH ;<br>MOVE EEADRH ;<br>MOVE EEADRH ;<br>MOVE EEADRH ;<br>MOVE EEADRH ;<br>MOVE FEROL ;<br>MOVE FEROL ;<br>MOVE FEROL ;<br>MOVE FEROL ;<br>MOVE FEROH ;<br>BSF EECONI,EERO ; Not configuration space<br>BSF EECONI,FCS ; Not configuration space<br>NOVIN CAN7 ; Check if lower bits of address are '000'<br>NOVIN CAN7 ; Check if lower both last of 8 addresses<br>ANDLM CAO7 ; Check if we're on the last of 8 addresses<br>ANDLM CAO7 ; Nites State of required write sequence:<br>NOVIN CARA<br>MOVIN EECON2 ; Write AAh<br>SF EECONI,WR ; Still loading latches Increment address<br>START_MRITE<br>BCF EECON1,WR ; Still loading latches Increment address<br>MOVIN EECON2 ; Write Sh<br>MOVIN                                                                                                                                                                                                                                                                                                                                                                                                                                     |          | BCF      | INTCON, GIE  | ; Disable ints so required sequences will execute properly |

| MOVEF EEADRL, # ;<br>MOVEF ADDR.W ;<br>MOVEF EEADRL ;<br>MOVEF EEADRL ;<br>MOVEF FERCE<br>MOVEF FERCE<br>BOF FECONI, EEADR ; Load initial data address<br>MOVEF FERCE<br>BOF FECONI, EEAD ;<br>LOOP MOVEF FERCE<br>BOF EECONI, EEA ;<br>MOVEF EEATL ;<br>MOVEF EEATL ;<br>MOVEF EEADRL ;<br>MO                                                                                                                                                                                                                                                                                                                   |          | BANKSEL  | EEADRH       | ; Bank 3                                                   |

| MOVF EADRL, W ;<br>MOVE EADRL ;<br>MOVIN LOW DATA ADDR ; Load initial data address<br>MOVNF FSROL ;<br>MOVINF HIGH DATA_ADDR ; Load initial data address<br>MOVNF FSROH ;<br>BSF BECONI.EDECO ; Point to program memory<br>BSF BECONI.EDECO ; Point to program memory<br>BSF EECONI.EDECO ; Point to program memory<br>MOVINF FSROH ; Load first data byte into lower<br>MOVINF EEDAIL ;<br>MOVINF EEDAIL ;<br>MOVINF EEDAIL ;<br>MOVINF EEDAIT ;<br>MOVINF EEDAIT ;<br>MOVINF EECONI ; Check if lower bits of address are '000'<br>XOLW 0x07 ; Check if lower bits of address are '000'<br>XOLW 0x07 ; Check if lower bits of address are '000'<br>XOLW 0x07 ; EECONI ; Exit if last of eight words,<br>GOTO START_WRITE ;<br>MOVINF EECONI ; Start of required write sequence:<br>MOVINF EECONI ; Write 3Ah<br>BSF EECONI ; Write 3Ah<br>BSF EECONI ; Write AAh<br>SSTART_WRITE ECONI ; No more loading latches Increment address<br>START_WRITE EECONI,LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>BSF EECONI ; Write AAh<br>BCF EECONI,WR ; Set WR bit to begin write<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence:<br>; MOVINF EECONI ; Write AAh<br>; memory write<br>BCF EECONI,WR ; Start of required write sequence:<br>; Processor will stop here and wait for write complete.<br>; After write processor continues with 3rd instruction.<br>BCF EECONI,WR ; Set WR bit to begin write<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>; Processor will stop here and wait for write complete.<br>; after write processor continues with 3rd instruction<br>; after write processor continues with 3rd instruction<br>; after write sequence ; Processor continues with 3rd instruction<br>; after write sequence ; Processor continues with 3rd instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | MOVF     | ADDRH,W      | ; Load initial address                                     |

| MOVWF EEADRL, ;<br>MOVUF LOB DATA ADDR ; Load initial data address<br>MOVWF FSROL ;<br>MOVUF HIGH DATA ADDR ; Load initial data address<br>MOVWF FSROL ;<br>BSF EECON1,EFG ; Point to program memory<br>BSF EECON1,FFG ; Not configuration space<br>BSF EECON1,FREN ; Enable writes<br>BSF EECON1,FREN ; Doald Write Latches<br>MOVWF EEDATL ;<br>MOVUF EEDATE ;<br>MOVUF EECON1, LWLO ; Check if lower bits of address are '000'<br>XORLW 0x07 ; Check if we're on the last of 8 addresses<br>MOVUF EEDATE ;<br>MOVUF EECON2 ; Write S5h<br>MOVUF EECON2 ; Write S5h<br>MOVUF EECON2 ; Write S5h<br>MOVUF EECON2 ; Write AAh<br>EECON1, WR ; Set WR bit to begin write<br>MOVF EECON2 ; Write AAh<br>EECON1, WR ; Set WR bit to begin write sequence<br>NOP ; Processor will stop here and wait for write to complete.<br>; After write processor continues with 3rd instruction.<br>INCF EECON1, LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>BCF EECON2 ; Write AAh<br>EECON1, LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>BCF EECON2 ; Write AAh<br>EECON2 ; Write AAh<br>EECON1, LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>BCF EECON2 ; Write AAh<br>EECON2 ; Write AAh                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          | MOVWF    | EEADRH       | ;                                                          |

| MOVUM LOW DATA_ADDR ; Load initial data address<br>MOVWF FSROL ; Load initial data address<br>MOVWF FSROH ; Load initial data address<br>MOVWF FSROH ; Point to program memory<br>BCF EECON1.CECS ; Not configuration space<br>BSF EECON1, LWLO ; Only Load Write Latches<br>MOVWF EEDATL ;<br>MOVWF EEDATL ;<br>MOVWF EEDATL ;<br>MOVWF EEDATH ;<br>MOVWF EECON2 ; Write Sch<br>MOVWF EECON2 ; Write AAH<br>EECON2 ; Write AAH<br>EECON2 ; Write Sch<br>MOVWF EECON2 ; Write AAH<br>EECON2 ; Write AAH<br>E                                                                                                                                                                                                                                                                                                                                                                                               |          |          |              | ;                                                          |

| MOVWE FEROL _ ;<br>MOVWE FEROL _ ;<br>MOVWE FERO ADDR ; Load initial data address<br>MOVWE FEROH ;<br>BF EECONI, FERS ; Not configuration space<br>BF EECONI, WEN ; Enable writes<br>BF EECONI, WEN ; Doad Write Latches<br>LOOP<br>MOVIE FEROTL ;<br>MOVIE FEROTL ;<br>MOVIE FEROTL ;<br>MOVIE EEDATL ;<br>MOVVE EEDATL ;<br>MOVVE EEDATH ;<br>MOVVE EECON2 ; Write last of address are '000'<br>XORIM 0x07 ; Check if lower bits of address are '000'<br>XORIM 0x07 ; Check if we're on the last of 8 addresses<br>ADDVWE EECON2 ; Write Sch<br>MOVIE EECON2 ; Write Sch<br>MOVIE EECON2 ; Write AAN<br>EECON2 ; Write AAN<br>BFF EECON2 ; Write AAN<br>BFF EECON2 ; Write AAN<br>BFF EECON2 ; Write AAN<br>BFF EECON2 ; Write AAN<br>BFF EECON1, WR ; Sturt of required write sequence<br>; After write processor continues with 3rd instruction.<br>INCF EEADEL, F ; Still loading latches - Actually start Flash program<br>MOVIE EECON2 ; Write AAN<br>EECON1, LWLO ; No more loading latches - Actually start Flash program<br>memory write<br>START_WRITE<br>BCF EECON1, LWLO ; No more loading latches - Actually start Flash program<br>MOVIE EECON2 ; Write AAN<br>BCF EECON1, WE ; Start of required write sequence:<br>; After write processor continues with 3rd instruction<br>ECF EECON1, WEN ; Start of processor continues with 3rd instruction<br>BCF EECON1, WEN ; Start of required write sequence ; Processor will stop here and wait for write complete.<br>; After write processor continues with 3rd instruction<br>; After write processor                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |          |              | ;                                                          |

| MOVLW HIGH DATA_ADDR / Load initial data address<br>MOVWF FSR0H ;<br>BSF EECON1,SER6D ; Point to program memory<br>BSF EECON1,SER6D ; Point to program memory<br>BSF EECON1,SER6D ; Only Load Write Latches<br>BSF EECON1,LNLO ; Only Load Write Latches<br>LOOP<br>MOVIW FSR0++ ; Load first data byte into lower<br>MOVWF EEDATL ;<br>MOVWF EEDATL ;<br>MOVWF EEDATL ;<br>MOVF EECATE ;<br>MOVF EECATE ;<br>MOVF EECATE ;<br>MOVF EECATE ;<br>MOVF EECATE ;<br>MOVF EECON2 ; Write 35h<br>MOVWF EECON2 ; Write 55h<br>MOVWF EECON2 ; Write AAh<br>BSF EECON1,WR ; Still loading latches Increment address<br>GOTO LOOP ; Write next latches<br>START_WRITE ECCN2 ; Write Abh<br>ECC ECON1,LNLO ; No more loading latches - Actually start Flash program<br>MOVIM 0AAh ;<br>MOVIM 0AAH ;                                                                                                                                                                                                                                                                                                                                        |          |          | _            | ; Load initial data address                                |

| MOWNE FISCH, EECONI, MEDEGD ; Point to program memory<br>ECF EECONI, WEND ; Enable writes<br>ESF EECONI, WEND ; Enable writes<br>ESF EECONI, WEND ; Only Load Write Latches<br>LOOP<br>MOVIW FISCH+ ; Load first data byte into lower<br>MOVIW FISCH+ ; Load first data byte into upper<br>MOVIW FISCH+ ; Load second data byte into upper<br>MOVIW FISCH+ ; Load second data byte into upper<br>MOVIW FISCHTH ;<br>MOVF EEDATH ;<br>MOVF EEDATH ;<br>MOVF EEDATH ;<br>MOVF EEDATH ;<br>MOVF EECON2 ; Exit if last of eight words,<br>GOTO START_WRITE ;<br>MOVE EECON2 ; Write S5h<br>MOVIW 0AAh ;<br>EECON2 ; Write AAh<br>EFF EECON1,WR ; Start of required write sequence:<br>MOVIW 0AAh ;<br>MOVF EECON2 ; Write AAh<br>EFF EECON1,WR ; Start of begin write<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>; Processor will stop here and wait for write to complete.<br>; After write processor continues with 3rd instruction.<br>INCF EEADEL,F ; Still loading latches Increment address<br>GOTO LOOP ; Write S5h<br>MOVIW 0AAh ;<br>EECON1,LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>START_WRITE<br>ECF EECON1,LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>MOVIW 0AAh ;<br>MOVIW 0AAh ;<br>EECON2 ; Write S5h<br>MOVIW 0AAh ;<br>EECON2 ; Write S5h<br>MOVIW 0AAh ;<br>EECON1,LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>MOVIW 0AAh ;<br>EECON2 ; Write AAh<br>EECON2 ; Write AAH<br>EFCON2 ; Write AAH<br>EFCON3 ; Start of required write sequence:<br>NOP ; Any instructions here are ignored as processor<br>; halts to begin write<br>; Arty instructions here are ignored as processor<br>; halts to begin write sequence<br>; Processor will stop here and wait for write complete.<br>; after write processor continues with 3rd instruction<br>ECF EECON1,WREN ; Disable writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |          |              | ;<br>                                                      |

| BSF EECON1, EPECD ; Point to program memory<br>BCF EECON1, CFGS ; Not configuration space<br>BSF EECON1, LWLO ; Only Load Write Latches<br>LOOP<br>MOVIW FSR0++ ; Load first data byte into lower<br>MOVWF EEDATL ;<br>MOVWF EEDATL ;<br>MOVWF EEDATR ;<br>MOVF EEADRL,W ; Check if lower bits of address are '000'<br>XORLW 0x07 ; Check if we're on the last of 8 addresses<br>ANDIM 0x07 ; Check if we're on the last of 8 addresses<br>GOTO START WRITE ;<br>MOVIW EECON2 ; Write 3ch eight words,<br>GOTO START WRITE ;<br>MOVIW EECON2 ; Write 5ch<br>MOVWF EECON2 ; Write AAh<br>BSF EECON1,WR ; Start of required write sequence:<br>MOVWF EECON2 ; Write AAh<br>BSF EECON1,WR ; Set WR bit to begin write<br>NOP ; Processor will stop here and wait for write to complete.<br>, After write processor continues with 3rd instruction.<br>INCF EEADRL,F ; Still loading latches - Actually start Flash program<br>, memory write<br>MOVIW 55h ; Start of required write sequence:<br>MOVWF EECON2 ; Write AAh<br>START_WRITE<br>BCF EECON1,LWLO ; No more loading latches - Actually start Flash program<br>, memory write<br>MOVIM 55h ; Start of required write sequence:<br>MOVIM 55h ; Start of required write sequence:<br>MOVIM 0AAh ;<br>MOVIM 0AAh<br>; Write first for sequence is processor ;<br>halts to begin write<br>BCF EECON1,LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>MOVIM 0AAh ;<br>MOVIM 0AAA ;<br>BCF EECON2 ; Write AAh<br>BCF EECON2 ; Write AAh<br>BCF EECON1,WREN ; Set WR bit to begin write<br>; Ary instructions here are ignored as processor<br>; halts to begin write sequence<br>; Arter write processor continues with 3rd instruction<br>BCF EECON1,WREN ; Disable writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |          | -            | ; LUAU INITIAL UATA AUDRESS .                              |

| BCF       EECON1, CFGS       ; Not configuration space         BSF       EECON1, WENN       ; Enable writes         BSF       EECON1, LWLO       ; Only Load Write Latches         MOVIN       FSR0++       ; Load first data byte into lower         MOVIN       FSR0++       ; Load second data byte into upper         MOVIN       FSR0++       ; Load second data byte into upper         MOVF       EEDATL       ;         MOVF       EEDATH       ;         MOVF       Start of required writes and '000'         XCRE       Work       FECON2 ;         Write Sh       ; Satur of required write sequence:         NOP       ; And instructions here are ignored as processor         NOP       ; After write processor continues with 3rd instruction.         INCF       EEDATL,F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |          |              | ; . Deint to program memory                                |

| BSF EECON1, WEEN ; Enable writes<br>BSF EECON1, IWLO ; Only Load Write Latches<br>HOVIW FSR0++ ; Load first data byte into lower<br>MOVIW FSR0++ ; Load second data byte into upper<br>MOVWF EEDATL ;<br>MOVF EEADRL,W ; Check if lower bits of address are '000'<br>XORIW AXO7 ; Check if we're on the last of 8 addresses<br>ANDLW DXO7 ; Check if we're on the last of 8 addresses<br>ANDLW DXO7 ; EEADRL,W ; Check if lower bits of address are '000'<br>XORIW AXO7 ; Check if we're on the last of 8 addresses<br>ANDLW DXO7 ; EECON2 ; Exit if last of eight words,<br>GOTO START_WRITE ;<br>MOVUW DAAh ;<br>WOVWF EECON2 ; Write AAh<br>EECON1 WR ; Set WR bit to begin write<br>BSF EECON1,WR ; Set WR bit to begin write sequence:<br>NOP ; Processor will stop here and wait for write to complete.<br>, After write processor continues with 3rd instruction.<br>INCF EEADRL,F ; Still loading latches Increment address<br>GOTO LOOP ; Write next latches<br>START_WRITE<br>ECF EECON1,LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>MOVIW DAAh ;<br>MOVIW DAAh ;<br>MOVIW DAAh ;<br>MOVIW DAAh ;<br>MOVIW EECON2 ; Write 55h<br>MOVIW DAAh ;<br>MOVIW DAAh ;<br>MOVIW DAAh ;<br>MOVIW DAAh ;<br>MOVIW DAAh ;<br>MOVIW DAAh ;<br>MOVIW EECON2 ; Write Start of required write sequence:<br>MOVIW EECON2 ; Write Start of required write sequence:<br>MOVIW DAAh ;<br>MOVIW DAAh ;<br>BSF EECON1,WR ; Start of required write sequence:<br>NOP ; Any instructions here are ignored as processor<br>; halts to begin write<br>ECF EECON1,WR ; Start of required write sequence;<br>NOP ; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>; After write processor continues with 3rd instruction<br>ECF EECON1,WREN ; Disable writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |          |              |                                                            |

| DOP<br>BSF EECON1, LWLO ; Only Load Write Latches<br>MOVIW FSR0++ ; Load first data byte into lower<br>MOVWF EEDATL ;<br>MOVWF EEDATH ;<br>MOVF EEADRL, W ; Check if lower bits of address are '000'<br>XORLW 0x07 ; Check if we're on the last of 8 addresses<br>ANDLW 0x07 ; Check if we're on the last of 8 addresses<br>ANDLW 0x07 ; Check if last of eight words,<br>GOTO START_WRITE ;<br>MOVIM 55h ; Start of required write sequence:<br>MOVIM 0AAh ;<br>MOVWF EECON2 ; Write 55h<br>MOVIM 0AAh ;<br>MOVWF EECON2 ; Write AAh<br>BSF EECON1, WR ; Still loading latches are ignored as processor<br>; halts to begin write sequence<br>NOP ; Frocessor will stop here and wait for write to complete.<br>; After write processor continues with 3rd instruction.<br>INCF EEADRL, F ; Still loading latches - Actually start Flash program<br>; memory write<br>START_WRITE<br>ECF EECON1, LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>MOVIM 0AAh ;<br>Write 55h<br>MOVIM 55h ; Start of required write sequence:<br>MOVIM 6AAh ;<br>MOVIM 55h ; Start of required write sequence:<br>MOVIM 55h ; Start of required write sequence:<br>MOVIM 55h ; Start of required write sequence:<br>MOVIM 6AAh ;<br>MOVIM 6AAh ;<br>MOVIM 6AAh ;<br>MOVIM 55h ; Start of required write sequence:<br>NOP ; Write AAh<br>BSF EECON2 ; Write 55h<br>MOVIM 6AAh ;<br>MOVIM 6AAh ;<br>START of EECON2 ; Write Start of required write sequence:<br>NOP ; Start of required write sequence:<br>NOP ; Start of required write sequence:<br>; After write processor continues with 3rd instruction<br>ECF EECON1, WR ; Set WR bit to begin write<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>; After write processor continues with 3rd instruction<br>ECF EECON1, WREN ; Disable writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |          |              |                                                            |

| LOOP<br>MOVIW FSR0++ ; Load first data byte into lower<br>MOVWF EEDATL ;<br>MOVWF EEDATH ;<br>MOVWF EEDATH ;<br>MOVWF EEDATH ;<br>MOVF EEDATH ;<br>MOVWF EECON2 ; Write Jast of eight words,<br>GOTO START_WRITE ;<br>MOVWF EECON2 ; Write 55h<br>MOVWF EECON2 ; Write 55h<br>NOP ; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>; Processor will stop here and wait for write to complete.<br>; After write processor continues with 3rd instruction.<br>INCF EEADRL,F ; Still loading latches Increment address<br>GOTO LOOP ; Write next latches<br>START_WRITE<br>ECF EECON1 ; Start of required write sequence:<br>; No more loading latches - Actually start Flash program<br>; memory write<br>MOVIW 55h ; Start of required write sequence:<br>; Write 55h<br>MOVIW 55h ; Start of required write sequence:<br>; Write 55h<br>MOVIW 55h ; Start of required write sequence:<br>; MOVIW 55h ; Start of required write sequence:<br>; NOV WT EECON2 ; Write 55h<br>MOVIW 64Ah ;<br>; Movie 55h ; Start of required write sequence:<br>; After write processor continues with 3rd instruction<br>; And is true begin write<br>; Start of required write sequence:<br>; Ant is to begin write sequence<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>; Processor will stop here and wait for write complete.<br>; after write processor continues with 3rd instruction<br>; BECM ; Disable writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |          |              |                                                            |

| MOVIN FSR0++ ; Load first data byte into lower<br>MOVWF EEDATL ;<br>MOVWF EEDATR ;<br>MOVF EECON2 ; Check if lower bits of address are '000'<br>XORLW 0x07 ; Check if we're on the last of 8 addresses<br>ANDLW 0x07 ; Check if we're on the last of 8 addresses<br>ANDLW 0x07 ; Check if we're on the last of 8 addresses<br>GOTO START_WRITE ;<br>MOVLW 0x07 ;<br>BTFSC STATUS,2 ; Exit if last of eight words,<br>GOTO START_WRITE ;<br>MOVLW 0AAh ;<br>MOVLW 0AAh ;<br>MOVWF EECON2 ; Write 55h<br>NOP ; Start of required write sequence:<br>NOP ; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>NOP ; After write processor continues with 3rd instruction.<br>INCF EEADRL,F ; Still loading latches Increment address<br>GOTO LOOP ; Write next latches<br>START_NRITE ECON2 ; Write AAh<br>BCF EECON1,LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>NOVWF EECON2 ; Write 55h<br>MOVIW 0AAh ;<br>MOVUW 55h ; Start of required write sequence:<br>NOP ; Start of required write sequence:<br>NOV START WRITE ;<br>ECON2 ; Write AAh<br>SF EECON1, LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>START_NRITE ECON2 ; Write AAh<br>SF EECON2 ; Write AAh<br>SF EECON2 ; Write AAh<br>MOVUW 55h ; Start of required write sequence:<br>NOP ; SF EECON2 ; Write AAh<br>MOVUW 55h ; Start of required write sequence:<br>NOP ; SF WR bit to begin write<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>; After write processor continues with 3rd instruction<br>ECF EECON1,WREN ; Disable writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LOOP     | 201      | / IIIDO      | ,                                                          |

| MOVWF       EEDATL       ;         MOVTW       FSR0++       ; Load second data byte into upper         MOVF       EEDATH       ;         MOVE       EECON2       ;         MOVE       EECON2       ;         MOVE       EECON2       ;         NOP       ;       Set WR bit to begin write sequence         NOP       ;       After write processor continues with 3rd instruction.         INCF       EEADRL,F       ;       Still loading latches - Actually start Flash program         MOVIW       S5h       ;       Start of required write sequence:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -        | MOVIW    | FSR0++       | ; Load first data byte into lower                          |

| MOVIW       FSR0++       ; Load second data byte into upper         MOVWF       EEDATH       ;         MOVF       EEADRL,W       ; Check if lower bits of address are '000'         XORUW       0x07       ; Check if we're on the last of 8 addresses         ANDLW       0x07       ; Check if we're on the last of 8 addresses         ANDLW       0x07       ; Ext of required writes         GOTO       START_WRITE       ;         MOVLW       S5h       ; Start of required write sequence:         MOVWF       EECON2       ; Write 55h         MOVWF       EECON2       ; Write AAh         BSF       EECON1, WR       ; Set WR bit to begin write         NOP       ; Processor will stop here and wait for write to complete.         NOP       ; After write processor continues with 3rd instruction.         INCF       EEADRL,F       ; Still loading latches - Actually start Flash program         MOVEF       ECCON2       ; Write AAh         BCF       EECON1,LWLO       ; No more loading latches - Actually start Flash program         MOVEF       EECON2       ; Write 55h         MOVEF       EECON2       ; Write 55h         MOVEF       EECON2       ; Write 55h         MOVEF       EECON2       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |          |              | ;                                                          |

| MOVF       EEADRL,W       ; Check if lower bits of address are '000'         XORLW       0x07       ; Check if we're on the last of 8 addresses         ANDLW       0x07       ;         BTFSC       STATUS,Z       ; Exit if last of eight words,         GOTO       START_URITE       ;         MOVLW       S5h       ; Start of required write sequence:         MOVWF       EECON2       ; Write 55h         MOVWF       EECON2       ; Write 55h         MOVWF       EECON2       ; Write begin write         NOP       ; Set WR bit to begin write sequence:         NOP       ; Processor will stop here and wait for write to complete.         NOP       ; After write processor continues with 3rd instruction.         INCF       EEADRL,F       ; Still loading latches Increment address         GOTO       LOOP       ; Write next latches         START_WRITE       ECCN1,LWLO       ; No more loading latches - Actually start Flash program         MOVLW       55h       ; Start of required write sequence:         MOVIM       55h       ; Start of required write sequence:         MOVUWF       EECON2       ; Write 55h         MOVUWF       EECON2       ; Write S5h         MOVUWF       EECON1       ; Wri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | MOVIW    | FSR0++       | ; Load second data byte into upper                         |

| XORLW       0x07       ; Check if we're on the last of 8 addresses         ANDLW       0x07       ;         ANDLW       0x07       ;         BTFSC       STATUS,Z       ; Exit if last of eight words,         GOTO       START_WRITE       ;         MOVUW       S5h       ; Start of required write sequence:         MOVWF       EECON2       ; Write 55h         MOVWF       EECON2       ; Write AAh         BSF       EECON1, WR       ; Set WR bit to begin write         NOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | MOVWF    | EEDATH       | ;                                                          |

| XORLW       0x07       ; Check if we're on the last of 8 addresses         ANDLW       0x07       ;         ANDLW       0x07       ;         BTFSC       START_WRITE       ;         GOTO       START_WRITE       ;         MOVUW       55h       ;       Start of required write sequence:         MOVWF       EECON2       ;       Write 55h         MOVWF       EECON2       ;       Write AAh         BSF       EECON1,WR       ;       Set WR bit to begin write         NOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |          |              |                                                            |

| ANDLW 0x07 ;<br>BTFSC STATUS,Z ; Exit if last of eight words,<br>GOTO START_WRITE ;<br>MOVLW 55h ; Start of required write sequence:<br>MOVWF EECON2 ; Write 55h<br>MOVWF EECON2 ; Write AAh<br>BSF EECON1,WR ; Set WR bit to begin write<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>NOP ; Processor will stop here and wait for write to complete.<br>; After write processor continues with 3rd instruction.<br>INCF EEADRL,F ; Still loading latches Increment address<br>GOTO LOOP ; Write next latches<br>START_WRITE<br>BCF EECON1,LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>MOVLW 55h ; Start of required write sequence:<br>MOVLW 55h ; Start of required write sequence:<br>MOVLW 0AAh ;<br>MOVWF EECON2 ; Write AAh<br>BSF EECON1, WR ; Set WR bit to begin write<br>NOP ; Write AAh<br>BSF EECON1, WR ; Set WR bit to begin write<br>NOP ; Processor will stop here and wait for write complete.<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence:<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>; Processor will stop here and wait for write complete.<br>; after write processor continues with 3rd instruction<br>BCF EECON1, WREN ; Disable writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |          |              |                                                            |

| BTFSC STATUS,2 ; Exit if last of eight words,<br>GOTO START_WRITE ;<br>MOVLW 55h ; Start of required write sequence:<br>MOVWF EECON2 ; Write 55h<br>MOUWW 0AAh ;<br>MOVWF EECON2 ; Write AAh<br>BSF EECON1,WR ; Set WR bit to begin write<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>NOP ; Processor will stop here and wait for write to complete.<br>; After write processor continues with 3rd instruction.<br>INCF EEADRL,F ; Still loading latches Increment address<br>GOTO LOOP ; Write next latches<br>START_WRITE<br>BCF EECON1,LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>MOVLW 55h ; Start of required write sequence:<br>MOVWF EECON2 ; Write 55h<br>MOVWF EECON2 ; Write 55h<br>MOVWF EECON2 ; Write AAh<br>BSF BECON1,WR ; Set WR bit to begin write<br>MOVWF EECON2 ; Write Sh<br>MOVWF EECON2 ; Write Sh<br>MOVWF EECON2 ; Write AAh<br>BSF BECON1,WR ; Set WE bit to begin write<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>; Processor will stop here and wait for write complete.<br>; after write processor continues with 3rd instruction<br>BCF EECON1,WREN ; Disable writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |          |              | ; Check if we're on the last of 8 addresses                |

| GOTO START_WRITE ;<br>MOVLW 55h ; Start of required write sequence:<br>MOVWF EECON2 ; Write 55h<br>MOVLW 0AAh ;<br>MOVWF EECON2 ; Write AAh<br>BSF EECON1,WR ; Set WR bit to begin write<br>Any instructions here are ignored as processor<br>; halts to begin write sequence<br>NOP ; Processor will stop here and wait for write to complete.<br>; After write processor continues with 3rd instruction.<br>INCF EEADRL,F ; Still loading latches Increment address<br>GOTO LOOP ; Write next latches<br>START_WRITE<br>BCF EECON1,LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>MOVWF EECCN2 ; Write 55h<br>MOVWF EECCN2 ; Write 55h<br>MOVWF EECCN2 ; Write 55h<br>MOVWF EECCN2 ; Write AAh<br>BSF EECON1,WR ; Set WR bit to begin write<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>; Processor will stop here and wait for write complete.<br>; After write processor continues with 3rd instruction<br>BCF EECON1,WREN ; Disable writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |          |              |                                                            |

| MOVLW 55h ; Start of required write sequence:<br>MOVWF EECON2 ; Write 55h<br>MOVWF EECON2 ; Write AAh<br>BSF EECON1, WR ; Set WR bit to begin write<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>NOP ; Processor will stop here and wait for write to complete.<br>; After write processor continues with 3rd instruction.<br>INCF EEADRL,F ; Still loading latches Increment address<br>GOTO LOOP ; Write next latches<br>START_WRITE<br>ECF EECON1,LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>MOVIW 55h ; Start of required write sequence:<br>MOVWF EECON2 ; Write 55h<br>MOVWF EECON2 ; Write 55h<br>MOVWF EECON2 ; Write AAh<br>ESF EECON1, WR ; Set WR bit to begin write<br>; Any instructions here are ignored as processor<br>; halts to begin write<br>ECF EECON1, WR ; Set WR bit to begin write<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence.<br>NOP ; Processor will stop here and wait for write complete.<br>; Ary instructions here are ignored as processor<br>; halts to begin write<br>ECF EECON1, WR ; Set WR bit to begin write<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>NOP ; Processor will stop here and wait for write complete.<br>; after write processor continues with 3rd instruction<br>ECF EECON1, WR ; Disable writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |          |              | -                                                          |

| MOVWF EECON2 ; Write 55h<br>MOVWF EECON2 ; Write 55h<br>MOVWF EECON2 ; Write AAh<br>BSF EECON1,WR ; Set WR bit to begin write<br>; Any instructions here are ignored as processor<br>; halts to begin write sequence<br>NOP ; Processor will stop here and wait for write to complete.<br>; After write processor continues with 3rd instruction.<br>INCF EEADRL,F ; Still loading latches Increment address<br>GOTO LOOP ; Write next latches<br>START_WRITE<br>BCF EECON1,LWLO ; No more loading latches - Actually start Flash program<br>; memory write<br>MOVLW 55h ; Start of required write sequence:<br>WOVWF EECON2 ; Write 55h<br>MOVLW 0AAh ;<br>WOVWF EECON2 ; Write AAh<br>BSF EECON1,WR ; Set WR bit to begin write<br>BSF EECON1,WR ; Set WR bit to begin write<br>NOP ; Processor will stop here and wait for write complete.<br>; Alter write processor continues with 3rd instruction<br>ECF EECON1,WREN ; Disable writes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | 6010     | SIAKI_WKIIE  | '                                                          |