#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1938-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

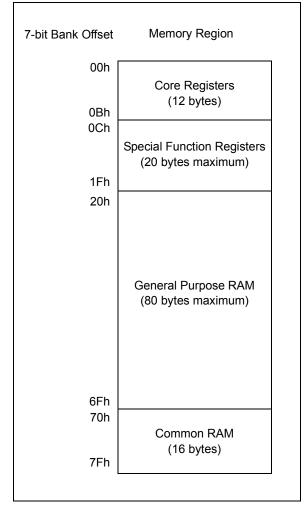

#### 3.3.1 SPECIAL FUNCTION REGISTER

The Special Function Registers are registers used by the application to control the desired operation of peripheral functions in the device. The registers associated with the operation of the peripherals are described in the appropriate peripheral chapter of this data sheet.

#### 3.3.2 GENERAL PURPOSE RAM

There are up to 80 bytes of GPR in each data memory bank.

#### 3.3.2.1 Linear Access to GPR

The general purpose RAM can be accessed in a non-banked method via the FSRs. This can simplify access to large memory structures. See Section 3.6.2 "Linear Data Memory" for more information.

#### 3.3.3 COMMON RAM

There are 16 bytes of common RAM accessible from all banks.

#### FIGURE 3-2: BANKED MEMORY PARTITIONING

#### 3.3.4 DEVICE MEMORY MAPS

The memory maps for the device family are as shown in Table 3-2.

#### TABLE 3-2: MEMORY MAP TABLES

| Device      | Banks | Table No.            |

|-------------|-------|----------------------|

| PIC16F1938  | 0-7   | Table 3-3            |

| PIC16LF1938 | 8-15  | Table 3-4, Table 3-7 |

|             | 16-23 | Table 3-5            |

|             | 23-31 | Table 3-6, Table 3-9 |

| PIC16F1939  | 0-7   | Table 3-3            |

| PIC16LF1939 | 8-15  | Table 3-4, Table 3-8 |

|             | 16-23 | Table 3-5            |

|             | 23-31 | Table 3-6, Table 3-9 |

### 6.12 Power Control (PCON) Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- Stack Overflow Reset (STKOVF)

- Stack Underflow Reset (STKUNF)

- MCLR Reset (RMCLR)

The PCON register bits are shown in Register 6-2.

#### 6.13 Register Definitions: Power Control (PCON)

#### REGISTER 6-2: PCON: POWER CONTROL REGISTER

| R/W/HS-0/q | R/W/HS-0/q | U-0 | U-0 | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-q/u | R/W/HC-q/u |

|------------|------------|-----|-----|------------|------------|------------|------------|

| STKOVF     | STKUNF     | —   | —   | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |     |     |            |            |            | bit 0      |

| Legend:                    |                      |                                                       |

|----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by har | dware                | HS = Bit is set by hardware                           |

| R = Readable bit           | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged       | x = Bit is unknown   | -m/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set           | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | STKOVF: Stack Overflow Flag bit                                                                       |

|---------|-------------------------------------------------------------------------------------------------------|

|         | 1 = A Stack Overflow occurred                                                                         |

|         | 0 = A Stack Overflow has not occurred or set to '0' by firmware                                       |

| bit 6   | STKUNF: Stack Underflow Flag bit                                                                      |

|         | 1 = A Stack Underflow occurred                                                                        |

|         | 0 = A Stack Underflow has not occurred or set to '0' by firmware                                      |

| bit 5-4 | Unimplemented: Read as '0'                                                                            |

| bit 3   | RMCLR: MCLR Reset Flag bit                                                                            |

|         | 1 = A $\overline{\text{MCLR}}$ Reset has not occurred or set to '1' by firmware                       |

|         | 0 = A MCLR Reset has occurred (set to '0' in hardware when a MCLR Reset occurs)                       |

| bit 2   | RI: RESET Instruction Flag bit                                                                        |

|         | 1 = A RESET instruction has not been executed or set to '1' by firmware                               |

|         | 0 = A RESET instruction has been executed (set to '0' in hardware upon executing a RESET instruction) |

| bit 1   | POR: Power-on Reset Status bit                                                                        |

|         | 1 = No Power-on Reset occurred                                                                        |

|         | 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)                 |

| bit 0   | BOR: Brown-out Reset Status bit                                                                       |

|         | 1 = No Brown-out Reset occurred                                                                       |

|         | 0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset     |

|         | occurs)                                                                                               |

|         |                                                                                                       |

| R/W-0/0         | R/W-0/0                                                                                                                                                  | R/W-0/0                            | R/W-0/0         | R/W-0/0         | R/W-0/0          | R/W-0/0 | R/W-0/0     |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|-----------------|------------------|---------|-------------|

| TMR1GIE         | ADIE                                                                                                                                                     | RCIE                               | TXIE            | SSPIE           | CCP1IE           | TMR2IE  | TMR1IE      |

| bit 7           |                                                                                                                                                          |                                    |                 |                 |                  |         | bit (       |

| Legend:         |                                                                                                                                                          |                                    |                 |                 |                  |         |             |

| R = Readab      | le bit                                                                                                                                                   | W = Writable                       | bit             | U = Unimpler    | nented bit, read | as '0'  |             |

| u = Bit is und  |                                                                                                                                                          | x = Bit is unkr                    | nown            | •               | at POR and BO    |         | ther Resets |

| '1' = Bit is se | •                                                                                                                                                        | '0' = Bit is cle                   | ared            |                 |                  |         |             |

| <b>L:4 7</b>    |                                                                                                                                                          | iment Cata Inte                    | www.wt Enchlau  | .:4             |                  |         |             |

| bit 7           |                                                                                                                                                          | imer1 Gate Inte<br>the Timer1 Gate |                 |                 |                  |         |             |

|                 |                                                                                                                                                          | the Timer1 Gat                     |                 |                 |                  |         |             |

| bit 6           | ADIE: A/D C                                                                                                                                              | onverter (ADC)                     | Interrupt Ena   | ble bit         |                  |         |             |

|                 |                                                                                                                                                          | the ADC interru                    |                 |                 |                  |         |             |

|                 |                                                                                                                                                          | the ADC interru                    | •               |                 |                  |         |             |

| bit 5           |                                                                                                                                                          | T Receive Inter                    | •               | it              |                  |         |             |

|                 |                                                                                                                                                          | the USART rec<br>the USART rec     |                 |                 |                  |         |             |

| bit 4           |                                                                                                                                                          | T Transmit Inter                   | •               |                 |                  |         |             |

|                 |                                                                                                                                                          | the USART trar                     | •               |                 |                  |         |             |

|                 | 0 = Disables                                                                                                                                             | the USART tra                      | nsmit interrup  | t               |                  |         |             |

| bit 3           | SSPIE: Sync                                                                                                                                              | hronous Serial                     | Port (MSSP)     | Interrupt Enabl | e bit            |         |             |

|                 |                                                                                                                                                          | the MSSP inter the MSSP inter      |                 |                 |                  |         |             |

| bit 2           | CCP1IE: CC                                                                                                                                               | P1 Interrupt En                    | able bit        |                 |                  |         |             |

|                 |                                                                                                                                                          | the CCP1 interr                    |                 |                 |                  |         |             |

| bit 1           |                                                                                                                                                          |                                    | •               | nable bit       |                  |         |             |

|                 | <b>TMR2IE:</b> TMR2 to PR2 Match Interrupt Enable bit<br>1 = Enables the Timer2 to PR2 match interrupt<br>0 = Disables the Timer2 to PR2 match interrupt |                                    |                 |                 |                  |         |             |

| bit 0           |                                                                                                                                                          | ner1 Overflow Ir                   |                 | •               |                  |         |             |

|                 |                                                                                                                                                          | the Timer1 over                    |                 |                 |                  |         |             |

|                 | 0 = Disables                                                                                                                                             | the Timer1 ove                     | rflow interrupt | :               |                  |         |             |

| Note: B         | it PEIE of the IN                                                                                                                                        |                                    | must bo         |                 |                  |         |             |

|                 | et to enable any                                                                                                                                         |                                    |                 |                 |                  |         |             |

### REGISTER 7-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| TABLE 10-3: | SUMMA | ARY OF R | EGISTER | S ASSOCI |  | IDOG TIM | ER |

|-------------|-------|----------|---------|----------|--|----------|----|

|             |       |          |         |          |  |          |    |

| Name   | Bit 7  | Bit 6 | Bit 5     | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|-------|-----------|-------|------------|-------|-------|--------|---------------------|

| OSCCON | SPLLEN |       | IRCF<3:0> |       |            | _     | SCS   | <1:0>  | 73                  |

| STATUS | —      |       |           | TO    | PD         | Z     | DC    | С      | 24                  |

| WDTCON | _      | _     |           |       | WDTPS<4:0> | >     |       | SWDTEN | 105                 |

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

### TABLE 10-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4  | Bit 11/3 | Bit 10/2 | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|-----------|----------|----------|-----------|---------|---------------------|

| CONFIG1 | 13:8 | _       | _       | FCMEN    | IESO      | CLKOUTEN | BORE     | N<1:0>    | CPD     | 54                  |

| CONFIGT | 7:0  | CP      | MCLRE   | PWRTE    | WDTE<1:0> |          |          | FOSC<2:0> |         | 54                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

### 12.6 Register Definitions: PORTB Control

#### REGISTER 12-6: PORTB: PORTB REGISTER

| R/W-x/u                                 | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u                                               | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-----------------------------------------|---------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| RB7                                     | RB6     | RB5               | RB4     | RB3                                                   | RB2     | RB1     | RB0     |  |

| bit 7                                   |         |                   |         |                                                       |         |         | bit 0   |  |

|                                         |         |                   |         |                                                       |         |         |         |  |

| Legend:                                 |         |                   |         |                                                       |         |         |         |  |

| R = Readable I                          | oit     | W = Writable      | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unchanged x = Bit is unknown |         |                   | nown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared    |                                                       |         |         |         |  |

bit 7-0 **RB<7:0>**: PORTB I/O Pin bit 1 = Port pin is > VIH 0 = Port pin is < VIL

#### REGISTER 12-7: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2  | TRISB1  | TRISB0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **TRISB<7:0>:** PORTB Tri-State Control bits 1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

#### REGISTER 12-8: LATB: PORTB DATA LATCH REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| LATB7   | LATB6   | LATB5   | LATB4   | LATB3   | LATB2   | LATB1   | LATB0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LATB<7:0>: PORTB Output Latch Value bits<sup>(1)</sup>

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

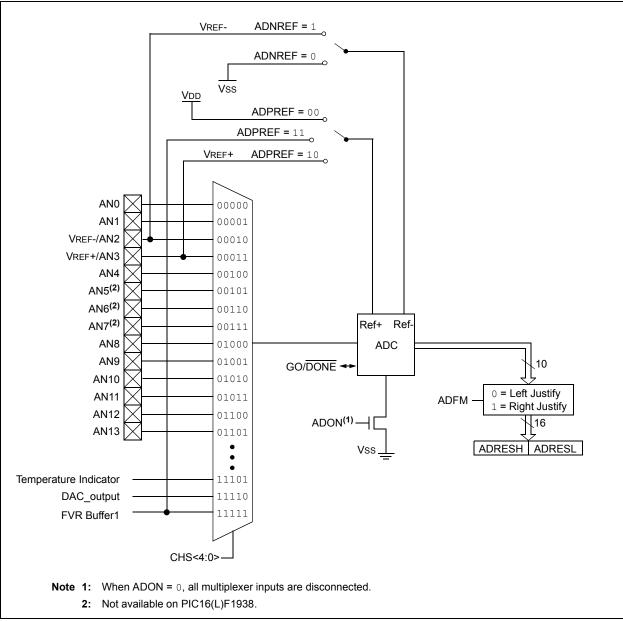

### 15.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair). Figure 15-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

#### FIGURE 15-1: ADC BLOCK DIAGRAM

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

### 15.2 ADC Operation

#### 15.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |  |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | same instruction that turns on the ADC.  |  |  |  |  |  |  |  |  |  |

|       | Refer to Section 15.2.6 "A/D Conver-     |  |  |  |  |  |  |  |  |  |

|       | sion Procedure".                         |  |  |  |  |  |  |  |  |  |

#### 15.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 15.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

#### 15.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 15.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCPx/ECCPX module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

#### TABLE 15-2: SPECIAL EVENT TRIGGER

| Device        | CCPx/ECCPx |

|---------------|------------|

| PIC16(L)F193X | CCP5       |

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 23.0 "Capture/Compare/PWM Modules" for more information.

NOTES:

| Name    | Bit 7      | Bit 6          | Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |                           |        |            |        |        | Register<br>on Page |

|---------|------------|----------------|-------------------------------------------|---------------------------|--------|------------|--------|--------|---------------------|

| CCP2CON | P2M<       | <1:0>          | DC2B                                      | 3<1:0>                    |        | CCP2M<3:0> |        |        |                     |

| INTCON  | GIE        | PEIE           | TMR0IE                                    | INTE                      | IOCIE  | TMR0IF     | INTF   | IOCIF  | 90                  |

| PIE1    | TMR1GIE    | ADIE           | RCIE                                      | TXIE                      | SSPIE  | CCP1IE     | TMR2IE | TMR1IE | 91                  |

| PIE3    |            | CCP5IE         | CCP4IE                                    | CCP3IE                    | TMR6IE |            | TMR4IE | _      | 93                  |

| PIR1    | TMR1GIF    | ADIF           | RCIF                                      | TXIF                      | SSPIF  | CCP1IF     | TMR2IF | TMR1IF | 94                  |

| PIR3    | —          | CCP5IF         | F CCP4IF CCP3IF TMR6IF — TMR4IF —         |                           |        |            |        | 96     |                     |

| PR2     | Timer2 Mod | dule Period    | Register                                  | •                         |        |            |        |        | 201*                |

| PR4     | Timer4 Mod | dule Period    | Register                                  |                           |        |            |        |        | 201*                |

| PR6     | Timer6 Mod | dule Period    | Register                                  |                           |        |            |        |        | 201*                |

| T2CON   | —          |                | T2OUT                                     | PS<3:0>                   |        | TMR2ON     | T2CKP  | S<1:0> | 203                 |

| T4CON   | —          |                | T4OUTI                                    | PS<3:0>                   |        | TMR4ON     | T4CKP  | S<1:0> | 203                 |

| T6CON   | _          |                | T6OUTI                                    | PS<3:0>                   |        | TMR2ON     | T6CKP  | S<1:0> | 203                 |

| TMR2    | Holding Re | gister for the | e 8-bit TMR2                              | 2 Register                |        |            |        |        | 201*                |

| TMR4    | Holding Re | gister for the | e 8-bit TMR4                              | 4 Register <sup>(1)</sup> |        |            |        |        | 201*                |

| TMR6    | Holding Re | gister for the | e 8-bit TMR                               | 6 Register <sup>(1)</sup> |        |            |        |        | 201*                |

#### TABLE 22-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2/4/6

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

#### 23.3.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PRx is 255. The resolution is a function of the PRx register value as shown by Equation 23-4.

#### EQUATION 23-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PRx+1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

#### TABLE 23-5:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 32 MHz)

| PWM Frequency             | 1.95 kHz | 7.81 kHz | 31.25 kHz | 125 kHz | 250 kHz | 333.3 kHz |

|---------------------------|----------|----------|-----------|---------|---------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1       | 1       | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F    | 0x1F    | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8       | 7       | 6.6       |

#### TABLE 23-6: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 23-7: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PRx Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

| U-0             | U-0        | U-0               | U-0  | U-0                                | U-0           | R/W-0/0          | R/W-0/0      |  |  |

|-----------------|------------|-------------------|------|------------------------------------|---------------|------------------|--------------|--|--|

| _               | —          | —                 | _    | —                                  | —             | C5TSEL<1:0>      |              |  |  |

| bit 7           |            |                   |      |                                    |               |                  | bit 0        |  |  |

|                 |            |                   |      |                                    |               |                  |              |  |  |

| Legend:         |            |                   |      |                                    |               |                  |              |  |  |

| R = Readab      | le bit     | W = Writable      | bit  | U = Unimplemented bit, read as '0' |               |                  |              |  |  |

| u = Bit is und  | changed    | x = Bit is unkr   | nown | -n/n = Value a                     | at POR and BO | R/Value at all o | other Resets |  |  |

| '1' = Bit is se | et         | '0' = Bit is clea | ared |                                    |               |                  |              |  |  |

|                 |            |                   |      |                                    |               |                  |              |  |  |

| bit 7-2         | Unimplemen | ted: Read as '    | 0'   |                                    |               |                  |              |  |  |

| bit 1-0         | C5TSEL<1:0 | >: CCP5 Timer     |      |                                    |               |                  |              |  |  |

### REGISTER 23-3: CCPTMRS1: PWM TIMER SELECTION CONTROL REGISTER 1

DIT 1-0 00 = CCP5 is based off Timer2 in PWM mode

01 = CCP5 is based off Timer4 in PWM mode

10 = CCP5 is based off Timer6 in PWM mode

11 = Reserved

| R/W-0/0                                 | R/W-0/0                                               | R/W-0/0                                                                  | R/W-0/0              | R/W-0/0        | R/W-0/0                 | R/W-0/0        | R/W-0/0      |

|-----------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------|----------------------|----------------|-------------------------|----------------|--------------|

| CCPxASE                                 | CCPxAS2                                               | CCPxAS1                                                                  | CCPxAS0              | PSSxA          | .C<1:0>                 | PSSxB          | D<1:0>       |

| bit 7                                   |                                                       |                                                                          |                      |                |                         |                | bit 0        |

|                                         |                                                       |                                                                          |                      |                |                         |                |              |

| Legend:                                 |                                                       |                                                                          |                      |                |                         |                |              |

| R = Readat                              |                                                       | W = Writable                                                             |                      | •              | nented bit, read        |                |              |

| u = Bit is unchanged x = Bit is unknown |                                                       |                                                                          |                      | -n/n = Value a | at POR and BO           | R/Value at all | other Resets |

| '1' = Bit is s                          | et                                                    | '0' = Bit is cle                                                         | ared                 |                |                         |                |              |

| bit 7                                   | CCPxASE: (                                            | CPx Auto-Shu                                                             | tdown Event S        | tatus bit      |                         |                |              |

|                                         |                                                       | wn event has o<br>tputs are opera                                        |                      | outputs are in | shutdown state          | e              |              |

| bit 6                                   | 1 = Auto-shu                                          | CPx Auto-Shu<br>utdown 2 source<br>utdown 2 source                       | e is enabled, V      |                |                         |                |              |

| bit 5                                   | 1 = Auto-shu                                          | CPx Auto-Shu<br>utdown 1 sourc<br>utdown 1 sourc                         | e is enabled, a      |                | ),(2) output low        |                |              |

| bit 4                                   | 1 = Auto-shu                                          | CPx Auto-Shu<br>utdown 0 sourc                                           | e is enabled, a      |                | <sup>)</sup> output low |                |              |

| bit 3-2                                 | 00 <b>= Drive pi</b><br>01 <b>= Drive pi</b>          | D>: Pins PxA and Px<br>ns PxA and Px<br>ns PxA and Px<br>A and PxC tri-s | C to '0'<br>C to '1' | wn State Contr | ol bits                 |                |              |

| bit 1-0                                 | 00 <b>= Drive pi</b><br>01 <b>= Drive pi</b>          | D>: Pins PxB ar<br>ns PxB and Px<br>ns PxB and Px<br>B and PxD tri-s     | D to '0'<br>D to '1' | wn State Contr | ol bits                 |                |              |

| <b>2</b> : a                            | f CxSYNC is ena<br>async_CxOUT = a<br>async_CxOUT = a | async_C2OUT                                                              | (for CCP1 and        |                | I.                      |                |              |

#### REGISTER 23-4: CCPxAS: CCPX AUTO-SHUTDOWN CONTROL REGISTER

NOTES:

| FIGURE 25-12:                            | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                   |

|------------------------------------------|-----------------------------------------------------------------------------|

| RX/DT<br>pin<br>TX/CK pin<br>(SCKP = 0)  |                                                                             |

| TX/CK pin                                |                                                                             |

| SREN bit                                 | ·0'                                                                         |

| RCIF bit<br>(Interrupt)<br>Read<br>RXREG |                                                                             |

| Note: Timing dia                         | gram demonstrates Sync Master mode with bit SREN = $1$ and bit BRGH = $0$ . |

### TABLE 25-8:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>RECEPTION

| Name    | Bit 7    | Bit 6      | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|----------|------------|------------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF   | RCIDL      | —          | SCKP   | BRG16  | —      | WUE    | ABDEN  | 298                 |

| INTCON  | GIE      | PEIE       | TMR0IE     | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 90                  |

| PIE1    | TMR1GIE  | ADIE       | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 91                  |

| PIR1    | TMR1GIF  | ADIF       | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 94                  |

| RCREG   | EUSART R | eceive Dat | a Register |        |        |        |        |        | 292*                |

| RCSTA   | SPEN     | RX9        | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 297                 |

| SPBRGL  |          |            |            | BRG    | <7:0>  |        |        |        | 299*                |

| SPBRGH  |          |            |            | BRG<   | :15:8> |        |        |        | 299*                |

| TRISC   | TRISC7   | TRISC6     | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 134                 |

| TXSTA   | CSRC     | TX9        | TXEN       | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 296                 |

**Legend:** — = unimplemented location read as '0'. Shaded cells are not used for synchronous master reception.

\* Page provides register information.

| Name                 | Bit 7  | Bit 6   | Bit 5  | Bit 4  | Bit 3          | Bit 2      | Bit 1  | Bit 0  | Register<br>on Page |

|----------------------|--------|---------|--------|--------|----------------|------------|--------|--------|---------------------|

| ANSELA               |        |         | ANSA5  | ANSA4  | ANSA3          | ANSA2      | ANSA1  | ANSA0  | 126                 |

| ANSELB               | _      |         | ANSB5  | ANSB4  | ANSB3          | ANSB2      | ANSB1  | ANSB0  | 131                 |

| ANSELD               | ANSD7  | ANSD6   | ANSD5  | ANSD4  | ANSD3          | ANSD2      | ANSD1  | ANSD0  | 138                 |

| CPSCON0              | CPSON  | CPSRM   | _      | _      | CPSRNG<1:0>    |            | CPSOUT | TOXCS  | 321                 |

| CPSCON1              | _      |         | _      | _      |                | CPSCH<3:0> |        |        | 322                 |

| OPTION_REG           | WPUEN  | INTEDG  | TMR0CS | TMR0SE | PSA            | PS2        | PS1    | PS0    | 187                 |

| T1CON                | TMR1C  | :S<1:0> | T1CKP  | S<1:0> | T1OSCEN T1SYNC |            | -      | TMR10N | 197                 |

| TRISA                | TRISA7 | TRISA6  | TRISA5 | TRISA4 | TRISA3         | TRISA2     | TRISA1 | TRISA0 | 125                 |

| TRISB                | TRISB7 | TRISB6  | TRISB5 | TRISB4 | TRISB3         | TRISB2     | TRISB1 | TRISB0 | 130                 |

| TRISD <sup>(1)</sup> | TRISD7 | TRISD6  | TRISD5 | TRISD4 | TRISD3         | TRISD2     | TRISD1 | TRISD0 | 137                 |

#### TABLE 26-3: SUMMARY OF REGISTERS ASSOCIATED WITH CAPACITIVE SENSING

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the CPS module.

Note 1: PIC16(L)F1939 only.

| MOVWI            | Move W to INDFn                                                                                                                                                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                              |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01,10,11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                            |

| Operation:       | <ul> <li>W → INDFn</li> <li>Effective address is determined by</li> <li>FSR + 1 (preincrement)</li> <li>FSR - 1 (predecrement)</li> <li>FSR + k (relative offset)</li> <li>After the Move, the FSR value will be either:</li> <li>FSR + 1 (all increments)</li> <li>FSR - 1 (all decrements)</li> <li>Unchanged</li> </ul> |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                       |

| Mode          | Syntax | mm |  |

|---------------|--------|----|--|

| Preincrement  | ++FSRn | 00 |  |

| Predecrement  | FSRn   | 01 |  |

| Postincrement | FSRn++ | 10 |  |

| Postdecrement | FSRn   | 11 |  |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

Note: The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP |

|-----|

|-----|

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| OPTION           | Load OPTION_REG Register with W                      |  |  |  |  |

|------------------|------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] OPTION                                       |  |  |  |  |

| Operands:        | None                                                 |  |  |  |  |

| Operation:       | (W) $\rightarrow$ OPTION_REG                         |  |  |  |  |

| Status Affected: | None                                                 |  |  |  |  |

| Description:     | Move data from W register to<br>OPTION_REG register. |  |  |  |  |

| Words:           | 1                                                    |  |  |  |  |

| Cycles:          | 1                                                    |  |  |  |  |

| Example:         | OPTION                                               |  |  |  |  |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F  |  |  |  |  |

|                  | After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F   |  |  |  |  |

| RESET            | Software Reset                                                                   |

|------------------|----------------------------------------------------------------------------------|

| Syntax:          | [label] RESET                                                                    |

| Operands:        | None                                                                             |

| Operation:       | Execute a device Reset. Resets the<br>nRI flag of the PCON register.             |

| Status Affected: | None                                                                             |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by soft-<br>ware. |

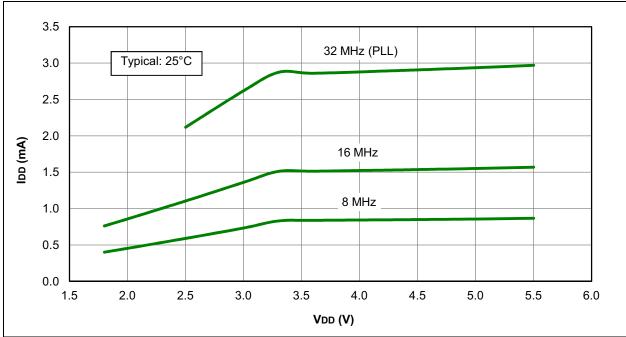

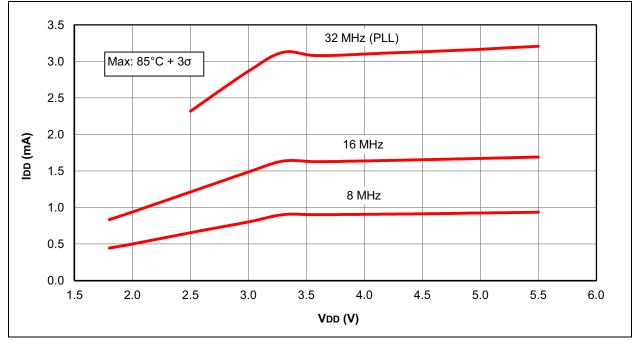

### 30.1 DC Characteristics: PIC16(L)F1938/39-I/E (Industrial, Extended)

| PIC16LF1938/39 |         |                                                                   | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |      |            |        |                                                                                                       |  |

|----------------|---------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------|--------|-------------------------------------------------------------------------------------------------------|--|

| PIC16F1938/39  |         |                                                                   | Standard Operating Conditions (unless otherwise stated)         Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended                                                               |      |            |        |                                                                                                       |  |

| Param.<br>No.  | Sym.    | Characteristic                                                    | Min.                                                                                                                                                                                                                                                           | Тур† | Max.       | Units  | Conditions                                                                                            |  |

| D001           | Vdd     | Supply Voltage                                                    |                                                                                                                                                                                                                                                                |      |            |        |                                                                                                       |  |

|                |         | PIC16LF1938/39                                                    | 1.8<br>2.5                                                                                                                                                                                                                                                     | _    | 3.6<br>3.6 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )                                                     |  |

| D001           |         | PIC16F1938/39                                                     | 1.8<br>2.5                                                                                                                                                                                                                                                     | _    | 5.5<br>5.5 | V<br>V | Fosc ≤ 16 MHz:<br>Fosc ≤ 32 MHz ( <b>Note 2</b> )                                                     |  |

| D002*          | Vdr     | RAM Data Retention Voltage <sup>(1)</sup>                         |                                                                                                                                                                                                                                                                |      |            |        | ·                                                                                                     |  |

|                |         | PIC16LF1938/39                                                    | 1.5                                                                                                                                                                                                                                                            | _    | _          | V      | Device in Sleep mode                                                                                  |  |

| D002*          |         | PIC16F1938/39                                                     | 1.7                                                                                                                                                                                                                                                            |      | —          | V      | Device in Sleep mode                                                                                  |  |

|                | VPOR*   | Power-on Reset Release Voltage                                    |                                                                                                                                                                                                                                                                |      |            |        |                                                                                                       |  |

| D002A          |         | PIC16LF1938/39                                                    | _                                                                                                                                                                                                                                                              | 1.6  |            | V      |                                                                                                       |  |

| D002A          |         | PIC16F1938/39                                                     | —                                                                                                                                                                                                                                                              | 1.6  | _          | V      |                                                                                                       |  |

|                | VPORR*  | Power-on Reset Rearm Voltage                                      |                                                                                                                                                                                                                                                                |      |            |        |                                                                                                       |  |

| D002B          |         | PIC16LF1938/39                                                    | _                                                                                                                                                                                                                                                              | 0.8  |            | V      | Device in Sleep mode                                                                                  |  |

| D002B          |         | PIC16F1938/39                                                     | _                                                                                                                                                                                                                                                              | 1.5  |            | V      | Device in Sleep mode                                                                                  |  |

| D003           | VADFVR  | Fixed Voltage Reference Voltage<br>for ADC                        | -8                                                                                                                                                                                                                                                             | _    | 6          | %      | 1.024V, VDD ≥ 2.5V<br>2.048V, VDD ≥ 2.5V<br>4.096V, VDD ≥ 4.75V                                       |  |

| D003A          | VCDAFVR | Fixed Voltage Reference Voltage<br>for Comparator and DAC         | -11                                                                                                                                                                                                                                                            | —    | 7          | %      | $\begin{array}{l} 1.024V, VDD \geq 2.5V\\ 2.048V, VDD \geq 2.5V\\ 4.096V, VDD \geq 4.75V \end{array}$ |  |

| D003B          | VLCDFVR | Fixed Voltage Reference Voltage<br>for LCD Bias, Initial Accuracy | -11                                                                                                                                                                                                                                                            | —    | 10         | %      | $3.072V, VDD \geq 3.6V$                                                                               |  |

| D004*          | SVDD    | VDD Rise Rate to ensure internal<br>Power-on Reset signal         | 0.05                                                                                                                                                                                                                                                           | —    | —          | V/ms   | See Section 6.1 "Power-on Reset (POR)" for details.                                                   |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

2: PLL required for 32 MHz operation.

\*

FIGURE 31-18: IDD MAXIMUM, EXTERNAL CLOCK (ECH), HIGH-POWER MODE, PIC16F1938/9 ONLY

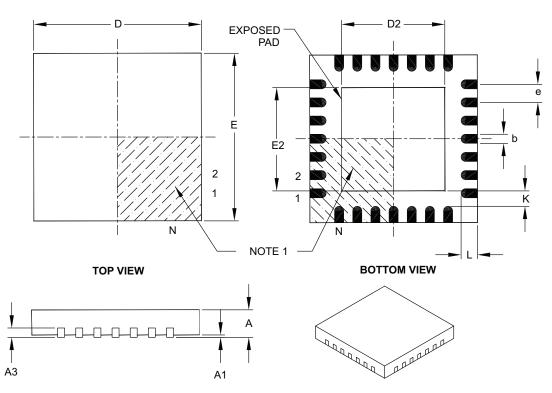

### 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            | MILLIMETERS    |          |      |  |

|------------------------|------------------|----------------|----------|------|--|

|                        | Dimension Limits |                |          | MAX  |  |

| Number of Pins         | N                | 28             |          |      |  |

| Pitch                  | е                |                | 0.65 BSC |      |  |

| Overall Height         | А                | 0.80           | 0.90     | 1.00 |  |

| Standoff               | A1               | 0.00           | 0.02     | 0.05 |  |

| Contact Thickness      | A3               | 0.20 REF       |          |      |  |

| Overall Width          | E                | 6.00 BSC       |          |      |  |

| Exposed Pad Width      | E2               | 3.65 3.70 4.20 |          | 4.20 |  |

| Overall Length D       |                  |                | 6.00 BSC |      |  |

| Exposed Pad Length     | D2               | 3.65           | 3.70     | 4.20 |  |

| Contact Width          | b                | 0.23           | 0.30     | 0.35 |  |

| Contact Length         | L                | 0.50           | 0.55     | 0.70 |  |

| Contact-to-Exposed Pad | K                | 0.20           | _        | _    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

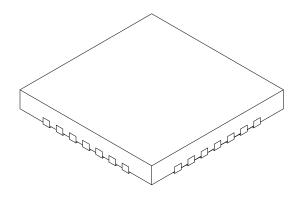

#### 28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |           |          |      |  |  |

|------------------------|-------------|-----------|----------|------|--|--|

| Dimension Limits       |             | MIN       | NOM      | MAX  |  |  |

| Number of Pins         | N           | 28        |          |      |  |  |

| Pitch                  | е           |           | 0.40 BSC |      |  |  |

| Overall Height         | A           | 0.45      | 0.50     | 0.55 |  |  |

| Standoff               | A1          | 0.00      | 0.02     | 0.05 |  |  |

| Contact Thickness      | A3          | 0.127 REF |          |      |  |  |

| Overall Width          | E           |           | 4.00 BSC |      |  |  |

| Exposed Pad Width      | E2          | 2.55      | 2.65     | 2.75 |  |  |

| Overall Length         | D           | 4.00 BSC  |          |      |  |  |

| Exposed Pad Length     | D2          | 2.55      | 2.65     | 2.75 |  |  |

| Contact Width          | b           | 0.15      | 0.20     | 0.25 |  |  |

| Contact Length         | L           | 0.30      | 0.40     | 0.50 |  |  |

| Contact-to-Exposed Pad |             | 0.20      | -        | -    |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-152A Sheet 2 of 2