#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1938t-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 3-9: PIC16(L)F1938/9 MEMORY MAP, BANK 31

|      | Bank 31                                                     |                              |  |  |  |  |  |  |  |

|------|-------------------------------------------------------------|------------------------------|--|--|--|--|--|--|--|

|      | F8Ch                                                        |                              |  |  |  |  |  |  |  |

|      |                                                             | Unimplemented<br>Read as '0' |  |  |  |  |  |  |  |

|      | FE3h                                                        |                              |  |  |  |  |  |  |  |

|      | FE4h                                                        | STATUS_SHAD                  |  |  |  |  |  |  |  |

|      | FE5h                                                        | WREG_SHAD                    |  |  |  |  |  |  |  |

|      | FE6h                                                        | BSR_SHAD                     |  |  |  |  |  |  |  |

|      | FE7h                                                        | PCLATH_SHAD                  |  |  |  |  |  |  |  |

|      | FE8h                                                        | FSR0L_SHAD                   |  |  |  |  |  |  |  |

|      | FE9h                                                        | FSR0H_SHAD                   |  |  |  |  |  |  |  |

|      | FEAh                                                        | FSR1L_SHAD                   |  |  |  |  |  |  |  |

|      | FEBh                                                        | FSR1H_SHAD                   |  |  |  |  |  |  |  |

|      | FECh                                                        | —                            |  |  |  |  |  |  |  |

|      | FEDh                                                        | STKPTR                       |  |  |  |  |  |  |  |

|      | FEEh                                                        | TOSL                         |  |  |  |  |  |  |  |

|      | FEFh                                                        | TOSH                         |  |  |  |  |  |  |  |

| Lege | Legend: = Unimplemented data memory locations, read as '0'. |                              |  |  |  |  |  |  |  |

### 3.3.5 SPECIAL FUNCTION REGISTERS SUMMARY

The Special Function Register Summary for the device family are as follows:

| Device          | Bank(s) | Page No. |

|-----------------|---------|----------|

|                 | 0       | 32       |

|                 | 1       | 33       |

|                 | 2       | 34       |

|                 | 3       | 35       |

|                 | 4       | 36       |

|                 | 5       | 37       |

| PIC16(L)F1938/9 | 6       | 38       |

|                 | 7       | 39       |

|                 | 8       | 40       |

|                 | 9-14    | 41       |

|                 | 15      | 42       |

|                 | 16-30   | 44       |

|                 | 31      | 45       |

| Address                          | Name   | Bit 7        | Bit 6                                                                                                     | Bit 5          | Bit 4    | Bit 3 | Bit 2    | Bit 1 | Bit 0 | Value<br>POR, |      | ot   | on all<br>her<br>sets |

|----------------------------------|--------|--------------|-----------------------------------------------------------------------------------------------------------|----------------|----------|-------|----------|-------|-------|---------------|------|------|-----------------------|

| Banks 1                          | 6-30   |              |                                                                                                           |                |          |       |          |       |       |               |      |      |                       |

| x00h/<br>x80h <sup>(2)</sup>     | INDF0  |              | Addressing this location uses contents of FSR0H/FSR0L to address data memory (not a physical register)    |                |          |       |          |       |       |               |      | XXXX | XXXX                  |

| x00h/<br>x81h <sup>(2)</sup>     | INDF1  |              | Addressing this location uses contents of FSR1H/FSR1L to address data memory<br>(not a physical register) |                |          |       |          |       |       |               | XXXX | XXXX | XXXX                  |

| x02h/<br>x82h <sup>(2)</sup>     | PCL    | Program Co   | ounter (PC) L                                                                                             | east Significa | int Byte |       |          |       |       | 0000          | 0000 | 0000 | 0000                  |

| x03h/<br>x83h <sup>(2)</sup>     | STATUS | —            | —                                                                                                         | —              | TO       | PD    | Z        | DC    | С     | 1             | 1000 | d    | quuu                  |

| x04h/<br>x84h <sup>(2)</sup>     | FSR0L  | Indirect Dat | Indirect Data Memory Address 0 Low Pointer                                                                |                |          |       |          |       |       |               | 0000 | uuuu | uuuu                  |

| x05h/<br>x85h <sup>(2)</sup>     | FSR0H  | Indirect Dat | Indirect Data Memory Address 0 High Pointer                                                               |                |          |       |          |       |       |               | 0000 | 0000 | 0000                  |

| x06h/<br>x86h <sup>(2)</sup>     | FSR1L  | Indirect Dat | a Memory Ac                                                                                               | Idress 1 Low   | Pointer  |       |          |       |       | 0000          | 0000 | uuuu | uuuu                  |

| x07h/<br>x87h <sup>(2)</sup>     | FSR1H  | Indirect Dat | a Memory Ac                                                                                               | ldress 1 High  | Pointer  |       |          |       |       | 0000          | 0000 | 0000 | 0000                  |

| x08h/<br>x88h <sup>(2)</sup>     | BSR    | —            | —                                                                                                         | —              |          |       | BSR<4:0> |       |       | 0             | 0000 | 0    | 0000                  |

| x09h/<br>x89h <sup>(2)</sup>     | WREG   | Working Re   | egister                                                                                                   |                | •        |       |          |       |       | 0000          | 0000 | uuuu | uuuu                  |

| x0Ah/<br>x8Ah <sup>(1),(2)</sup> | PCLATH | —            | Write Buffer for the upper 7 bits of the Program Counter                                                  |                |          |       |          |       |       |               | 0000 | -000 | 0000                  |

| x0Bh/<br>x8Bh <sup>(2)</sup>     | INTCON | GIE          | PEIE                                                                                                      | TMR0IE         | INTE     | IOCIE | TMR0IF   | INTF  | IOCIF | 0000          | 0000 | 0000 | 0000                  |

| x0Ch/<br>x8Ch                    | —      | Unimpleme    | Unimplemented                                                                                             |                |          |       |          |       |       |               | -    | -    | _                     |

| <br>x1Fh/<br>x9Fh                |        |              |                                                                                                           |                |          |       |          |       |       |               |      |      |                       |

$\label{eq:Legend: Legend: Le$

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

**2:** These registers can be addressed from any bank.

3: These registers/bits are not implemented on PIC16(L)F1938 devices, read as '0'.

4: Unimplemented, read as '1'.

| R-1/q                                                                                                                                                                                                                     | R-0/q                                                                                                                                                                                                   | R-q/q                                                    | R-0/q            | R-0/q         | R-q/q                    | R-0/q            | R-0/q        |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------|---------------|--------------------------|------------------|--------------|--|--|--|

| T10SCR                                                                                                                                                                                                                    | PLLR                                                                                                                                                                                                    | OSTS                                                     | HFIOFR           | HFIOFL        | MFIOFR                   | LFIOFR           | HFIOFS       |  |  |  |

| bit 7                                                                                                                                                                                                                     |                                                                                                                                                                                                         |                                                          | 1                | 1             |                          | 1                | bit 0        |  |  |  |

| <u> </u>                                                                                                                                                                                                                  |                                                                                                                                                                                                         |                                                          |                  |               |                          |                  |              |  |  |  |

| Legend:                                                                                                                                                                                                                   |                                                                                                                                                                                                         |                                                          |                  |               |                          |                  |              |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'                                                                                                                                                        |                                                                                                                                                                                                         |                                                          |                  |               |                          |                  |              |  |  |  |

| u = Bit is unch                                                                                                                                                                                                           | anged                                                                                                                                                                                                   | x = Bit is unk                                           | nown             | -n/n = Value  | at POR and BO            | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is set                                                                                                                                                                                                          |                                                                                                                                                                                                         | '0' = Bit is cle                                         | ared             | q = Condition | nal                      |                  |              |  |  |  |

| bit 7 <b>T1OSCR:</b> Timer1 Oscillator Ready bit<br><u>If T1OSCEN = 1</u> :<br>1 = Timer1 oscillator is ready<br>0 = Timer1 oscillator is not ready<br><u>If T1OSCEN = 0</u> :<br>1 = Timer1 clock source is always ready |                                                                                                                                                                                                         |                                                          |                  |               |                          |                  |              |  |  |  |

| bit 6                                                                                                                                                                                                                     | PLLR 4x PLL<br>1 = 4x PLL<br>0 = 4x PLL                                                                                                                                                                 | ₋ Ready bit<br>is ready                                  |                  |               |                          |                  |              |  |  |  |

| bit 5                                                                                                                                                                                                                     | 1 = Running                                                                                                                                                                                             | lator Start-up T<br>g from the clocl<br>g from an interr | c defined by the | e FOSC<2:0>   | bits of the Confi<br>00) | guration Word    | S            |  |  |  |

| bit 4                                                                                                                                                                                                                     | 1 = HFINTO                                                                                                                                                                                              | h-Frequency lı<br>SC is ready<br>SC is not ready         |                  | or Ready bit  |                          |                  |              |  |  |  |

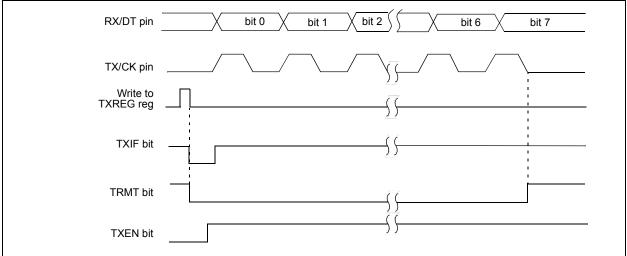

| bit 3                                                                                                                                                                                                                     | 1 = HFINTO                                                                                                                                                                                              | h-Frequency Ir<br>SC is at least 2<br>SC is not 2% a     | 2% accurate      | or Locked bit |                          |                  |              |  |  |  |

| bit 2                                                                                                                                                                                                                     | MFIOFR: Medium-Frequency Internal Oscillator Ready bit<br>1 = MFINTOSC is ready<br>0 = MFINTOSC is not ready                                                                                            |                                                          |                  |               |                          |                  |              |  |  |  |

| bit 1                                                                                                                                                                                                                     | t 1 LFIOFR: Low-Frequency Internal Oscillator Ready bit<br>1 = LFINTOSC is ready<br>0 = LFINTOSC is not ready                                                                                           |                                                          |                  |               |                          |                  |              |  |  |  |

| bit 0                                                                                                                                                                                                                     | <ul> <li>0 = LFINTOSC is not ready</li> <li>HFIOFS: High-Frequency Internal Oscillator Stable bit</li> <li>1 = HFINTOSC is at least 0.5% accurate</li> <li>0 = HFINTOSC is not 0.5% accurate</li> </ul> |                                                          |                  |               |                          |                  |              |  |  |  |

#### REGISTER 5-2: OSCSTAT: OSCILLATOR STATUS REGISTER

| R/W-0/0          | R/W-0/0                                                                             | R/W-0/0                                                                                        | R/W-0/0          | U-0              | U-0              | R/W-0/0        | R/W-0/0      |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------|------------------|------------------|----------------|--------------|--|--|--|--|

| CxINTP           | CxINTN                                                                              | CxINTN CxPCH<1:0>                                                                              |                  | _                | —                | – CxNCł        |              |  |  |  |  |

| bit 7            |                                                                                     |                                                                                                |                  |                  |                  |                | bit 0        |  |  |  |  |

|                  |                                                                                     |                                                                                                |                  |                  |                  |                |              |  |  |  |  |

| Legend:          |                                                                                     |                                                                                                |                  |                  |                  |                |              |  |  |  |  |

| R = Readable     | e bit                                                                               | W = Writable                                                                                   | bit              | U = Unimpler     | nented bit, read | l as '0'       |              |  |  |  |  |

| u = Bit is unc   | hanged                                                                              | x = Bit is unkr                                                                                | iown             | -n/n = Value a   | at POR and BO    | R/Value at all | other Resets |  |  |  |  |

| '1' = Bit is set | t                                                                                   | '0' = Bit is clea                                                                              | ared             |                  |                  |                |              |  |  |  |  |

|                  |                                                                                     |                                                                                                |                  |                  |                  |                |              |  |  |  |  |

| bit 7            | CxINTP: Con                                                                         | nparator Interru                                                                               | pt on Positive   | Going Edge E     | nable bits       |                |              |  |  |  |  |

|                  | 1 = The CxIF                                                                        | interrupt flag v                                                                               | vill be set upo  | n a positive goi | ng edge of the   | CxOUT bit      |              |  |  |  |  |

|                  | 0 = No interr                                                                       | upt flag will be                                                                               | set on a positi  | ve going edge    | of the CxOUT b   | bit            |              |  |  |  |  |

| bit 6            | CxINTN: Con                                                                         | CxINTN: Comparator Interrupt on Negative Going Edge Enable bits                                |                  |                  |                  |                |              |  |  |  |  |

|                  | 1 = The CxIF interrupt flag will be set upon a negative going edge of the CxOUT bit |                                                                                                |                  |                  |                  |                |              |  |  |  |  |

|                  | 0 = No interr                                                                       | upt flag will be                                                                               | set on a negat   | ive going edge   | of the CxOUT     | bit            |              |  |  |  |  |

| bit 5-4          | CxPCH<1:0>                                                                          | Comparator F                                                                                   | Positive Input ( | Channel Select   | bits             |                |              |  |  |  |  |

|                  | 11 = CxVP connects to Vss                                                           |                                                                                                |                  |                  |                  |                |              |  |  |  |  |

|                  | 10 = CxVP connects to FVR Voltage Reference                                         |                                                                                                |                  |                  |                  |                |              |  |  |  |  |

|                  | 01 = CxVP connects to DAC Voltage Reference<br>00 = CxVP connects to CxIN+ pin      |                                                                                                |                  |                  |                  |                |              |  |  |  |  |

| bit 3-2          |                                                                                     |                                                                                                | •                |                  |                  |                |              |  |  |  |  |

|                  | -                                                                                   | Unimplemented: Read as '0'                                                                     |                  |                  |                  |                |              |  |  |  |  |

| bit 1-0          |                                                                                     | CxNCH<1:0>: Comparator Negative Input Channel Select bits<br>11 = CxVN connects to C12IN3- pin |                  |                  |                  |                |              |  |  |  |  |

|                  |                                                                                     | onnects to C12                                                                                 |                  |                  |                  |                |              |  |  |  |  |

|                  |                                                                                     |                                                                                                |                  |                  |                  |                |              |  |  |  |  |

|                  |                                                                                     | 01 = CxVN connects to C12IN1- pin<br>00 = CxVN connects to C12IN0- pin                         |                  |                  |                  |                |              |  |  |  |  |

### REGISTER 18-2: CMxCON1: COMPARATOR Cx CONTROL REGISTER 1

#### REGISTER 18-3: CMOUT: COMPARATOR OUTPUT REGISTER

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | R-0/0  | R-0/0  |  |  |  |

|-------------|-----|-----|-----|-----|-----|--------|--------|--|--|--|

| —           | _   | _   | _   | _   | —   | MC2OUT | MC1OUT |  |  |  |

| bit 7 bit 0 |     |     |     |     |     |        |        |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-2 Unimplemented: Read as '0'

bit 1 MC2OUT: Mirror Copy of C2OUT bit

bit 0 MC1OUT: Mirror Copy of C1OUT bit

| FIGURE 21-5:           | TIMER1 GATE SINGLE-PULSE MODE                                     |

|------------------------|-------------------------------------------------------------------|

|                        |                                                                   |

| TMR1GE                 |                                                                   |

| T1GPOL                 |                                                                   |

| T1GSPM                 |                                                                   |

| T1GG <u>O/</u><br>DONE | Cleared by hardware on falling edge of T1GVAL                     |

| t1g_in                 | rising edge of T1G                                                |

| Т1СКІ                  |                                                                   |

| T1GVAL                 |                                                                   |

| Timer1                 | N N + 1 N + 2                                                     |

| TMR1GIF                | Cleared by software Cleared by hardware on falling edge of T1GVAL |

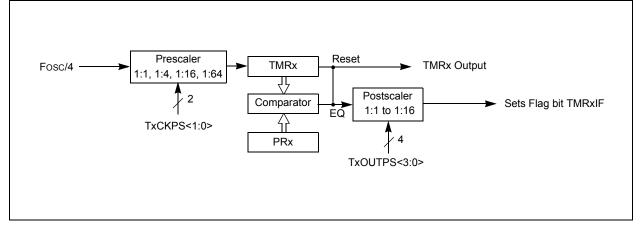

### 22.0 TIMER2/4/6 MODULES

There are up to three identical Timer2-type modules available. To maintain pre-existing naming conventions, the Timers are called Timer2, Timer4 and Timer6 (also Timer2/4/6).

| Note: | The 'x' variable used in this section is used to designate Timer2, Timer4, or |

|-------|-------------------------------------------------------------------------------|

|       | Timer6. For example, TxCON references                                         |

|       | T2CON, T4CON, or T6CON. PRx refer-                                            |

|       | ences PR2, PR4, or PR6.                                                       |

The Timer2/4/6 modules incorporate the following features:

- 8-bit Timer and Period registers (TMRx and PRx, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMRx match with PRx, respectively

- Optional use as the shift clock for the MSSP module (Timer2 only)

See Figure 22-1 for a block diagram of Timer2/4/6.

#### 23.1.6 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a Reset, see Section 12.1 "Alternate Pin Function" for more information.

| Name                 | Bit 7       | Bit 6               | Bit 5        | Bit 4          | Bit 3            | Bit 2                 | Bit 1                 | Bit 0                 | Register<br>on Page |

|----------------------|-------------|---------------------|--------------|----------------|------------------|-----------------------|-----------------------|-----------------------|---------------------|

| APFCON               | _           | CCP3SEL             | T1GSEL       | P2BSEL         | SRNQSEL          | C2OUTSEL              | SSSEL                 | CCP2SEL               | 123                 |

| CCPxCON              | PxM<        | 1:0> <sup>(1)</sup> | DCxB         | <1:0>          |                  | CCPxM<                | :3:0>                 |                       | 228                 |

| CCPRxL               | Capture/Co  | mpare/PWM           | Register x l | Low Byte (LS   | SB)              |                       |                       |                       | 206                 |

| CCPRxH               | Capture/Co  | mpare/PWM           | Register x I | High Byte (M   | ISB)             |                       |                       |                       | 206                 |

| INTCON               | GIE         | PEIE                | TMR0IE       | INTE           | IOCIE            | TMR0IF                | INTF                  | IOCIF                 | 90                  |

| PIE1                 | TMR1GIE     | ADIE                | RCIE         | TXIE           | SSPIE            | CCP1IE                | TMR2IE                | TMR1IE                | 91                  |

| PIE2                 | OSFIE       | C2IE                | C1IE         | EEIE           | BCLIE            | LCDIE                 | _                     | CCP2IE                | 92                  |

| PIE3                 | —           | CCP5IE              | CCP4IE       | CCP3IE         | TMR6IE           |                       | TMR4IE                | —                     | 93                  |

| PIR1                 | TMR1GIF     | ADIF                | RCIF         | TXIF           | SSPIF            | CCP1IF                | TMR2IF                | TMR1IF                | 94                  |

| PIR2                 | OSFIF       | C2IF                | C1IF         | EEIF           | BCLIF            | LCDIF                 | _                     | CCP2IF                | 95                  |

| PIR3                 | —           | CCP5IF              | CCP4IF       | CCP3IF         | TMR6IF           | _                     | TMR4IF                | —                     | 95                  |

| T1CON                | TMR1C       | S<1:0>              | T1CKP        | S<1:0>         | T1OSCEN          | T1SYNC                | _                     | TMR10N                | 197                 |

| T1GCON               | TMR1GE      | T1GPOL              | T1GTM        | T1GSPM         | T1GGO/DONE       | T1GVAL                | T1GS                  | S<1:0>                | 198                 |

| TMR1L                | Holding Reg | gister for the      | Least Signif | ficant Byte of | f the 16-bit TMR | 1 Register            |                       |                       | 193                 |

| TMR1H                | Holding Reg | gister for the      | Most Signifi | cant Byte of   | the 16-bit TMR1  | Register              |                       |                       | 193                 |

| TRISA                | TRISA7      | TRISA6              | TRISA5       | TRISA4         | TRISA3           | TRISA2                | TRISA1                | TRISA0                | 125                 |

| TRISB                | TRISB7      | TRISB6              | TRISB5       | TRISB4         | TRISB3           | TRISB2                | TRISB1                | TRISB0                | 130                 |

| TRISC                | TRISC7      | TRISC6              | TRISC5       | TRISC4         | TRISC3           | TRISC2                | TRISC1                | TRISC0                | 134                 |

| TRISD <sup>(2)</sup> | TRISD7      | TRISD6              | TRISD5       | TRISD4         | TRISD3           | TRISD2                | TRISD1                | TRISD0                | 137                 |

| TRISE                |             |                     |              | —              | (3)              | TRISE2 <sup>(2)</sup> | TRISE1 <sup>(2)</sup> | TRISE0 <sup>(2)</sup> | 140                 |

TABLE 23-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPTURE

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by Capture mode.

**Note 1:** Applies to ECCP modules only.

2: These registers/bits are not implemented on PIC16(L)F1938 devices, read as '0'.

3: Unimplemented, read as '1'.

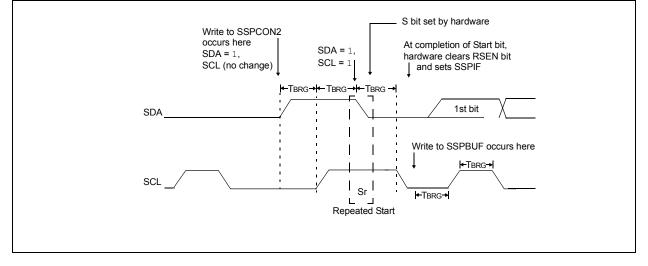

#### 24.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit of the SSPCON2 register is programmed high and the Master state machine is no longer active. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. SCL is asserted low. Following this, the RSEN bit of the SSPCON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit of the SSPSTAT register will be set. The SSPIF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

#### REGISTER 24-2: SSPCON1: SSP CONTROL REGISTER 1

| R/C/HS-0/0                        | R/C/HS-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W-0/0                                                                    | R/W-0/0                       | R/W-0/0               | R/W-0/0              | R/W-0/0        |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------|-----------------------|----------------------|----------------|

| WCOL                              | SSPOV SSPEN CKP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            | SSPM<3:0>                     |                       |                      |                |

| bit 7                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |                               |                       |                      | bit (          |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |                               |                       |                      |                |

| L <b>egend:</b><br>R = Readable I | nit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            | II = I Inimplemen             | ited bit, read as '0' |                      |                |

| u = Bit is uncha                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | x = Bit is unknow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | n                                                                          | •                             | OR and BOR/Value      | at all other Posets  |                |

|                                   | linged                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |                               |                       |                      |                |

| 1' = Bit is set                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | '0' = Bit is cleared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                          | HS = Bit is set by            | naruware              | C = User cleared     |                |

| bit 7                             | WCOL: Write Collision Detect bit<br><u>Master mode:</u><br>1 = A write to the SSPBUF register was attempted while the I <sup>2</sup> C conditions were not valid for a transmission to be started<br>0 = No collision<br><u>Slave mode:</u><br>1 = The SSPBUF register is written while it is still transmitting the previous word (must be cleared in software)<br>0 = No collision                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |                               |                       |                      |                |

| pit 6                             | <u>In SPI mode:</u><br>1 = A new byte<br>Overflow ca<br>setting overfl<br>SSPBUF re<br>0 = No overflow<br><u>In I<sup>2</sup>C mode:</u><br>1 = A byte is re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>SSPOV: Receive Overflow Indicator bit<sup>(1)</sup>         In SPI mode:         1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost.<br/>Overflow can only occur in Slave mode. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to avoid<br/>setting overflow. In Master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the<br/>SSPBUF register (must be cleared in software).         0 = No overflow<br/>In 1<sup>2</sup>C mode:         1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in Transmit mode<br/>(must be cleared in software).     </li> </ul> |                                                                            |                               |                       |                      |                |

| bit 5                             | <ul> <li>SSPEN: Synchronous Serial Port Enable bit</li> <li>In both modes, when enabled, these pins must be properly configured as input or output<br/><u>In SPI mode:</u></li> <li>1 = Enables serial port and configures SCK, SDO, SDI and SS as the source of the serial port pins<sup>(2)</sup></li> <li>0 = Disables serial port and configures these pins as I/O port pins<br/><u>In I<sup>2</sup>C mode:</u></li> <li>1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins<sup>(3)</sup></li> <li>0 = Disables serial port and configures these pins as I/O port pins</li> </ul>                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |                               |                       |                      |                |

| bit 4                             | CKP: Clock Polarity Select bit<br>In SPI mode:<br>1 = Idle state for clock is a high level<br>0 = Idle state for clock is a low level<br>In I <sup>2</sup> C Slave mode:<br>SCL release control<br>1 = Enable clock<br>0 = Holds clock low (clock stretch). (Used to ensure data setup time.)<br>In I <sup>2</sup> C Master mode:<br>Unused in this mode                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |                               |                       |                      |                |

| bit 3-0                           | SSPM<3:0>: Synchronous Serial Port Mode Select bits<br>0000 = SPI Master mode, clock = Fosc/4<br>0011 = SPI Master mode, clock = Fosc/64<br>0011 = SPI Master mode, clock = TMR2 output/2<br>0100 = SPI Slave mode, clock = SCK pin, <u>SS</u> pin control enabled<br>0101 = SPI Slave mode, clock = SCK pin, <u>SS</u> pin control disabled, <u>SS</u> can be used as I/O pin<br>0110 = I <sup>2</sup> C Slave mode, 7-bit address<br>0111 = I <sup>2</sup> C Slave mode, clock = Fosc / (4 * (SSPADD+1)) <sup>(4)</sup><br>1001 = Reserved<br>1010 = SPI Master mode, clock = Fosc / (4 * (SSPADD+1)) <sup>(5)</sup><br>1011 = I <sup>2</sup> C firmware controlled Master mode (Slave idle)<br>1100 = Reserved<br>1101 = Reserved<br>1101 = Reserved<br>1101 = Reserved<br>1101 = Reserved<br>1101 = Reserved |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                            |                               |                       |                      |                |

| 2: V<br>3: V<br>4: S              | n Master mode, the over<br>Vhen enabled, these pi<br>Vhen enabled, the SDA<br>SPADD values of 0, 1<br>SPADD value of '0' is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ins must be properl<br>A and SCL pins mu<br>or 2 are not suppo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | y configured as in<br>st be configured a<br>rted for I <sup>2</sup> C mode | nput or output.<br>as inputs. | mission) is initiated | by writing to the SS | PBUF register. |

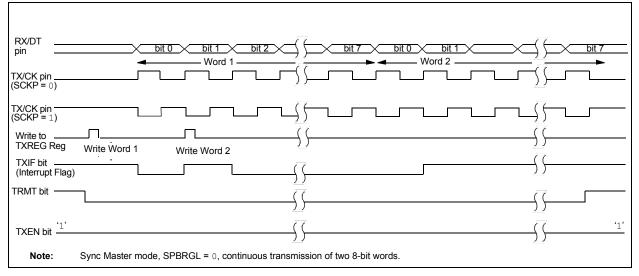

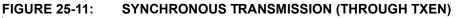

### TABLE 25-7:SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER<br/>TRANSMISSION

| Name    | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL  | _      | SCKP   | BRG16  | _      | WUE    | ABDEN  | 298                 |

| INTCON  | GIE                           | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 90                  |

| PIE1    | TMR1GIE                       | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 91                  |

| PIR1    | TMR1GIF                       | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 94                  |

| RCSTA   | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 297                 |

| SPBRGL  | BRG<7:0>                      |        |        |        |        |        |        | 299*   |                     |

| SPBRGH  | BRG<15:8>                     |        |        |        |        |        | 299*   |        |                     |

| TRISC   | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 134                 |

| TXREG   | EUSART Transmit Data Register |        |        |        |        |        | 289*   |        |                     |

| TXSTA   | CSRC                          | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 296                 |

Legend: — = unimplemented location read as '0'. Shaded cells are not used for synchronous master transmission.

\* Page provides register information.

#### 26.7.3 FREQUENCY THRESHOLD

The frequency threshold should be placed midway between the value of nominal frequency and the reduced frequency of the capacitive sensing oscillator. Refer to Application Note AN1103, "*Software Handling for Capacitive Sensing*" (DS01103) for more detailed information on the software required for CPS module.

| Note: | For more information on general capacitive sensing refer to Application Notes:        |

|-------|---------------------------------------------------------------------------------------|

|       | <ul> <li>AN1101, "Introduction to Capacitive<br/>Sensing" (DS01101)</li> </ul>        |

|       | <ul> <li>AN1102, "Layout and Physical<br/>Design Guidelines for Capacitive</li> </ul> |

### 26.8 Operation during Sleep

Sensing" (DS01102)

The capacitive sensing oscillator will continue to run as long as the module is enabled, independent of the part being in Sleep. In order for the software to determine if a frequency change has occurred, the part must be awake. However, the part does not have to be awake when the timer resource is acquiring counts.

Note: Timer0 does not operate when in Sleep, and therefore cannot be used for capacitive sense measurements in Sleep.

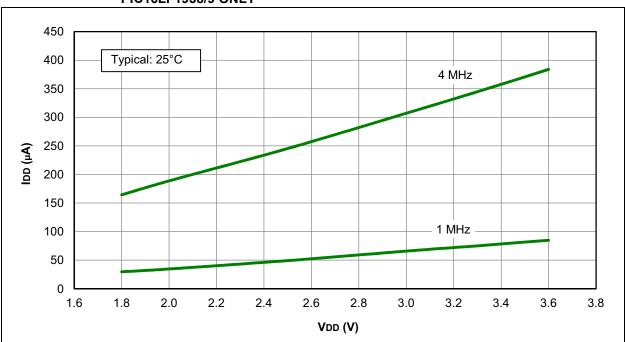

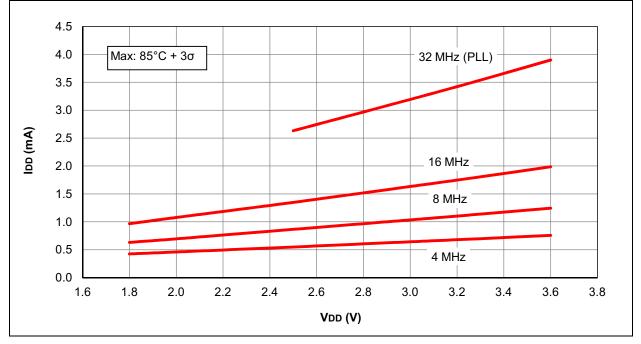

FIGURE 31-11: IDD TYPICAL, EXTERNAL CLOCK (ECM), MEDIUM-POWER MODE, PIC16LF1938/9 ONLY

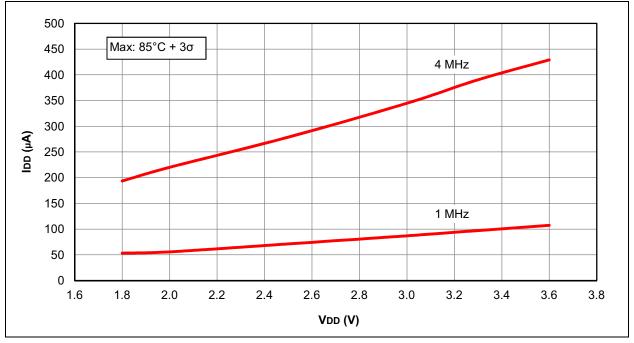

FIGURE 31-12: IDD MAXIMUM, EXTERNAL CLOCK (ECM), MEDIUM-POWER MODE, PIC16LF1938/9 ONLY

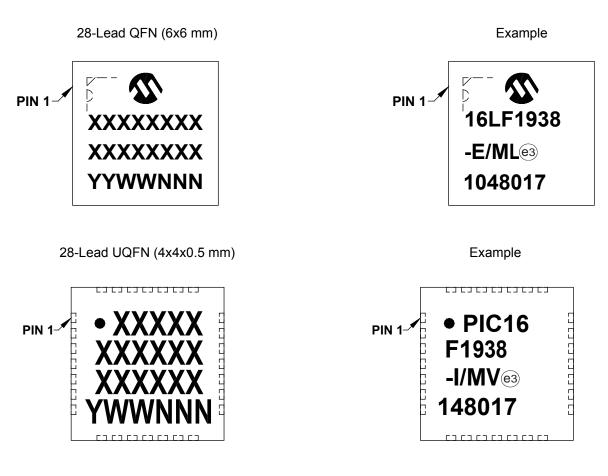

#### Package Marking Information (Continued)

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                      | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                |  |  |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

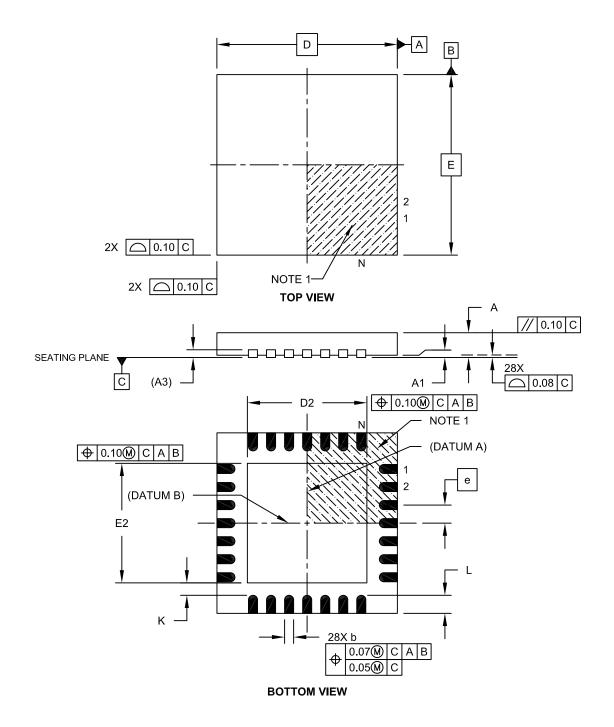

#### 28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-152A Sheet 1 of 2

### **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                 | [X] <sup>(1)</sup> - <u>X</u> /XX XXX<br>│ │ │<br>Tape and Reel Temperature Package Pattern<br>Option Range                                            | <ul> <li>Examples:</li> <li>a) PIC16LF1938 - I/P = Industrial temp., Plastic DIP package, low-voltage VDD limits.</li> <li>b) PIC16F1939 - I/PT = Industrial temp., TQFP package, standard VDD limits.</li> </ul>                                                            |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                  | PIC16F1938, PIC16LF1938<br>PIC16F1939, PIC16LF1939                                                                                                     | <ul> <li>c) PIC16F1939 - E/ML = Extended temp., QFN package, standard VDD limits.</li> </ul>                                                                                                                                                                                 |

| Tape and Reel<br>Option: | Blank = Standard packaging (tube or tray)<br>T = Tape and Reel <sup>(1)</sup>                                                                          |                                                                                                                                                                                                                                                                              |

| Temperature<br>Range:    | $ \begin{array}{rcl} I &=& -40^{\circ}\text{C to } +85^{\circ}\text{C} \\ E &=& -40^{\circ}\text{C to } +125^{\circ}\text{C} \end{array} \end{array} $ |                                                                                                                                                                                                                                                                              |

| Package:                 | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                  | Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option. |

| Pattern:                 | 3-Digit Pattern Code for QTP (blank otherwise)                                                                                                         |                                                                                                                                                                                                                                                                              |