Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1938t-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                            | Function            | Input<br>Type | Output<br>Type | Description                                                 |

|----------------------------------------------------------------------------|---------------------|---------------|----------------|-------------------------------------------------------------|

| RA0/AN0/C12IN0-/C2OUT <sup>(1)</sup> /                                     | RA0                 | TTL           | CMOS           | General purpose I/O.                                        |

| SRNQ <sup>(1)</sup> / <del>SS<sup>(1)</sup>/VCAP<sup>(2)</sup>/SEG12</del> | AN0                 | AN            | _              | A/D Channel 0 input.                                        |

|                                                                            | C12IN0-             | AN            |                | Comparator C1 or C2 negative input.                         |

|                                                                            | C2OUT               | —             | CMOS           | Comparator C2 output.                                       |

|                                                                            | SRNQ                | _             | CMOS           | SR Latch inverting output.                                  |

|                                                                            | SS                  | ST            | _              | Slave Select input.                                         |

|                                                                            | VCAP                | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F1938/9 only). |

|                                                                            | SEG12               | _             | AN             | LCD Analog output.                                          |

| RA1/AN1/C12IN1-/SEG7                                                       | RA1                 | TTL           | CMOS           | General purpose I/O.                                        |

|                                                                            | AN1                 | AN            | —              | A/D Channel 1 input.                                        |

|                                                                            | C12IN1-             | AN            | —              | Comparator C1 or C2 negative input.                         |

|                                                                            | SEG7                | _             | AN             | LCD Analog output.                                          |

| RA2/AN2/C2IN+/VREF-/                                                       | RA2                 | TTL           | CMOS           | General purpose I/O.                                        |

| DACOUT/COM2                                                                | AN2                 | AN            | —              | A/D Channel 2 input.                                        |

|                                                                            | C2IN+               | AN            | —              | Comparator C2 positive input.                               |

|                                                                            | VREF-               | AN            | —              | A/D Negative Voltage Reference input.                       |

|                                                                            | DACOUT              | —             | AN             | Voltage Reference output.                                   |

|                                                                            | COM2                | —             | AN             | LCD Analog output.                                          |

| RA3/AN3/C1IN+/VREF+/                                                       | RA3                 | TTL           | CMOS           | General purpose I/O.                                        |

| COM3 <sup>(3)</sup> /SEG15                                                 | AN3                 | AN            | —              | A/D Channel 3 input.                                        |

|                                                                            | C1IN+               | AN            | _              | Comparator C1 positive input.                               |

|                                                                            | VREF+               | AN            | —              | A/D Voltage Reference input.                                |

|                                                                            | COM3 <sup>(3)</sup> | —             | AN             | LCD Analog output.                                          |

|                                                                            | SEG15               | —             | AN             | LCD Analog output.                                          |

| RA4/C1OUT/CPS6/T0CKI/SRQ/                                                  | RA4                 | TTL           | CMOS           | General purpose I/O.                                        |

| CCP5/SEG4                                                                  | C10UT               | —             | CMOS           | Comparator C1 output.                                       |

|                                                                            | CPS6                | AN            | _              | Capacitive sensing input 6.                                 |

|                                                                            | TOCKI               | ST            | _              | Timer0 clock input.                                         |

|                                                                            | SRQ                 |               | CMOS           | SR Latch non-inverting output.                              |

|                                                                            | CCP5                | ST            | CMOS           | Capture/Compare/PWM5.                                       |

|                                                                            | SEG4                | _             | AN             | LCD Analog output.                                          |

| RA5/AN4/C2OUT <sup>(1)</sup> /CPS7/                                        | RA5                 | TTL           | CMOS           | General purpose I/O.                                        |

| SRNQ <sup>(1)</sup> /SS <sup>(1)</sup> /VCAP <sup>(2)</sup> /SEG5          | AN4                 | AN            | _              | A/D Channel 4 input.                                        |

|                                                                            | C2OUT               |               | CMOS           | Comparator C2 output.                                       |

|                                                                            | CPS7                | AN            | _              | Capacitive sensing input 7.                                 |

|                                                                            | SRNQ                | _             | CMOS           | SR Latch inverting output.                                  |

|                                                                            | SS                  | ST            | _              | Slave Select input.                                         |

|                                                                            | VCAP                | Power         | Power          | Filter capacitor for Voltage Regulator (PIC16F1938/9 only). |

|                                                                            | SEG5                | _             | AN             | LCD Analog output.                                          |

TABLE 1-2: PIC16(L)F1938/9 PINOUT DESCRIPTION

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels XTAL = Crystal

HV = High Voltage  $I^2C^{TM}$  = Schmitt Trigger input with I<sup>2</sup>C levels

**Note 1:** Pin function is selectable via the APFCON register.

- 2: PIC16F1938/9 devices only.

- 3: PIC16(L)F1938 devices only.

- 4: PORTD is available on PIC16(L)F1939 devices only.

- 5: RE<2:0> are available on PIC16(L)F1939 devices only.

## TABLE 3-9: PIC16(L)F1938/9 MEMORY MAP, BANK 31

|      |                                                            | Bank 31                      |  |  |

|------|------------------------------------------------------------|------------------------------|--|--|

|      | F8Ch                                                       |                              |  |  |

|      |                                                            | Unimplemented<br>Read as '0' |  |  |

|      | FE3h                                                       |                              |  |  |

|      | FE4h                                                       | STATUS_SHAD                  |  |  |

|      | FE5h                                                       | WREG_SHAD                    |  |  |

|      | FE6h                                                       | BSR_SHAD                     |  |  |

|      | FE7h                                                       | PCLATH_SHAD                  |  |  |

|      | FE8h                                                       | FSR0L_SHAD                   |  |  |

|      | FE9h                                                       | FSR0H_SHAD                   |  |  |

|      | FEAh                                                       | FSR1L_SHAD                   |  |  |

|      | FEBh                                                       | FSR1H_SHAD                   |  |  |

|      | FECh                                                       | —                            |  |  |

|      | FEDh                                                       | STKPTR                       |  |  |

|      | FEEh                                                       | TOSL                         |  |  |

|      | FEFh                                                       | TOSH                         |  |  |

| Lege | Legend: = Unimplemented data memory locations, rea as '0'. |                              |  |  |

## 3.3.5 SPECIAL FUNCTION REGISTERS SUMMARY

The Special Function Register Summary for the device family are as follows:

| Device          | Bank(s) | Page No. |

|-----------------|---------|----------|

|                 | 0       | 32       |

|                 | 1       | 33       |

|                 | 2       | 34       |

|                 | 3       | 35       |

|                 | 4       | 36       |

|                 | 5       | 37       |

| PIC16(L)F1938/9 | 6       | 38       |

|                 | 7       | 39       |

|                 | 8       | 40       |

|                 | 9-14    | 41       |

|                 | 15      | 42       |

|                 | 16-30   | 44       |

|                 | 31      | 45       |

# PIC16(L)F1938/9

| Address                | Name     | Bit 7                                | Bit 6                           | Bit 5          | Bit 4           | Bit 3         | Bit 2        | Bit 1     | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|----------|--------------------------------------|---------------------------------|----------------|-----------------|---------------|--------------|-----------|---------|----------------------|---------------------------------|

| Bank 5                 |          |                                      |                                 |                |                 |               |              |           |         |                      |                                 |

| 280h <sup>(2)</sup>    | INDF0    |                                      | this location<br>ical register) | uses contents  | s of FSR0H/F    | SR0L to addre | ess data mei | mory      |         | **** ****            | ****                            |

| 281h <sup>(2)</sup>    | INDF1    |                                      | this location<br>ical register) | uses contents  | s of FSR1H/F    | SR1L to addre | ess data mei | mory      |         | **** ****            | ****                            |

| 282h <sup>(2)</sup>    | PCL      | Program Co                           | ounter (PC) L                   | east Significa | int Byte        |               |              |           |         | 0000 0000            | 0000 0000                       |

| 283h <sup>(2)</sup>    | STATUS   | _                                    | _                               | _              | TO              | PD            | Z            | DC        | С       | 1 1000               | q quuu                          |

| 284h <sup>(2)</sup>    | FSR0L    | Indirect Dat                         | a Memory Ac                     | Idress 0 Low   | Pointer         |               |              | •         | •       | 0000 0000            | uuuu uuuu                       |

| 285h <sup>(2)</sup>    | FSR0H    | Indirect Dat                         | a Memory Ac                     | ldress 0 High  | Pointer         |               |              |           |         | 0000 0000            | 0000 0000                       |

| 286h <sup>(2)</sup>    | FSR1L    | Indirect Dat                         | a Memory Ac                     | Idress 1 Low   | Pointer         |               |              |           |         | 0000 0000            | uuuu uuuu                       |

| 287h <sup>(2)</sup>    | FSR1H    | Indirect Dat                         | a Memory Ac                     | ldress 1 High  | Pointer         |               |              |           |         | 0000 0000            | 0000 0000                       |

| 288h <sup>(2)</sup>    | BSR      | _                                    | _                               | —              |                 | E             | BSR<4:0>     |           |         | 0 0000               | 0 0000                          |

| 289h <sup>(2)</sup>    | WREG     | Working Re                           | gister                          |                |                 |               |              |           |         | 0000 0000            | uuuu uuuu                       |

| 28Ah <sup>(1, 2)</sup> | PCLATH   | _                                    | Write Buffer                    | for the upper  | 7 bits of the F | rogram Coun   | iter         |           |         | -000 0000            | -000 0000                       |

| 28Bh <sup>(2)</sup>    | INTCON   | GIE                                  | PEIE                            | TMR0IE         | INTE            | IOCIE         | TMR0IF       | INTF      | IOCIF   | 0000 0000            | 0000 0000                       |

| 28Ch                   | —        | Unimpleme                            | nted                            |                |                 |               |              |           |         | _                    | _                               |

| 28Dh                   | _        | Unimpleme                            | Unimplemented                   |                |                 |               |              |           | _       | _                    |                                 |

| 28Eh                   | —        | Unimpleme                            | Unimplemented                   |                |                 |               |              |           |         | _                    | _                               |

| 28Fh                   | _        | Unimpleme                            | nted                            |                |                 |               |              |           |         | _                    | _                               |

| 290h                   | _        | Unimpleme                            | nted                            |                |                 |               |              |           |         | _                    | _                               |

| 291h                   | CCPR1L   | Capture/Co                           | mpare/PWM                       | Register 1 (L  | SB)             |               |              |           |         | XXXX XXXX            | uuuu uuuu                       |

| 292h                   | CCPR1H   | Capture/Co                           | mpare/PWM                       | Register 1 (M  | ISB)            |               |              |           |         | XXXX XXXX            | uuuu uuuu                       |

| 293h                   | CCP1CON  | P1M                                  | <1:0>                           | DC1E           | 8<1:0>          |               | CCP1M        | <3:0>     |         | 0000 0000            | 0000 0000                       |

| 294h                   | PWM1CON  | P1RSEN                               |                                 |                | F               | 21DC<6:0>     |              |           |         | 0000 0000            | 0000 0000                       |

| 295h                   | CCP1AS   | CCP1ASE                              | CCP1AS2                         | CCP1AS1        | CCP1AS0         | PSS1A         | C<1:0>       | PSS1B     | D<1:0>  | 0000 0000            | 0000 0000                       |

| 296h                   | PSTR1CON | _                                    | _                               | _              | STR1SYNC        | STR1D         | STR1C        | STR1B     | STR1A   | 0 0001               | 0 0001                          |

| 297h                   | _        | Unimpleme                            | nted                            |                |                 |               |              |           |         | _                    | _                               |

| 298h                   | CCPR2L   | Capture/Co                           | mpare/PWM                       | Register 2 (L  | SB)             |               |              |           |         | XXXX XXXX            | uuuu uuuu                       |

| 299h                   | CCPR2H   | Capture/Compare/PWM Register 2 (MSB) |                                 |                |                 |               | XXXX XXXX    | uuuu uuuu |         |                      |                                 |

| 29Ah                   | CCP2CON  | P2M                                  | <1:0>                           | DC2E           | 3<1:0>          |               | CCP2M        | <3:0>     |         | 0000 0000            | 0000 0000                       |

| 29Bh                   | PWM2CON  | P2RSEN                               |                                 |                | F               | 2DC<6:0>      |              |           |         | 0000 0000            | 0000 0000                       |

| 29Ch                   | CCP2AS   | CCP2ASE                              | CCP2AS2                         | CCP2AS1        | CCP2AS0         | PSS2A         | C<1:0>       | PSS2E     | D<1:0>  | 0000 0000            | 0000 0000                       |

| 29Dh                   | PSTR2CON | _                                    | _                               | —              | STR2SYNC        | STR2D         | STR2C        | STR2B     | STR2A   | 0 0001               | 0 0001                          |

| 29Eh                   | CCPTMRS0 | C4TSEL1                              | C4TSEL0                         | C3TSEL1        | C3TSEL0         | C2TSEL1       | C2TSEL0      | C1TSEL1   | C1TSEL0 | 0000 0000            | 0000 0000                       |

| 29Fh                   | CCPTMRS1 | 1                                    |                                 | <u> </u>       |                 | <u> </u>      |              |           | L<1:0>  | 00                   | 00                              |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-10.

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16(L)F1938 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

# PIC16(L)F1938/9

NOTES:

## 6.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

### 6.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms timeout on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

## 6.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 6-3 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 6-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Device<br>Operation upon<br>release of POR | Device<br>Operation upon<br>wake- up from<br>Sleep |  |

|------------|--------|-------------|----------|--------------------------------------------|----------------------------------------------------|--|

| 11         | Х      | Х           | Active   | Waits for B                                | OR ready <sup>(1)</sup>                            |  |

| 1.0        |        | Awake       | Active   | Waite for I                                |                                                    |  |

| 10         | Х      | Sleep       | Disabled | Waits for BOR ready                        |                                                    |  |

| 0.1        | 1      | х           | Active   | Begins im                                  | mediately                                          |  |

| 01         | 0      | ^           | Disabled | Begins im                                  | mediately                                          |  |

| 00         | Х      | х           | Disabled | Begins im                                  | mediately                                          |  |

#### TABLE 6-1:BOR OPERATING MODES

Note 1: In these specific cases, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold. BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

#### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device startup is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

## 9.0 POWER-DOWN MODE (SLEEP)

The Power-Down mode is entered by executing a SLEEP instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3.  $\overline{\text{TO}}$  bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 oscillator is unaffected and peripherals that operate from it may continue operation in Sleep.

- 7. ADC is unaffected, if the dedicated FRC clock is selected.

- 8. Capacitive Sensing oscillator is unaffected.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- 10. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- I/O pins should not be floating

- External circuitry sinking current from I/O pins

- · Internal circuitry sourcing current from I/O pins

- · Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- Modules using Timer1 oscillator

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include modules such as the DAC and FVR modules. See Section 17.0 "Digital-to-Analog Converter (DAC) Module" and Section 14.0 "Fixed Voltage Reference (FVR)" for more information on these modules.

### 9.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to Section 6.11 "Determining the Cause of a Reset".

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

## 12.10 Register Definitions: PORTD Control

## REGISTER 12-14: PORTD: PORTD REGISTER<sup>(1)</sup>

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|--------------|

| RD7              | RD6     | RD5               | RD4     | RD3            | RD2              | RD1              | RD0          |

| bit 7            |         |                   |         |                |                  |                  | bit 0        |

|                  |         |                   |         |                |                  |                  |              |

| Legend:          |         |                   |         |                |                  |                  |              |

| R = Readable I   | bit     | W = Writable      | bit     | U = Unimpler   | mented bit, read | as '0'           |              |

| u = Bit is uncha | anged   | x = Bit is unkn   | iown    | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |              |

bit 7-0 **RD<7:0>**: PORTD General Purpose I/O Pin bits 1 = Port pin is > VIH 0 = Port pin is < VIL

Note 1: PORTD is not implemented on PIC16(L)F1938 devices, read as '0'.

## REGISTER 12-15: TRISD: PORTD TRI-STATE REGISTER<sup>(1)</sup>

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISD7  | TRISD6  | TRISD5  | TRISD4  | TRISD3  | TRISD2  | TRISD1  | TRISD0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **TRISD<7:0>:** PORTD Tri-State Control bits

- 1 = PORTD pin configured as an input (tri-stated)

- 0 = PORTD pin configured as an output

- Note 1: TRISD is not implemented on PIC16(L)F1938 devices, read as '0'.

- 2: PORTD implemented on PIC16(L)F1939 devices only.

## 15.4 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 15-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 15-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the

source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 15-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 15-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V VDD$

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} ; [1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{CHOLD} ; [2] V_{CHOLD} charge response to V_{APPLIED} (1 - e^{\frac{-Tc}{RC}}) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) ; combining [1] and [2]$$

*Note: Where* n = number *of bits of the ADC.*

Solving for TC:

$$T_{C} = -C_{HOLD}(R_{IC} + R_{SS} + R_{S}) \ln(1/2047)$$

= -13.5pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)

= 1.20\mu\_{S}

Therefore:

$$TACQ = 2\mu s + 1.20\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.45\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

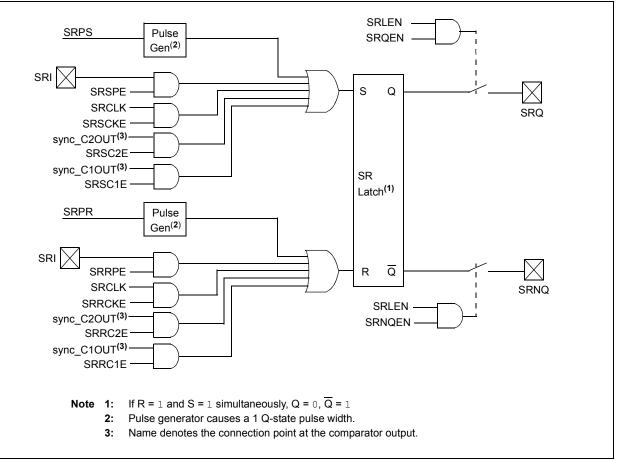

## 19.2 Latch Output

The SRQEN and SRNQEN bits of the SRCON0 register control the Q and  $\overline{Q}$  latch outputs. Both of the SR Latch outputs may be directly output to an I/O pin at the same time. The  $\overline{Q}$  latch output pin function can be moved to an alternate pin using the SRNQSEL bit of the APFCON register.

The applicable TRIS bit of the corresponding port must be cleared to enable the port pin output driver.

## 19.3 Effects of a Reset

Upon any device Reset, the SR Latch output is not initialized to a known state. The user's firmware is responsible for initializing the latch output before enabling the output pins.

#### FIGURE 19-1: SR LATCH SIMPLIFIED BLOCK DIAGRAM

## 21.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

## 21.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to using Timer1. A suitable delay similar to the OST delay can be implemented in software by clearing the TMR1IF bit then presetting the TMR1H:TMR1L register pair to FC00h. The TMR1IF flag will be set when 1024 clock cycles have elapsed, thereby indicating that the oscillator is running and reasonably stable.

## 21.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 21.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

| Note: | When switching from synchronous to        |

|-------|-------------------------------------------|

|       | asynchronous operation, it is possible to |

|       | skip an increment. When switching from    |

|       | asynchronous to synchronous operation,    |

|       | it is possible to produce an additional   |

|       | increment.                                |

#### 21.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

## 21.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

## 21.6.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 21-3 for timing details.

TABLE 21-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| $\uparrow$ | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| 1          | 1      | 1   | Counts           |

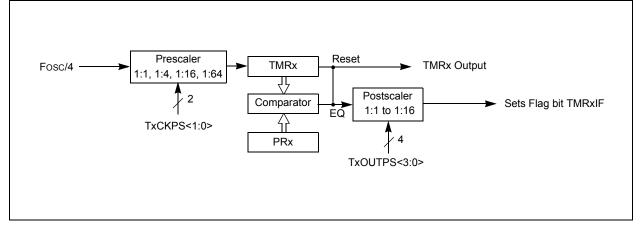

## 22.0 TIMER2/4/6 MODULES

There are up to three identical Timer2-type modules available. To maintain pre-existing naming conventions, the Timers are called Timer2, Timer4 and Timer6 (also Timer2/4/6).

| Note: | The 'x' variable used in this section is used to designate Timer2, Timer4, or |

|-------|-------------------------------------------------------------------------------|

|       | Timer6. For example, TxCON references                                         |

|       | T2CON, T4CON, or T6CON. PRx refer-                                            |

|       | ences PR2, PR4, or PR6.                                                       |

The Timer2/4/6 modules incorporate the following features:

- 8-bit Timer and Period registers (TMRx and PRx, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMRx match with PRx, respectively

- Optional use as the shift clock for the MSSP module (Timer2 only)

See Figure 22-1 for a block diagram of Timer2/4/6.

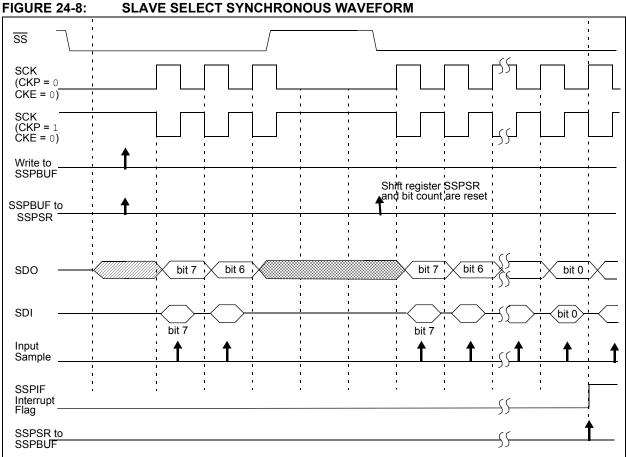

**FIGURE 24-8:**

## 24.4.9 ACKNOWLEDGE SEQUENCE

The ninth SCL pulse for any transferred byte in  $I^2C$  is dedicated as an Acknowledge. It allows receiving devices to respond back to the transmitter by pulling the SDA line low. The transmitter must release control of the line during this time to shift in the response. The Acknowledge (ACK) is an active-low signal, pulling the SDA line low indicated to the transmitter that the device has received the transmitted data and is ready to receive more.

The result of an  $\overline{ACK}$  is placed in the ACKSTAT bit of the SSPCON2 register.

Slave software, when the AHEN and DHEN bits are set, allow the user to set the  $\overline{ACK}$  value sent back to the transmitter. The ACKDT bit of the SSPCON2 register is set/cleared to determine the response.

Slave hardware will generate an ACK response if the AHEN and DHEN bits of the SSPCON3 register are clear.

There are certain conditions where an ACK will not be sent by the slave. If the BF bit of the SSPSTAT register or the SSPOV bit of the SSPCON1 register are set when a byte is received.

When the module is addressed, after the eighth falling edge of SCL on the bus, the ACKTIM bit of the SSPCON3 register is set. The ACKTIM bit indicates the acknowledge time of the active bus. The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is enabled.

## 24.5 I<sup>2</sup>C Slave Mode Operation

The MSSP Slave mode operates in one of four modes selected in the SSPM bits of SSPCON1 register. The modes can be divided into 7-bit and 10-bit Addressing mode. 10-bit Addressing modes operate the same as 7-bit with some additional overhead for handling the larger addresses.

Modes with Start and Stop bit interrupts operated the same as the other modes with SSPIF additionally getting set upon detection of a Start, Restart, or Stop condition.

## 24.5.1 SLAVE MODE ADDRESSES

The SSPADD register (Register 24-6) contains the Slave mode address. The first byte received after a Start or Restart condition is compared against the value stored in this register. If the byte matches, the value is loaded into the SSPBUF register and an interrupt is generated. If the value does not match, the module goes idle and no indication is given to the software that anything happened.

The SSP Mask register (Register 24-5) affects the address matching process. See Section 24.5.9 "SSP Mask Register" for more information.

#### 24.5.1.1 I<sup>2</sup>C Slave 7-bit Addressing Mode

In 7-bit Addressing mode, the LSb of the received data byte is ignored when determining if there is an address match.

## 24.5.1.2 I<sup>2</sup>C Slave 10-bit Addressing Mode

In 10-bit Addressing mode, the first received byte is compared to the binary value of '1 1 1 1 0 A9 A8 0'. A9 and A8 are the two MSb of the 10-bit address and stored in bits 2 and 1 of the SSPADD register.

After the acknowledge of the high byte the UA bit is set and SCL is held low until the user updates SSPADD with the low address. The low address byte is clocked in and all eight bits are compared to the low address value in SSPADD. Even if there is not an address match; SSPIF and UA are set, and SCL is held low until SSPADD is updated to receive a high byte again. When SSPADD is updated the UA bit is cleared. This ensures the module is ready to receive the high address byte on the next communication.

A high and low address match as a write request is required at the start of all 10-bit addressing communication. A transmission can be initiated by issuing a Restart once the slave is addressed, and clocking in the high address with the R/W bit set. The slave hardware will then acknowledge the read request and prepare to clock out data. This is only valid for a slave after it has received a complete high and low address byte match.

## 24.6 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate SSPM bits in the SSPCON1 register and by setting the SSPEN bit. In Master mode, the SDA and SCK pins must be configured as inputs. The MSSP peripheral hardware will override the output driver TRIS controls when necessary to drive the pins low.

Master mode of operation is supported by interrupt generation on the detection of the Start and Stop conditions. The Stop (P) and Start (S) bits are cleared from a Reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is Idle.

In Firmware Controlled Master mode, user code conducts all I<sup>2</sup>C bus operations based on Start and Stop bit condition detection. Start and Stop condition detection is the only active circuitry in this mode. All other communication is done by the user software directly manipulating the SDA and SCL lines.

The following events will cause the SSP Interrupt Flag bit, SSPIF, to be set (SSP interrupt, if enabled):

- Start condition detected

- · Stop condition detected

- · Data transfer byte transmitted/received

- Acknowledge transmitted/received

- Repeated Start generated

- Note 1: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPBUF register to initiate transmission before the Start condition is complete. In this case, the SSPBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur

- 2: When in Master mode, Start/Stop detection is masked and an interrupt is generated when the SEN/PEN bit is cleared and the generation is complete.

## 24.6.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received eight bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

A Baud Rate Generator is used to set the clock frequency output on SCL. See Section 24.7 "Baud Rate Generator" for more detail.

## REGISTER 24-5: SSPMSK: SSP MASK REGISTER

| R/W-1/1              | R/W-1/1                                                                                                                                                                                         | R/W-1/1                                                                                  | R/W-1/1                                          | R/W-1/1                                                         | R/W-1/1                      | R/W-1/1      | R/W-1/1 |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------|------------------------------|--------------|---------|--|

|                      |                                                                                                                                                                                                 |                                                                                          | MSK                                              | <7:0>                                                           |                              |              |         |  |

| bit 7                |                                                                                                                                                                                                 |                                                                                          |                                                  |                                                                 |                              |              | bit 0   |  |

|                      |                                                                                                                                                                                                 |                                                                                          |                                                  |                                                                 |                              |              |         |  |

| Legend:              |                                                                                                                                                                                                 |                                                                                          |                                                  |                                                                 |                              |              |         |  |

| R = Readable bit     |                                                                                                                                                                                                 | W = Writable bit                                                                         |                                                  | U = Unimplemented bit, read as '0'                              |                              |              |         |  |

| u = Bit is unchanged |                                                                                                                                                                                                 | x = Bit is unknown                                                                       |                                                  | -n/n = Value at POR and BOR/Value at all other Resets           |                              |              |         |  |

| '1' = Bit is set     |                                                                                                                                                                                                 | '0' = Bit is cle                                                                         | ared                                             |                                                                 |                              |              |         |  |

| bit 7-1              | MSK<7:1>:                                                                                                                                                                                       | Mask bits                                                                                |                                                  |                                                                 |                              |              |         |  |

|                      | 1 = The received address bit n is compared to SSPADD <n> to detect <math>I^2C</math> address match<br/>0 = The received address bit n is not used to detect <math>I^2C</math> address match</n> |                                                                                          |                                                  |                                                                 |                              |              |         |  |

| bit 0                | $I^2C$ Slave me<br>1 = The rec<br>0 = The rec                                                                                                                                                   | ask bit for I <sup>2</sup> C S<br>ode, 10-bit addr<br>eived address b<br>eived address b | ess (SSPM<3<br>it 0 is compar<br>it 0 is not use | 3:0> = 0111 or<br>red to SSPADD<br>d to detect I <sup>2</sup> C | <0> to detect I <sup>2</sup> | C address ma | tch     |  |

I<sup>2</sup>C Slave mode, 7-bit address, the bit is ignored

'0' = Bit is cleared

## REGISTER 24-6: SSPADD: MSSP ADDRESS AND BAUD RATE REGISTER (I<sup>2</sup>C MODE)

| 1               |                        |                 |         |                                                       |         |         |         |  |

|-----------------|------------------------|-----------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| R/W-0/0         | R/W-0/0                | R/W-0/0         | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|                 |                        |                 | ADD     | <7:0>                                                 |         |         |         |  |

| bit 7           |                        |                 |         |                                                       |         |         | bit 0   |  |

|                 |                        |                 |         |                                                       |         |         |         |  |

| Legend:         |                        |                 |         |                                                       |         |         |         |  |

| R = Readable    | e bit W = Writable bit |                 | bit     | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is unch | anged                  | x = Bit is unkn | iown    | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

#### Master mode:

'1' = Bit is set

bit 7-0 ADD<7:0>: Baud Rate Clock Divider bits SCL pin clock period = ((ADD<7:0> + 1) \*4)/Fosc

#### <u>10-Bit Slave mode – Most Significant Address Byte:</u>

- bit 7-3 **Not used:** Unused for Most Significant Address byte. Bit state of this register is a "don't care". Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, those bits are compared by hardware and are not affected by the value in this register.

- bit 2-1 ADD<2:1>: Two Most Significant bits of 10-bit address

- bit 0 Not used: Unused in this mode. Bit state is a "don't care".

#### 10-Bit Slave mode – Least Significant Address Byte:

bit 7-0 ADD<7:0>: Eight Least Significant bits of 10-bit address

#### 7-Bit Slave mode:

| bit 7-1 ADD<7:1>: 7-bit address |  |

|---------------------------------|--|

|---------------------------------|--|

bit 0 Not used: Unused in this mode. Bit state is a "don't care".

## PIC16(L)F1938/9

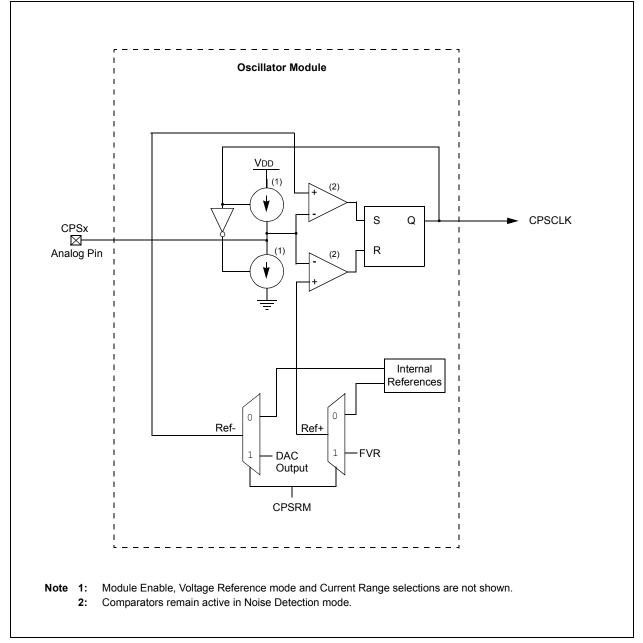

## FIGURE 26-2: CAPACITIVE SENSING OSCILLATOR BLOCK DIAGRAM

© 2011-2013 Microchip Technology Inc.

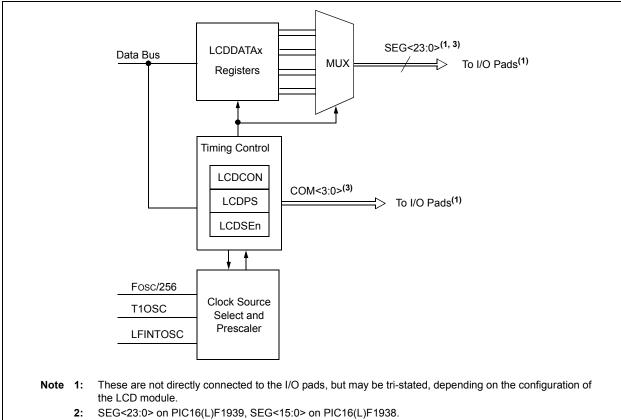

## 27.0 LIQUID CRYSTAL DISPLAY (LCD) DRIVER MODULE

The Liquid Crystal Display (LCD) Driver module generates the timing control to drive a static or multiplexed LCD panel. In the PIC16(L)F193X device, the module drives the panels of up to four commons and up to 24 segments. The LCD module also provides control of the LCD pixel data.

The LCD Driver module supports:

- Direct driving of LCD panel

- Three LCD clock sources with selectable prescaler

- Up to four common pins:

- Static (1 common)

- 1/2 multiplex (2 commons)

- 1/3 multiplex (3 commons)

- 1/4 multiplex (4 commons)

- · Segment pins up to:

- 16 (PIC16(L)F1938)

- 24 (PIC16(L)F1939)

- Static, 1/2 or 1/3 LCD Bias

## FIGURE 27-1: LCD DRIVER MODULE BLOCK DIAGRAM

3: COM3 and SEG15 share the same physical pin on the PIC16(L)F1938, therefore SEG15 is not available when using 1/4 multiplex displays.

Note: COM3 and SEG15 share the same physical pin on the PIC16(L)F1938, therefore SEG15 is not available when using 1/4 multiplex displays.

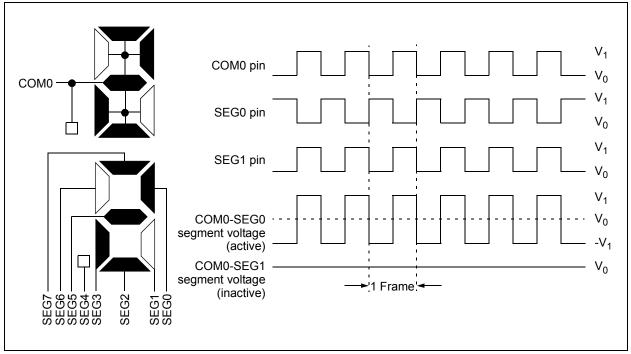

## 27.10 LCD Waveform Generation

LCD waveforms are generated so that the net AC voltage across the dark pixel should be maximized and the net AC voltage across the clear pixel should be minimized. The net DC voltage across any pixel should be zero.

The COM signal represents the time slice for each common, while the SEG contains the pixel data.

The pixel signal (COM-SEG) will have no DC component and it can take only one of the two RMS values. The higher RMS value will create a dark pixel and a lower RMS value will create a clear pixel.

As the number of commons increases, the delta between the two RMS values decreases. The delta represents the maximum contrast that the display can have.

The LCDs can be driven by two types of waveform: Type-A and Type-B. In Type-A waveform, the phase changes within each common type, whereas in Type-B waveform, the phase changes on each frame boundary. Thus, Type-A waveform maintains 0 VDc over a single frame, whereas Type-B waveform takes two frames.

- Note 1: If Sleep has to be executed with LCD Sleep disabled (LCDCON<SLPEN> is '1'), then care must be taken to execute Sleep only when VDc on all the pixels is '0'.

- 2: When the LCD clock source is Fosc/256, if Sleep is executed, irrespective of the LCDCON<SLPEN> setting, the LCD immediately goes into Sleep. Thus, take care to see that VDc on all pixels is '0' when Sleep is executed.

Figure 27-8 through Figure 27-18 provide waveforms for static, half-multiplex, 1/3-multiplex and 1/4-multiplex drives for Type-A and Type-B waveforms.

#### FIGURE 27-8: TYPE-A/TYPE-B WAVEFORMS IN STATIC DRIVE

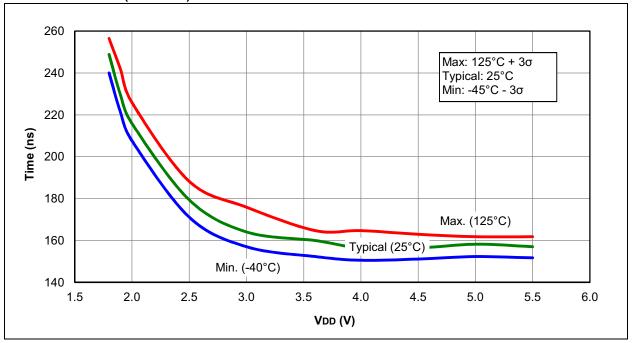

FIGURE 31-68: COMPARATOR RESPONSE TIME OVER TEMPERATURE, NORMAL-POWER MODE (CxSP = 1)