Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                  |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1938t-i-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name                                                                                    | Function | Input<br>Type    | Output<br>Type | Description                                                                                        |

|-----------------------------------------------------------------------------------------|----------|------------------|----------------|----------------------------------------------------------------------------------------------------|

| RB4/AN11/CPS4/P1D/COM0                                                                  | RB4      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

|                                                                                         | AN11     | AN               | —              | A/D Channel 11 input.                                                                              |

|                                                                                         | CPS4     | AN               | _              | Capacitive sensing input 4.                                                                        |

|                                                                                         | P1D      | _                | CMOS           | PWM output.                                                                                        |

|                                                                                         | COM0     | _                | AN             | LCD Analog output.                                                                                 |

| RB5/AN13/CPS5/P2B/CCP3 <sup>(1)</sup> /<br>P3A <sup>(1)</sup> /T1G <sup>(1)</sup> /COM1 | RB5      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

|                                                                                         | AN13     | AN               |                | A/D Channel 13 input.                                                                              |

|                                                                                         | CPS5     | AN               |                | Capacitive sensing input 5.                                                                        |

|                                                                                         | P2B      | _                | CMOS           | PWM output.                                                                                        |

|                                                                                         | CCP3     | ST               | CMOS           | Capture/Compare/PWM3.                                                                              |

|                                                                                         | P3A      | _                | CMOS           | PWM output.                                                                                        |

|                                                                                         | T1G      | ST               |                | Timer1 Gate input.                                                                                 |

|                                                                                         | COM1     | _                | AN             | LCD Analog output.                                                                                 |

| RB6/ICSPCLK/ICDCLK/SEG14                                                                | RB6      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

|                                                                                         | ICSPCLK  | ST               |                | Serial Programming Clock.                                                                          |

|                                                                                         | ICDCLK   | ST               |                | In-Circuit Debug Clock.                                                                            |

|                                                                                         | SEG14    |                  | AN             | LCD Analog output.                                                                                 |

| RB7/ICSPDAT/ICDDAT/SEG13                                                                | RB7      | TTL              | CMOS           | General purpose I/O. Individually controlled interrupt-on-change.<br>Individually enabled pull-up. |

|                                                                                         | ICSPDAT  | ST               | CMOS           | ICSP™ Data I/O.                                                                                    |

|                                                                                         | ICDDAT   | ST               | CMOS           | In-Circuit Data I/O.                                                                               |

|                                                                                         | SEG13    |                  | AN             | LCD Analog output.                                                                                 |

| RC0/T1OSO/T1CKI/P2B <sup>(1)</sup>                                                      | RC0      | ST               | CMOS           | General purpose I/O.                                                                               |

|                                                                                         | T10S0    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                      |

|                                                                                         | T1CKI    | ST               |                | Timer1 clock input.                                                                                |

|                                                                                         | P2B      |                  | CMOS           | PWM output.                                                                                        |

| RC1/T10SI/CCP2 <sup>(1)</sup> /P2A <sup>(1)</sup>                                       | RC1      | ST               | CMOS           | General purpose I/O.                                                                               |

|                                                                                         | T10SI    | XTAL             | XTAL           | Timer1 oscillator connection.                                                                      |

|                                                                                         | CCP2     | ST               | CMOS           | Capture/Compare/PWM2.                                                                              |

|                                                                                         | P2A      |                  | CMOS           | PWM output.                                                                                        |

| RC2/CCP1/P1A/SEG3                                                                       | RC2      | ST               | CMOS           | General purpose I/O.                                                                               |

|                                                                                         | CCP1     | ST               | CMOS           | Capture/Compare/PWM1.                                                                              |

|                                                                                         | P1A      | _                | CMOS           | PWM output.                                                                                        |

|                                                                                         | SEG3     | —                | AN             | LCD Analog output.                                                                                 |

| RC3/SCK/SCL/SEG6                                                                        | RC3      | ST               | CMOS           | General purpose I/O.                                                                               |

|                                                                                         | SCK      | ST               | CMOS           | SPI clock.                                                                                         |

|                                                                                         | SCL      | I <sup>2</sup> C | OD             | I <sup>2</sup> C™ clock.                                                                           |

|                                                                                         | SEG6     |                  | AN             | LCD Analog output.                                                                                 |

#### **TABLE 1-2:** PIC16(L)F1938/9 PINOUT DESCRIPTION (CONTINUED)

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels XTAL = Crystal

$I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$  levels HV = High Voltage

Note 1: Pin function is selectable via the APFCON register.

- 2: PIC16F1938/9 devices only.

- 3: PIC16(L)F1938 devices only.

- 4: PORTD is available on PIC16(L)F1939 devices only.

- 5: RE<2:0> are available on PIC16(L)F1939 devices only.

## TABLE 3-4: PIC16(L)F1938/9 MEMORY MAP, BANKS 8-15

|      | BANK 8               | -    | BANK 9               |      | BANK 10              |      | BANK 11              |      | BANK 12              |      | BANK 13       |      | BANK 14       |      | BANK 15          |

|------|----------------------|------|----------------------|------|----------------------|------|----------------------|------|----------------------|------|---------------|------|---------------|------|------------------|

| 400h | INDF0                | 480h | INDF0                | 500h | INDF0                | 580h | INDF0                | 600h | INDF0                | 680h | INDF0         | 700h | INDF0         | 780h | INDF0            |

| 401h | INDF1                | 481h | INDF1                | 501h | INDF1                | 581h | INDF1                | 601h | INDF1                | 681h | INDF1         | 701h | INDF1         | 781h | INDF1            |

| 402h | PCL                  | 482h | PCL                  | 502h | PCL                  | 582h | PCL                  | 602h | PCL                  | 682h | PCL           | 702h | PCL           | 782h | PCL              |

| 403h | STATUS               | 483h | STATUS               | 503h | STATUS               | 583h | STATUS               | 603h | STATUS               | 683h | STATUS        | 703h | STATUS        | 783h | STATUS           |

| 404h | FSR0L                | 484h | FSR0L                | 504h | FSR0L                | 584h | FSR0L                | 604h | FSR0L                | 684h | FSR0L         | 704h | FSR0L         | 784h | FSR0L            |

| 405h | FSR0H                | 485h | FSR0H                | 505h | FSR0H                | 585h | FSR0H                | 605h | FSR0H                | 685h | FSR0H         | 705h | FSR0H         | 785h | FSR0H            |

| 406h | FSR1L                | 486h | FSR1L                | 506h | FSR1L                | 586h | FSR1L                | 606h | FSR1L                | 686h | FSR1L         | 706h | FSR1L         | 786h | FSR1L            |

| 407h | FSR1H                | 487h | FSR1H                | 507h | FSR1H                | 587h | FSR1H                | 607h | FSR1H                | 687h | FSR1H         | 707h | FSR1H         | 787h | FSR1H            |

| 408h | BSR                  | 488h | BSR                  | 508h | BSR                  | 588h | BSR                  | 608h | BSR                  | 688h | BSR           | 708h | BSR           | 788h | BSR              |

| 409h | WREG                 | 489h | WREG                 | 509h | WREG                 | 589h | WREG                 | 609h | WREG                 | 689h | WREG          | 709h | WREG          | 789h | WREG             |

| 40Ah | PCLATH               | 48Ah | PCLATH               | 50Ah | PCLATH               | 58Ah | PCLATH               | 60Ah | PCLATH               | 68Ah | PCLATH        | 70Ah | PCLATH        | 78Ah | PCLATH           |

| 40Bh | INTCON               | 48Bh | INTCON               | 50Bh | INTCON               | 58Bh | INTCON               | 60Bh | INTCON               | 68Bh | INTCON        | 70Bh | INTCON        | 78Bh | INTCON           |

| 40Ch | _                    | 48Ch | _                    | 50Ch |                      | 58Ch |                      | 60Ch |                      | 68Ch | —             | 70Ch | _             | 78Ch | —                |

| 40Dh | —                    | 48Dh | _                    | 50Dh | _                    | 58Dh | —                    | 60Dh |                      | 68Dh | —             | 70Dh |               | 78Dh | —                |

| 40Eh | —                    | 48Eh | _                    | 50Eh | _                    | 58Eh | _                    | 60Eh |                      | 68Eh | —             | 70Eh | _             | 78Eh | —                |

| 40Fh | —                    | 48Fh | —                    | 50Fh | —                    | 58Fh | —                    | 60Fh | _                    | 68Fh | —             | 70Fh | —             | 78Fh | —                |

| 410h | —                    | 490h | —                    | 510h | —                    | 590h | —                    | 610h | —                    | 690h | —             | 710h | —             | 790h | —                |

| 411h | —                    | 491h | —                    | 511h | —                    | 591h | —                    | 611h | _                    | 691h | —             | 711h | —             | 791h |                  |

| 412h | —                    | 492h | —                    | 512h | —                    | 592h | —                    | 612h | —                    | 692h | —             | 712h | —             | 792h |                  |

| 413h | —                    | 493h | —                    | 513h | —                    | 593h | —                    | 613h | —                    | 693h | —             | 713h |               | 793h |                  |

| 414h | —                    | 494h | _                    | 514h | _                    | 594h | _                    | 614h | _                    | 694h | _             | 714h |               | 794h |                  |

| 415h | TMR4                 | 495h | —                    | 515h | —                    | 595h | —                    | 615h | _                    | 695h | _             | 715h | _             | 795h |                  |

| 416h | PR4                  | 496h | —                    | 516h | _                    | 596h | _                    | 616h | _                    | 696h |               | 716h |               | 796h |                  |

| 417h | T4CON                | 497h | _                    | 517h | _                    | 597h | _                    | 617h | _                    | 697h | _             | 717h | _             | 797h |                  |

| 418h | _                    | 498h | _                    | 518h | _                    | 598h | _                    | 618h | _                    | 698h | _             | 718h | _             | 798h |                  |

| 419h | _                    | 499h | _                    | 519h | _                    | 599h | _                    | 619h | _                    | 699h | _             | 719h | _             | 799h |                  |

| 41Ah | —                    | 49Ah | —                    | 51Ah | _                    | 59Ah |                      | 61Ah |                      | 69Ah | _             | 71Ah | _             | 79Ah | See Table 3-7 or |

| 41Bh |                      | 49Bh | _                    | 51Bh | _                    | 59Bh |                      | 61Bh |                      | 69Bh | _             | 71Bh |               | 79Bh | Table 3-8        |

| 41Ch | TMR6                 | 49Ch |                      | 51Ch |                      | 59Ch |                      | 61Ch |                      | 69Ch | _             | 71Ch |               | 79Ch |                  |

| 41Dh | PR6                  | 49Dh | _                    | 51Dh |                      | 59Dh |                      | 61Dh |                      | 69Dh | _             | 71Dh | _             | 79Dh |                  |

| 41Eh | T6CON                | 49Eh | _                    | 51Eh | —                    | 59Eh | —                    | 61Eh |                      | 69Eh |               | 71Eh |               | 79Eh |                  |

| 41Fh | —                    | 49Fh | —                    | 51Fh | —                    | 59Fh | —                    | 61Fh | —                    | 69Fh | —             | 71Fh | _             | 79Fh |                  |

| 420h |                      | 4A0h |                      | 520h |                      | 5A0h |                      | 620h | General Purpose      | 6A0h |               | 720h |               | 7A0h |                  |

|      | General              |      | General              |      | General              |      | General              |      | Register<br>48 Bytes |      |               |      |               |      |                  |

|      | Purpose              |      | Purpose              |      | Purpose              |      | Purpose              |      | 40 Byles             |      | Unimplemented |      | Unimplemented |      |                  |

|      | Register<br>80 Bytes |      | Register<br>80 Bytes |      | Register<br>80 Bytes |      | Register<br>80 Bytes |      | Unimplemented        |      | Read as '0'   |      | Read as '0'   |      |                  |

|      | of Bytes             |      | 00 Dytes             |      | 00 Dytes             |      | 00 Dytes             |      | Read as '0'          |      |               |      |               |      |                  |

| 46Fh |                      | 4EFh |                      | 56Fh |                      | 5EFh |                      | 66Fh |                      | 6EFh |               | 76Fh |               | 7EFh |                  |

| 470h |                      | 4F0h |                      | 570h |                      | 5F0h |                      | 670h |                      | 6F0h |               | 770h |               | 7F0h |                  |

|      | Accesses             |      | Accesses      |      | Accesses      |      | Accesses         |

|      | 70h – 7Fh            |      | 70h – 7Fh     |      | 70h – 7Fh     |      | 70h – 7Fh        |

| 47Fh |                      | 4FFh |                      | 57Fh |                      | 5FFh |                      | 67Fh |                      | 6FFh |               | 77Fh |               | 7FFh |                  |

Legend: = Unimplemented data memory locations, read as '0'.

| Address                | Name            | Bit 7        | Bit 6                                                                                                    | Bit 5          | Bit 4   | Bit 3   | Bit 2                | Bit 1                | Bit 0                | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|-----------------|--------------|----------------------------------------------------------------------------------------------------------|----------------|---------|---------|----------------------|----------------------|----------------------|----------------------|---------------------------------|

| Bank 2                 |                 |              |                                                                                                          |                |         |         |                      |                      |                      |                      |                                 |

| 100h <sup>(2)</sup>    | INDF0           |              | ddressing this location uses contents of FSR0H/FSR0L to address data memory<br>ot a physical register)   |                |         |         |                      |                      |                      |                      | ****                            |

| 101h <sup>(2)</sup>    | INDF1           |              | Addressing this location uses contents of FSR1H/FSR1L to address data memory<br>not a physical register) |                |         |         |                      |                      |                      |                      | ****                            |

| 102h <sup>(2)</sup>    | PCL             | Program Co   | ounter (PC) L                                                                                            | east Significa | nt Byte |         |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 103h <sup>(2)</sup>    | STATUS          | _            | _                                                                                                        | _              | TO      | PD      | Z                    | DC                   | С                    | 1 1000               | q quuu                          |

| 104h <sup>(2)</sup>    | FSR0L           | Indirect Dat | a Memory Ac                                                                                              | Idress 0 Low   | Pointer |         |                      |                      |                      | 0000 0000            | uuuu uuuu                       |

| 105h <sup>(2)</sup>    | FSR0H           | Indirect Dat | a Memory Ac                                                                                              | ldress 0 High  | Pointer |         |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 106h <sup>(2)</sup>    | FSR1L           | Indirect Dat | a Memory Ac                                                                                              | Idress 1 Low   | Pointer |         |                      |                      |                      | 0000 0000            | uuuu uuuu                       |

| 107h <sup>(2)</sup>    | FSR1H           | Indirect Dat | a Memory Ac                                                                                              | ldress 1 High  | Pointer |         |                      |                      |                      | 0000 0000            | 0000 0000                       |

| 108h <sup>(2)</sup>    | BSR             | _            | —                                                                                                        | —              |         | I       | BSR<4:0>             |                      |                      | 0 0000               | 0 0000                          |

| 109h <sup>(2)</sup>    | WREG            | Working Re   | Vorking Register                                                                                         |                |         |         |                      |                      |                      | 0000 0000            | uuuu uuuu                       |

| 10Ah <sup>(1, 2)</sup> | PCLATH          | _            | Write Buffer for the upper 7 bits of the Program Counter                                                 |                |         |         |                      |                      | -000 0000            | -000 0000            |                                 |

| 10Bh <sup>(2)</sup>    | INTCON          | GIE          | PEIE                                                                                                     | TMR0IE         | INTE    | IOCIE   | TMR0IF               | INTF                 | IOCIF                | 0000 0000            | 0000 0000                       |

| 10Ch                   | LATA            | PORTA Dat    | PORTA Data Latch                                                                                         |                |         |         |                      |                      |                      |                      | uuuu uuuu                       |

| 10Dh                   | LATB            | PORTB Da     | PORTB Data Latch                                                                                         |                |         |         |                      |                      |                      |                      | uuuu uuuu                       |

| 10Eh                   | LATC            | PORTC Da     | PORTC Data Latch                                                                                         |                |         |         |                      |                      |                      | XXXX XXXX            | uuuu uuuu                       |

| 10Fh <sup>(3)</sup>    | LATD            | PORTD Da     | ta Latch                                                                                                 |                |         |         |                      |                      |                      | XXXX XXXX            | uuuu uuuu                       |

| 110h                   | LATE            | _            | —                                                                                                        | —              | —       | —       | LATE2 <sup>(3)</sup> | LATE1 <sup>(3)</sup> | LATE0 <sup>(3)</sup> | xxx                  | uuu                             |

| 111h                   | CM1CON0         | C10N         | C10UT                                                                                                    | C10E           | C1POL   | _       | C1SP                 | C1HYS                | C1SYNC               | 0000 -100            | 0000 -100                       |

| 112h                   | CM1CON1         | C1INTP       | C1INTN                                                                                                   | C1PCH1         | C1PCH0  | _       | _                    | C1NC                 | H<1:0>               | 000000               | 000000                          |

| 113h                   | CM2CON0         | C2ON         | C2OUT                                                                                                    | C2OE           | C2POL   | _       | C2SP                 | C2HYS                | C2SYNC               | 0000 -100            | 0000 -100                       |

| 114h                   | CM2CON1         | C2INTP       | C2INTN                                                                                                   | C2PCH1         | C2PCH0  | _       | _                    | C2NC                 | H<1:0>               | 000000               | 000000                          |

| 115h                   | CMOUT           | _            | _                                                                                                        | _              | _       | _       | _                    | MC2OUT               | MC1OUT               | 00                   | 00                              |

| 116h                   | BORCON          | SBOREN       | _                                                                                                        | _              | _       | _       | _                    |                      | BORRDY               | 1 q                  | u u                             |

| 117h                   | FVRCON          | FVREN        | FVRRDY                                                                                                   | TSEN           | TSRNG   | CDAFVR1 | CDAFVR0              | ADFV                 | R<1:0>               | 0q00 00p0            | 0q00 0000                       |

| 118h                   | DACCON0         | DACEN        | DACLPS                                                                                                   | DACOE          |         | DACPS   | S<1:0>               |                      | DACNSS               | 000- 00-0            | 000- 00-0                       |

| 119h                   | DACCON1         |              |                                                                                                          |                |         | D       | ACR<4:0>             |                      | •                    | 0 0000               | 0 0000                          |

| 11Ah                   | SRCON0          | SRLEN        | SRCLK2                                                                                                   | SRCLK1         | SRCLK0  | SRQEN   | SRNQEN               | SRPS                 | SRPR                 | 0000 0000            | 0000 0000                       |

| 11Bh                   | SRCON1          | SRSPE        | SRSCKE                                                                                                   | SRSC2E         | SRSC1E  | SRRPE   | SRRCKE               | SRRC2E               | SRRC1E               | 0000 0000            | 0000 0000                       |

| 11Ch                   | _               | Unimpleme    | nted                                                                                                     |                |         |         |                      | •                    | •                    | _                    | _                               |

| 11Dh                   | APFCON          | _            | CCP3SEL                                                                                                  | T1GSEL         | P2BSEL  | SRNQSEL | C2OUTSEL             | SSSEL                | CCP2SEL              | -000 0000            | -000 0000                       |

| 11Eh                   | _               | Unimpleme    | nted                                                                                                     |                | I       |         |                      | 1                    | 1                    | _                    | _                               |

| 11Fh                   | - Unimplemented |              |                                                                                                          |                |         |         |                      |                      |                      |                      |                                 |

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) TABLE 3-10.

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend:

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

These registers can be addressed from any bank. 2:

These registers/bits are not implemented on PIC16(L)F1938 devices, read as '0'. 3:

4: Unimplemented, read as '1'.

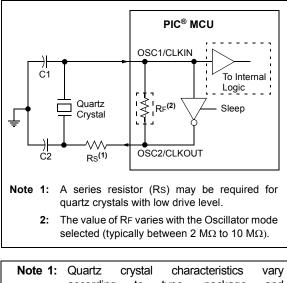

### FIGURE 5-3:

#### QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

- ote 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

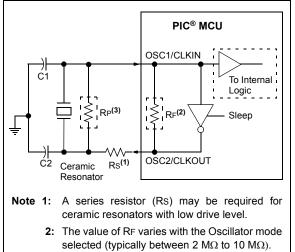

### FIGURE 5-4: CERAMIC RESONATOR OPERATION

(XT OR HS MODE)

An additional parallel feedback resistor (RP) may be required for proper ceramic resonator operation.

## 5.2.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

In order to minimize latency between external oscillator start-up and code execution, the Two-Speed Clock Start-up mode can be selected (see Section 5.4 "Two-Speed Clock Start-up Mode").

## 5.2.1.4 4X PLL

The oscillator module contains a 4X PLL that can be used with both external and internal clock sources to provide a system clock source. The input frequency for the 4X PLL must fall within specifications. See the PLL Clock Timing Specifications in the applicable Electrical Specifications Chapter.

The 4X PLL may be enabled for use by one of two methods:

- 1. Program the PLLEN bit in Configuration Words to a '1'.

- Write the SPLLEN bit in the OSCCON register to a '1'. If the PLLEN bit in Configuration Words is programmed to a '1', then the value of SPLLEN is ignored.

## 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- · GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1, PIE2 and PIE3 registers)

The INTCON, PIR1, PIR2 and PIR3 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See Section 7.5 "Automatic Context Saving")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

## 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

#### 11.7 **Register Definitions: EEPROM and Flash Control**

#### **REGISTER 11-1: EEDATL: EEPROM DATA LOW-BYTE REGISTER**

| R/W-x/u           | R/W-x/u | R/W-x/u             | R/W-x/u | R/W-x/u         | R/W-x/u            | R/W-x/u             | R/W-x/u |

|-------------------|---------|---------------------|---------|-----------------|--------------------|---------------------|---------|

|                   |         |                     | EEDA    | AT<7:0>         |                    |                     |         |

| bit 7             |         |                     |         |                 |                    |                     | bit 0   |

|                   |         |                     |         |                 |                    |                     |         |

| Legend:           |         |                     |         |                 |                    |                     |         |

| R = Readable bi   | t       | W = Writable bit    | t       | U = Unimplem    | ented bit, read as | ʻ0'                 |         |

| u = Bit is unchar | nged    | x = Bit is unknown  |         | -n/n = Value at | POR and BOR/V      | alue at all other f | Resets  |

| '1' = Bit is set  |         | '0' = Bit is cleare | ed      |                 |                    |                     |         |

bit 7-0

EEDAT<7:0>: Read/write value for EEPROM data byte or Least Significant bits of program memory

## **REGISTER 11-2: EEDATH: EEPROM DATA HIGH-BYTE REGISTER**

|     | U-0 | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-----|-----|-----|---------|---------|---------|---------|---------|---------|

|     | _   | —   |         |         | EEDA    | T<13:8> |         |         |

| bit | 7   |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

bit 5-0 EEDAT<13:8>: Read/write value for Most Significant bits of program memory

### REGISTER 11-3: EEADRL: EEPROM ADDRESS LOW-BYTE REGISTER

| EEADR<7:0> |       |  |  |  |  |  |  |  |

|------------|-------|--|--|--|--|--|--|--|

| EEADR<7:0> |       |  |  |  |  |  |  |  |

| bit 7      | bit 0 |  |  |  |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

EEADR<7:0>: Specifies the Least Significant bits for program memory address or EEPROM address

## REGISTER 11-4: EEADRH: EEPROM ADDRESS HIGH-BYTE REGISTER

| U-1   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|------------|---------|---------|---------|

| —     |         |         |         | EEADR<14:8 | >       |         |         |

| bit 7 |         |         |         |            |         |         | bit 0   |

|       |         |         |         |            |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

bit 7 Unimplemented: Read as '1'

bit 6-0 EEADR<14:8>: Specifies the Most Significant bits for program memory address or EEPROM address

## 12.3 PORTA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 12-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 12-1 shows how to initialize an I/O port.

Reading the PORTA register (Register 12-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

The TRISA register (Register 12-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

### 12.3.1 ANSELA REGISTER

The ANSELA register (Register 12-5) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

Note: The ANSELA bits default to the Analog mode after Reset. To use any pins as digital general purpose or peripheral inputs, the corresponding ANSEL bits must be initialized to '0' by user software.

### 12.3.2 PORTA FUNCTIONS AND OUTPUT PRIORITIES

Each PORTA pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-3.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC, comparator and CapSense inputs, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown in Table 12-3.

| TABLE 12-3. FURTA OUTFUT FRIORIT | <b>TABLE 12-3</b> : | PORTA OUTPUT PRIORITY |

|----------------------------------|---------------------|-----------------------|

|----------------------------------|---------------------|-----------------------|

| Pin Name | Function Priority <sup>(1)</sup>                                                                                          |

|----------|---------------------------------------------------------------------------------------------------------------------------|

| RA0      | VCAP<br>SEG12 (LCD)<br>SRNQ (SR Latch)<br>C2OUT (Comparator)<br>RA0                                                       |

| RA1      | SEG7 (LCD)<br>RA1                                                                                                         |

| RA2      | COM2 (LCD)<br>DACOUT (DAC)<br>RA2                                                                                         |

| RA3      | COM3 (LCD) 28-pin only<br>SEG15<br>RA3                                                                                    |

| RA4      | SEG4 (LCD)<br>SRQ (SR Latch)<br>C1OUT (Comparator)<br>CCP5, 28-pin only<br>RA4                                            |

| RA5      | VCAP (enabled by Config. Word)<br>SEG5 (LCD)<br>SRNQ (SR Latch)<br>C2OUT (Comparator)<br>RA5                              |

| RA6      | VCAP (enabled by Config. Word)<br>OSC2 (enabled by Config. Word)<br>CLKOUT (enabled by Config. Word)<br>SEG1 (LCD)<br>RA6 |

| RA7      | OSC1/CLKIN (enabled by Config. Word)<br>SEG2 (LCD)<br>RA7                                                                 |

Note 1: Priority listed from highest to lowest.

|                      |          |                    |                    |                    | 520                |

|----------------------|----------|--------------------|--------------------|--------------------|--------------------|

| ECCP Mode            | PxM<1:0> | CCPx/PxA           | PxB                | PxC                | PxD                |

| Single               | 00       | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> | Yes <sup>(1)</sup> |

| Half-Bridge          | 10       | Yes                | Yes                | No                 | No                 |

| Full-Bridge, Forward | 01       | Yes                | Yes                | Yes                | Yes                |

| Full-Bridge, Reverse | 11       | Yes                | Yes                | Yes                | Yes                |

#### **TABLE 23-9**: **EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES**

**Note 1:** PWM Steering enables outputs in Single mode.

#### **FIGURE 23-6:** EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH STATE)

| PxM<1:0>               | Signal        | <sup>0</sup> | PRX+1       |

|------------------------|---------------|--------------|-------------|

|                        |               | -            | - Period    |

| 00 (Single Output)     | PxA Modulated |              |             |

|                        | PxA Modulated | Delay        | Delay<br>➡━ |

| 10 (Half-Bridge)       | PxB Modulated | -            |             |

|                        | PxA Active    | - <u>-</u>   |             |

| (Full-Bridge,          | PxB Inactive  |              |             |

| <sup>01</sup> Forward) | PxC Inactive  |              |             |

|                        | PxD Modulated |              |             |

|                        | PxA Inactive  | - :          |             |

| (Full-Bridge,          | PxB Modulated | :            |             |

| Reverse)               | PxC Active    |              |             |

|                        | PxD Inactive  | - !          |             |

Period = 4 \* Tosc \* (PRx + 1) \* (TMRx Prescale Value)

Pulse Width = Tosc \* (CCPRxL<7:0>:CCPxCON<5:4>) \* (TMRx Prescale Value)

Delay = 4 \* Tosc \* (PWMxCON<6:0>)

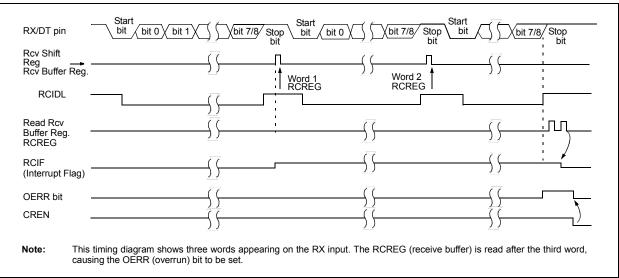

- 25.1.2.8 Asynchronous Reception Set-up:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set the RX9 bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 8. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

### 25.1.2.9 9-bit Address Detection Mode Set-up

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGH, SPBRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 25.4 "EUSART Baud Rate Generator (BRG)").

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. Enable 9-bit reception by setting the RX9 bit.

- 6. Enable address detection by setting the ADDEN bit.

- 7. Enable reception by setting the CREN bit.

- The RCIF interrupt flag bit will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit was also set.

- 9. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 10. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 11. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 12. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

## FIGURE 25-5: ASYNCHRONOUS RECEPTION

## 25.5.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the EUSART.

### 25.5.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see Section 25.5.1.3 "Synchronous Master Transmission"), except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 25.5.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

## TABLE 25-9: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Name    | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|---------|-------------------------------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| BAUDCON | ABDOVF                        | RCIDL  | _      | SCKP   | BRG16  | _      | WUE    | ABDEN  | 298                 |

| INTCON  | GIE                           | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 90                  |

| PIE1    | TMR1GIE                       | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 91                  |

| PIR1    | TMR1GIF                       | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 94                  |

| RCSTA   | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 297                 |

| TRISC   | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 134                 |

| TXREG   | EUSART Transmit Data Register |        |        |        |        | 289*   |        |        |                     |

| TXSTA   | CSRC                          | TX9    | TXEN   | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 296                 |

Legend: — = unimplemented location read as '0'. Shaded cells are not used for synchronous slave transmission. \* Page provides register information.

## REGISTER 27-2: LCDPS: LCD PHASE REGISTER

| R/W-0/0          | R/W-0/0                           | R-0/0                         | R-0/0             | R/W-0/0        | R/W-0/0          | R/W-1/1          | R/W-1/1      |

|------------------|-----------------------------------|-------------------------------|-------------------|----------------|------------------|------------------|--------------|

| WFT              | BIASMD                            | LCDA                          | WA                |                | LP<              | :3:0>            |              |

| bit 7            |                                   |                               |                   |                |                  |                  | bit 0        |

|                  |                                   |                               |                   |                |                  |                  |              |

| Legend:          |                                   |                               |                   |                |                  |                  |              |

| R = Readable     | bit                               | W = Writable                  | bit               | U = Unimpler   | nented bit, read | 1 as '0'         |              |

| u = Bit is unch  | nanged                            | x = Bit is unk                | nown              | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |                                   | '0' = Bit is cle              | ared              | C = Only clea  | rable bit        |                  |              |

|                  |                                   |                               |                   |                |                  |                  |              |

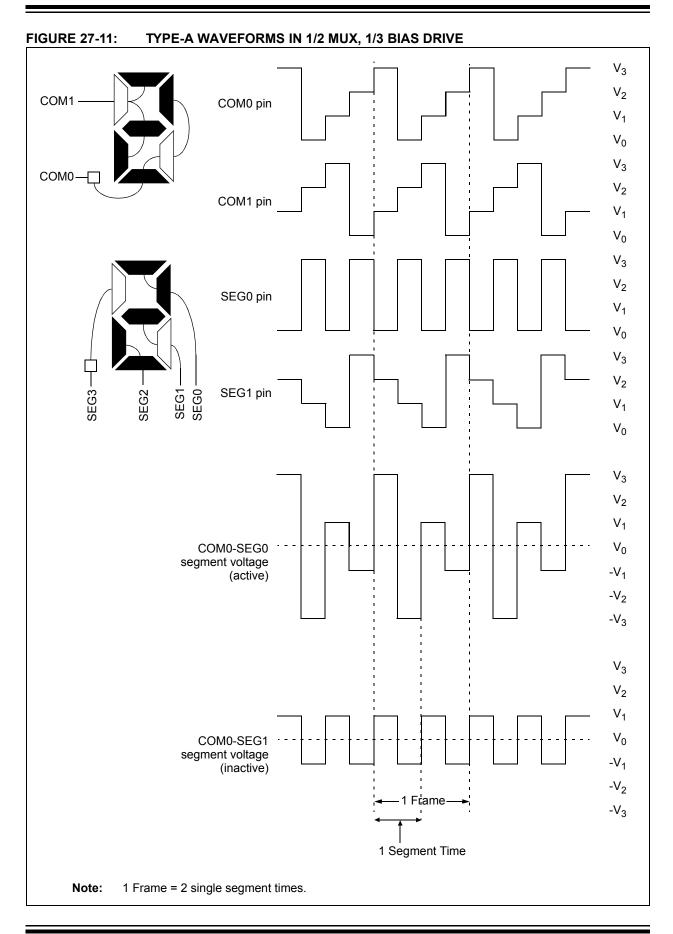

| bit 7            | WFT: Wavefo                       | orm Type bit                  |                   |                |                  |                  |              |

|                  |                                   | phase changes                 |                   |                |                  |                  |              |

|                  | • • • •                           | bhase changes                 |                   | common type    |                  |                  |              |

| bit 6            |                                   | as Mode Select                | bit               |                |                  |                  |              |

|                  | When LMUX                         |                               | t a at this hit t | - (1 )         |                  |                  |              |

|                  | When LMUX                         | as mode (do no<br><1:0> = 01: |                   | J⊥)            |                  |                  |              |

|                  | 1 = 1/2 Bias I                    |                               |                   |                |                  |                  |              |

|                  | 0 = 1/3 Bias I                    | mode                          |                   |                |                  |                  |              |

|                  | When LMUX                         |                               |                   |                |                  |                  |              |

|                  | 1 = 1/2 Bias I                    |                               |                   |                |                  |                  |              |

|                  | 0 = 1/3 Bias i<br>When LMUX       |                               |                   |                |                  |                  |              |

|                  |                                   | mode (do not s                | et this bit to '  | 1')            |                  |                  |              |

| bit 5            |                                   | Active Status b               |                   | ,              |                  |                  |              |

|                  | 1 = LCD Driv                      | er module is a                | ctive             |                |                  |                  |              |

|                  | 0 = LCD Driver module is inactive |                               |                   |                |                  |                  |              |

| bit 4            | WA: LCD Wr                        | ite Allow Status              | s bit             |                |                  |                  |              |

|                  |                                   | the LCDDATA<br>the LCDDATA    |                   |                |                  |                  |              |

| bit 3-0          | LP<3:0>: LC                       | D Prescaler Se                | election bits     |                |                  |                  |              |

|                  | 1111 <b>= 1:16</b>                |                               |                   |                |                  |                  |              |

|                  | 1110 = 1:15                       |                               |                   |                |                  |                  |              |

|                  | 1101 = 1:14<br>1100 = 1:13        |                               |                   |                |                  |                  |              |

|                  | 1011 = <b>1</b> : <b>1</b> 2      |                               |                   |                |                  |                  |              |

|                  | 1010 <b>= 1:11</b>                |                               |                   |                |                  |                  |              |

|                  | 1001 = 1:10                       |                               |                   |                |                  |                  |              |

|                  | 1000 = 1:9<br>0111 = 1:8          |                               |                   |                |                  |                  |              |

|                  | 0110 = 1:7                        |                               |                   |                |                  |                  |              |

|                  | 0101 = 1:6                        |                               |                   |                |                  |                  |              |

|                  | 0100 = 1:5<br>0011 = 1:4          |                               |                   |                |                  |                  |              |

|                  | 0011 = 1.4<br>0010 = 1:3          |                               |                   |                |                  |                  |              |

|                  | 0001 = 1:2                        |                               |                   |                |                  |                  |              |

|                  | 0000 = 1:1                        |                               |                   |                |                  |                  |              |

## 28.2 Low-Voltage Programming Entry Mode

The Low-Voltage Programming Entry mode allows the PIC16(L)F193X devices to be programmed using VDD only, without high voltage. When the LVP bit of Configuration Words is set to '1', the low-voltage ICSP programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'.

Entry into the Low-Voltage Programming Entry mode requires the following steps:

- 1.  $\overline{\text{MCLR}}$  is brought to VIL.

- 2. A 32-bit key sequence is presented on ICSPDAT, while clocking ICSPCLK.

Once the key sequence is complete,  $\overline{\text{MCLR}}$  must be held at VIL for as long as Program/Verify mode is to be maintained.

If low-voltage programming is enabled (LVP = 1), the  $\overline{\text{MCLR}}$  Reset function is automatically enabled and cannot be disabled. See **Section 6.4 "MCLR"** for more information.

The LVP bit can only be reprogrammed to '0' by using the High-Voltage Programming mode.

## 28.3 Common Programming Interfaces

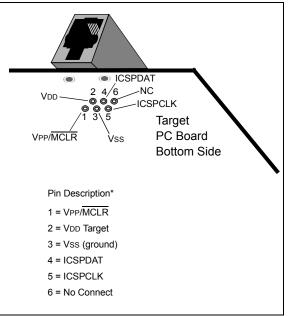

Connection to a target device is typically done through an ICSP<sup>™</sup> header. A commonly found connector on development tools is the RJ-11 in the 6P6C (6-pin, 6-connector) configuration. See Figure 28-2.

### FIGURE 28-2: ICD RJ-11 STYLE CONNECTOR INTERFACE

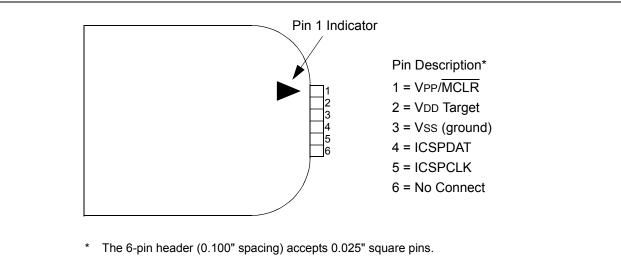

Another connector often found in use with the PICkit<sup>™</sup> programmers is a standard 6-pin header with 0.1 inch spacing. Refer to Figure 28-3.

## FIGURE 28-3: PICkit<sup>™</sup> STYLE CONNECTOR INTERFACE

| MOVWI            | Move W to INDFn                                                                                                                                                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                              |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01,10,11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                            |

| Operation:       | <ul> <li>W → INDFn</li> <li>Effective address is determined by</li> <li>FSR + 1 (preincrement)</li> <li>FSR - 1 (predecrement)</li> <li>FSR + k (relative offset)</li> <li>After the Move, the FSR value will be either:</li> <li>FSR + 1 (all increments)</li> <li>FSR - 1 (all decrements)</li> <li>Unchanged</li> </ul> |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                       |

| Mode          | Syntax | mm |  |

|---------------|--------|----|--|

| Preincrement  | ++FSRn | 00 |  |

| Predecrement  | FSRn   | 01 |  |

| Postincrement | FSRn++ | 10 |  |

| Postdecrement | FSRn   | 11 |  |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

Note: The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP |

|-----|

|-----|

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| OPTION           | Load OPTION_REG Register with W                      |

|------------------|------------------------------------------------------|

| Syntax:          | [label] OPTION                                       |

| Operands:        | None                                                 |

| Operation:       | (W) $\rightarrow$ OPTION_REG                         |

| Status Affected: | None                                                 |

| Description:     | Move data from W register to<br>OPTION_REG register. |

| Words:           | 1                                                    |

| Cycles:          | 1                                                    |

| Example:         | OPTION                                               |

|                  | Before Instruction<br>OPTION_REG = 0xFF<br>W = 0x4F  |

|                  | After Instruction<br>OPTION_REG = 0x4F<br>W = 0x4F   |

| RESET            | Software Reset                                                                   |

|------------------|----------------------------------------------------------------------------------|

| Syntax:          | [label] RESET                                                                    |

| Operands:        | None                                                                             |

| Operation:       | Execute a device Reset. Resets the<br>nRI flag of the PCON register.             |

| Status Affected: | None                                                                             |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by soft-<br>ware. |

## 30.3 DC Characteristics: PIC16(L)F1938/39-I/E (Power-Down)

| PIC16LF1938/39<br>PIC16F1938/39 |                         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |               |                                                                                                             |       | lustrial   |                                    |  |

|---------------------------------|-------------------------|------------------------------------------------------|------|---------------|-------------------------------------------------------------------------------------------------------------|-------|------------|------------------------------------|--|

|                                 |                         | Standard Operating Cond<br>Operating temperature     |      |               | ditions (unless otherwise s<br>-40°C $\leq$ TA $\leq$ +85°C for ind<br>-40°C $\leq$ TA $\leq$ +125°C for ex |       |            | lustrial                           |  |

| Param                           | Device Characteristics  | Min.                                                 | Тур† | Max.<br>+85°C | Max.<br>+125°C                                                                                              | Units | Conditions |                                    |  |

| No.                             |                         |                                                      | וקעי |               |                                                                                                             |       | VDD        | Note                               |  |

|                                 | Power-down Base Current | (IPD) <sup>(2)</sup>                                 |      |               |                                                                                                             |       |            |                                    |  |

| D023                            | Base IPD                | —                                                    | 0.06 | 1.0           | 8.0                                                                                                         | μA    | 1.8        | WDT, BOR, FVR, and T1OSC           |  |

|                                 |                         | —                                                    | 0.08 | 2.0           | 9.0                                                                                                         | μA    | 3.0        | disabled, all Peripherals Inactive |  |

| D023                            | Base IPD                | —                                                    | 15   | 35            | 45                                                                                                          | μA    | 1.8        | WDT, BOR, FVR, and T1OSC           |  |

|                                 |                         | _                                                    | 18   | 40            | 50                                                                                                          | μA    | 3.0        | disabled, all Peripherals Inactive |  |

|                                 |                         | —                                                    | 19   | 45            | 55                                                                                                          | μA    | 5.0        |                                    |  |

| D024                            |                         |                                                      | 0.5  | 6.0           | 9.0                                                                                                         | μA    | 1.8        | LPWDT Current (Note 1)             |  |

|                                 |                         | —                                                    | 0.8  | 7.0           | 10                                                                                                          | μA    | 3.0        |                                    |  |

| D024                            |                         |                                                      | 16   | 35            | 45                                                                                                          | μA    | 1.8        | LPWDT Current (Note 1)             |  |

|                                 |                         |                                                      | 19   | 40            | 50                                                                                                          | μA    | 3.0        |                                    |  |

|                                 |                         | —                                                    | 20   | 45            | 55                                                                                                          | μA    | 5.0        |                                    |  |

| D025                            |                         |                                                      | 8.5  | 23            | 30                                                                                                          | μA    | 1.8        | FVR current                        |  |

|                                 |                         | —                                                    | 8.5  | 26            | 33                                                                                                          | μA    | 3.0        |                                    |  |

| D025                            |                         |                                                      | 32   | 55            | 70                                                                                                          | μA    | 1.8        | FVR current (Note 4)               |  |

|                                 |                         |                                                      | 39   | 72            | 80                                                                                                          | μA    | 3.0        |                                    |  |

|                                 |                         | —                                                    | 70   | 100           | 110                                                                                                         | μA    | 5.0        |                                    |  |