Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

|                            |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1939-e-pt |

TABLE 3-9: PIC16(L)F1938/9 MEMORY MAP, BANK 31

|      |                                                             | Davids 04                    |  |  |  |  |  |

|------|-------------------------------------------------------------|------------------------------|--|--|--|--|--|

|      |                                                             | Bank 31                      |  |  |  |  |  |

|      | F8Ch                                                        |                              |  |  |  |  |  |

|      |                                                             | Unimplemented<br>Read as '0' |  |  |  |  |  |

|      | FE3h                                                        |                              |  |  |  |  |  |

|      | FE4h                                                        | STATUS_SHAD                  |  |  |  |  |  |

|      | FE5h                                                        | WREG_SHAD                    |  |  |  |  |  |

|      | FE6h                                                        | BSR_SHAD                     |  |  |  |  |  |

|      | FE7h                                                        | PCLATH_SHAD                  |  |  |  |  |  |

|      | FE8h                                                        | FSR0L_SHAD                   |  |  |  |  |  |

|      | FE9h                                                        | FSR0H_SHAD                   |  |  |  |  |  |

|      | FEAh                                                        | FSR1L_SHAD                   |  |  |  |  |  |

|      | FEBh                                                        | FSR1H_SHAD                   |  |  |  |  |  |

|      | FECh                                                        | _                            |  |  |  |  |  |

|      | FEDh                                                        | STKPTR                       |  |  |  |  |  |

|      | FEEh                                                        | TOSL                         |  |  |  |  |  |

|      | FEFh                                                        | TOSH                         |  |  |  |  |  |

| Lege | Legend: = Unimplemented data memory locations, read as '0'. |                              |  |  |  |  |  |

# 3.3.5 SPECIAL FUNCTION REGISTERS SUMMARY

The Special Function Register Summary for the device family are as follows:

| Device          | Bank(s) | Page No. |

|-----------------|---------|----------|

|                 | 0       | 32       |

|                 | 1       | 33       |

|                 | 2       | 34       |

|                 | 3       | 35       |

|                 | 4       | 36       |

|                 | 5       | 37       |

| PIC16(L)F1938/9 | 6       | 38       |

|                 | 7       | 39       |

|                 | 8       | 40       |

|                 | 9-14    | 41       |

|                 | 15      | 42       |

|                 | 16-30   | 44       |

|                 | 31      | 45       |

TABLE 3-10: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

|                                  |            |                                                                                                        |                                              |                |                 | •            |          | ,     |       |                      |                                 |

|----------------------------------|------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------|-----------------|--------------|----------|-------|-------|----------------------|---------------------------------|

| Address                          | Name       | Bit 7                                                                                                  | Bit 6                                        | Bit 5          | Bit 4           | Bit 3        | Bit 2    | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Banks 9                          | Banks 9-14 |                                                                                                        |                                              |                |                 |              |          |       |       |                      |                                 |

| x00h/<br>x80h <sup>(2)</sup>     | INDF0      | Addressing this location uses contents of FSR0H/FSR0L to address data memory (not a physical register) |                                              |                |                 |              |          |       |       | xxxx xxxx            | xxxx xxxx                       |

| x00h/<br>x81h <sup>(2)</sup>     | INDF1      | Addressing this location uses contents of FSR1H/FSR1L to address data memory (not a physical register) |                                              |                |                 |              |          |       |       | xxxx xxxx            | xxxx xxxx                       |

| x02h/<br>x82h <sup>(2)</sup>     | PCL        | Program Co                                                                                             | ounter (PC) L                                | east Significa | int Byte        |              |          |       |       | 0000 0000            | 0000 0000                       |

| x03h/<br>x83h <sup>(2)</sup>     | STATUS     | _                                                                                                      | _                                            | _              | TO              | PD           | Z        | DC    | С     | 1 1000               | q quuu                          |

| x04h/<br>x84h <sup>(2)</sup>     | FSR0L      | Indirect Data Memory Address 0 Low Pointer                                                             |                                              |                |                 |              |          |       |       | 0000 0000            | uuuu uuuu                       |

| x05h/<br>x85h <sup>(2)</sup>     | FSR0H      | Indirect Date                                                                                          | Indirect Data Memory Address 0 High Pointer  |                |                 |              |          |       |       | 0000 0000            | 0000 0000                       |

| x06h/<br>x86h <sup>(2)</sup>     | FSR1L      | Indirect Date                                                                                          | Indirect Data Memory Address 1 Low Pointer   |                |                 |              |          |       |       | 0000 0000            | uuuu uuuu                       |

| x07h/<br>x87h <sup>(2)</sup>     | FSR1H      | Indirect Date                                                                                          | ta Memory Ac                                 | ldress 1 High  | Pointer         |              |          |       |       | 0000 0000            | 0000 0000                       |

| x08h/<br>x88h <sup>(2)</sup>     | BSR        | _                                                                                                      | _                                            | _              |                 | I            | BSR<4:0> |       |       | 0 0000               | 0 0000                          |

| x09h/<br>x89h <sup>(2)</sup>     | WREG       | Working Re                                                                                             | egister                                      |                |                 |              |          |       |       | 0000 0000            | uuuu uuuu                       |

| x0Ah/<br>x8Ah <sup>(1),(2)</sup> | PCLATH     | _                                                                                                      | Write Buffer                                 | for the upper  | 7 bits of the F | Program Cour | nter     |       |       | -000 0000            | -000 0000                       |

| x0Bh/<br>x8Bh <sup>(2)</sup>     | INTCON     | GIE                                                                                                    | GIE PEIE TMR0IE INTE IOCIE TMR0IF INTF IOCIF |                |                 |              |          |       |       | 0000 0000            | 0000 0000                       |

| x0Ch/<br>x8Ch                    | _          | Unimplemented                                                                                          |                                              |                |                 |              |          |       | _     | _                    |                                 |

| x1Fh/<br>x9Fh                    |            |                                                                                                        |                                              |                |                 |              |          |       |       |                      |                                 |

**Legend:** x = unknown, u = unchanged, q = value depends on condition, -= unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

- 2: These registers can be addressed from any bank.

- 3: These registers/bits are not implemented on PIC16(L)F1938 devices, read as '0'.

- 4: Unimplemented, read as '1'.

#### 3.4 PCL and PCLATH

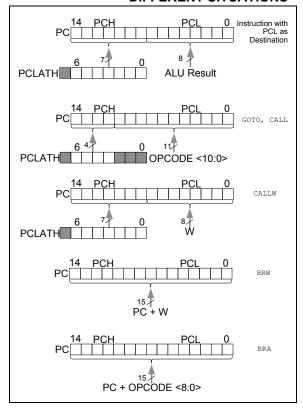

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-3 shows the five situations for the loading of the PC.

FIGURE 3-3: LOADING OF PC IN DIFFERENT SITUATIONS

### 3.4.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register and those being written to the PCL register.

#### 3.4.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to the Application Note AN556, "Implementing a Table Read" (DS00556).

#### 3.4.3 COMPUTED FUNCTION CALLS

A computed function <code>CALL</code> allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function <code>CALL</code>, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 3.4.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 +, the signed value of the operand of the BRA instruction.

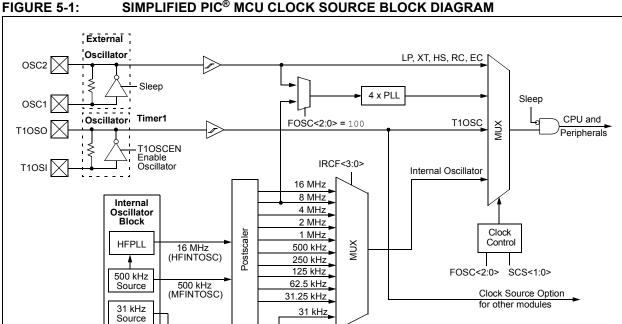

SIMPLIFIED PIC® MCU CLOCK SOURCE BLOCK DIAGRAM

31 kHz (LFINTOSC)

WDT, PWRT, Fail-Safe Clock Monitor

Two-Speed Start-up and other modules

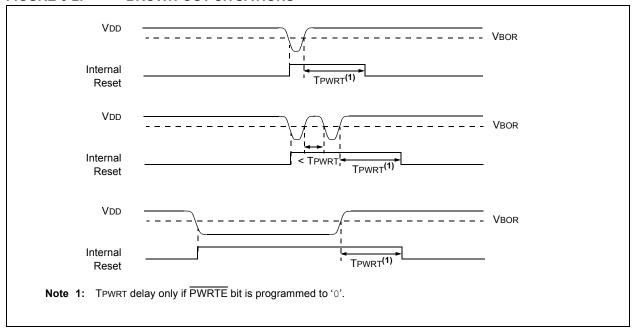

### FIGURE 6-2: BROWN-OUT SITUATIONS

# 6.3 Register Definitions: BOR Control

### REGISTER 6-1: BORCON: BROWN-OUT RESET CONTROL REGISTER

| R/W-1/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R-q/u  |

|---------|-----|-----|-----|-----|-----|-----|--------|

| SBOREN  | _   | _   | _   | _   | _   | _   | BORRDY |

| bit 7   | •   | •   | •   | •   | •   | •   | bit 0  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

bit 7 SBOREN: Software Brown-out Reset Enable bit

If BOREN <1:0> in Configuration Words ≠ 01:

SBOREN is read/write, but has no effect on the BOR.

If BOREN <1:0> in Configuration Words = 01:

1 = BOR Enabled

0 = BOR Disabled

bit 6-1 **Unimplemented:** Read as '0'

bit 0 BORRDY: Brown-out Reset Circuit Ready Status bit

1 = The Brown-out Reset circuit is active

0 = The Brown-out Reset circuit is inactive

TABLE 12-7: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Name       | Bit 7  | Bit 6   | Bit 5  | Bit 4   | Bit 3      | Bit 2    | Bit 1   | Bit 0   | Register on Page |

|------------|--------|---------|--------|---------|------------|----------|---------|---------|------------------|

| ADCON0     | _      |         |        | CHS<4:0 | >          |          | GO/DONE | ADON    | 155              |

| ANSELB     | _      | _       | ANSB5  | ANSB4   | ANSB3      | ANSB2    | ANSB1   | ANSB0   | 131              |

| APFCON     | _      | CCP3SEL | T1GSEL | P2BSEL  | SRNQSEL    | C2OUTSEL | SSSEL   | CCP2SEL | 123              |

| CCPxCON    | PxM<   | <1:0>   | DCxB   | <1:0>   |            | CCPxM<   | 3:0>    |         | 228              |

| CPSCON0    | CPSON  | CPSRM   | _      | _       | CPSRNG     | <1:0>    | CPSOUT  | T0XCS   | 321              |

| CPSCON1    | _      | _       | _      | _       |            | CPSCH-   | <3:>    |         | 322              |

| INTCON     | GIE    | PEIE    | TMR0IE | INTE    | IOCIE      | TMR0IF   | INTF    | IOCIF   | 90               |

| IOCBP      | IOCBP7 | IOCBP6  | IOCBP5 | IOCBP4  | IOCBP3     | IOCBP2   | IOCBP1  | IOCBP0  | 145              |

| IOCBN      | IOCBN7 | IOCBN6  | IOCBN5 | IOCBN4  | IOCBN3     | IOCBN2   | IOCBN1  | IOCBN0  | 145              |

| IOCBF      | IOCBF7 | IOCBF6  | IOCBF5 | IOCBF4  | IOCBF3     | IOCBF2   | IOCBF1  | IOCBF0  | 145              |

| LATB       | LATB7  | LATB6   | LATB5  | LATB4   | LATB3      | LATB2    | LATB1   | LATB0   | 130              |

| LCDCON     | LCDEN  | SLPEN   | WERR   | _       | CS<1:      | 0>       | LMUX    | <1:0>   | 327              |

| LCDSE0     | SE7    | SE6     | SE5    | SE4     | SE3        | SE2      | SE1     | SE0     | 331              |

| LCDSE1     | SE15   | SE14    | SE13   | SE12    | SE11       | SE10     | SE9     | SE8     | 331              |

| OPTION_REG | WPUEN  | INTEDG  | TMR0CS | TMR0SE  | PSA        |          | PS<2:0> |         | 187              |

| PORTB      | RB7    | RB6     | RB5    | RB4     | RB3        | RB2      | RB1     | RB0     | 130              |

| T1GCON     | TMR1GE | T1GPOL  | T1GTM  | T1GSPM  | T1GGO/DONE | T1GVAL   | T1GS    | S<1:0>  | 198              |

| TRISB      | TRISB7 | TRISB6  | TRISB5 | TRISB4  | TRISB3     | TRISB2   | TRISB1  | TRISB0  | 130              |

| WPUB       | WPUB7  | WPUB6   | WPUB5  | WPUB4   | WPUB3      | WPUB2    | WPUB1   | WPUB0   | 131              |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

### 18.2 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 registers (see Register 18-1) contain Control and Status bits for the following:

- Fnable

- · Output selection

- · Output polarity

- · Speed/Power selection

- · Hysteresis enable

- · Output synchronization

The CMxCON1 registers (see Register 18-2) contain Control bits for the following:

- · Interrupt enable

- · Interrupt edge polarity

- · Positive input channel selection

- · Negative input channel selection

#### 18.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

### 18.2.2 COMPARATOR OUTPUT SELECTION

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register. In order to make the output available for an external connection, the following conditions must be true:

- CxOE bit of the CMxCON0 register must be set

- · Corresponding TRIS bit must be cleared

- CxON bit of the CMxCON0 register must be set

- Note 1: The CxOE bit of the CMxCON0 register overrides the PORT data latch. Setting the CxON bit of the CMxCON0 register has no impact on the port override.

- 2: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### 18.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 18-1 shows the output state versus input conditions, including polarity control.

TABLE 18-1: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |

|-----------------|-------|-------|

| CxVn > CxVp     | 0     | 0     |

| CxVn < CxVp     | 0     | 1     |

| CxVn > CxVp     | 1     | 1     |

| CxVn < CxVp     | 1     | 0     |

# 18.2.4 COMPARATOR SPEED/POWER SELECTION

The trade-off between speed or power can be optimized during program execution with the CxSP control bit. The default state for this bit is '1' which selects the Normal speed mode. Device power consumption can be optimized at the cost of slower comparator propagation delay by clearing the CxSP bit to '0'.

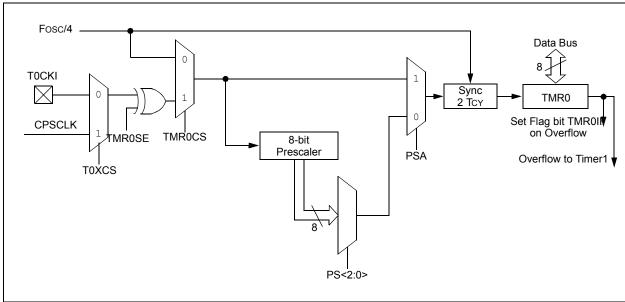

### 20.0 TIMERO MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (independent of Watchdog Timer)

- · Programmable internal or external clock source

- · Programmable external clock edge selection

- · Interrupt on overflow

- · TMR0 can be used to gate Timer1

Figure 20-1 is a block diagram of the Timer0 module.

### 20.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 20.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-bit Timer mode is selected by clearing the TMR0CS bit of the OPTION\_REG register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### 20.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin or the Capacitive Sensing Oscillator (CPSCLK) signal.

8-Bit Counter mode using the T0CKI pin is selected by setting the TMR0CS bit in the OPTION\_REG register to '1' and resetting the T0XCS bit in the CPSCON0 register to '0'.

8-Bit Counter mode using the Capacitive Sensing Oscillator (CPSCLK) signal is selected by setting the TMR0CS bit in the OPTION\_REG register to '1' and setting the T0XCS bit in the CPSCON0 register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the TMR0SE bit in the OPTION\_REG register.

#### FIGURE 20-1: BLOCK DIAGRAM OF THE TIMER0

The I<sup>2</sup>C interface supports the following modes and features:

- · Master mode

- · Slave mode

- · Byte NACKing (Slave mode)

- · Limited Multi-master support

- · 7-bit and 10-bit addressing

- · Start and Stop interrupts

- · Interrupt masking

- · Clock stretching

- · Bus collision detection

- · General call address matching

- · Address masking

- · Address Hold and Data Hold modes

- Selectable SDA hold times

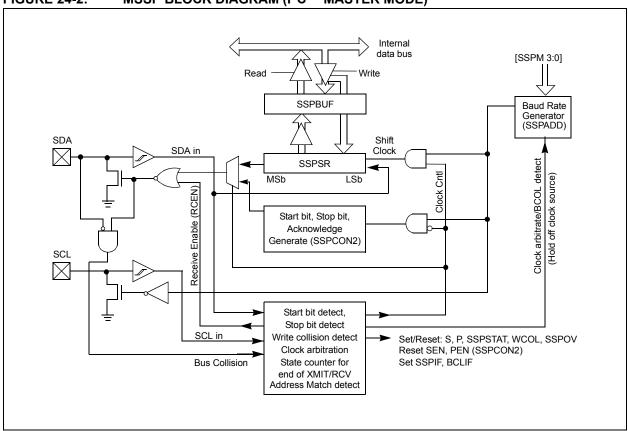

Figure 24-2 is a block diagram of the I<sup>2</sup>C Interface module in Master mode. Figure 24-3 is a diagram of the I<sup>2</sup>C Interface module in Slave mode.

FIGURE 24-2: MSSP BLOCK DIAGRAM (I<sup>2</sup>C™ MASTER MODE)

#### 24.2.6 SPI OPERATION IN SLEEP MODE

In SPI Master mode, module clocks may be operating at a different speed than when in Full-Power mode; in the case of the Sleep mode, all clocks are halted.

Special care must be taken by the user when the MSSP clock is much faster than the system clock.

In Slave mode, when MSSP interrupts are enabled, after the master completes sending data, an MSSP interrupt will wake the controller from Sleep.

If an exit from Sleep mode is not desired, MSSP interrupts should be disabled.

In SPI Master mode, when the Sleep mode is selected, all module clocks are halted and the transmission/reception will remain in that state until the device wakes. After the device returns to Run mode, the module will resume transmitting and receiving data.

In SPI Slave mode, the SPI Transmit/Receive Shift register operates asynchronously to the device. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the MSSP interrupt flag bit will be set and if enabled, will wake the device.

TABLE 24-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

| Name    | Bit 7       | Bit 6           | Bit 5           | Bit 4         | Bit 3   | Bit 2    | Bit 1  | Bit 0   | Register on Page |

|---------|-------------|-----------------|-----------------|---------------|---------|----------|--------|---------|------------------|

| ANSELA  | _           | _               | ANSA5           | ANSA4         | ANSA3   | ANSA2    | ANSA1  | ANSA0   | 126              |

| APFCON  | _           | CCP3SEL         | T1GSEL          | P2BSEL        | SRNQSEL | C2OUTSEL | SSSEL  | CCP2SEL | 123              |

| INTCON  | GIE         | PEIE            | TMR0IE          | INTE          | IOCIE   | TMR0IF   | INTF   | IOCIF   | 90               |

| PIE1    | TMR1GIE     | ADIE            | RCIE            | TXIE          | SSP1IE  | CCP1IE   | TMR2IE | TMR1IE  | 91               |

| PIR1    | TMR1GIF     | ADIF            | RCIF            | TXIF          | SSP1IF  | CCP1IF   | TMR2IF | TMR1IF  | 94               |

| SSPBUF  | Synchronous | s Serial Port F | Receive Buffe   | r/Transmit Re | egister |          |        |         | 239*             |

| SSPCON1 | WCOL        | SSPOV           | SSPEN           | CKP           |         | SSPM     | <3:0>  |         | 283              |

| SSPCON3 | ACKTIM      | PCIE            | SCIE            | BOEN          | SDAHT   | SBCDE    | AHEN   | DHEN    | 285              |

| SSPSTAT | SMP         | CKE             | D/ <del>A</del> | Р             | S       | R/W      | UA     | BF      | 282              |

| TRISA   | TRISA7      | TRISA6          | TRISA5          | TRISA4        | TRISA3  | TRISA2   | TRISA1 | TRISA0  | 125              |

| TRISC   | TRISC7      | TRISC6          | TRISC5          | TRISC4        | TRISC3  | TRISB2   | TRISC1 | TRISC0  | 134              |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the MSSP in SPI mode.

<sup>\*</sup> Page provides register information.

TABLE 24-3: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C™ OPERATION

| Name    | Bit 7     | Bit 6          | Bit 5           | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0                 | Reset<br>Values on<br>Page: |

|---------|-----------|----------------|-----------------|--------|--------|--------|--------|-----------------------|-----------------------------|

| INTCON  | GIE       | PEIE           | TMR0IE          | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF                 | 90                          |

| PIE1    | TMR1GIE   | ADIE           | RCIE            | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE                | 91                          |

| PIE2    | OSFIE     | C2IE           | C1IE            | EEIE   | BCLIE  | _      | _      | CCP2IE <sup>(1)</sup> | 92                          |

| PIR1    | TMR1GIF   | ADIF           | RCIF            | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF                | 94                          |

| PIR2    | OSFIF     | C2IF           | C1IF            | EEIF   | BCLIF  | _      | _      | CCP2IF <sup>(1)</sup> | 95                          |

| SSPADD  |           |                |                 | ADD<   | 7:0>   |        |        |                       | 286                         |

| SSPBUF  | MSSP Rece | ive Buffer/Tra | nsmit Registe   | r      |        |        |        |                       | 239*                        |

| SSPCON1 | WCOL      | SSPOV          | SSPEN           | CKP    |        | SSPM   | <3:0>  |                       | 283                         |

| SSPCON2 | GCEN      | ACKSTAT        | ACKDT           | ACKEN  | RCEN   | PEN    | RSEN   | SEN                   | 284                         |

| SSPCON3 | ACKTIM    | PCIE           | SCIE            | BOEN   | SDAHT  | SBCDE  | AHEN   | DHEN                  | 285                         |

| SSPMSK  |           |                |                 | MSK<   | :7:0>  |        |        |                       | 286                         |

| SSPSTAT | SMP       | CKE            | D/ <del>A</del> | Р      | S      | R/W    | UA     | BF                    | 282                         |

| TRISC   | TRISC7    | TRISC6         | TRISC5          | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0                | 134                         |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by the MSSP module in  $I^2C^{TM}$  mode.

\* Page provides register information.

**Note 1:** PIC16F1934 only.

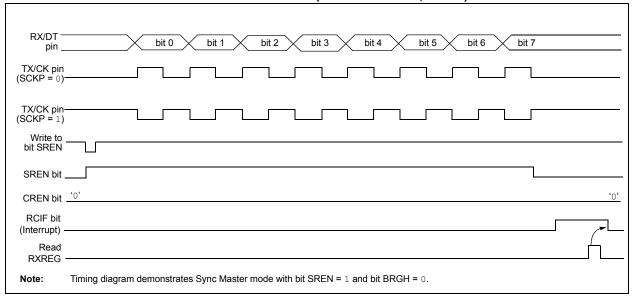

TABLE 25-8: SUMMARY OF REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Name    | Bit 7    | Bit 6      | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register on Page |

|---------|----------|------------|------------|--------|--------|--------|--------|--------|------------------|

| BAUDCON | ABDOVF   | RCIDL      | _          | SCKP   | BRG16  | _      | WUE    | ABDEN  | 298              |

| INTCON  | GIE      | PEIE       | TMR0IE     | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 90               |

| PIE1    | TMR1GIE  | ADIE       | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 91               |

| PIR1    | TMR1GIF  | ADIF       | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 94               |

| RCREG   | EUSART R | eceive Dat | a Register |        |        |        |        |        | 292*             |

| RCSTA   | SPEN     | RX9        | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 297              |

| SPBRGL  |          |            |            | BRG-   | <7:0>  |        |        |        | 299*             |

| SPBRGH  |          |            |            | BRG<   | :15:8> |        |        |        | 299*             |

| TRISC   | TRISC7   | TRISC6     | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 134              |

| TXSTA   | CSRC     | TX9        | TXEN       | SYNC   | SENDB  | BRGH   | TRMT   | TX9D   | 296              |

**Legend:** — = unimplemented location read as '0'. Shaded cells are not used for synchronous master reception.

<sup>\*</sup> Page provides register information.

#### REGISTER 26-2: CPSCON1: CAPACITIVE SENSING CONTROL REGISTER 1

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 <sup>(2)</sup> | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|------------------------|---------|---------|---------|

| _     | _   | _   | _   |                        | CPSCI   | H<3:0>  |         |

| bit 7 |     |     |     |                        |         | _       | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-4 **Unimplemented:** Read as '0'

bit 3-0 CPSCH<3:0>: Capacitive Sensing Channel Select bits

If CPSON = 0:

These bits are ignored. No channel is selected.

If CPSON = 1:

0000 = channel 0, (CPS0)

0001 = channel 1, (CPS1)

0010 = channel 2, (CPS2) 0011 = channel 3, (CPS3)

0100 = channel 4, (CPS4)

0101 = channel 5, (CPS5)

0110 = channel 6, (CPS6)

0111 = channel 7, (CPS7)

$1000 = \text{channel 8, (CPS8}^{(1)})$

$1001 = \text{channel 9, (CPS9}^{(1)})$

1010 = channel 10, (CPS10<sup>(1)</sup>)

1011 = channel 11, (CPS11(1))

1100 = channel 12, (CPS12<sup>(1)</sup>)

1101 = channel 13, (CPS13 $^{(1)}$ )

1110 = channel 14, (CPS14<sup>(1)</sup>) 1111 = channel 15, (CPS15<sup>(1)</sup>)

Note 1: These channels are not implemented on the PIC16(L)F1938.

2: This bit is not implemented on PIC16(L)F1938, read as '0'

### 27.6 LCD Multiplex Types

The LCD Driver module can be configured into one of four multiplex types:

- Static (only COM0 is used)

- 1/2 multiplex (COM<1:0> are used)

- 1/3 multiplex (COM<2:0> are used)

- 1/4 multiplex (COM<3:0> are used)

The LMUX<1:0> bit setting of the LCDCON register decides which of the LCD common pins are used (see Table 27-4 for details).

If the pin is a digital I/O, the corresponding TRIS bit controls the data direction. If the pin is a COM drive, then the TRIS setting of that pin is overridden.

TABLE 27-4: COMMON PIN USAGE

| Multiplex | LMUX<br><1:0> | СОМЗ   | COM2   | COM1   |

|-----------|---------------|--------|--------|--------|

| Static    | 00            | Unused | Unused | Unused |

| 1/2       | 01            | Unused | Unused | Active |

| 1/3       | 10            | Unused | Active | Active |

| 1/4       | 11            | Active | Active | Active |

### 27.7 Segment Enables

The LCDSEn registers are used to select the pin function for each segment pin. The selection allows each pin to operate as either an LCD segment driver or as one of the pin's alternate functions. To configure the pin as a segment pin, the corresponding bits in the LCDSEn registers must be set to '1'.

If the pin is a digital I/O, the corresponding TRIS bit controls the data direction. Any bit set in the LCDSEn registers overrides any bit settings in the corresponding TRIS register.

**Note:** On a Power-on Reset, these pins are configured as normal I/O, not LCD pins.

#### 27.8 Pixel Control

The LCDDATAx registers contain bits which define the state of each pixel. Each bit defines one unique pixel.

Register 27-6 shows the correlation of each bit in the LCDDATAx registers to the respective common and segment signals.

Any LCD pixel location not being used for display can be used as general purpose RAM.

### 27.9 LCD Frame Frequency

The rate at which the COM and SEG outputs change is called the LCD frame frequency.

TABLE 27-5: FRAME FREQUENCY FORMULAS

| Multiplex | Frame Frequency =                            |

|-----------|----------------------------------------------|

| Static    | Clock source/(4 x 1 x (LCD Prescaler) x 32)) |

| 1/2       | Clock source/(2 x 2 x (LCD Prescaler) x 32)) |

| 1/3       | Clock source/(1 x 3 x (LCD Prescaler) x 32)) |

| 1/4       | Clock source/(1 x 4 x (LCD Prescaler) x 32)) |

Note: Clock source is Fosc/256, T1OSC or LFINTOSC.

TABLE 27-6: APPROXIMATE FRAME FREQUENCY (IN Hz) USING Fosc @ 8 MHz, TIMER1 @ 32.768 kHz OR LFINTOSC

| LP<3:0> | Static | 1/2 | 1/3 | 1/4 |

|---------|--------|-----|-----|-----|

| 2       | 122    | 122 | 162 | 122 |

| 3       | 81     | 81  | 108 | 81  |

| 4       | 61     | 61  | 81  | 61  |

| 5       | 49     | 49  | 65  | 49  |

| 6       | 41     | 41  | 54  | 41  |

| 7       | 35     | 35  | 47  | 35  |

TABLE 30-5: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET

Standard Operating Conditions (unless otherwise stated) Operating Temperature -40°C ≤ TA ≤ +125°C Param Sym. Characteristic Min. Typ† Max. Units **Conditions** No. MCLR Pulse Width (low) 30 **TMCL** 2 μS 31 **TWDTLP** Low-Power Watchdog Timer 10 16 27 ms VDD = 3.3V-5VTime-out Period 1:16 Prescaler used 32 Tost Oscillator Start-up Timer Period<sup>(1)</sup> 1024 Tosc Power-up Timer Period, PWRTE = 0 33\* **TPWRT** 40 65 140 ms 34\* Tioz I/O high-impedance from MCLR Low 2.0 μS or Watchdog Timer Reset **V**BOR Brown-out Reset Voltage<sup>(2)</sup> 35 2.55 BORV = 0 2.7 2.85 ٧ 1.80 BORV = 11.9 2.11 ٧ 36\* **VHYST** Brown-out Reset Hysteresis 20 35 60 -40°C to +85°C mV 37\* **TBORDC** Brown-out Reset DC Response 1 3 35  $VDD \leq VBOR$ μS Time

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: By design, the Oscillator Start-up Timer (OST) counts the first 1024 cycles, independent of frequency.

- 2: To ensure these voltage tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible.  $0.1~\mu F$  and  $0.01~\mu F$  values in parallel are recommended.

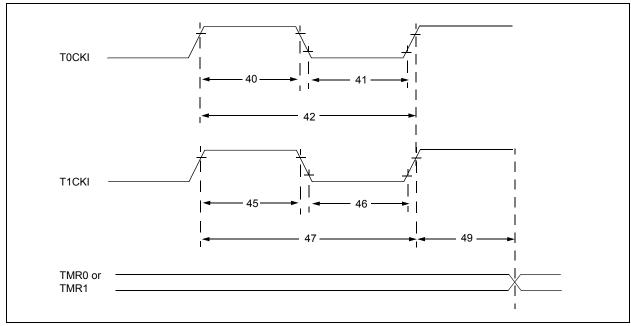

FIGURE 30-10: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

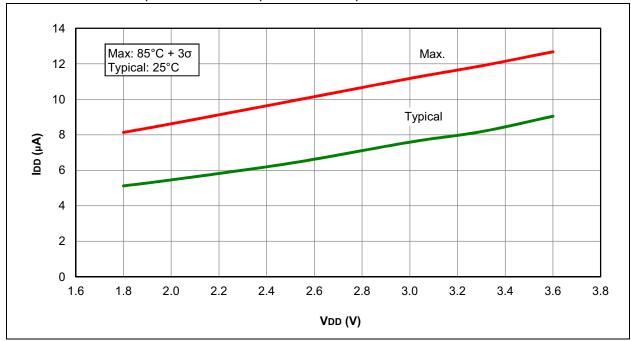

FIGURE 31-1: IDD, LP OSCILLATOR, FOSC = 32 kHz, PIC16LF1938/9 ONLY

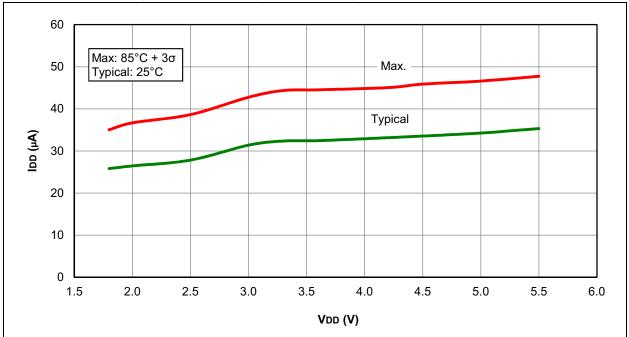

FIGURE 31-2: IDD, LP OSCILLATOR, Fosc = 32 kHz, PIC16F1938/9 ONLY

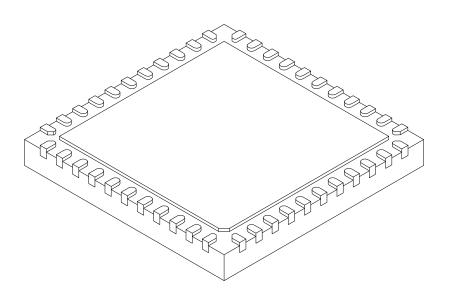

# 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                   |        | MILLIMETERS |      |      |

|-------------------------|--------|-------------|------|------|

| Dimension               | Limits | MIN         | NOM  | MAX  |

| Number of Pins          | N      | 44          |      |      |

| Pitch                   | е      | 0.65 BSC    |      |      |

| Overall Height          | Α      | 0.80        | 0.90 | 1.00 |

| Standoff                | A1     | 0.00        | 0.02 | 0.05 |

| Terminal Thickness      | A3     | 0.20 REF    |      |      |

| Overall Width           | Е      | 8.00 BSC    |      |      |

| Exposed Pad Width       | E2     | 6.25        | 6.45 | 6.60 |

| Overall Length          | О      | 8.00 BSC    |      |      |

| Exposed Pad Length      | D2     | 6.25        | 6.45 | 6.60 |

| Terminal Width          | b      | 0.20        | 0.30 | 0.35 |

| Terminal Length         | L      | 0.30        | 0.40 | 0.50 |

| Terminal-to-Exposed-Pad | K      | 0.20        | -    | -    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension. usually without tolerance. for information purposes only.

Microchip Technology Drawing C04-103C Sheet 2 of 2

# APPENDIX A: DATA SHEET REVISION HISTORY

## Revision A (05/2011)

Original release of this data sheet.

### **Revision B (02/2012)**

Added new Family Types table; Updated Register 4-3; Added DC and AC Characteristics Graphs; Updated the Electrical Specifications section; Updated the Packaging Information section; Other minor corrections.

### **Revision C (06/2013)**

Revised Data Sheet to Final status.

# APPENDIX B: MIGRATING FROM OTHER PIC® DEVICES

This discusses some of the issues in migrating from other PIC<sup>®</sup> devices to the PIC16(L)F193X family of devices.

# B.1 PIC16F917 to PIC16(L)F193X TABLE B-1: FEATURE COMPARISON

| Feature                               | PIC16F917         | PIC16F1938          |

|---------------------------------------|-------------------|---------------------|

| Max. Operating Speed                  | 20 MHz            | 32 MHz              |

| Max. Program<br>Memory (Words)        | 8K                | 8K                  |

| Max. SRAM (Bytes)                     | 368               | 512                 |

| A/D Resolution                        | 10-bit            | 10-bit              |

| Timers (8/16-bit)                     | 2/1               | 4/1                 |

| Oscillator Modes                      | 4                 | 8                   |

| Brown-out Reset                       | Υ                 | Y                   |

| Internal Pull-ups                     | RB<7:0>           | RB<7:0>             |

| Interrupt-on-change                   | RB<7:4>           | RB<7:0>             |

| Comparator                            | 2                 | 2                   |

| AUSART/EUSART                         | 1/0               | 0/1                 |

| Extended WDT                          | Y                 | Y                   |

| Software Control<br>Option of WDT/BOR | N                 | Y                   |

| INTOSC Frequencies                    | 30 kHz -<br>8 MHz | 500 kHz -<br>32 MHz |

| Clock Switching                       | Y                 | Y                   |

| Capacitive Sensing                    | N                 | Y                   |

| CCP/ECCP                              | 2/0               | 2/3                 |

| Enhanced PIC16 CPU                    | N                 | Y                   |

| MSSP/SSP                              | 0/1               | 1/0                 |

| LCD                                   | Y                 | Y                   |

| CCP1CON Register                                | 37, 38  | Industrial and Extended (PIC16(L)F1938/9)    |       |

|-------------------------------------------------|---------|----------------------------------------------|-------|

| CCPR1H Register                                 | 37, 38  | Development Support                          | . 445 |

| CCPR1L Register                                 | 37, 38  | Device Configuration                         | 53    |

| CCPTMRS0 Register                               |         | Code Protection                              |       |

| CCPTMRS1 Register                               |         | Configuration Word                           |       |

| CCPxAS Register                                 |         | User ID5                                     |       |

| CCPxCON (ECCPx) Register                        |         | Device Overview                              |       |

| Clock Accuracy with Asynchronous Operation      |         | Digital-to-Analog Converter (DAC)            | -     |

|                                                 | 290     |                                              |       |

| Clock Sources                                   | 0.4     | Effects of a Reset                           |       |

| External Modes                                  |         | Specifications                               | . 400 |

| EC                                              |         | E                                            |       |

| HS                                              |         | _                                            |       |

| LP                                              | 61      | ECCP/CCP. See Enhanced Capture/Compare/PWM   |       |

| OST                                             | 62      | EEADR Registers                              | . 107 |

| RC                                              | 63      | EEADRH Registers                             | . 107 |

| XT                                              | 61      | EEADRL Register                              | . 118 |

| Internal Modes                                  | 64      | EEADRL Registers                             | . 107 |

| HFINTOSC                                        |         | EECON1 Register107                           |       |

| Internal Oscillator Clock Switch Timing         |         | EECON2 Register107                           |       |

| LFINTOSC                                        |         | EEDATH Register                              |       |

|                                                 |         | EEDATL Register                              |       |

| MFINTOSC                                        |         |                                              | . 110 |

| Clock Switching                                 |         | EEPROM Data Memory                           | 400   |

| CMOUT Register                                  |         | Avoiding Spurious Write                      |       |

| CMxCON0 Register                                |         | Write Verify                                 | . 117 |

| CMxCON1 Register                                | 176     | Effects of Reset                             |       |

| Code Examples                                   |         | PWM mode                                     | . 213 |

| A/D Conversion                                  | 154     | Electrical Specifications (PIC16(L)F1938/9)  | . 377 |

| Changing Between Capture Prescalers             | 206     | Enhanced Capture/Compare/PWM (ECCP)          | . 205 |

| Initializing PORTA                              |         | Enhanced PWM Mode                            | . 214 |

| Initializing PORTE                              |         | Auto-Restart                                 | . 223 |

| Write Verify                                    |         | Auto-shutdown                                |       |

| Writing to Flash Program Memory                 |         | Direction Change in Full-Bridge Output Mode. |       |

|                                                 | 113     | Full-Bridge Application                      |       |

| Comparator                                      | 477 470 |                                              |       |

| Associated Registers                            |         | Full-Bridge Mode                             |       |

| Operation                                       |         | Half-Bridge Application                      |       |

| Comparator Module                               |         | Half-Bridge Application Examples             |       |

| Cx Output State Versus Input Conditions         | 171     | Half-Bridge Mode                             | . 217 |

| Comparator Specifications                       | 400     | Output Relationships (Active-High and        |       |

| Comparators                                     |         | Active-Low)                                  | . 215 |

| C2OUT as T1 Gate                                | 191     | Output Relationships Diagram                 | . 216 |

| Compare Module. See Enhanced Capture/           |         | Programmable Dead Band Delay                 | . 224 |

| Compare/PWM (ECCP)                              |         | Shoot-through Current                        | . 224 |

| CONFIG1 Register                                | 54      | Start-up Considerations                      |       |

| CONFIG2 Register                                |         | Specifications                               |       |

| Core Registers                                  |         | Enhanced Mid-range CPU                       |       |

|                                                 |         | Enhanced Universal Synchronous Asynchronous  | 10    |

| CPSCONI Register                                |         | Receiver Transmitter (EUSART)                | 297   |

| CPSCON1 Register                                |         | , ,                                          |       |

| Customer Change Notification Service            |         | Errata                                       |       |

| Customer Notification Service                   |         | EUSART                                       | . 287 |

| Customer Support                                | 483     | Associated Registers                         |       |

| D                                               |         | Baud Rate Generator                          |       |

| D                                               |         | Asynchronous Mode                            |       |

| DACCON0 (Digital-to-Analog Converter Control 0) |         | 12-bit Break Transmit and Receive            | . 307 |

| Register                                        | 168     | Associated Registers                         |       |

| DACCON1 (Digital-to-Analog Converter Control 1) |         | Receive                                      | . 295 |

| Register                                        | 168     | Transmit                                     |       |

| Data EEPROM Memory                              |         | Auto-Wake-up on Break                        |       |

| Associated Registers                            |         | Baud Rate Generator (BRG)                    |       |

| <u> </u>                                        |         |                                              |       |

| Code Protection                                 |         | Clock Accuracy                               |       |

| Reading                                         |         | Receiver                                     |       |

| Writing                                         |         | Setting up 9-bit Mode with Address Detect    |       |

| Data Memory                                     |         | Transmitter                                  | . 289 |

| DC and AC Characteristics                       | 409     | Baud Rate Generator (BRG)                    |       |

| Graphs and Tables                               | 409     | Auto Baud Rate Detect                        |       |

| DC Characteristics                              |         | Baud Rate Error, Calculating                 |       |

| Extended and Industrial (PIC16(L)F1938/9)       | 387     | Baud Rates, Asynchronous Modes               |       |