Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LCD, POR, PWM, WDT                                 |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 28KB (16K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 14x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1939-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

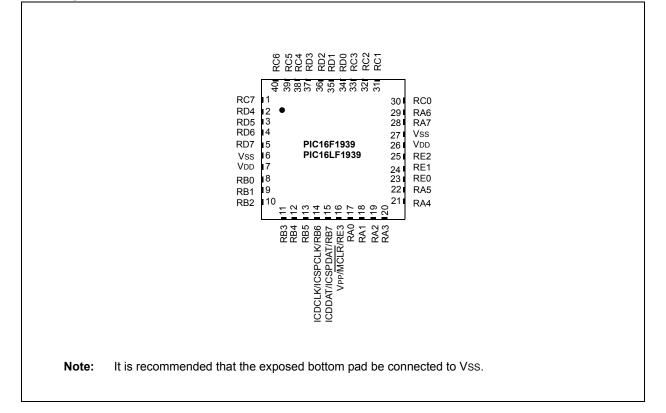

### Pin Diagram – 40-Pin PDIP

| VPP/MCLR/RE3 | 1          |                                              |

|--------------|------------|----------------------------------------------|

| RA0          | 2          |                                              |

| RA1          | 3          | 38 RB5                                       |

| RA2          | 4          | 37 RB4                                       |

| RA3          | 5          | 36 RB3                                       |

| RA4          | 6          | 35 RB2                                       |

| RA5          | 7          | 34 RB1                                       |

| RE0          | 8          | 33 RB0                                       |

| RE1          | 939 6      | 32     VDD       31     Vss       30     RD7 |

| RE2          | PIC16F1939 | 31 □ Vss                                     |

| VDD          | 11 5       | <u>5</u> 30 ∏ RD7                            |

| Vss          | 12 6       | • 29 RD6                                     |

| RA7          | 13         | 28 RD5                                       |

| RA6          | 14         | 27 RD4                                       |

| RC0          | 15         | 26 RC7                                       |

| RC1          | 16         | 25 RC6                                       |

| RC2          | 17         | 24 RC5                                       |

| RC3          | 18         | 23 RC4                                       |

| RD0          | 19         | 22 RD3                                       |

| RD1          | 20         | 21 RD2                                       |

|              | L          |                                              |

|              |            |                                              |

Pin Diagram – 40-Pin UQFN 5x5

#### **TABLE 1-2:** PIC16(L)F1938/9 PINOUT DESCRIPTION (CONTINUED)

| Name                                  | Function | Input<br>Type    | Output<br>Type | Description                          |

|---------------------------------------|----------|------------------|----------------|--------------------------------------|

| RC4/SDI/SDA/T1G <sup>(1)</sup> /SEG11 | RC4      | ST               | CMOS           | General purpose I/O.                 |

|                                       | SDI      | ST               | —              | SPI data input.                      |

|                                       | SDA      | l <sup>2</sup> C | OD             | I <sup>2</sup> C™ data input/output. |

|                                       | T1G      | ST               | —              | Timer1 Gate input.                   |

|                                       | SEG11    | _                | AN             | LCD Analog output.                   |

| RC5/SDO/SEG10                         | RC5      | ST               | CMOS           | General purpose I/O.                 |

|                                       | SDO      |                  | CMOS           | SPI data output.                     |

|                                       | SEG10    |                  | AN             | LCD Analog output.                   |

| RC6/TX/CK/CCP3/P3A/SEG9               | RC6      | ST               | CMOS           | General purpose I/O.                 |

|                                       | TX       |                  | CMOS           | USART asynchronous transmit.         |

|                                       | СК       | ST               | CMOS           | USART synchronous clock.             |

|                                       | CCP3     | ST               | CMOS           | Capture/Compare/PWM3.                |

|                                       | P3A      |                  | CMOS           | PWM output.                          |

|                                       | SEG9     |                  | AN             | LCD Analog output.                   |

| RC7/RX/DT/P3B/SEG8                    | RC7      | ST               | CMOS           | General purpose I/O.                 |

|                                       | RX       | ST               | —              | USART asynchronous input.            |

|                                       | DT       | ST               | CMOS           | USART synchronous data.              |

|                                       | P3B      | _                | CMOS           | PWM output.                          |

|                                       | SEG8     |                  | AN             | LCD Analog output.                   |

| RD0 <sup>(4)</sup> /CPS8/COM3         | RD0      | ST               | CMOS           | General purpose I/O.                 |

|                                       | CPS8     | AN               |                | Capacitive sensing input 8.          |

|                                       | COM3     |                  | AN             | LCD analog output.                   |

| RD1 <sup>(4)</sup> /CPS9/CCP4         | RD1      | ST               | CMOS           | General purpose I/O.                 |

|                                       | CPS9     | AN               |                | Capacitive sensing input 9.          |

|                                       | CCP4     | ST               | CMOS           | Capture/Compare/PWM4.                |

| RD2 <sup>(4)</sup> /CPS10/P2B         | RD2      | ST               | CMOS           | General purpose I/O.                 |

|                                       | CPS10    | AN               | _              | Capacitive sensing input 10.         |

|                                       | P2B      |                  | CMOS           | PWM output.                          |

| RD3 <sup>(4)</sup> /CPS11/P2C/SEG16   | RD3      | ST               | CMOS           | General purpose I/O.                 |

|                                       | CPS11    | AN               | -              | Capacitive sensing input 11.         |

|                                       | P2C      |                  | CMOS           | PWM output.                          |

|                                       | SEG16    | _                | AN             | LCD analog output.                   |

| RD4 <sup>(4)</sup> /CPS12/P2D/SEG17   | RD4      | ST               | CMOS           | General purpose I/O.                 |

|                                       | CPS12    | AN               | —              | Capacitive sensing input 12.         |

|                                       | P2D      | _                | CMOS           | PWM output.                          |

|                                       | SEG17    | _                | AN             | LCD analog output.                   |

| RD5 <sup>(4)</sup> /CPS13/P1B/SEG18   | RD5      | ST               | CMOS           | General purpose I/O.                 |

|                                       | CPS13    | AN               | _              | Capacitive sensing input 13.         |

|                                       | P1D      | _                | CMOS           | PWM output.                          |

|                                       | SEG18    | _                | AN             | LCD analog output.                   |

Legend: AN = Analog input or output CMOS = CMOS compatible input or output OD = Open Drain with CMOS levels XTAL = Crystal TTL = TTL compatible i

IIL = IIL compatible input SI = Schmitt Trigger input

HV = High Voltage

$$I^2C^{TM}$$

= Schmitt Trigger input

$I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$  levels

Note 1: Pin function is selectable via the APFCON register.

- 2: PIC16F1938/9 devices only.

- 3: PIC16(L)F1938 devices only.

- 4: PORTD is available on PIC16(L)F1939 devices only.

5: RE<2:0> are available on PIC16(L)F1939 devices only.

### TABLE 3-6: PIC16(L)F1938/9 MEMORY MAP, BANKS 24-31

|              | BANK 24                      |              | BANK 25                      |              | BANK 26                      |              | BANK 27                      |              | BANK 28                      |              | BANK 29                      |              | BANK 30                      |              | BANK 31               |

|--------------|------------------------------|--------------|------------------------------|--------------|------------------------------|--------------|------------------------------|--------------|------------------------------|--------------|------------------------------|--------------|------------------------------|--------------|-----------------------|

| C00h         | INDF0                        | C80h         | INDF0                        | D00h         | INDF0                        | D80h         | INDF0                        | E00h         | INDF0                        | E80h         | INDF0                        | F00h         | INDF0                        | F80h         | INDF0                 |

| C01h         | INDF1                        | C81h         | INDF1                        | D01h         | INDF1                        | D81h         | INDF1                        | E01h         | INDF1                        | E81h         | INDF1                        | F01h         | INDF1                        | F81h         | INDF1                 |

| C02h         | PCL                          | C82h         | PCL                          | D02h         | PCL                          | D82h         | PCL                          | E02h         | PCL                          | E82h         | PCL                          | F02h         | PCL                          | F82h         | PCL                   |

| C03h         | STATUS                       | C83h         | STATUS                       | D03h         | STATUS                       | D83h         | STATUS                       | E03h         | STATUS                       | E83h         | STATUS                       | F03h         | STATUS                       | F83h         | STATUS                |

| C04h         | FSR0L                        | C84h         | FSR0L                        | D04h         | FSR0L                        | D84h         | FSR0L                        | E04h         | FSR0L                        | E84h         | FSR0L                        | F04h         | FSR0L                        | F84h         | FSR0L                 |

| C05h         | FSR0H                        | C85h         | FSR0H                        | D05h         | FSR0H                        | D85h         | FSR0H                        | E05h         | FSR0H                        | E85h         | FSR0H                        | F05h         | FSR0H                        | F85h         | FSR0H                 |

| C06h         | FSR1L                        | C86h         | FSR1L                        | D06h         | FSR1L                        | D86h         | FSR1L                        | E06h         | FSR1L                        | E86h         | FSR1L                        | F06h         | FSR1L                        | F86h         | FSR1L                 |

| C07h         | FSR1H                        | C87h         | FSR1H                        | D07h         | FSR1H                        | D87h         | FSR1H                        | E07h         | FSR1H                        | E87h         | FSR1H                        | F07h         | FSR1H                        | F87h         | FSR1H                 |

| C08h         | BSR                          | C88h         | BSR                          | D08h         | BSR                          | D88h         | BSR                          | E08h         | BSR                          | E88h         | BSR                          | F08h         | BSR                          | F88h         | BSR                   |

| C09h         | WREG                         | C89h         | WREG                         | D09h         | WREG                         | D89h         | WREG                         | E09h         | WREG                         | E89h         | WREG                         | F09h         | WREG                         | F89h         | WREG                  |

| C0Ah         | PCLATH                       | C8Ah         | PCLATH                       | D0Ah         | PCLATH                       | D8Ah         | PCLATH                       | E0Ah         | PCLATH                       | E8Ah         | PCLATH                       | F0Ah         | PCLATH                       | F8Ah         | PCLATH                |

| C0Bh         | INTCON                       | C8Bh         | INTCON                       | D0Bh         | INTCON                       | D8Bh         | INTCON                       | E0Bh         | INTCON                       | E8Bh         | INTCON                       | F0Bh         | INTCON                       | F8Bh         | INTCON                |

| C0Ch         | _                            | C8Ch         | —                            | D0Ch         |                              | D8Ch         | —                            | E0Ch         |                              | E8Ch         | _                            | F0Ch         | _                            | F8Ch         |                       |

| C0Dh         | _                            | C8Dh         | —                            | D0Dh         |                              | D8Dh         | —                            | E0Dh         |                              | E8Dh         | _                            | F0Dh         | _                            | F8Dh         |                       |

| C0Eh         | _                            | C8Eh         | —                            | D0Eh         |                              | D8Eh         | —                            | E0Eh         |                              | E8Eh         |                              | F0Eh         | _                            | F8Eh         |                       |

| C0Fh         | _                            | C8Fh         | —                            | D0Fh         |                              | D8Fh         | —                            | E0Fh         |                              | E8Fh         |                              | F0Fh         | _                            | F8Fh         |                       |

| C10h         | _                            | C90h         | —                            | D10h         |                              | D90h         | —                            | E10h         |                              | E90h         |                              | F10h         | _                            | F90h         |                       |

| C11h         | _                            | C91h         | —                            | D11h         |                              | D91h         | —                            | E11h         |                              | E91h         | _                            | F11h         | _                            | F91h         |                       |

| C12h         | —                            | C92h         | —                            | D12h         | _                            | D92h         | —                            | E12h         | —                            | E92h         | —                            | F12h         | —                            | F92h         |                       |

| C13h         | —                            | C93h         | —                            | D13h         | _                            | D93h         | —                            | E13h         | —                            | E93h         | —                            | F13h         | —                            | F93h         |                       |

| C14h         | —                            | C94h         | —                            | D14h         | _                            | D94h         | —                            | E14h         | —                            | E94h         | —                            | F14h         | —                            | F94h         |                       |

| C15h         | —                            | C95h         | —                            | D15h         | _                            | D95h         | —                            | E15h         | _                            | E95h         | _                            | F15h         | —                            | F95h         |                       |

| C16h         | —                            | C96h         | _                            | D16h         | _                            | D96h         | —                            | E16h         | _                            | E96h         | _                            | F16h         | —                            | F96h         |                       |

| C17h         | —                            | C97h         | _                            | D17h         | _                            | D97h         | —                            | E17h         | _                            | E97h         | _                            | F17h         | —                            | F97h         |                       |

| C18h         | —                            | C98h         | _                            | D18h         | _                            | D98h         | —                            | E18h         | _                            | E98h         | —                            | F18h         | —                            | F98h         | See Table 3-9         |

| C19h         | —                            | C99h         | _                            | D19h         | _                            | D99h         | _                            | E19h         | _                            | E99h         | —                            | F19h         | —                            | F99h         |                       |

| C1Ah         | —                            | C9Ah         | _                            | D1Ah         |                              | D9Ah         | _                            | E1Ah         |                              | E9Ah         |                              | F1Ah         | —                            | F9Ah         |                       |

| C1Bh         | —                            | C9Bh         | _                            | D1Bh         | —                            | D9Bh         | _                            | E1Bh         | _                            | E9Bh         | —                            | F1Bh         | —                            | F9Bh         |                       |

| C1Ch         | —                            | C9Ch         | _                            | D1Ch         | _                            | D9Ch         | —                            | E1Ch         | _                            | E9Ch         | —                            | F1Ch         | —                            | F9Ch         |                       |

| C1Dh         | —                            | C9Dh         | —                            | D1Dh         | —                            | D9Dh         | —                            | E1Dh         | _                            | E9Dh         | —                            | F1Dh         | —                            | F9Dh         |                       |

| C1Eh         | —                            | C9Eh         | —                            | D1Eh         | —                            | D9Eh         | —                            | E1Eh         | _                            | E9Eh         | —                            | F1Eh         | —                            | F9Eh         |                       |

| C1Fh         | —                            | C9Fh         | —                            | D1Fh         | —                            | D9Fh         | —                            | E1Fh         | _                            | E9Fh         | —                            | F1Fh         | —                            | F9Fh         |                       |

| C20h         |                              | CA0h         |                              | D20h         |                              | DA0h         |                              | E20h         |                              | EA0h         |                              | F20h         |                              | FA0h         |                       |

| C6Fh         | Unimplemented<br>Read as '0' | CEFh         | Unimplemented<br>Read as '0' | D6Fh         | Unimplemented<br>Read as '0' | DEFh         | Unimplemented<br>Read as '0' | E6Fh         | Unimplemented<br>Read as '0' | EEFh         | Unimplemented<br>Read as '0' | F6Fh         | Unimplemented<br>Read as '0' | FEFh         |                       |

| C6Fh<br>C70h |                              | CEFn<br>CF0h |                              | D6Fn<br>D70h |                              | DEFn<br>DF0h |                              | E6Fn<br>E70h |                              | EEFn<br>EF0h |                              | F6FN<br>F70h |                              | FEFN<br>FF0h |                       |

| 0701         | Accesses<br>70h – 7Fh        |              | Accesses<br>70h – 7Fh        | -            | Accesses<br>70h – 7Fh        |              | Accesses<br>70h – 7Fh        | -            | Accesses<br>70h – 7Fh |

| CFFh         |                              | CFFh         |                              | D7Fh         |                              | DFFh         |                              | E7Fh         |                              | EFFh         |                              | F7Fh         |                              | FFFh         |                       |

Legend: = Unimplemented data memory locations, read as '0'.

| Address                | Name   | Bit 7                   | Bit 6                                                                                                    | Bit 5          | Bit 4           | Bit 3        | Bit 2        | Bit 1 | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|------------------------|--------|-------------------------|----------------------------------------------------------------------------------------------------------|----------------|-----------------|--------------|--------------|-------|-----------|----------------------|---------------------------------|

| Bank 8                 |        |                         |                                                                                                          |                |                 |              |              |       |           |                      |                                 |

| 400h <sup>(2)</sup>    | INDF0  |                         | Addressing this location uses contents of FSR0H/FSR0L to address data memory<br>not a physical register) |                |                 |              |              |       |           |                      | ****                            |

| 401h <sup>(2)</sup>    | INDF1  |                         | this location cal register)                                                                              | uses contents  | s of FSR1H/F    | SR1L to addr | ess data men | nory  |           | ****                 | XXXX XXXX                       |

| 402h <sup>(2)</sup>    | PCL    | Program Co              | ounter (PC) L                                                                                            | east Significa | nt Byte         |              |              |       |           | 0000 0000            | 0000 0000                       |

| 403h <sup>(2)</sup>    | STATUS | _                       | _                                                                                                        | _              | TO              | PD           | Z            | DC    | С         | 1 1000               | q quuu                          |

| 404h <sup>(2)</sup>    | FSR0L  | Indirect Dat            | a Memory Ac                                                                                              | Idress 0 Low   | Pointer         |              |              |       |           | 0000 0000            | uuuu uuuu                       |

| 405h <sup>(2)</sup>    | FSR0H  | Indirect Dat            | a Memory Ac                                                                                              | ldress 0 High  | Pointer         |              |              |       |           | 0000 0000            | 0000 0000                       |

| 406h <sup>(2)</sup>    | FSR1L  | Indirect Dat            | a Memory Ac                                                                                              | Idress 1 Low   | Pointer         |              |              |       |           | 0000 0000            | uuuu uuuu                       |

| 407h <sup>(2)</sup>    | FSR1H  | Indirect Dat            | a Memory Ac                                                                                              | ldress 1 High  | Pointer         |              |              |       |           | 0000 0000            | 0000 0000                       |

| 408h <sup>(2)</sup>    | BSR    | _                       | _                                                                                                        | —              |                 |              | BSR<4:0>     |       |           | 0 0000               | 0 0000                          |

| 409h <sup>(2)</sup>    | WREG   | Working Re              | gister                                                                                                   |                |                 |              |              |       |           | 0000 0000            | uuuu uuuu                       |

| 40Ah <sup>(1, 2)</sup> | PCLATH | _                       | Write Buffer                                                                                             | for the upper  | 7 bits of the I | Program Cour | nter         |       |           | -000 0000            | -000 0000                       |

| 40Bh <sup>(2)</sup>    | INTCON | GIE                     | PEIE                                                                                                     | TMR0IE         | INTE            | IOCIE        | TMR0IF       | INTF  | IOCIF     | 0000 0000            | 0000 0000                       |

| 40Ch                   | _      | Unimpleme               | Unimplemented                                                                                            |                |                 |              |              |       |           |                      | _                               |

| 40Dh                   | —      | Unimpleme               | Unimplemented                                                                                            |                |                 |              |              |       |           |                      | _                               |

| 40Eh                   | —      | Unimpleme               | nted                                                                                                     |                |                 |              |              |       |           | _                    | _                               |

| 40Fh                   | —      | Unimpleme               | nted                                                                                                     |                |                 |              |              |       |           | _                    | _                               |

| 410h                   | —      | Unimpleme               | nted                                                                                                     |                |                 |              |              |       |           | _                    | _                               |

| 411h                   | —      | Unimpleme               | nted                                                                                                     |                |                 |              |              |       |           | _                    | _                               |

| 412h                   | —      | Unimpleme               | nted                                                                                                     |                |                 |              |              |       |           | _                    | _                               |

| 413h                   | —      | Unimpleme               | nted                                                                                                     |                |                 |              |              |       |           | _                    | _                               |

| 414h                   | —      | Unimpleme               | nted                                                                                                     |                |                 |              |              |       |           | _                    | _                               |

| 415h                   | TMR4   | Timer 4 Mo              | dule Register                                                                                            |                |                 |              |              |       |           | 0000 0000            | 0000 0000                       |

| 416h                   | PR4    | Timer 4 Per             | iod Register                                                                                             |                |                 |              |              |       |           | 1111 1111            | 1111 1111                       |

| 417h                   | T4CON  | —                       |                                                                                                          | T4OUT          | PS<3:0>         |              | TMR40N       | T4CK  | PS<1:0>   | -000 0000            | -000 0000                       |

| 418h                   | —      | Unimpleme               | Unimplemented                                                                                            |                |                 |              |              |       |           | _                    | _                               |

| 419h                   | —      | Unimpleme               | Unimplemented                                                                                            |                |                 |              |              |       |           | _                    | _                               |

| 41Ah                   | —      | Unimplemented           |                                                                                                          |                |                 |              |              |       |           | _                    | _                               |

| 41Bh                   | —      | Unimplemented           |                                                                                                          |                |                 |              |              |       |           | _                    | _                               |

| 41Ch                   | TMR6   | Timer 6 Module Register |                                                                                                          |                |                 |              |              |       | 0000 0000 | 0000 0000            |                                 |

| 41Dh                   | PR6    | Timer 6 Period Register |                                                                                                          |                |                 |              |              |       | 1111 1111 | 1111 1111            |                                 |

| 41Eh                   | T6CON  | —                       | - T6OUTPS<3:0> TMR6ON T6CKPS<1:0>                                                                        |                |                 |              |              |       |           | -000 0000            | -000 0000                       |

| 41Fh                   | _      | Unimpleme               | Unimplemented                                                                                            |                |                 |              |              |       |           |                      | _                               |

#### TABLE 3-10: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<14:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

3: These registers/bits are not implemented on PIC16(L)F1938 devices, read as '0'.

4: Unimplemented, read as '1'.

DS40001574C-page 40

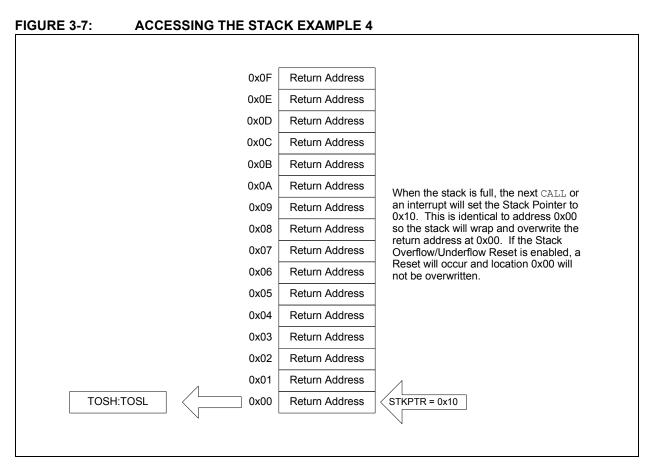

### 3.5.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words is programmed to '1', the device will be reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

#### 3.6 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- · Traditional Data Memory

- Linear Data Memory

- Program Flash Memory

# 5.0 OSCILLATOR MODULE (WITH FAIL-SAFE CLOCK MONITOR)

### 5.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 5-1 illustrates a block diagram of the oscillator module.

Clock sources can be supplied from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be supplied from one of two internal oscillators and PLL circuits, with a choice of speeds selectable via software. Additional clock features include:

- Selectable system clock source between external or internal sources via software.

- Two-Speed Start-up mode, which minimizes latency between external oscillator start-up and code execution.

- Fail-Safe Clock Monitor (FSCM) designed to detect a failure of the external clock source (LP, XT, HS, EC or RC modes) and switch automatically to the internal oscillator.

- Oscillator Start-up Timer (OST) ensures stability

of crystal oscillator sources

The oscillator module can be configured in one of eight clock modes.

- 1. ECL External Clock Low-Power mode (0 MHz to 0.5 MHz)

- 2. ECM External Clock Medium-Power mode (0.5 MHz to 4 MHz)

- 3. ECH External Clock High-Power mode (4 MHz to 32 MHz)

- 4. LP 32 kHz Low-Power Crystal mode

- 5. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode (up to 4 MHz)

- 6. HS High Gain Crystal or Ceramic Resonator mode (4 MHz to 20 MHz)

- 7. RC External Resistor-Capacitor (RC)

- 8. INTOSC Internal oscillator (31 kHz to 32 MHz)

Clock Source modes are selected by the FOSC<2:0> bits in the Configuration Words. The FOSC bits determine the type of oscillator that will be used when the device is first powered.

The EC clock mode relies on an external logic level signal as the device clock source. The LP, XT, and HS clock modes require an external crystal or resonator to be connected to the device. Each mode is optimized for a different frequency range. The RC clock mode requires an external resistor and capacitor to set the oscillator frequency.

The INTOSC internal oscillator block produces low, medium, and high frequency clock sources, designated LFINTOSC, MFINTOSC, and HFINTOSC. (see Internal Oscillator Block, Figure 5-1). A wide selection of device clock frequencies may be derived from these three clock sources.

| U-0                  | U-0         | R/W-0/0           | R/W-0/0         | R/W-0/0           | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|----------------------|-------------|-------------------|-----------------|-------------------|------------------|----------------|--------------|

| —                    | —           |                   |                 | TUN               | <5:0>            |                |              |

| bit 7                |             |                   |                 |                   |                  |                | bit 0        |

|                      |             |                   |                 |                   |                  |                |              |

| Legend:              |             |                   |                 |                   |                  |                |              |

| R = Readable         | e bit       | W = Writable      | bit             | U = Unimplen      | nented bit, read | d as '0'       |              |

| u = Bit is unchanged |             | x = Bit is unkr   | nown            | -n/n = Value a    | t POR and BO     | R/Value at all | other Resets |

| '1' = Bit is set     |             | '0' = Bit is clea | ared            |                   |                  |                |              |

|                      |             |                   |                 |                   |                  |                |              |

| bit 7-6              | Unimplemen  | ted: Read as '    | 0'              |                   |                  |                |              |

| bit 5-0              | TUN<5:0>: F | requency Tunir    | ng bits         |                   |                  |                |              |

|                      | 100000 = M  | inimum frequer    | псу             |                   |                  |                |              |

|                      | •           |                   |                 |                   |                  |                |              |

|                      | •           |                   |                 |                   |                  |                |              |

|                      | 111111 =    |                   |                 |                   |                  |                |              |

|                      |             | scillator module  | e is running at | the factory-calil | prated frequen   | cy.            |              |

|                      | 000001 =    |                   |                 |                   |                  |                |              |

|                      | •           |                   |                 |                   |                  |                |              |

|                      | •           |                   |                 |                   |                  |                |              |

|                      | 011110 =    |                   |                 |                   |                  |                |              |

|                      | 011111 = M  | aximum freque     | ncy             |                   |                  |                |              |

### REGISTER 5-3: OSCTUNE: OSCILLATOR TUNING REGISTER

| Bit 7  | Bit 6                                                | Bit 5                                         | Bit 4                                                                                                                                                      | Bit 3                                                                                                                                                                                                                                                               | Bit 2                                                                                                                                                                                                                                                                                                                                                         | Bit 1                                                                                                                                                                   | Bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Register<br>on Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|--------|------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SPLLEN |                                                      | IRCF                                          | <3:0>                                                                                                                                                      |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                               | SCS                                                                                                                                                                     | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| T1OSCR | PLLR                                                 | OSTS                                          | HFIOFR                                                                                                                                                     | HFIOFL                                                                                                                                                                                                                                                              | MFIOFR                                                                                                                                                                                                                                                                                                                                                        | LFIOFR                                                                                                                                                                  | HFIOFS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| _      |                                                      |                                               | TUN<5:0>                                                                                                                                                   |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| OSFIE  | C2IE                                                 | C1IE                                          | EEIE                                                                                                                                                       | BCLIE                                                                                                                                                                                                                                                               | LCDIE                                                                                                                                                                                                                                                                                                                                                         | —                                                                                                                                                                       | CCP2IE <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| OSFIF  | C2IF                                                 | C1IF                                          | EEIF                                                                                                                                                       | BCLIF                                                                                                                                                                                                                                                               | LCDIF                                                                                                                                                                                                                                                                                                                                                         | —                                                                                                                                                                       | CCP2IF <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| TMR1C  | S<1:0>                                               | T1CKP                                         | S<1:0>                                                                                                                                                     | T1OSCEN                                                                                                                                                                                                                                                             | T1SYNC                                                                                                                                                                                                                                                                                                                                                        | —                                                                                                                                                                       | TMR10N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 197                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|        | SPLLEN<br>T1OSCR<br>OSFIE<br>OSFIE<br>OSFIF<br>TMR1C | SPLLENT1OSCRPLLROSFIEC2IEOSFIFC2IFTMR1CS<1:0> | SPLLEN     IRCF       T10SCR     PLLR     OSTS       —     —     —       OSFIE     C2IE     C1IE       OSFIF     C2IF     C1IF       TMR1CS<1:0>     T1CKP | SPLLEN         IRCF-3:0>           T10SCR         PLLR         OSTS         HFI0FR                 OSFIE         C2IE         C1IE         EEIE           OSFIF         C2IF         C1IF         EEIF           TMR1CS-1:0>         T1CKFS-1:0>         T1CKFS-1:0 | SPLLEN         IRCF-3:0>           T10SCR         PLLR         OSTS         HFIOFR         HFIOFL           —         —         —         TUN         TUN           OSFIE         C2IE         C1IE         EEIE         BCLIE           OSFIF         C2IF         C1IF         EEIF         BCLIF           TMR1CS<1:0>         T1CKPS<1:0>         T1OSCEN | SPLLEN         IRCF<3:0>         —           T10SCR         PLLR         OSTS         HFIOFR         HFIOFL         MFIOFR           —         —         —         TUN< | SPLLEN         IRCF<3:0>         —         SCS           T1OSCR         PLLR         OSTS         HFIOFR         HFIOFL         MFIOFR         LFIOFR           —         —         —         SCS         SCS | SPLLENIRCF<3:0>IRCSCST10SCRPLLROSTSHFI0FRHFI0FLMFI0FRLFI0FRHFI0FSImage: Image: Imag |  |

Note 1: PIC16F1934 only.

#### TABLE 5-3: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5                   | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1   | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------------------------|----------|----------|----------|-----------|---------|---------------------|

|         | 13:8 | _       |         | FCMEN                      | IESO     | CLKOUTEN | BOREI    | N<1:0>    | CPD     | 54                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE                      | WDTE     | =<1:0>   |          | FOSC<2:0> |         | 54                  |

|         | 13:8 | _       | _       | LVP                        | DEBUG    | _        | BORV     | STVREN    | PLLEN   | 50                  |

| CONFIG2 | 7:0  |         |         | VCAPEN<1:0> <sup>(1)</sup> |          | _        | — WRT    |           | <1:0>   | 56                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

Note 1: PIC16F193X only.