Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                           |

|----------------------------|------------------------------------------------------------------------------------|

| Core Processor             | 8051                                                                               |

| Core Size                  | 8-Bit                                                                              |

| Speed                      | 40MHz                                                                              |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                   |

| Number of I/O              | 36                                                                                 |

| Program Memory Size        | 72KB (72K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                              |

| EEPROM Size                | -                                                                                  |

| RAM Size                   | 1K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                        |

| Data Converters            | -                                                                                  |

| Oscillator Type            | External                                                                           |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                    |

| Mounting Type              | Through Hole                                                                       |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                           |

| Supplier Device Package    | 40-PDIL                                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89e516rd-40-c-pie-nxx |

|                            |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Data Sheet

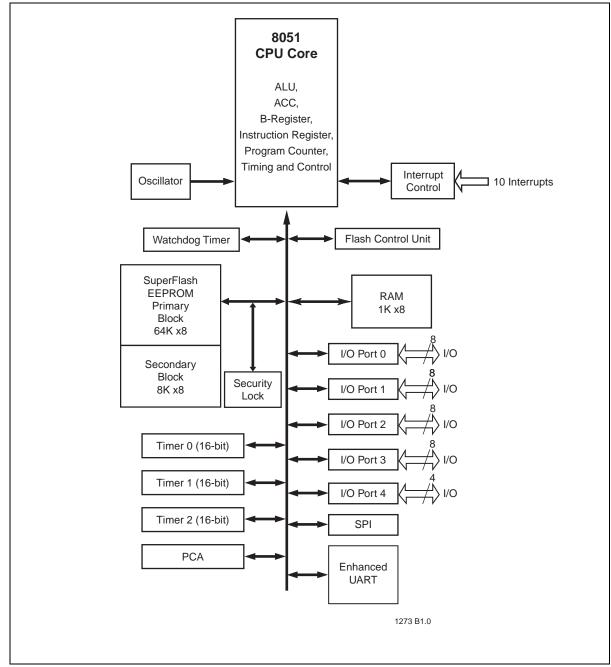

## **Functional Blocks**

Figure 1: Functional Block Diagram

Data Sheet

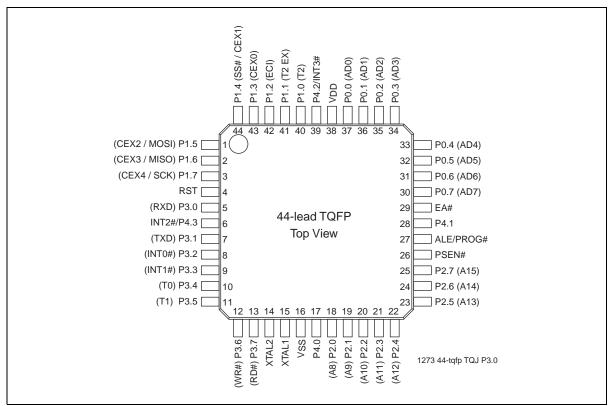

Figure 4: Pin Assignments for 44-lead TQFP

### Data Sheet

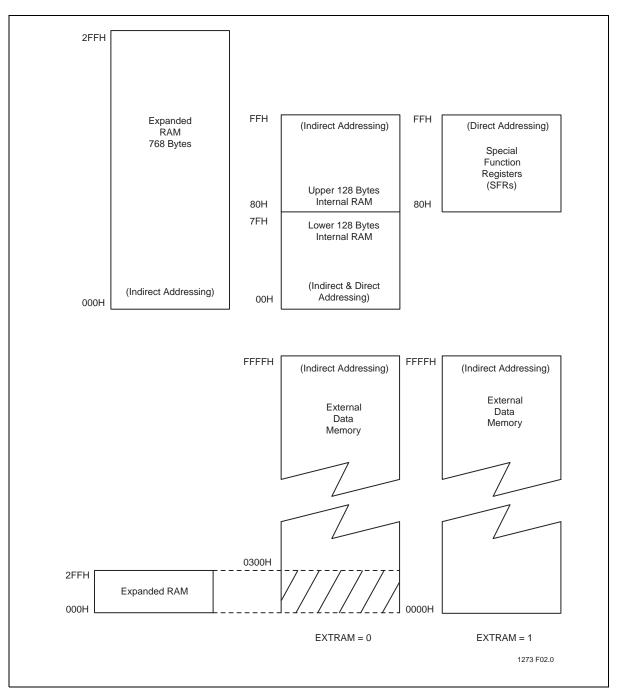

### Figure 7: Internal and External Data Memory Structure

Data Sheet

### Auxiliary Register (AUXR)

| Location | 7 | 6 | 5 | 4 | 3 | 2 | 1          | 0  | Reset Value |

|----------|---|---|---|---|---|---|------------|----|-------------|

| 8EH      | - | - | - | - | - | - | EXTRA<br>M | AO | xxxxxx00b   |

|          |   |   |   |   |   |   |            |    | l           |

### Symbol Function

EXTRAM Internal/External RAM access

0: Internal Expanded RAM access within range of 00H to 2FFH using MOVX @Ri / @DPTR. Beyond 300H, the MCU always accesses external data memory. For details, refer to Section, "Expanded Data RAM Addressing". 1: External data memory access.

AO D

Disable/Enable ALE

0: ALE is emitted at a constant rate of 1/3 the oscillator frequency in 6 clock mode, 1/6  $f_{\rm OSC}$  in 12 clock mode.

1: ALE is active only during a MOVX or MOVC instruction.

### Auxiliary Register 1 (AUXR1)

| Location | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0   | Reset Value |

|----------|---|---|---|---|-----|---|---|-----|-------------|

| A2H      | - | - | - | - | GF2 | 0 | - | DPS | xxxx00x0b   |

### Symbol Function

GF2 General purpose user-defined flag.

DPS DPTR registers select bit.

0: DPTR0 is selected.

1: DPTR1 is selected.

### Watchdog Timer Control Register (WDTC)

| Location | 7 | 6 | 5 | 4     | 3    | 2    | 1   | 0    | Reset Value |

|----------|---|---|---|-------|------|------|-----|------|-------------|

| C0H      | - | - | - | WDOUT | WDRE | WDTS | WDT | SWDT | xxx00000b   |

### Symbol Function

WDOUT Watchdog output enable.

0: Watchdog reset will not be exported on Reset pin.

1: Watchdog reset if enabled by WDRE, will assert Reset pin for 32 clocks.

### WDRE Watchdog timer reset enable.

0: Disable watchdog timer reset.

1: Enable watchdog timer reset.

WDTS Watchdog timer reset flag.

0: External hardware reset or power-on reset clears the flag.

- Flag can also be cleared by writing a 1.

- Flag survives if chip reset happened because of watchdog timer overflow.

- 1: Hardware sets the flag on watchdog overflow.

### WDT Watchdog timer refresh.

0: Hardware resets the bit when refresh is done.

- 1: Software sets the bit to force a watchdog timer refresh.

- SWDT Start watchdog timer.

- 0: Stop WDT.

- 1: Start WDT.

### Data Sheet

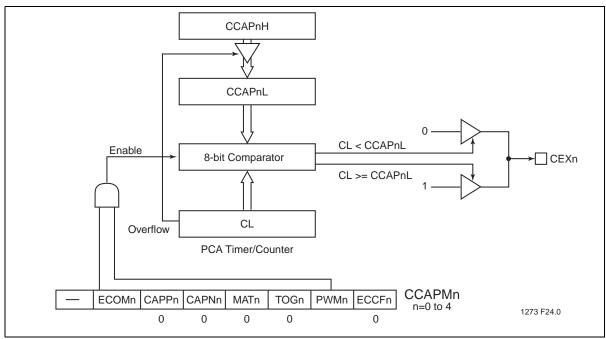

| counter Mod | ie Registe   |              | )               |               |              |               |                 |              |             |

|-------------|--------------|--------------|-----------------|---------------|--------------|---------------|-----------------|--------------|-------------|

| Location    | 7            | 6            | 5               | 4             | 3            | 2             | 1               | 0            | Reset Value |

| D9H         | CIDL         | WDTE         | -               | -             | -            | CPS1          | CPS0            | ECF          | 00xxx000b   |

|             | 1. Not bit a | addressable  |                 |               |              |               |                 |              | -           |

| Symbol      | Function     |              |                 |               |              |               |                 |              |             |

| CIDL        | Counter Id   | lle Control  | :               |               |              |               |                 |              |             |

|             | 0: Progran   |              |                 |               |              | 0 0           | idle mode       | 9            |             |

|             | 1: Progran   | ns the PC    | A Counter       | to be gate    | ed off durir | ng idle       |                 |              |             |

| WDTE        | Watchdog     |              |                 |               |              |               |                 |              |             |

|             | 0: Disable   |              | •               |               |              |               |                 |              |             |

|             | 1: Enables   |              | •<br>•          |               |              | uie 4         |                 |              |             |

| -           | Not impler   | -            |                 |               |              |               |                 |              |             |

|             | Note: User s | hould not wr | ite '1's to res | erved bits. T | he value rea | d from a rese | erved bit is ir | ndeterminate | <b>e.</b>   |

| CPS1        | PCA Cour     | nt Pulse Se  | elect bit 1     |               |              |               |                 |              |             |

| CPS0        | PCA Cour     | nt Pulse Se  | elect bit 2     |               |              |               |                 |              |             |

|             |              |              |                 |               |              |               |                 |              |             |

| CPS1 | CPS0 | Selected<br>PCA Input <sup>1</sup> |                                                                                             |

|------|------|------------------------------------|---------------------------------------------------------------------------------------------|

| 0    | 0    | 0                                  | Internal clock, f <sub>OSC</sub> /6 in 6 clock mode (f <sub>OSC</sub> /12 in 12 clock mode) |

| 0    | 1    | 1                                  | Internal clock, $f_{OSC}/2$ in 6 clock mode ( $f_{OSC}/4$ in 12 clock mode)                 |

| 1    | 0    | 2                                  | Timer 0 overflow                                                                            |

| 1    | 1    | 3                                  | External clock at ECI/P1.2 pin                                                              |

|      |      |                                    | (max. rate = $f_{OSC}/4$ in 6 clock mode, $f_{OSC}/8$ in 12 clock mode)                     |

1. f<sub>OSC</sub> = oscillator frequency

ECF PCA Enable Counter Overflow interrupt:

0: Disables the CF bit in CCON

1: Enables CF bit in CCON to generate an interrupt

### Data Sheet

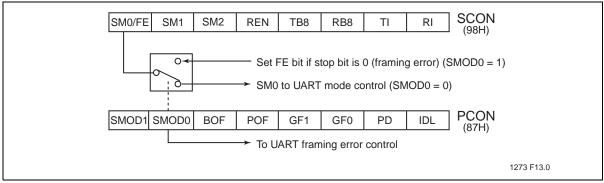

### Serial Port Control Register (SCON)

| Location | 7      | 6   | 5   | 4   | 3   | 2   | 1  | 0  | Reset Value |

|----------|--------|-----|-----|-----|-----|-----|----|----|-------------|

| 98H      | SM0/FE | SM1 | SM2 | REN | TB8 | RB8 | TI | RI | 0000000b    |

### Symbol Function

| <ul> <li>FE Set SMOD0 = 1 to access FE bit.</li> <li>0: No framing error</li> <li>1: Framing Error. Set by receiver when an invalid stop bit is detected. This bit needs to be</li> </ul> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                           |

- SM0 SMOD0 = 0 to access SM0 bit. Serial Port Mode Bit 0

- SM1 Serial Port Mode Bit 1

| SM0 | SM1                    | Mode | Description    | Baud Rate <sup>1</sup>                                                                      |

|-----|------------------------|------|----------------|---------------------------------------------------------------------------------------------|

| 0   | 0                      | 0    | Shift Register | f <sub>OSC</sub> /6 (6 clock mode) or<br>f <sub>OSC</sub> /12 (12 clock mode)               |

| 0   | 1                      | 1    | 8-bit UART     | Variable                                                                                    |

| 1   | 0                      | 2    | 9-bit UART     | $f_{OSC}/32$ or $f_{OSC}/16$ (6 clock mode) or $f_{OSC}/64$ or $f_{OSC}/32$ (12 clock mode) |

| 1   | 1<br>illator fraguenov | 3    | 9-bit UART     | Variable                                                                                    |

1. f<sub>OSC</sub> = oscillator frequency

- SM2 Enables the Automatic Address Recognition feature in Modes 2 or 3. If SM2 = 1 then RI will not be set unless the received 9th data bit (RB8) is 1, indicating an address, and the received byte is a given or broadcast address. In Mode 1, if SM2 = 1 then RI will not be activated unless a valid stop bit was received. In Mode 0, SM2 should be 0.

- REN Enables serial reception. 0: to disable reception. 1: to enable reception.

- TB8 The 9th data bit that will be transmitted in Modes 2 and 3. Set or clear by software as

- desired.

- RB8 In Modes 2 and 3, the 9th data bit that was received. In Mode 1, if SM2 = 0, RB8 is the stop bit that was received. In Mode 0, RB8 is not used.

- TI Transmit interrupt flag. Set by hardware at the end of the 8th bit time in Mode 0, or at the beginning of the stop bit in the other modes, in any serial transmission, Must be cleared by software.

- RI Receive interrupt flag. Set by hardware at the end of the8th bit time in Mode 0, or halfway through the stop bit time in the other modes, in any serial reception (except see SM2). Must be cleared by software.

Data Sheet

|                 |                                                         | T20                           | CON                           |

|-----------------|---------------------------------------------------------|-------------------------------|-------------------------------|

|                 | Mode                                                    | Internal Control <sup>1</sup> | External Control <sup>2</sup> |

|                 | 16-bit Auto-Reload                                      | 00H                           | 08H                           |

|                 | 16-bit Capture                                          | 01H                           | 09H                           |

| Used as Timer   | Baud rate generator receive and transmit same baud rate | 34H                           | 36H                           |

|                 | Receive only                                            | 24H                           | 26H                           |

|                 | Transmit only                                           | 14H                           | 16H                           |

| Used as Counter | 16-bit Auto-Reload                                      | 02H                           | 0AH                           |

| Useu as Counter | 16-bit Capture                                          | 03H                           | 0BH                           |

### Table 17: Timer/Counter 2

1. Capture/Reload occurs only on timer/counter overflow.

T0-0.0 25093

2. Capture/Reload occurs on timer/counter overflow and a 1 to 0 transition on T2EX (P1.1) pin except when Timer 2 is used in the baud rate generating mode.

### **Programmable Clock-Out**

A 50% duty cycle clock can be programmed to come out on P1.0. This pin, besides being a regular I/O pin, has two alternate functions. It can be programmed:

- 1. to input the external clock for Timer/Counter 2, or

- 2. to output a 50% duty cycle clock ranging from 122 Hz to 8 MHz at a 16 MHz operating frequency (61 Hz to 4 MHz in 12 clock mode).

To configure Timer/Counter 2 as a clock generator, bit

C/#T2 (in T2CON) must be cleared and bit T20E in T2MOD must be set. Bit TR2 (T2CON.2) also must be set to start the timer.

The Clock-Out frequency depends on the oscillator frequency and the reload value of Timer 2 capture registers (RCAP2H, RCAP2L) as shown in this equation:

n =2 (in 6 clock mode) 4 (in 12 clock mode)

Where (RCAP2H, RCAP2L) = the contents of RCAP2H and RCAP2L taken as a 16-bit unsigned integer.

In the Clock-Out mode, Timer 2 roll-overs will not generate an interrupt. This is similar to when it is used as a baud-rate generator. It is possible to use Timer 2 as a baud-rate generator and a clock generator simultaneously. Note, however, that the baud-rate and the Clock-Out frequency will not be the same.

Data Sheet

## Serial I/O

## Full-Duplex, Enhanced UART

The device serial I/O port is a full-duplex port that allows data to be transmitted and received simultaneously in hardware by the transmit and receive registers, respectively, while the software is performing other tasks. The transmit and receive registers are both located in the Serial Data Buffer (SBUF) special function register. Writing to the SBUF register loads the transmit register, and reading from the SBUF register obtains the contents of the receive register.

The UART has four modes of operation which are selected by the Serial Port Mode Specifier (SM0 and SM1) bits of the Serial Port Control (SCON) special function register. In all four modes, transmission is initiated by any instruction that uses the SBUF register as a destination register. Reception is initiated in mode 0 when the Receive Interrupt (RI) flag bit of the Serial Port Control (SCON) SFR is cleared and the Reception Enable/ Disable (REN) bit of the SCON register is set. Reception is initiated in the other modes by the incoming start bit if the REN bit of the SCON register is set.

### **Framing Error Detection**

Framing Error Detection is a feature, which allows the receiving controller to check for valid stop bits in modes 1, 2, or 3. Missing stops bits can be caused by noise in serial lines or from simultaneous transmission by two CPUs.

Framing Error Detection is selected by going to the PCON register and changing SMOD0 = 1 (see Figure 17). If a stop bit is missing, the Framing Error bit (FE) will be set. Software may examine the FE bit after each reception to check for data errors. After the FE bit has been set, it can only be cleared by software. Valid stop bits do not clear FE. When FE is enabled, RI rises on the stop bit, instead of the last data bit (see Figure 18 and Figure 19).

Figure 17: Framing Error Block Diagram

### Data Sheet

If mode 1 is used, the stop bit takes the place of the 9th bit. Bit RI is set only when the received command frame address matches the device's address and is terminated by a valid stop bit. Note that mode 0 cannot be used. Setting SM2 bit in the SCON register in mode 0 will have no effect.

Each slave's individual address is specified by SFR SADDR. SFR SADEN is a mask byte that defines "don't care" bits to form the given address when combined with SADDR. See the example below:

### Slave 1

| SADDR | = | 1111 0001 |

|-------|---|-----------|

| SADEN | = | 1111 1010 |

| GIVEN | = | 1111 0X0X |

### Slave 2

| SADDR | = | 1111 0011 |

|-------|---|-----------|

| SADEN | = | 1111 1001 |

| GIVEN | = | 1111 0XX1 |

### Using the Given Address to Select Slaves

Any bits masked off by a 0 from SADEN become a "don't care" bit for the given address. Any bit masked off by a 1, becomes ANDED with SADDR. The "don't cares" provide flexibility in the user-defined addresses to address more slaves when using the given address.

Shown in the example above, Slave 1 has been given an address of 1111 0001 (SADDR). The SADEN byte has been used to mask off bits to a given address to allow more combinations of selecting Slave 1 and Slave 2. In this case for the given addresses, the last bit (LSB) of Slave 1 is a "don't care" and the last bit of Slave 2 is a 1. To communicate with Slave 1 and Slave 2, the master would need to send an address with the last bit equal to 1 (e.g. 1111 0001) since Slave 1's last bit is a don't care and Slave 2's last bit has to be a 1. To communicate with Slave 1 alone, the master would send an address with the last bit equal to 0 (e.g. 1111 0000), since Slave 2's last bit is a 1. See the table below for other possible combinations.

| Select Slave 1 Only                      |           |           |  |  |

|------------------------------------------|-----------|-----------|--|--|

| Slave 1 Given Address Possible Addresses |           |           |  |  |

|                                          | 1111 0X0X | 1111 0000 |  |  |

|                                          |           | 1111 0100 |  |  |

| Select Slave 2 Only                      |           |           |  |  |  |

|------------------------------------------|-----------|-----------|--|--|--|

| Slave 2 Given Address Possible Addresses |           |           |  |  |  |

|                                          | 1111 0XX1 | 1111 0111 |  |  |  |

|                                          |           | 1111 0011 |  |  |  |

| Select Slaves 1 & 2             |           |  |  |  |

|---------------------------------|-----------|--|--|--|

| Slaves 1 & 2 Possible Addresses |           |  |  |  |

|                                 | 1111 0001 |  |  |  |

|                                 | 1111 0101 |  |  |  |

Data Sheet

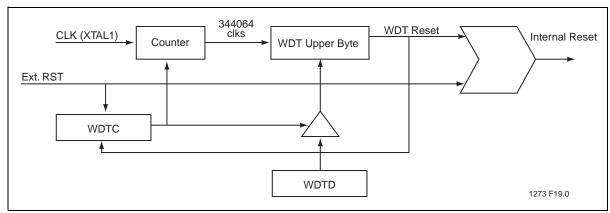

## Watchdog Timer

The device offers a programmable Watchdog Timer (WDT) for fail safe protection against software deadlock and automatic recovery.

To protect the system against software deadlock, the user software must refresh the WDT within a user-defined time period. If the software fails to do this periodical refresh, an internal hardware reset will be initiated if enabled (WDRE= 1). The software can be designed such that the WDT times out if the program does not work properly.

The WDT in the device uses the system clock (XTAL1) as its time base. So strictly speaking, it is a watchdog counter rather than a watchdog timer. The WDT register will increment every 344,064 crystal clocks. The upper 8-bits of the time base register (WDTD) are used as the reload register of the WDT.

The WDTS flag bit is set by WDT overflow and is not changed by WDT reset. User software can clear WDTS by writing "1" to it.

Figure 23 provides a block diagram of the WDT. Two SFRs (WDTC and WDTD) control watchdog timer operation. During idle mode, WDT operation is temporarily suspended, and resumes upon an interrupt exit from idle.

The time-out period of the WDT is calculated as follows:

Period = (255 - WDTD) \* 344064 \* 1/f<sub>CLK (XTAL1)</sub>

where WDTD is the value loaded into the WDTD register and f<sub>OSC</sub> is the oscillator frequency.

Figure 23: Block Diagram of Programmable Watchdog Timer

Data Sheet

### Figure 28: PCA Pulse Width Modulator Mode

| Table 24: Pulse Width | n Modulator F | Frequencies |

|-----------------------|---------------|-------------|

|-----------------------|---------------|-------------|

|                           | PWM Frequency      |                    |  |

|---------------------------|--------------------|--------------------|--|

| PCA Timer Mode            | 12 MHz             | 16 MHz             |  |

| 1/12 Oscillator Frequency | 3.9 KHz            | 5.2 KHz            |  |

| 1/4 Oscillator Frequency  | 11.8 KHz           | 15.6 KHz           |  |

| Timer 0 Overflow:         |                    |                    |  |

| 8-bit                     | 15.5 Hz            | 20.3 Hz            |  |

| 16-bit                    | 0.06 Hz            | 0.08 Hz            |  |

| 8-bit Auto-Reload         | 3.9 KHz to 15.3 Hz | 5.2 KHz to 20.3 Hz |  |

| External Input (Max)      | 5.9 KHz            | 7.8 KHz            |  |

T0-0.0 25093

Data Sheet

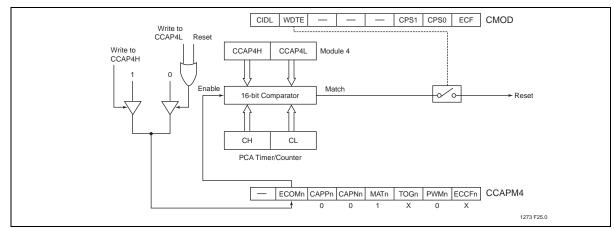

CLR EA; Hold off interrupts

MOVCCAP4L, #00; Next compare value is within

MOVCCAP4H, CH; 65,535 counts of the ; current PCA

SETBEA; timer value

RET

This routine should not be part of an interrupt service routine. If the program counter goes astray and gets stuck in an infinite loop, interrupts will still be serviced and the watchdog will keep getting reset. Thus, the purpose of the watchdog would be defeated. Instead, call this subroutine from the main program of the PCA timer.

Figure 29: PCA Watchdog Timer (Module 4 only)

Data Sheet

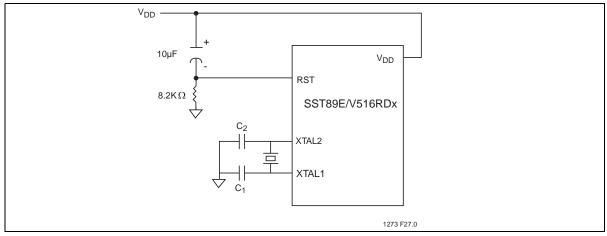

## Reset

A system reset initializes the MCU and begins program execution at program memory location 0000H. The reset input for the device is the RST pin. In order to reset the device, a logic level high must be applied to the RST pin for at least two machine cycles (24 clocks), after the oscillator becomes stable. ALE, PSEN# are weakly pulled high during reset. During reset, ALE and PSEN# output a high level in order to perform a proper reset. This level must not be affected by external element. A system reset will not affect the 1 KByte of on-chip RAM while the device is running, however, the contents of the on-chip RAM during power up are indeterminate. Following reset, all Special Function Registers (SFR) return to their reset values outlined in Tables 6 to 10.

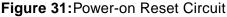

### **Power-on Reset**

At initial power up, the port pins will be in a random state until the oscillator has started and the internal reset algorithm has weakly pulled all pins high. Powering up the device without a valid reset could cause the MCU to start executing instructions from an indeterminate location. Such undefined states may inadvertently corrupt the code in the flash.

When power is applied to the device, the RST pin must be held high long enough for the oscillator to start up (usually several milliseconds for a low frequency crystal), in addition to two machine cycles for a valid power-on reset. An example of a method to extend the RST signal is to implement a RC circuit by connecting the RST pin to  $V_{DD}$  through a 10 µF capacitor and to  $V_{SS}$  through an 8.2K $\Omega$  resistor as shown in Figure 31. Note that if an RC circuit is being used, provisions should be made to ensure the  $V_{DD}$  rise time does not exceed 1 millisecond and the oscillator start-up time does not exceed 10 milliseconds.

For a low frequency oscillator with slow start-up time the reset signal must be extended in order to account for the slow start-up time. This method maintains the necessary relationship between  $V_{DD}$  and RST to avoid programming at an indeterminate location, which may cause corruption in the code of the flash. The power-on detection is designed to work as power up initially, before the voltage reaches the brown-out detection level. The POF flag in the PCON register is set to indicate an initial power up condition. The POF flag will remain active until cleared by software. Please see Section , "Power Control Register (PCON)" on page 31 for detailed information.

For more information on system level design techniques, please review the *FlashFlex MCU: Oscillator Circuit Design Considerations* application note.

### Data Sheet

### Table 32: Reliability Characteristics

| Symbol                        | Parameter      | Minimum Specification | Units  | Test Method         |

|-------------------------------|----------------|-----------------------|--------|---------------------|

| N <sub>END</sub> <sup>1</sup> | Endurance      | 10,000                | Cycles | JEDEC Standard A117 |

| T <sub>DR</sub> <sup>1</sup>  | Data Retention | 100                   | Years  | JEDEC Standard A103 |

| I <sub>LTH</sub> <sup>1</sup> | Latch Up       | 100 + I <sub>DD</sub> | mA     | JEDEC Standard 78   |

T0-0.0 25093 1. This parameter is measured only for initial qualification and after a design or process change that could affect this

parameter.

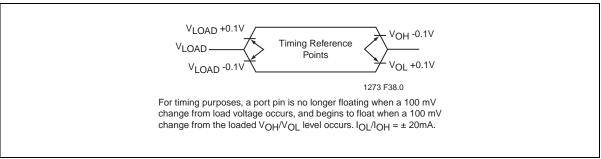

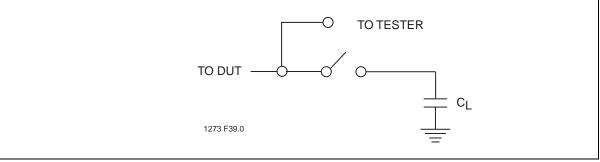

### Table 33: AC Conditions of Test<sup>1</sup>

| Input Rise/Fall Time | Output Load             |

|----------------------|-------------------------|

| 10 ns                | C <sub>L</sub> = 100 pF |

1. See Figures 41 and 43

T33.1 25093

### Table 34: Recommended System Power-up Timings

| Symbol                             | Parameter                   | Minimum | Units        |

|------------------------------------|-----------------------------|---------|--------------|

| T <sub>PU-READ</sub> <sup>1</sup>  | Power-up to Read Operation  | 100     | μs           |

| T <sub>PU-WRITE</sub> <sup>1</sup> | Power-up to Write Operation | 100     | μs           |

|                                    |                             |         | T0-0.0 25093 |

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter

### Table 35: Pin Impedance (V<sub>DD</sub>=3.3V, T<sub>A</sub>=25°C, f=1 Mhz, other pins open)

| Parameter                     | Description         | Test Condition | Maximum      |

|-------------------------------|---------------------|----------------|--------------|

| C <sub>I/O</sub> <sup>1</sup> | I/O Pin Capacitance | $V_{I/O} = 0V$ | 15 pF        |

| C <sub>IN</sub> <sup>1</sup>  | Input Capacitance   | $V_{IN} = 0V$  | 12 pF        |

| L <sub>PIN</sub> <sup>2</sup> | Pin Inductance      |                | 20 nH        |

|                               | ·                   |                | T0-0.0 25093 |

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

2. Refer to PCI spec.

Data Sheet

## **DC Electrical Characteristics**

| Symbol           | Parameter                                                      | Test Conditions                        | Min                         | Max                         | Units |

|------------------|----------------------------------------------------------------|----------------------------------------|-----------------------------|-----------------------------|-------|

| VIL              | Input Low Voltage                                              | 4.5 < V <sub>DD</sub> < 5.5            | -0.5                        | 0.2V <sub>DD</sub> -<br>0.1 | V     |

| V <sub>IH</sub>  | Input High Voltage                                             | 4.5 < V <sub>DD</sub> < 5.5            | 0.2V <sub>DD</sub> +<br>0.9 | V <sub>DD</sub> + 0.5       | V     |

| V <sub>IH1</sub> | Input High Voltage (XTAL1, RST)                                | $4.5 < V_{DD} < 5.5$                   | $0.7V_{DD}$                 | V <sub>DD</sub> + 0.5       | V     |

| V <sub>OL</sub>  | Output Low Voltage (Ports 1.5, 1.6, 1.7)                       | $V_{DD} = 4.5V$                        |                             |                             |       |

|                  |                                                                | I <sub>OL</sub> = 16mA                 |                             | 1.0                         | V     |

| V <sub>OL</sub>  | Output Low Voltage (Ports 1, 2, 3) <sup>1</sup>                | $V_{DD} = 4.5V$                        |                             |                             |       |

|                  |                                                                | $I_{OL} = 100 \mu A^2$                 |                             | 0.3                         | V     |

|                  |                                                                | $I_{OL} = 1.6 m A^2$                   |                             | 0.45                        | V     |

|                  |                                                                | $I_{OL} = 3.5 \text{mA}^2$             |                             | 1.0                         | V     |

| V <sub>OL1</sub> | Output Low Voltage (Port 0, ALE,                               | $V_{DD} = 4.5V$                        |                             |                             |       |

|                  | PSEN#) <sup>1,3</sup>                                          | $I_{OL} = 200 \mu A^2$                 |                             | 0.3                         | V     |

|                  |                                                                | $I_{OL} = 3.2 \text{mA}^2$             |                             | 0.45                        | V     |

| V <sub>OH</sub>  | Output High Voltage (Ports 1, 2, 3, ALE, PSEN#) <sup>4</sup>   | $V_{DD} = 4.5V$                        |                             |                             |       |

|                  |                                                                | I <sub>OH</sub> = -10μA                | V <sub>DD</sub> - 0.3       |                             | V     |

|                  |                                                                | I <sub>OH</sub> = -30μA                | V <sub>DD</sub> - 0.7       |                             | V     |

|                  |                                                                | I <sub>OH</sub> = -60μA                | V <sub>DD</sub> - 1.5       |                             | V     |

| V <sub>OH1</sub> | Output High Voltage (Port 0 in External Bus Mode) <sup>4</sup> | $V_{DD} = 4.5V$                        |                             |                             |       |

|                  |                                                                | I <sub>OH</sub> = -200μA               | V <sub>DD</sub> - 0.3       |                             | V     |

|                  |                                                                | I <sub>OH</sub> = -3.2mA               | V <sub>DD</sub> - 0.7       |                             | V     |

| V <sub>BOD</sub> | Brown-out Detection Voltage                                    |                                        | 3.85                        | 4.15                        | V     |

| IIL              | Logical 0 Input Current (Ports 1, 2, 3)                        | $V_{IN} = 0.4V$                        |                             | -75                         | μA    |

| I <sub>TL</sub>  | Logical 1-to-0 Transition Current (Ports 1, 2, 3) <sup>5</sup> | $V_{IN} = 2V$                          |                             | -650                        | μA    |

| ILI              | Input Leakage Current (Port 0)                                 | $0.45 < V_{IN} < V_{DD}$ -0.3          |                             | ±10                         | μA    |

| R <sub>RST</sub> | RST Pull-down Resistor                                         |                                        | 40                          | 225                         | KΩ    |

| C <sub>IO</sub>  | Pin Capacitance <sup>6</sup>                                   | @ 1 MHz, 25°C                          |                             | 15                          | pF    |

| I <sub>DD</sub>  | Power Supply Current                                           |                                        |                             |                             |       |

|                  | IAP Mode                                                       |                                        |                             |                             |       |

|                  | @ 40 MHz                                                       |                                        |                             | 88                          | mA    |

|                  | Active Mode                                                    |                                        |                             |                             |       |

|                  | @ 40 MHz                                                       |                                        |                             | 50                          | mA    |

|                  | Idle Mode                                                      |                                        |                             |                             |       |

|                  | @ 40 MHz                                                       |                                        |                             | 42                          | mA    |

|                  | Power-down Mode (min. $V_{DD} = 2V$ )                          | $T_A = 0^{\circ}C$ to +70°C            |                             | 80                          | μA    |

|                  |                                                                | $T_A = -40^{\circ}C$ to $+85^{\circ}C$ |                             | 90                          | μA    |

### **Table 36:** DC Electrical Characteristics for SST89E516RDx $T_{A} = -40^{\circ}$ C to $+85^{\circ}$ C: $V_{DD} = 4.5 \cdot 5.5$ V: $V_{SS} = 0$ V

T0-0.1 25093

Data Sheet

1. Under steady state (non-transient) conditions,  $I_{OL}$  must be externally limited as follows:

Maximum I<sub>OL</sub> per port pin: 15mA Maximum I<sub>OL</sub> per 8-bit port: 26mA

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification.

Pins are not guaranteed to sink current greater than the listed test conditions.

- 2. Capacitive loading on Ports 0 and 2 may cause spurious noise to be superimposed on the V<sub>OL</sub>s of ALE and Ports 1 & 3. The noise due to external bus capacitance discharging into the Port 0 & 2 pins when the pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100pF), the noise pulse on the ALE pin may exceed 0.8V. In such cases, it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input.

- 3. Load capacitance for Port 0, ALE & PSEN#= 100pF, load capacitance for all other outputs = 80pF.

- 4. Capacitive loading on Ports 0 and 2 may cause the  $V_{OH}$  on ALE and PSEN# to momentarily fall below the  $V_{DD}$  0.7 specification when the address bits are stabilizing.

- 5. Pins of Ports 1, 2, and 3 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when V<sub>IN</sub> is approximately 2V.

- 6. Pin capacitance is characterized but not tested. EA# is 25pF (max).

Data Sheet

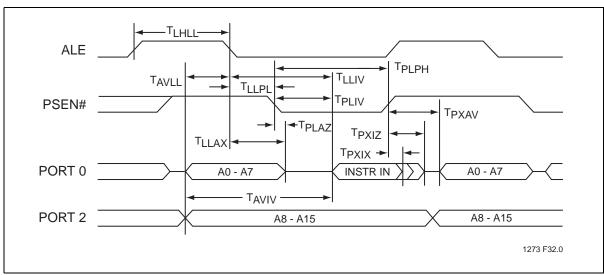

Figure 36: External Program Memory Read Cycle

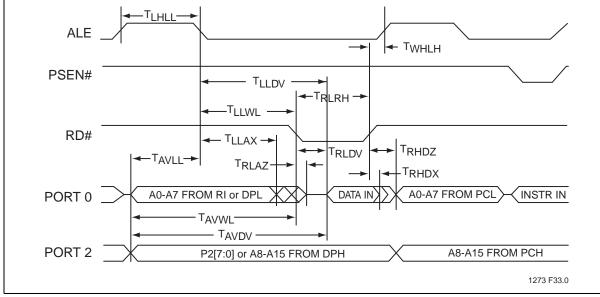

Figure 37: External Data Memory Read Cycle

Data Sheet

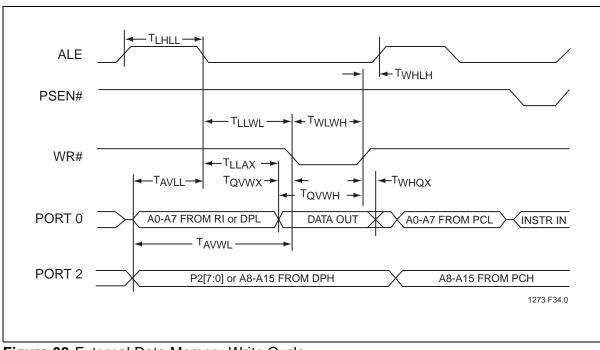

## Figure 38: External Data Memory Write Cycle

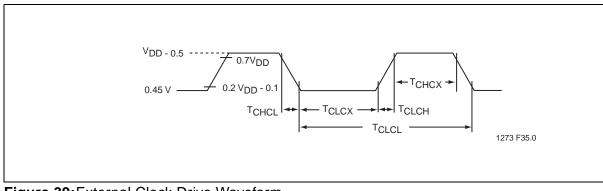

### Table 39: External Clock Drive

|                     |                      |     | Oscillator |      |             |                       |                       |       |  |

|---------------------|----------------------|-----|------------|------|-------------|-----------------------|-----------------------|-------|--|

|                     |                      | 12  | 12MHz      |      | 12MHz 40MHz |                       | Variable              |       |  |

| Symbol              | Parameter            | Min | Max        | Min  | Max         | Min                   | Max                   | Units |  |

| 1/T <sub>CLCL</sub> | Oscillator Frequency |     |            |      |             | 0                     | 40                    | MHz   |  |

| T <sub>CLCL</sub>   |                      | 83  |            | 25   |             |                       |                       | ns    |  |

| T <sub>CHCX</sub>   | High Time            |     |            | 8.75 |             | 0.35T <sub>CLCL</sub> | 0.65T <sub>CLCL</sub> | ns    |  |

| T <sub>CLCX</sub>   | Low Time             |     |            | 8.75 |             | 0.35T <sub>CLCL</sub> | 0.65T <sub>CLCL</sub> | ns    |  |

| T <sub>CLCH</sub>   | Rise Time            |     | 20         |      | 10          |                       |                       | ns    |  |

| T <sub>CHCL</sub>   | Fall Time            |     | 20         |      | 10          |                       |                       | ns    |  |

T0-0.0 25093

### Figure 39: External Clock Drive Waveform

Data Sheet

### Figure 42: Float Waveform

### Figure 43: A Test Load Example

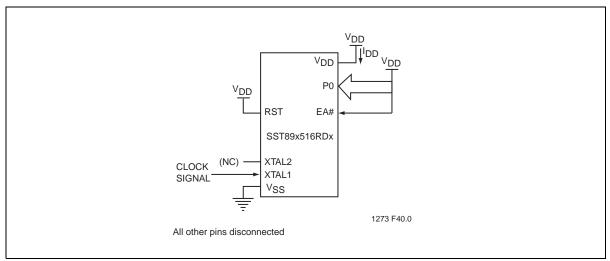

Figure 44:I<sub>DD</sub> Test Condition, Active Mode

Data Sheet

### Valid Combinations

### Valid combinations for SST89E516RD2

SST89E516RD2-40-C-NJE SST89E516RD2-40-C-TQJE

SST89E516RD2-40-I-NJE SST89E516RD2-40-I-TQJE

### Valid combinations for SST89V516RD2

SST89V516RD2-33-C-NJE SST89V516RD2-33-C-TQJE

SST89V516RD2-33-I-NJE SST89V516RD2-33-I-TQJE

### Valid combinations for SST89E516RD

SST89E516RD-40-C-PIE

SST89E516RD-40-C-QIF SST89E516RD-40-I-QIF

### Valid combinations for SST89V516RD

SST89V516RD-33-C-PIE

SST89V516RD-33-C-QIF SST89V516RD-33-I-QIF

**Note:** Valid combinations are those products in mass production or will be in mass production. Consult your SST sales representative to confirm availability of valid combinations and to determine availability of new combinations.