Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | 8051                                                                            |

| Core Size                  | 8-Bit                                                                           |

| Speed                      | 40MHz                                                                           |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                |

| Number of I/O              | 36                                                                              |

| Program Memory Size        | 72KB (72K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                     |

| Data Converters            | -                                                                               |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | 0°C ~ 70°C                                                                      |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-LCC (J-Lead)                                                                 |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89e516rd2-40-c-nje |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Data Sheet

# **Product Description**

The SST89E516RDx and SST89V516RDx are members of the FlashFlex family of 8-bit microcontroller products designed and manufactured with SST's patented and proprietary SuperFlash CMOS semiconductor process technology. The split-gate cell design and thick-oxide tunneling injector offer significant cost and reliability benefits for SST's customers. The devices use the 8051 instruction set and are pin-for-pin compatible with standard 8051 microcontroller devices.

The devices come with 72 KByte of on-chip flash EEPROM program memory which is partitioned into 2 independent program memory blocks. The primary Block 0 occupies 64 KByte of internal program memory space and the secondary Block 1 occupies 8 KByte of internal program memory space.

The 8-KByte secondary block can be mapped to the lowest location of the 64 KByte address space; it can also be hidden from the program counter and used as an independent EEPROM-like data memory.

In addition to the 72 KByte of EEPROM program memory on-chip and 1024 x8 bits of on-chip RAM, the devices can address up to 64 KByte of external program memory and up to 64 KByte of external RAM.

The flash memory blocks can be programmed via a standard 87C5x OTP EPROM programmer fitted with a special adapter and the firmware for SST's devices. During power-on reset, the devices can be configured as either a slave to an external host for source code storage or a master to an external host for an in-application programming (IAP) operation. The devices are designed to be programmed in-system and in-application on the printed circuit board for maximum flexibility. The devices are pre-programmed with an example of the bootstrap loader in the memory, demonstrating the initial user program code loading or subsequent user code updating via the IAP operation. The sample bootstrap loader is available for the user's reference and convenience only; SST does not guarantee its functionality or usefulness. Chip-Erase or Block-Erase operations will erase the pre-programmed sample code.

Data Sheet

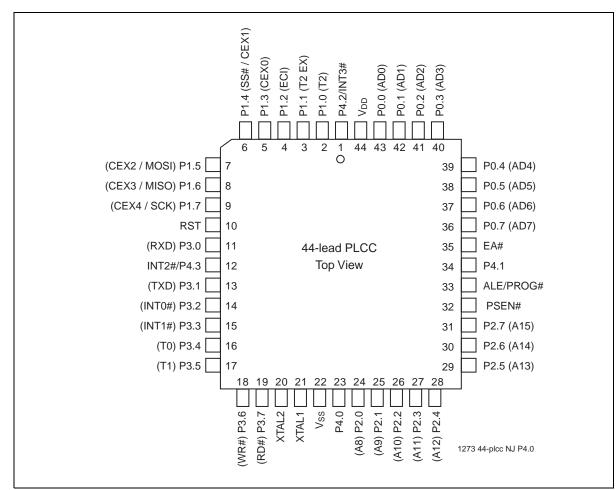

Figure 5: Pin Assignments for 44-lead PLCC

Data Sheet

|        |                            | Direct  |           | Bit Address, Symbol, or Alternative Port Function                  |           |       |                    |                 |                    |                | Reset         |

|--------|----------------------------|---------|-----------|--------------------------------------------------------------------|-----------|-------|--------------------|-----------------|--------------------|----------------|---------------|

| Symbol | Description                | Address | MSB       |                                                                    |           |       |                    |                 |                    | LSB            | Value         |

| SFCF   | SuperFlash                 | B1H     | -         | IAPE                                                               | -         | -     | -                  | -               | SW                 | BSE            | x0xxxx00      |

|        | Configuration              |         |           | Ν                                                                  |           |       |                    |                 | R                  | L              | b             |

| SFCM   | SuperFlash<br>Command      | B2H     | FIE       | FIE FCM[6:0]                                                       |           |       |                    |                 |                    | 00H            |               |

| SFAL   | SuperFlash<br>Address Low  | B3H     | Super     | SuperFlash Low Order Byte Address Register - $A_7$ to $A_0$ (SFAL) |           |       |                    |                 |                    | SFAL)          | 00H           |

| SFAH   | SuperFlash<br>Address High | B4H     | Su        | perFlasł                                                           | n High (  | Order | Byte Add<br>(SFAH) | ress Register - | A <sub>15</sub> to | A <sub>8</sub> | 00H           |

| SFDT   | SuperFlash<br>Data         | B5H     |           | SuperFlash Data Register                                           |           |       |                    |                 |                    | 00H            |               |

| SFST   | SuperFlash<br>Status       | B6H     | SB1<br>_i | SB2_<br>i                                                          | SB3<br>_i | -     | EDC_i              | FLASH_BU<br>SY  | -                  | -              | 000x00xx<br>b |

### Table 7: Flash Memory Programming SFRs

T0-0.0 25093

### Table 8: Watchdog Timer SFRs

|           |                                  | Direct  | Bit Ade | Bit Address, Symbol, or Alternative Port Function |   |            |           |          |     |      | Reset         |

|-----------|----------------------------------|---------|---------|---------------------------------------------------|---|------------|-----------|----------|-----|------|---------------|

| Symbol    | Description                      | Address | MSB     |                                                   |   |            |           |          |     | LSB  | Value         |

| WDTC<br>1 | Watchdog<br>Timer<br>Control     | С0Н     | -       | -                                                 | - | WDOUT      | WDRE      | WDTS     | WDT | SWDT | xxx00x00<br>b |

| WDTD      | Watchdog<br>Timer<br>Data/Reload | 85H     |         |                                                   | ١ | Vatchdog T | imer Data | a/Reload |     |      | 00H           |

1. Bit Addressable SFRs

T0-0.0 25093

Data Sheet

|                   |                                   | Direct  | Bit Add  | dress, Sy   | ymbol, o | r Alterna | ative Port | Functio  | n         |             | Reset         |

|-------------------|-----------------------------------|---------|----------|-------------|----------|-----------|------------|----------|-----------|-------------|---------------|

| Symbol            | Description                       | Address | MSB      |             |          |           |            |          |           | LSB         | Value         |

| TMOD              | Timer/Counter                     | 89H     |          | Tim         | er 1     |           |            | Tii      | mer 0     |             | 00H           |

|                   | Mode Control                      |         | GAT<br>E | C/T#        | M1       | M0        | GATE       | C/<br>T# | M1        | MO          |               |

| TCON <sup>1</sup> | Timer/Counter<br>Control          | 88H     | TF1      | TR1         | TF0      | TR0       | IE1        | IT1      | IE0       | IT0         | 00H           |

| TH0               | Timer 0 MSB                       | 8CH     |          | TH0[7:0]    |          |           |            |          |           |             | 00H           |

| TL0               | Timer 0 LSB                       | 8AH     |          | TL0[7:0]    |          |           |            |          |           |             | 00H           |

| TH1               | Timer 1 MSB                       | 8DH     |          | TH1[7:0]    |          |           |            |          |           | 00H         |               |

| TL1               | Timer 1 LSB                       | 8BH     |          | TL1[7:0]    |          |           |            |          |           | 00H         |               |

| T2CON<br>1        | Timer / Coun-<br>ter 2<br>Control | C8H     | TF2      | EXF<br>2    | RCL<br>K | TCL<br>K  | EXEN<br>2  | TR2      | C/<br>T2# | CP/<br>RL2# | 00H           |

| T2MOD             | Timer2<br>Mode Control            | C9H     | -        | -           | -        | -         | -          | -        | T2O<br>E  | DCEN        | xxxxxx00<br>b |

| TH2               | Timer 2 MSB                       | CDH     |          |             |          | Tł        | H2[7:0]    |          |           |             | 00H           |

| TL2               | Timer 2 LSB                       | ССН     |          |             |          | TI        | _2[7:0]    |          |           |             | 00H           |

| RCAP2<br>H        | Timer 2<br>Capture MSB            | CBH     |          | RCAP2H[7:0] |          |           |            |          |           | 00H         |               |

| RCAP2<br>L        | Timer 2<br>Capture LSB            | CAH     |          |             |          | RCA       | AP2L[7:0]  |          |           |             | 00H           |

### Table 9: Timer/Counters SFRs

1. Bit Addressable SFRs

T0-0.0 25093

### Data Sheet

### Interrupt Priority (IP)

| ·) (·· ) |   |     |     |    |     |     |     |     |             |

|----------|---|-----|-----|----|-----|-----|-----|-----|-------------|

| Location | 7 | 6   | 5   | 4  | 3   | 2   | 1   | 0   | Reset Value |

| B8H      | - | PPC | PT2 | PS | PT1 | PX1 | PT0 | PX0 | x0000000b   |

### Symbol Function

- PT2 Timer 2 interrupt priority bit

- PS Serial Port interrupt priority bit

- PT1 Timer 1 interrupt priority bit

- PX1 External interrupt 1 priority bit

- PT0 Timer 0 interrupt priority bit

- PX0 External interrupt 0 priority bit

### Interrupt Priority High (IPH)

| Location | 7 | 6    | 5    | 4   | 3    | 2    | 1    | 0    | Reset Value |

|----------|---|------|------|-----|------|------|------|------|-------------|

| B7H      | - | PPCH | PT2H | PSH | PT1H | PX1H | PT0H | PX0H | x0000000b   |

### Symbol Function

| PPCH | PCA interrupt priority bit high         |

|------|-----------------------------------------|

| PT2H | Timer 2 interrupt priority bit high     |

| PSH  | Serial Port interrupt priority bit high |

| PT1H | Timer 1 interrupt priority bit high     |

| PX1H | External interrupt 1 priority bit high  |

| PT0H | Timer 0 interrupt priority bit high     |

| PX0H | External interrupt 0 priority bit high  |

### Interrupt Priority 1 (IP1)

| Location | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0 | Reset Value |

|----------|---|---|---|---|-----|-----|-----|---|-------------|

| F8H      | 1 | - | - | 1 | PBO | PX3 | PX2 | 1 | 1xx10001b   |

### Symbol Function

PBO Brown-out interrupt priority bit

PX2 External Interrupt 2 priority bit

PX3 External Interrupt 3 priority bit

### Interrupt Priority 1 High (IP1H)

| Location | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0 | Reset Value |

|----------|---|---|---|---|------|------|------|---|-------------|

| F7H      | 1 | - | - | 1 | PBOH | РХЗН | PX2H | 1 | 1xx10001b   |

### Symbol Function

- PBOH Brown-out Interrupt priority bit high

- PX2H External Interrupt 2 priority bit high

- PX3H External Interrupt 3 priority bit high

Data Sheet

## **Timers/Counters**

### Timers

The device has three 16-bit registers that can be used as either timers or event counters. The three timers/counters are denoted Timer 0 (T0), Timer 1 (T1), and Timer 2 (T2). Each is designated a pair of 8-bit registers in the SFRs. The pair consists of a most significant (high) byte and least significant (low) byte. The respective registers are TL0, TH0, TL1, TH1, TL2, and TH2.

## **Timer Set-up**

Refer to Table 9 for TMOD, TCON, and T2CON registers regarding timers T0, T1, and T2. The following tables provide TMOD values to be used to set up Timers T0, T1, and T2.

Except for the baud rate generator mode, the values given for T2CON do not include the setting of the TR2 bit. Therefore, bit TR2 must be set separately to turn the timer on.

|               |      |                   | TN                            | IOD                           |

|---------------|------|-------------------|-------------------------------|-------------------------------|

|               | Mode | Function          | Internal Control <sup>1</sup> | External Control <sup>2</sup> |

|               | 0    | 13-bit Timer      | 00H                           | 08H                           |

| Used as Timer | 1    | 16-bit Timer      | 01H                           | 09H                           |

|               | 2    | 8-bit Auto-Reload | 02H                           | 0AH                           |

|               | 3    | Two 8-bit Timers  | 03H                           | 0BH                           |

|               | 0    | 13-bit Timer      | 04H                           | 0CH                           |

| Used as       | 1    | 16-bit Timer      | 05H                           | 0DH                           |

| Counter       | 2    | 8-bit Auto-Reload | 06H                           | 0EH                           |

|               | 3    | Two 8-bit Timers  | 07H                           | 0FH                           |

|               |      |                   | •                             | T0-0.0 25093                  |

#### Table 15: Timer/Counter 0

1. The Timer is turned ON/OFF by setting/clearing bit TR0 in the software.

2. The Timer is turned ON/OFF by the 1 to 0 transition on INT0# (P3.2) when TR0 = 1 (hardware control).

### Table 16: Timer/Counter 1

|               |      |                   | TN                            | IOD                           |

|---------------|------|-------------------|-------------------------------|-------------------------------|

|               | Mode | Function          | Internal Control <sup>1</sup> | External Control <sup>2</sup> |

|               | 0    | 13-bit Timer      | 00H                           | 80H                           |

| Used as Timer | 1    | 16-bit Timer      | 10H                           | 90H                           |

|               | 2    | 8-bit Auto-Reload | 20H                           | A0H                           |

|               | 3    | Does not run      | 30H                           | B0H                           |

|               | 0    | 13-bit Timer      | 40H                           | СОН                           |

| Used as       | 1    | 16-bit Timer      | 50H                           | D0H                           |

| Counter       | 2    | 8-bit Auto-Reload | 60H                           | E0H                           |

|               | 3    | Not available     | -                             | -                             |

1. The Timer is turned ON/OFF by setting/clearing bit TR1 in the software.

2. The Timer is turned ON/OFF by the 1 to 0 transition on INT1# (P3.3) when TR1 = 1 (hardware control).

T0-0.0 25093

Data Sheet

|                 |                                                         | T2CON                         |                               |

|-----------------|---------------------------------------------------------|-------------------------------|-------------------------------|

|                 | Mode                                                    | Internal Control <sup>1</sup> | External Control <sup>2</sup> |

|                 | 16-bit Auto-Reload                                      | 00H                           | 08H                           |

|                 | 16-bit Capture                                          | 01H                           | 09H                           |

| Used as Timer   | Baud rate generator receive and transmit same baud rate | 34H                           | 36H                           |

|                 | Receive only                                            | 24H                           | 26H                           |

|                 | Transmit only                                           | 14H                           | 16H                           |

| Used as Counter | 16-bit Auto-Reload                                      | 02H                           | 0AH                           |

| Useu as Counter | 16-bit Capture                                          | 03H                           | 0BH                           |

### Table 17: Timer/Counter 2

1. Capture/Reload occurs only on timer/counter overflow.

T0-0.0 25093

2. Capture/Reload occurs on timer/counter overflow and a 1 to 0 transition on T2EX (P1.1) pin except when Timer 2 is used in the baud rate generating mode.

## **Programmable Clock-Out**

A 50% duty cycle clock can be programmed to come out on P1.0. This pin, besides being a regular I/O pin, has two alternate functions. It can be programmed:

- 1. to input the external clock for Timer/Counter 2, or

- 2. to output a 50% duty cycle clock ranging from 122 Hz to 8 MHz at a 16 MHz operating frequency (61 Hz to 4 MHz in 12 clock mode).

To configure Timer/Counter 2 as a clock generator, bit

C/#T2 (in T2CON) must be cleared and bit T20E in T2MOD must be set. Bit TR2 (T2CON.2) also must be set to start the timer.

The Clock-Out frequency depends on the oscillator frequency and the reload value of Timer 2 capture registers (RCAP2H, RCAP2L) as shown in this equation:

n =2 (in 6 clock mode) 4 (in 12 clock mode)

Where (RCAP2H, RCAP2L) = the contents of RCAP2H and RCAP2L taken as a 16-bit unsigned integer.

In the Clock-Out mode, Timer 2 roll-overs will not generate an interrupt. This is similar to when it is used as a baud-rate generator. It is possible to use Timer 2 as a baud-rate generator and a clock generator simultaneously. Note, however, that the baud-rate and the Clock-Out frequency will not be the same.

Data Sheet

# Serial I/O

## Full-Duplex, Enhanced UART

The device serial I/O port is a full-duplex port that allows data to be transmitted and received simultaneously in hardware by the transmit and receive registers, respectively, while the software is performing other tasks. The transmit and receive registers are both located in the Serial Data Buffer (SBUF) special function register. Writing to the SBUF register loads the transmit register, and reading from the SBUF register obtains the contents of the receive register.

The UART has four modes of operation which are selected by the Serial Port Mode Specifier (SM0 and SM1) bits of the Serial Port Control (SCON) special function register. In all four modes, transmission is initiated by any instruction that uses the SBUF register as a destination register. Reception is initiated in mode 0 when the Receive Interrupt (RI) flag bit of the Serial Port Control (SCON) SFR is cleared and the Reception Enable/ Disable (REN) bit of the SCON register is set. Reception is initiated in the other modes by the incoming start bit if the REN bit of the SCON register is set.

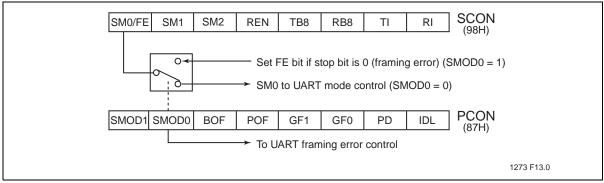

### **Framing Error Detection**

Framing Error Detection is a feature, which allows the receiving controller to check for valid stop bits in modes 1, 2, or 3. Missing stops bits can be caused by noise in serial lines or from simultaneous transmission by two CPUs.

Framing Error Detection is selected by going to the PCON register and changing SMOD0 = 1 (see Figure 17). If a stop bit is missing, the Framing Error bit (FE) will be set. Software may examine the FE bit after each reception to check for data errors. After the FE bit has been set, it can only be cleared by software. Valid stop bits do not clear FE. When FE is enabled, RI rises on the stop bit, instead of the last data bit (see Figure 18 and Figure 19).

Figure 17: Framing Error Block Diagram

Data Sheet

If the user added a third slave such as the example below:

Slave 3

SADDR

=

1111

1001

SADEN

=

1111

0101

GIVEN

=

1111

X0X1

| Select Slave 3 Only |               |                        |  |  |  |

|---------------------|---------------|------------------------|--|--|--|

| Slave 2             | Given Address | Possible Addresses     |  |  |  |

|                     | 1111 X0X1     | 1111 1011<br>1111 1001 |  |  |  |

The user could use the possible addresses above to select slave 3 only. Another combination could be to select slave 2 and 3 only as shown below.

| Select Slaves 2 & 3 Only |                    |  |  |

|--------------------------|--------------------|--|--|

| Slaves 2 & 3             | Possible Addresses |  |  |

|                          | 1111 0011          |  |  |

More than one slave may have the same SADDR address as well, and a given address could be used to modify the address so that it is unique.

#### Using the Broadcast Address to Select Slaves

Using the broadcast address, the master can communicate with all the slaves at once. It is formed by performing a logical OR of SADDR and SADEN with '0's in the result treated as "don't cares".

#### Slave 1

1111 0001 = SADDR +1111 1010 = SADEN 1111 1X11 = Broadcast

"Don't cares" allow for a wider range in defining the broadcast address, but in most cases, the broadcast address will be FFH.

On reset, SADDR and SADEN are "0". This produces an given address of all "don't cares" as well as a broadcast address of all "don't cares." This effectively disables Automatic Addressing mode and allows the microcontroller to function as a standard 8051, which does not make use of this feature.

Data Sheet

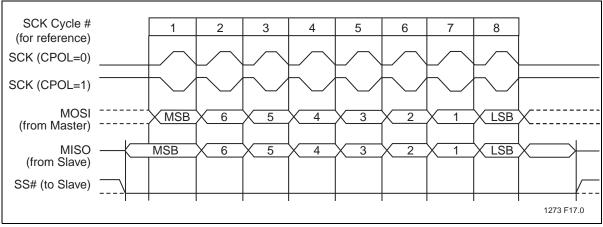

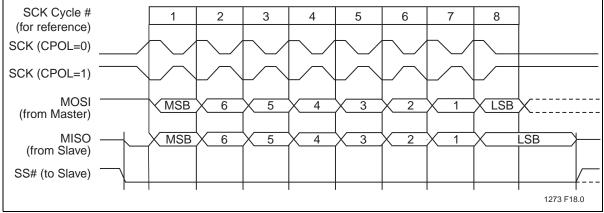

## **SPI Transfer Formats**

Figure 21:SPI Transfer Format with CPHA = 0

Figure 22:SPI Transfer Format with CPHA = 1

Data Sheet

### Table 22: PCA Module Modes

| W  | ithout Inte        | rrupt ena          | bled               |                   |                        |                   |                    |                                                              |

|----|--------------------|--------------------|--------------------|-------------------|------------------------|-------------------|--------------------|--------------------------------------------------------------|

| _1 | ECOMy <sup>2</sup> | CAPPy <sup>2</sup> | CAPNy <sup>2</sup> | MATy <sup>2</sup> | TOGy <sup>2</sup>      | PWMy <sup>2</sup> | ECCFy <sup>2</sup> | Module Code                                                  |

| -  | 0                  | 0                  | 0                  | 0                 | 0                      | 0                 | 0                  | No Operation                                                 |

| -  | 0                  | 1                  | 0                  | 0                 | 0                      | 0                 | 0                  | 16-bit capture on positive-edge trigger at CEX[4:0]          |

| -  | 0                  | 0                  | 1                  | 0                 | 0                      | 0                 | 0                  | 16-bit capture on negative-edge trigger at CEX[4:0]          |

| -  | 0                  | 1                  | 1                  | 0                 | 0                      | 0                 | 0                  | 16-bit capture on positive/negative-edge trigger at CEX[4:0] |

| -  | 1                  | 0                  | 0                  | 1                 | 0                      | 0                 | 0                  | Compare: software timer                                      |

| -  | 1                  | 0                  | 0                  | 1                 | 1                      | 0                 | 0                  | Compare: high-speed output                                   |

| -  | 1                  | 0                  | 0                  | 0                 | 0                      | 1                 | 0                  | Compare: 8-bit PWM                                           |

| -  | 1                  | 0                  | 0                  | 1                 | 0 or<br>1 <sup>3</sup> | 0                 | 0                  | Compare: PCA WDT (CCAPM4 only) <sup>4</sup>                  |

T0-0.0 25093

1. User should not write '1's to reserved bits. The value read from a reserved bit is indeterminate.

2. y = 0, 1, 2, 3, 4

3. A 0 disables toggle function. A 1 enables toggle function on CEX[4:0] pin.

4. For PCA WDT mode, also set the WDTE bit in the CMOD register to enable the reset output signal.

| Wi | th Interrup        | t enabled          |                    |                   |                     |                   |                    |                                                                     |

|----|--------------------|--------------------|--------------------|-------------------|---------------------|-------------------|--------------------|---------------------------------------------------------------------|

| _1 | ECOMy <sup>2</sup> | CAPPy <sup>2</sup> | CAPNy <sup>2</sup> | MATy <sup>2</sup> | TOGy <sup>2</sup>   | PWMy <sup>2</sup> | ECCFy <sup>2</sup> | Module Code                                                         |

| -  | 0                  | 1                  | 0                  | 0                 | 0                   | 0                 | 1                  | 16-bit capture on positive-edge trig-<br>ger at CEX[4:0]            |

| -  | 0                  | 0                  | 1                  | 0                 | 0                   | 0                 | 1                  | 16-bit capture on negative-edge trig-<br>ger at CEX[4:0]            |

| -  | 0                  | 1                  | 1                  | 0                 | 0                   | 0                 | 1                  | 16-bit capture on positive/negative-<br>edge<br>trigger at CEX[4:0] |

| -  | 1                  | 0                  | 0                  | 1                 | 0                   | 0                 | 1                  | Compare: software timer                                             |

| -  | 1                  | 0                  | 0                  | 1                 | 1                   | 0                 | 1                  | Compare: high-speed output                                          |

| -  | 1                  | 0                  | 0                  | 0                 | 0                   | 1                 | X <sup>3</sup>     | Compare: 8-bit PWM                                                  |

| -  | 1                  | 0                  | 0                  | 1                 | 0 or 1 <sup>4</sup> | 0                 | X <sup>5</sup>     | Compare: PCA WDT (CCAPM4 only) <sup>6</sup>                         |

### Table 23: PCA Module Modes

T0-0.0 25093

1. User should not write '1's to reserved bits. The value read from a reserved bit is indeterminate.

2. y = 0, 1, 2, 3, 4

3. No PCA interrupt is needed to generate the PWM.

4. A 0 disables toggle function. A 1 enables toggle function on CEX[4:0] pin.

5. Enabling an interrupt for the Watchdog Timer would defeat the purpose of the Watchdog Timer.

6. For PCA WDT mode, also set the WDTE bit in the CMOD register to enable the reset output signal.

Data Sheet

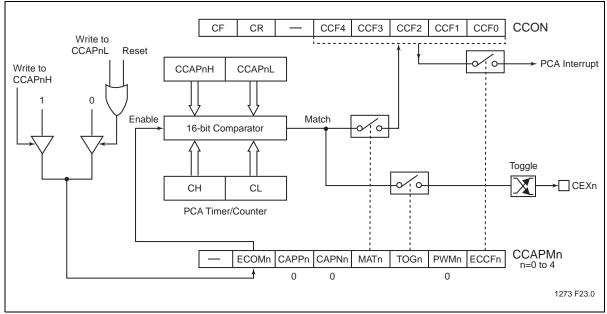

Figure 27: PCA High Speed Output Mode

### **Pulse Width Modulator**

The Pulse Width Modulator (PWM) mode is used to generate 8-bit PWMs by comparing the low byte of the PCA timer (CL) with the low byte of the compare register (CCAPnL). When CL < CCAPnL the output is low. When  $CL \ge CCAPnL$  the output is high. To activate this mode, the user must set the PWM and ECOM bits in the module's CCAPMn SFR. (See Figure 28 and Table 24)

In PWM mode, the frequency of the output depends on the source for the PCA timer. Since there is only one set of CH and CL registers, all modules share the PCA timer and frequency. Duty cycle of the output is controlled by the value loaded into the high byte (CCAPnH). Since writes to the CCAPnH register are asynchronous, a new value written to the high byte will not be shifted into CCAPnL for comparison until the next period of the output (when CL rolls over from 255 to 00).

To calculate values for CCAPnH for any duty cycle, use the following equation:

CCAPnH = 256(1 - Duty Cycle)

where CCAPnH is an 8-bit integer and Duty Cycle is a fraction.

Data Sheet

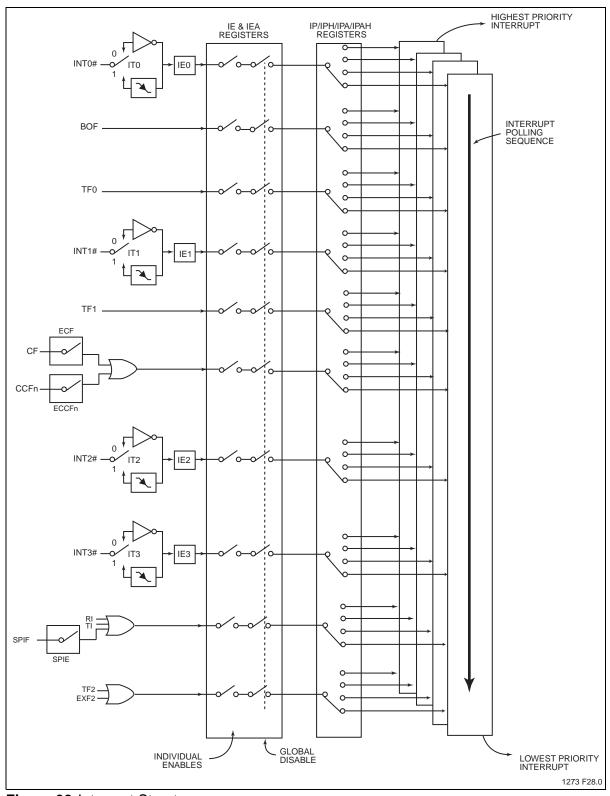

## Figure 32: Interrupt Structure

Data Sheet

# System Clock and Clock Options

## **Clock Input Options and Recommended Capacitor Values for Oscillator**

Shown in Figure 33 are the input and output of an internal inverting amplifier (XTAL1, XTAL2), which can be configured for use as an on-chip oscillator.

When driving the device from an external clock source, XTAL2 should be left disconnected and XTAL1 should be driven.

At start-up, the external oscillator may encounter a higher capacitive load at XTAL1 due to interaction between the amplifier and its feedback capacitance. However, the capacitance will not exceed 15 pF once the external signal meets the  $V_{IL}$  and  $V_{IH}$  specifications.

Crystal manufacturer, supply voltage, and other factors may cause circuit performance to differ from one application to another. C1 and C2 should be adjusted appropriately for each design. Table 29, shows the typical values for C1 and C2 vs. crystal type for various frequencies

### Table 29: Recommended Values for C1 and C2 by Crystal Type

| Crystal | C1 = C2 |

|---------|---------|

| Quartz  | 20-30pF |

| Ceramic | 40-50pF |

T0-0.0 25093

More specific information about on-chip oscillator design can be found in the *FlashFlex Oscillator Circuit Design Considerations* application note.

## **Clock Doubling Option**

By default, the device runs at 12 clocks per machine cycle (x1 mode). The device has a clock doubling option to speed up to 6 clocks per machine cycle. Please refer to Table 30 for detail.

Clock double mode can be enabled either via the external host mode or the IAP mode. Please refer to Table 14 for the IAP mode enabling commands (When set, the EDC# bit in SFST register will indicate 6 clock mode.).

The clock double mode is only for doubling the internal system clock and the internal flash memory, i.e. EA#=1. To access the external memory and the peripheral devices, careful consideration must be taken. Also note that the crystal output (XTAL2) will not be doubled.

Data Sheet

## **DC Electrical Characteristics**

| Symbol           | Parameter                                                      | Test Conditions                        | Min                         | Max                         | Units |

|------------------|----------------------------------------------------------------|----------------------------------------|-----------------------------|-----------------------------|-------|

| VIL              | Input Low Voltage                                              | 4.5 < V <sub>DD</sub> < 5.5            | -0.5                        | 0.2V <sub>DD</sub> -<br>0.1 | V     |

| V <sub>IH</sub>  | Input High Voltage                                             | 4.5 < V <sub>DD</sub> < 5.5            | 0.2V <sub>DD</sub> +<br>0.9 | V <sub>DD</sub> + 0.5       | V     |

| V <sub>IH1</sub> | Input High Voltage (XTAL1, RST)                                | $4.5 < V_{DD} < 5.5$                   | $0.7V_{DD}$                 | V <sub>DD</sub> + 0.5       | V     |

| V <sub>OL</sub>  | Output Low Voltage (Ports 1.5, 1.6, 1.7)                       | $V_{DD} = 4.5V$                        |                             |                             |       |

|                  |                                                                | $I_{OL} = 16 \text{mA}$                |                             | 1.0                         | V     |

| V <sub>OL</sub>  | Output Low Voltage (Ports 1, 2, 3) <sup>1</sup>                | $V_{DD} = 4.5V$                        |                             |                             |       |

|                  |                                                                | $I_{OL} = 100 \mu A^2$                 |                             | 0.3                         | V     |

|                  |                                                                | $I_{OL} = 1.6 m A^2$                   |                             | 0.45                        | V     |

|                  |                                                                | $I_{OL} = 3.5 \text{mA}^2$             |                             | 1.0                         | V     |

| V <sub>OL1</sub> | Output Low Voltage (Port 0, ALE,                               | $V_{DD} = 4.5V$                        |                             |                             |       |

|                  | PSEN#) <sup>1,3</sup>                                          | $I_{OL} = 200 \mu A^2$                 |                             | 0.3                         | V     |

|                  |                                                                | $I_{OL} = 3.2 \text{mA}^2$             |                             | 0.45                        | V     |

| V <sub>OH</sub>  | Output High Voltage (Ports 1, 2, 3, ALE,                       | $V_{DD} = 4.5V$                        |                             |                             |       |

|                  | PSEN#) <sup>4</sup>                                            | I <sub>OH</sub> = -10μA                | V <sub>DD</sub> - 0.3       |                             | V     |

|                  |                                                                | I <sub>OH</sub> = -30μA                | V <sub>DD</sub> - 0.7       |                             | V     |

|                  |                                                                | I <sub>OH</sub> = -60μA                | V <sub>DD</sub> - 1.5       |                             | V     |

| V <sub>OH1</sub> | Output High Voltage (Port 0 in External                        | $V_{DD} = 4.5V$                        |                             |                             |       |

|                  | Bus Mode) <sup>4</sup>                                         | I <sub>OH</sub> = -200μA               | V <sub>DD</sub> - 0.3       |                             | V     |

|                  |                                                                | I <sub>OH</sub> = -3.2mA               | V <sub>DD</sub> - 0.7       |                             | V     |

| V <sub>BOD</sub> | Brown-out Detection Voltage                                    |                                        | 3.85                        | 4.15                        | V     |

| IIL              | Logical 0 Input Current (Ports 1, 2, 3)                        | $V_{IN} = 0.4V$                        |                             | -75                         | μA    |

| I <sub>TL</sub>  | Logical 1-to-0 Transition Current (Ports 1, 2, 3) <sup>5</sup> | $V_{IN} = 2V$                          |                             | -650                        | μA    |

| ILI              | Input Leakage Current (Port 0)                                 | $0.45 < V_{IN} < V_{DD}$ -0.3          |                             | ±10                         | μA    |

| R <sub>RST</sub> | RST Pull-down Resistor                                         |                                        | 40                          | 225                         | KΩ    |

| C <sub>IO</sub>  | Pin Capacitance <sup>6</sup>                                   | @ 1 MHz, 25°C                          |                             | 15                          | pF    |

| I <sub>DD</sub>  | Power Supply Current                                           |                                        |                             |                             |       |

|                  | IAP Mode                                                       |                                        |                             |                             |       |

|                  | @ 40 MHz                                                       |                                        |                             | 88                          | mA    |

|                  | Active Mode                                                    |                                        |                             |                             |       |

|                  | @ 40 MHz                                                       |                                        |                             | 50                          | mA    |

|                  | Idle Mode                                                      |                                        |                             |                             |       |

|                  | @ 40 MHz                                                       |                                        |                             | 42                          | mA    |

|                  | Power-down Mode (min. $V_{DD} = 2V$ )                          | $T_A = 0^{\circ}C$ to +70°C            |                             | 80                          | μA    |

|                  |                                                                | $T_A = -40^{\circ}C$ to $+85^{\circ}C$ |                             | 90                          | μA    |

#### **Table 36:** DC Electrical Characteristics for SST89E516RDx $T_{A} = -40^{\circ}$ C to $+85^{\circ}$ C: $V_{DD} = 4.5 \cdot 5.5$ V: $V_{SS} = 0$ V

T0-0.1 25093

Data Sheet

### **Table 37:** DC Electrical Characteristics for SST89V516RDx $T_A = -40^{\circ}$ C to +85°C; $V_{DD} = 2.7-3.6$ V; $V_{SS} = 0$ V

| Symbo            | Denometer                                                      | Test Canditians                                 | Min                         | Max                      | Unit |

|------------------|----------------------------------------------------------------|-------------------------------------------------|-----------------------------|--------------------------|------|

| <b>I</b>         | Parameter                                                      | Test Conditions                                 | Min                         | Max                      | S    |

| VIL              | Input Low Voltage                                              | 2.7 < V <sub>DD</sub> < 3.6                     | -0.5                        | 0.7                      | V    |

| Vih              | Input High Voltage                                             | $2.7 < V_{DD} < 3.6$                            | 0.2V <sub>DD</sub> +<br>0.9 | V <sub>DD</sub> +<br>0.5 | V    |

| V <sub>IH1</sub> | Input High Voltage (XTAL1, RST)                                | $2.7 < V_{DD} < 3.6$                            | $0.7V_{DD}$                 | V <sub>DD</sub> +<br>0.5 | V    |

| V <sub>OL</sub>  | Output Low Voltage (Ports 1.5, 1.6, 1.7)                       | V <sub>DD</sub> = 2.7V                          |                             |                          |      |

|                  |                                                                | I <sub>OL</sub> = 16mA                          |                             | 1.0                      | V    |

| V <sub>OL</sub>  | Output Low Voltage (Ports 1, 2, 3) <sup>1</sup>                | V <sub>DD</sub> = 2.7V                          |                             |                          |      |

|                  |                                                                | $I_{OL} = 100 \mu A^2$                          |                             | 0.3                      | V    |

|                  |                                                                | $I_{OL} = 1.6 \text{mA}^2$                      |                             | 0.45                     | V    |

|                  |                                                                | $I_{OL} = 3.5 \text{mA}^2$                      |                             | 1.0                      | V    |

| V <sub>OL1</sub> | Output Low Voltage (Port 0, ALE, PSEN#) <sup>1,3</sup>         | V <sub>DD</sub> = 2.7V                          |                             |                          |      |

|                  |                                                                | $I_{OL} = 200 \mu A^2$                          |                             | 0.3                      | V    |

|                  |                                                                | $I_{OL} = 3.2 \text{mA}^2$                      |                             | 0.45                     | V    |

| Voн              | Output High Voltage (Ports 1, 2, 3, ALE,                       | $V_{DD} = 2.7V$                                 |                             |                          |      |

|                  | PSEN#) <sup>4</sup>                                            | I <sub>OH</sub> = -10μA                         | V <sub>DD</sub> - 0.3       |                          | V    |

|                  |                                                                | I <sub>OH</sub> = -30µА                         | V <sub>DD</sub> - 0.7       |                          | V    |

|                  |                                                                | I <sub>OH</sub> = -60μA                         | V <sub>DD</sub> - 1.5       |                          | V    |

| V <sub>OH1</sub> | Output High Voltage (Port 0 in External Bus                    | V <sub>DD</sub> = 2.7V                          |                             |                          |      |

|                  | Mode) <sup>4</sup>                                             | I <sub>OH</sub> = -200μA                        | V <sub>DD</sub> - 0.3       |                          | V    |

|                  |                                                                | I <sub>OH</sub> = -3.2mA                        | V <sub>DD</sub> - 0.7       |                          | V    |

| V <sub>BOD</sub> | Brown-out Detection Voltage                                    |                                                 | 2.35                        | 2.55                     | V    |

| IIL              | Logical 0 Input Current (Ports 1, 2, 3)                        | $V_{IN} = 0.4V$                                 |                             | -75                      | μA   |

| I <sub>TL</sub>  | Logical 1-to-0 Transition Current (Ports 1, 2, 3) <sup>5</sup> | $V_{IN} = 2V$                                   |                             | -650                     | μA   |

| ILI              | Input Leakage Current (Port 0)                                 | $0.45 < V_{IN} < V_{DD}$ -0.3                   |                             | ±10                      | μA   |

| R <sub>RST</sub> | RST Pull-down Resistor                                         |                                                 |                             | 225                      | KΩ   |

| C <sub>IO</sub>  | Pin Capacitance <sup>6</sup>                                   | @ 1 MHz, 25°C                                   |                             | 15                       | pF   |

| I <sub>DD</sub>  | Power Supply Current                                           |                                                 |                             |                          |      |

|                  | IAP Mode                                                       |                                                 |                             |                          |      |

|                  | @ 33 MHz                                                       |                                                 |                             | 47                       | mA   |

|                  | Active Mode                                                    |                                                 |                             |                          |      |

|                  | @ 33 MHz                                                       |                                                 |                             | 30                       | mA   |

|                  | Idle Mode                                                      |                                                 |                             |                          |      |

|                  | @ 33 MHz                                                       |                                                 |                             | 21                       | mA   |

|                  | Power-down Mode (min. V <sub>DD</sub> = 2V)                    | $T_A = 0^{\circ}C$ to +70°C                     |                             | 45                       | μA   |

|                  |                                                                | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$ |                             | 55                       | μA   |

T0-0.1 25093

Data Sheet

|                   |                                                | Oscillator |                                                 |            |                                               |                                                              |                                                              |       |  |

|-------------------|------------------------------------------------|------------|-------------------------------------------------|------------|-----------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|-------|--|

|                   |                                                | M<br>16 M  | IHz (x1<br>ode)<br>IHz (x2<br>ode) <sup>1</sup> | Мс<br>20 М | Hz (x1<br>ode)<br>Hz (x2<br>ode) <sup>1</sup> | Var                                                          | iable                                                        |       |  |

| Symbol            | Parameter                                      | Min        | Max                                             | Min        | Мах                                           | Min                                                          | Max                                                          | Units |  |

|                   |                                                |            |                                                 |            | 75                                            |                                                              | 5T <sub>CLCL</sub> - 50 (5V)                                 | ns    |  |

| T <sub>RHDX</sub> | Data Hold After RD#                            | 0          |                                                 | 0          |                                               | 0                                                            |                                                              | ns    |  |

| T <sub>RHDZ</sub> | Data Float After RD#                           |            | 36                                              |            |                                               |                                                              | 2T <sub>CLCL</sub> - 25 (3V)                                 | ns    |  |

|                   |                                                |            |                                                 |            | 38                                            |                                                              | 2T <sub>CLCL</sub> - 12 (5V)                                 | ns    |  |

| T <sub>LLDV</sub> | ALE Low to Valid Data In                       |            | 152                                             |            |                                               |                                                              | 8T <sub>CLCL</sub> - 90 (3V)                                 | ns    |  |

|                   |                                                |            |                                                 |            | 150                                           |                                                              | 8T <sub>CLCL</sub> - 50 (5V)                                 | ns    |  |

| T <sub>AVDV</sub> | Address to Valid Data In                       |            | 183                                             |            |                                               |                                                              | 9T <sub>CLCL</sub> - 90 (3V)                                 | ns    |  |

|                   |                                                |            |                                                 |            | 150                                           |                                                              | 9T <sub>CLCL</sub> - 75 (5V)                                 | ns    |  |

| T <sub>LLWL</sub> | ALE Low to RD# or WR#<br>Low                   | 66         | 116                                             | 60         | 90                                            | 3T <sub>CLCL</sub> - 25 (3V)<br>3T <sub>CLCL</sub> - 15 (5V) | 3T <sub>CLCL</sub> + 25 (3V)<br>3T <sub>CLCL</sub> + 15 (5V) | ns    |  |

| T <sub>AVWL</sub> | Address to RD# or WR#<br>Low                   | 46         |                                                 |            |                                               | 4T <sub>CLCL</sub> - 75 (3V)                                 |                                                              | ns    |  |

|                   |                                                |            |                                                 | 70         |                                               | 4T <sub>CLCL</sub> - 30 (5V)                                 |                                                              | ns    |  |

| T <sub>WHQX</sub> | Data Hold After WR#                            | 3          |                                                 |            |                                               | T <sub>CLCL</sub> - 27 (3V)                                  |                                                              | ns    |  |

|                   |                                                |            |                                                 | 5          |                                               | T <sub>CLCL</sub> - 20 (5V)                                  |                                                              | ns    |  |

| T <sub>QVWH</sub> | Data Valid to WR# High                         | 142        |                                                 |            |                                               | 7T <sub>CLCL</sub> - 70 (3V)                                 |                                                              | ns    |  |

|                   |                                                |            |                                                 | 125        |                                               | 7T <sub>CLCL</sub> - 50 (5V)                                 |                                                              | ns    |  |

| T <sub>QVWX</sub> | Data Valid to WR# High to<br>Low<br>Transition | 10         |                                                 | 5          |                                               | T <sub>CLCL</sub> - 20                                       |                                                              | ns    |  |

| T <sub>RLAZ</sub> | RD# Low to Address Float                       |            | 0                                               |            | 0                                             |                                                              | 0                                                            | ns    |  |

| T <sub>WHLH</sub> | RD# to WR# High to ALE<br>High                 | 5          | 55                                              |            |                                               | T <sub>CLCL</sub> - 25 (3V)                                  | T <sub>CLCL</sub> + 25 (3V)                                  | ns    |  |

|                   |                                                |            |                                                 | 10         | 40                                            | T <sub>CLCL</sub> - 15 (5V)                                  | T <sub>CLCL</sub> + 15 (5V)                                  | ns    |  |

**Table 38:** AC Electrical Characteristics (Continued) (2 of 2)  $T_4 = -40^{\circ}$ C to  $+85^{\circ}$ C.  $V_{DD} = 2.7-3.6V/@33MHz = 4.5-5.5V/@40MHz = 0V$

1. Calculated values are for x1 Mode only

T0-0.0 25093

Data Sheet

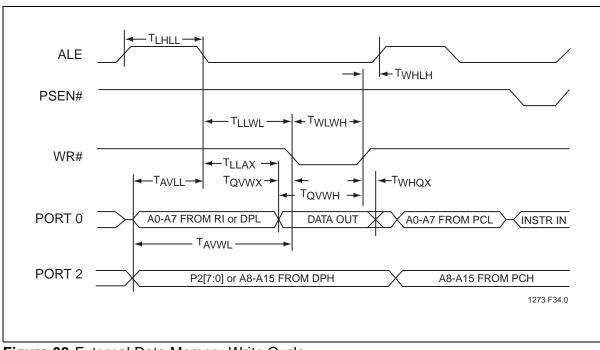

## Figure 38: External Data Memory Write Cycle

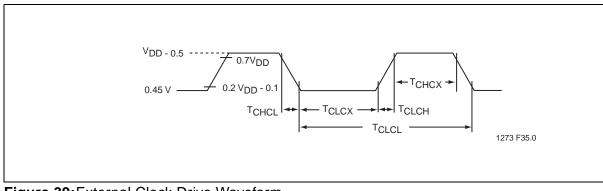

### Table 39: External Clock Drive

|                     |                      |       | Oscillator |       |     |                       |                       |       |

|---------------------|----------------------|-------|------------|-------|-----|-----------------------|-----------------------|-------|

|                     |                      | 12MHz |            | 40MHz |     | Variable              |                       |       |

| Symbol              | Parameter            | Min   | Max        | Min   | Max | Min                   | Max                   | Units |

| 1/T <sub>CLCL</sub> | Oscillator Frequency |       |            |       |     | 0                     | 40                    | MHz   |

| T <sub>CLCL</sub>   |                      | 83    |            | 25    |     |                       |                       | ns    |

| T <sub>CHCX</sub>   | High Time            |       |            | 8.75  |     | 0.35T <sub>CLCL</sub> | 0.65T <sub>CLCL</sub> | ns    |

| T <sub>CLCX</sub>   | Low Time             |       |            | 8.75  |     | 0.35T <sub>CLCL</sub> | 0.65T <sub>CLCL</sub> | ns    |

| T <sub>CLCH</sub>   | Rise Time            |       | 20         |       | 10  |                       |                       | ns    |

| T <sub>CHCL</sub>   | Fall Time            |       | 20         |       | 10  |                       |                       | ns    |

T0-0.0 25093

### Figure 39: External Clock Drive Waveform

Data Sheet

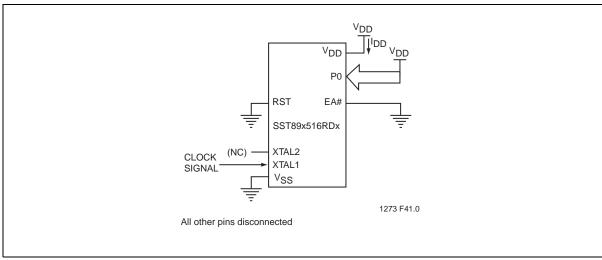

Figure 45:I<sub>DD</sub> Test Condition, Idle Mode

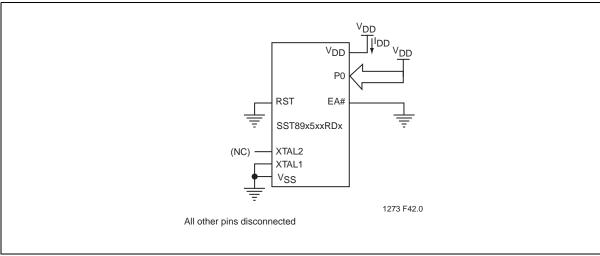

Figure 46:I<sub>DD</sub> Test Condition, Power-down Mode

| Table 41: Flash Memory Prog | ramming/Verification Parameters <sup>1</sup> |

|-----------------------------|----------------------------------------------|

|-----------------------------|----------------------------------------------|

| Parameter <sup>2</sup>              | Max | Units      |

|-------------------------------------|-----|------------|

| Chip-Erase Time                     | 150 | ms         |

| Block-Erase Time                    | 100 | ms         |

| Sector-Erase Time                   | 30  | ms         |

| Byte-Program Time <sup>3</sup>      | 50  | μs         |

| Select-Block Program Time           | 500 | ns         |

| Re-map or Security bit Program Time | 80  | μs         |

|                                     |     | T0-0.1 250 |

1. For IAP operations, the program execution overhead must be added to the above timing parameters.

2. Program and Erase times will scale inversely proportional to programming clock frequency.

3. Each byte must be erased before programming.

### Data Sheet

Figure 49:44-lead Plastic Lead Chip Carrier (PLCC) SST Package Code: NJ