Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | 8051                                                                             |

| Core Size                  | 8-Bit                                                                            |

| Speed                      | 40MHz                                                                            |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                 |

| Number of I/O              | 36                                                                               |

| Program Memory Size        | 72KB (72K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            |                                                                                  |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | 0°C ~ 70°C                                                                       |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89e516rd2-40-c-tqje |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Data Sheet

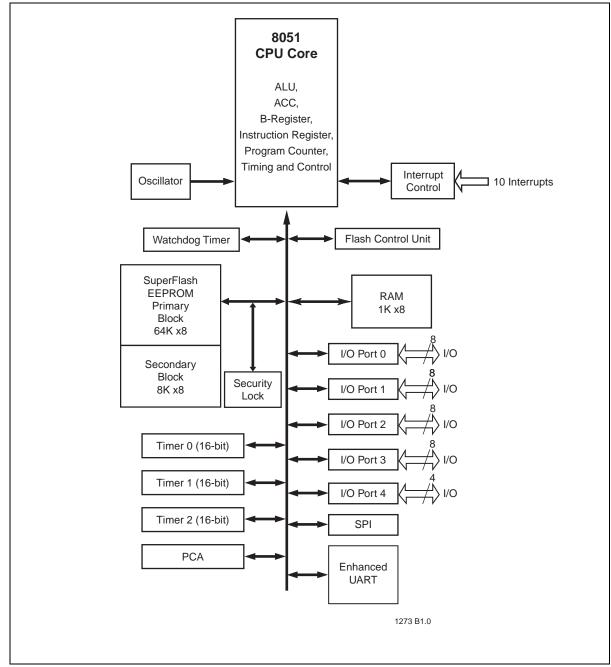

### **Functional Blocks**

Figure 1: Functional Block Diagram

Data Sheet

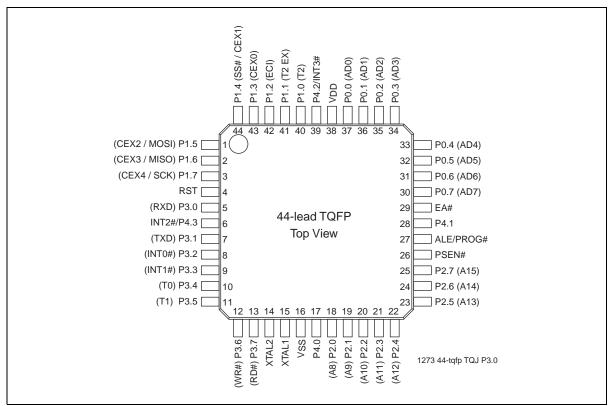

Figure 4: Pin Assignments for 44-lead TQFP

Data Sheet

| Table 1: | Pin Descriptions | (Continued) | (2 of 3) |

|----------|------------------|-------------|----------|

|----------|------------------|-------------|----------|

| Symbol               | Type <sup>1</sup>               | Name and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3[7:0]              | I/O with inter-<br>nal pull-up  | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 3 output buffers can drive LS TTL inputs. Port 3 pins are pulled high by the internal pull-ups when "1"s are written to them and can be used as inputs in this state. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups. Port 3 also receives some control signals and a partial of high-order address bits during the external host mode programming and verification.                                                                                 |

| P3[0]                | I                               | RXD: Universal Asynchronous Receiver/Transmitter (UART) - Receive input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P3[1]                | 0                               | TXD: UART - Transmit output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P3[2]                | I                               | INT0#: External Interrupt 0 Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P3[3]                | I                               | INT1#: External Interrupt 1 Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P3[4]                | I                               | T0: External count input to Timer/Counter 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P3[5]                | I                               | T1: External count input to Timer/Counter 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P3[6]                | 0                               | WR#: External Data Memory Write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P3[7]                | 0                               | RD#: External Data Memory Read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PSEN#                | I/O                             | <b>Program Store Enable:</b> PSEN# is the Read strobe to External Program Store.<br>When the device is executing from Internal Program Memory, PSEN# is inactive $(V_{OH})$ . When the device is executing code from External Program Memory, PSEN# is activated twice each machine cycle, except when access to External Data Memory while one PSEN# activation is skipped in each machine cycle. A forced high-to-low input transition on the PSEN# pin while the RST input is continually held high for more than ten machine cycles will cause the device to enter External Host mode for programming. |

| RST                  | 1                               | <b>Reset:</b> While the oscillator is running, a high logic state on this pin for two machine cycles will reset the device. After a reset, if the PSEN# pin is driven by a high-to-low input transition while the RST input pin is held high, the device will enter the External Host mode, otherwise the device will enter the Normal operation mode.                                                                                                                                                                                                                                                     |

| EA#                  | I                               | <b>External Access Enable:</b> EA# must be driven to $V_{IL}$ in order to enable the device to fetch code from the External Program Memory. EA# must be driven to $V_{IH}$ for internal program execution. However, Security lock level 4 will disable EA#, and program execution is only possible from internal program memory. The EA# pin can tolerate a high voltage <sup>2</sup> of 12V.                                                                                                                                                                                                              |

| ALE/<br>PROG#        | I/O                             | Address Latch Enable: ALE is the output signal for latching the low byte of the address during an access to external memory. This pin is also the programming pulse input (PROG#) for flash programming. Normally the ALE <sup>3</sup> is emitted at a constant rate of 1/6 the crystal frequency <sup>4</sup> and can be used for external timing and clocking. One ALE pulse is skipped during each access to external data memory However, if AO is set to 1, ALE is disabled.                                                                                                                          |

| P4[3:0] <sup>5</sup> | I/O with inter-<br>nal pull-ups | <b>Port 4:</b> Port 4 is an 4-bit bi-directional I/O port with internal pull-ups. The port 4 output buffers can drive LS TTL inputs. Port 4 pins are pulled high by the interna pull-ups when '1's are written to them and can be used as inputs in this state. As inputs, port 4 pins that are externally pulled low will source current because of the internal pull-ups.                                                                                                                                                                                                                                |

| P4[0]                | I/O                             | Bit 0 of port 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P4[1]                | I/O                             | Bit 1 of port 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P4[2] /<br>INT3#     | I/O                             | Bit 2 of port 4 / INT3# External interrupt 3 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Data Sheet

### Program Memory Block Switching

The program memory block switching feature of the device allows either Block 1 or the lowest 8 KByte of Block 0 to be used for the lowest 8 KByte of the program address space. SFCF[1:0] controls program memory block switching.

### Table 2: SFCF Values for Program Memory Block Switching

| SFCF[1:0]  | Program Memory Block Switching                                                                                                                                                                                                                                                                                                                              |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01, 10, 11 | Block 1 is not visible to the program counter (PC).<br>Block 1 is reachable only via in-application programming from 0000H - 1FFFH.                                                                                                                                                                                                                         |

| 00         | Block 1 is overlaid onto the low 8K of the program address space; occupying address locations 0000H - 1FFFH.<br>When the PC falls within 0000H - 1FFFH, the instruction will be fetched from Block 1 instead of Block 0.<br>Outside of 0000H - 1FFFH, Block 0 is used. Locations 0000H - 1FFFH of Block 0 are reachable through in-application programming. |

T0-0.0 25093

### **Reset Configuration of Program Memory Block Switching**

Program memory block switching is initialized after reset according to the state of the Start-up Configuration bit SC0. The SC0 bit is programmed via an external host mode command or an IAP Mode command. See Table 14.

Once out of reset, the SFCF[0] bit can be changed dynamically by the program for desired effects. Changing SFCF[0] will not change the SC0 bit.

Caution must be taken when dynamically changing the SFCF[0] bit. Since this will cause different physical memory to be mapped to the logical program address space. The user must avoid executing block switching instructions within the address range 0000H to 1FFFH.

|                  | State of SFCF[1:0] after:           |                                       |                   |  |  |  |  |  |

|------------------|-------------------------------------|---------------------------------------|-------------------|--|--|--|--|--|

| SC0 <sup>1</sup> | Power-on<br>or<br>External<br>Reset | WDT Reset<br>or<br>Brown-out<br>Reset | Software<br>Reset |  |  |  |  |  |

| U (1)            | 00<br>(default)                     | x0                                    | 10                |  |  |  |  |  |

| P (0)            | 01                                  | x1                                    | 11                |  |  |  |  |  |

| ·                |                                     |                                       | T0-0.0 250        |  |  |  |  |  |

**Table 3:** SFCF Values Under Different Reset Conditions

1. P = Programmed (Bit logic state = 0),

U = Unprogrammed (Bit logic state = 1)

### Data RAM Memory

The data RAM has 1024 bytes of internal memory. The RAM can be addressed up to 64KB for external data memory.

Data Sheet

| Symbol           | Description                           | Direct<br>Address | MSB       | Bit Addre | ss, Syrr | nbol, or | Alternat | ive Port | Function   | LSB      | Reset<br>Value |

|------------------|---------------------------------------|-------------------|-----------|-----------|----------|----------|----------|----------|------------|----------|----------------|

| ACC <sup>1</sup> | Accumulator                           | E0H               |           | ACC[7:0]  |          |          |          |          |            |          | 00H            |

| B <sup>1</sup>   | B Register                            | F0H               |           |           |          | B[       | 7:0]     |          |            |          | 00H            |

| PSW <sup>1</sup> | Program Sta-<br>tus<br>Word           | D0H               | CY        | AC        | F0       | RS<br>1  | RS0      | OV       | F1         | Р        | 00H            |

| SP               | Stack Pointer                         | 81H               |           |           |          | SP       | [7:0]    |          |            | •        | 07H            |

| DPL              | Data Pointer<br>Low                   | 82H               |           |           |          | DPI      | L[7:0]   |          |            |          | 00H            |

| DPH              | Data Pointer<br>High                  | 83H               |           |           |          | DPI      | H[7:0]   |          |            |          | 00H            |

| IE <sup>1</sup>  | Interrupt<br>Enable                   | A8H               | EA        | EC        | ET2      | ES       | ET1      | EX1      | ET0        | EX0      | 00H            |

| IEA <sup>1</sup> | Interrupt<br>Enable A                 | E8H               | -         | -         | -        | -        | EBO      | -        | -          | -        | xxxx0xxx<br>b  |

| IP <sup>1</sup>  | Interrupt Prior-<br>ity<br>Reg        | B8H               | -         | PPC       | PT2      | PS       | PT1      | PX1      | PT0        | PX0      | x0000000<br>b  |

| IPH              | Interrupt Prior-<br>ity<br>Reg High   | B7H               | -         | PPCH      | PT2<br>H | PS<br>H  | PT1H     | PX1<br>H | PT0H       | PX0<br>H | x0000000<br>b  |

| IP1 <sup>1</sup> | Interrupt Prior-<br>ity<br>Reg A      | F8H               | -         | -         | -        | -        | РВО      | PX3      | PX2        | -        | xxxx0xxx<br>b  |

| IP1H             | Interrupt Prior-<br>ity<br>Reg A High | F7H               | -         | -         | -        | -        | PBO<br>H | PX3<br>H | PX2H       | -        | xxxx0xxx<br>b  |

| PCON             | Power Control                         | 87H               | SMOD<br>1 | SMOD<br>0 | BOF      | PO<br>F  | GF1      | GF0      | PD         | IDL      | 00010000<br>b  |

| AUXR             | Auxiliary Reg                         | 8EH               | -         | -         | -        | -        | -        | -        | EXTRA<br>M | AO       | xxxxxxx0<br>0b |

| AUXR1            | Auxiliary Reg<br>1                    | A2H               | -         | -         | -        | -        | GF2      | 0        | -          | DPS      | xxxx00x0<br>b  |

| XICON            | External<br>Interrupt Con-<br>trol    | AEH               | -         | EX3       | IE3      | IT3      | 0        | EX2      | IE2        | IT2      | 00H            |

1. Bit Addressable SFRs

T0-0.0 25093

Data Sheet

### Table 11: PCA SFRs

|                   |                                            | Direct     |          | Bit Address, Symbol, or Alternative Port Function |           |           |          |          |          | RESET     |               |

|-------------------|--------------------------------------------|------------|----------|---------------------------------------------------|-----------|-----------|----------|----------|----------|-----------|---------------|

| Symbol            | Description                                | Address    | MSB      |                                                   |           |           |          |          |          | LSB       | Value         |

| CH<br>CL          | PCA Timer/Coun-<br>ter                     | F9H<br>E9H |          | CH[7:0]<br>CL[7:0]                                |           |           |          |          |          |           | 00H<br>00H    |

| CCON <sup>1</sup> | PCA Timer/Coun-<br>ter<br>Control Register | D8H        | CF       | CR                                                | -         | CCF4      | CCF<br>3 | CCF<br>2 | CCF<br>1 | CCF0      | 00x0000<br>0b |

| CMOD              | PCA Timer/Coun-<br>ter<br>Mode Register    | D9H        | CID<br>L | WDTE                                              | -         | -         | -        | CPS<br>1 | CPS<br>0 | ECF       | 00xxx000<br>b |

| CCAP0<br>H        | PCA Module 0<br>Compare/Cap-               | FAH        |          |                                                   |           | CCAP0     | H[7:0]   |          |          |           | 00H           |

| CCAP0<br>L        | ture<br>Registers                          | EAH        |          |                                                   |           | CCAPO     | 0L[7:0]  |          |          |           | 00H           |

| CCAP1<br>H        | PCA Module 1<br>Compare/Cap-               | FBH        |          |                                                   |           | CCAP1     | H[7:0]   |          |          |           | 00H           |

| CCAP1<br>L        | ture<br>Registers                          | EBH        |          | CCAP1L[7:0]                                       |           |           |          |          |          | 00H       |               |

| CCAP2<br>H        | PCA Module 2<br>Compare/Cap-               | FCH        |          | CCAP2H[7:0]                                       |           |           |          |          |          | 00H       |               |

| CCAP2<br>L        | ture<br>Registers                          | ECH        |          |                                                   |           | CCAP2     | 2L[7:0]  |          |          |           | 00H           |

| CCAP3<br>H        | PCA Module 3<br>Compare/Cap-               | FDH        |          |                                                   |           | CCAP3     | H[7:0]   |          |          |           | 00H           |

| CCAP3<br>L        | ture<br>Registers                          | EDH        |          |                                                   |           | CCAP3     | BL[7:0]  |          |          |           | 00H           |

| CCAP4<br>H        | PCA Module 4<br>Compare/Cap-               | FEH        |          |                                                   |           | CCAP4     | H[7:0]   |          |          |           | 00H           |

| CCAP4<br>L        | ture<br>Registers                          | EEH        |          |                                                   |           | CCAP4     | L[7:0]   |          |          |           | 00H           |

| CCAPM<br>0        | PCA<br>Compare/Cap-                        | DAH        | -        | ECOM<br>0                                         | CAPP<br>0 | CAPN<br>0 | MAT<br>0 | TOG<br>0 | PWM<br>0 | ECCF<br>0 | x000000<br>0b |

| CCAPM<br>1        | ture<br>Module Mode                        | DBH        | -        | ECOM<br>1                                         | CAPP<br>1 | CAPN<br>1 | MAT<br>1 | TOG<br>1 | PWM<br>1 | ECCF<br>1 | x000000<br>0b |

| CCAPM<br>2        | Registers                                  | DCH        | -        | ECOM<br>2                                         | CAPP<br>2 | CAPN<br>2 | MAT<br>2 | TOG<br>2 | PWM<br>2 | ECCF<br>2 | x000000<br>0b |

| CCAPM<br>3        |                                            | DDH        | -        | ECOM<br>3                                         | CAPP<br>3 | CAPN<br>3 | MAT<br>3 | TOG<br>3 | PWM<br>3 | ECCF<br>3 | x000000<br>0b |

| CCAPM<br>4        |                                            | DEH        | -        | ECOM<br>4                                         | CAPP<br>4 | CAPN<br>4 | MAT<br>4 | TOG<br>4 | PWM<br>4 | ECCF<br>4 | x000000<br>0b |

1. Bit Addressable SFRs

T0-0.0 25093

#### Data Sheet

| SPI Control Register (S | PCR)                                                                                                 |                                                                                                                      |                          |                          |                          |             |           |            |              |

|-------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|-------------|-----------|------------|--------------|

| Location                | 7                                                                                                    | 6                                                                                                                    | 5                        | 4                        | 3                        | 2           | 1         | 0          | Reset Value  |

| D5H                     | SPIE                                                                                                 | SPE                                                                                                                  | DORD                     | MSTR                     | CPOL                     | CPHA        | SPR1      | SPR0       | 00H          |

| Symbol                  | Function                                                                                             |                                                                                                                      |                          |                          |                          |             |           |            |              |

| SPIE                    | If both SP                                                                                           | IE and ES                                                                                                            | are set to               | one, SPI                 | interrupts               | are enable  | ed.       |            |              |

| SPE                     | 0: Disables                                                                                          | PI enable bit.<br>Disables SPI.<br>Enables SPI and connects SS#, MOSI, MISO, and SCK to pins P1.4, P1.5, P1.6, P1.7. |                          |                          |                          |             |           |            |              |

| DORD                    | Data Transmission Order.<br>0: MSB first in data transmission.<br>1: LSB first in data transmission. |                                                                                                                      |                          |                          |                          |             |           |            |              |

| MSTR                    | Master/Slave select.<br>0: Selects Slave mode.<br>1: Selects Master mode.                            |                                                                                                                      |                          |                          |                          |             |           |            |              |

| CPOL                    | Clock Pola<br>0: SCK is<br>1: SCK is                                                                 | low when                                                                                                             | •                        | 0,                       |                          |             |           |            |              |

| CPHA                    | Clock Pha<br>relationshi<br>0: Shift trig<br>1: Shift trig                                           | p betweer<br>ggered on                                                                                               | n master a<br>the leadin | nd slave. S<br>g edge of | See Figure<br>the clock. | es 21 and   |           | ock and c  | lata         |

| SPR1. S                 | PR0SPI Clo                                                                                           | ock Rate S                                                                                                           | Select bits.             | These tw                 | o bits cont              | trol the SC | K rate of | the device | e configured |

SPR1, SPR0SPI Clock Rate Select bits. These two bits control the SCK rate of the device configured as master. SPR1 and SPR0 have no effect on the slave. The relationship between SCK and the oscillator frequency, f<sub>OSC</sub>, is as follows:

| SPR1 | SPR0 | SCK = f <sub>OSC</sub> divided by |

|------|------|-----------------------------------|

| 0    | 0    | 4                                 |

| 0    | 1    | 16                                |

| 1    | 0    | 64                                |

| 1    | 1    | 128                               |

#### SPI Status Register (SPSR)

| Location | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 | Reset Value |

|----------|------|------|---|---|---|---|---|---|-------------|

| AAH      | SPIF | WCOL | - | - | - | - | - | - | 00xxxxxxb   |

#### Symbol Function

| SPIF | SPI Interrupt Flag.<br>Upon completion of data transfer, this bit is set to 1.<br>If SPIE =1 and ES =1, an interrupt is then generated.<br>This bit is cleared by software. |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WCOL | Write Collision Flag.<br>Set if the SPI data register is written to during data transfer.<br>This bit is cleared by software.                                               |

#### Data Sheet

| External Interrupt Contr |                             | )            |              |            |             |            |               |            |             |

|--------------------------|-----------------------------|--------------|--------------|------------|-------------|------------|---------------|------------|-------------|

| Location                 | 7                           | 6            | 5            | 4          | 3           | 2          | 1             | 0          | Reset Value |

| AEH                      | -                           | EX3          | IE3          | IT3        | 0           | EX2        | IE2           | IT2        | 00H         |

| Symbol                   | Function                    |              |              |            |             |            |               |            |             |

| EX2                      | External Ir<br>Enable bit   | •            |              |            |             |            |               |            |             |

| IE2                      | Interrupt E<br>If IT2=1, II |              | leared aut   | omatically | by hardw    | are when i | interrupt is  | s detected | l/serviced. |

| IT2                      | External Ir                 | nterrupt 2 i | is falling-e | dge/low-le | vel trigger | ed when t  | his bit is c  | leared by  | software.   |

| EX3                      | External Ir<br>Enable bit   | •            |              |            |             |            |               |            |             |

| IE3                      | Interrupt E<br>If IT3=1, II |              | leared aut   | omatically | by hardw    | are when i | interrupt is  | detectec   | l/serviced. |

| IT3                      | External Ir                 | nterrupt3 is | s falling-eo | ge/low-le  | el trigger  | ed when th | nis bit is cl | eared by   | software.   |

#### ©2013 Silicon Storage Technology, Inc.

Data Sheet

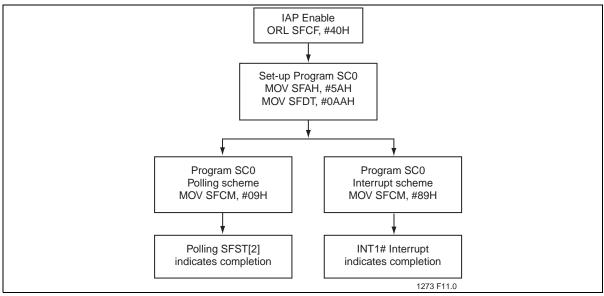

#### Prog-SC0

Prog-SC0 command is used to program the SC0 bit. This command only changes the SC0 bit and has no effect on BSEL bit until after a reset cycle.

SC0 bit previously in un-programmed state can be programmed by this command. The Prog-SC0 command should reside only in Block 1 or external code memory.

### Figure 15: Prog-SC0

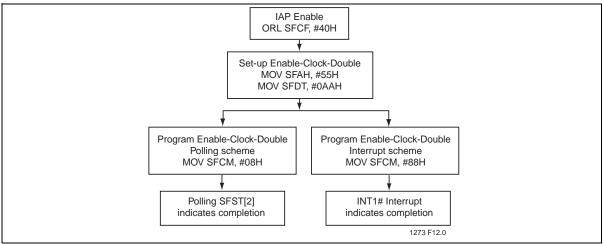

### Enable-Clock-Double

Enable-Clock-Double command is used to make the MCU run at 6 clocks per machine cycle. The standard (default) is 12 clocks per machine cycle (i.e. clock double command disabled).

### Figure 16: Enable-Clock-Double

There are no IAP counterparts for the external host commands Select-Block0 and Select-Block1.

Data Sheet

#### Table 22: PCA Module Modes

| W  | Without Interrupt enabled |                    |                    |                   |                        |                   |                    |                                                              |

|----|---------------------------|--------------------|--------------------|-------------------|------------------------|-------------------|--------------------|--------------------------------------------------------------|

| _1 | ECOMy <sup>2</sup>        | CAPPy <sup>2</sup> | CAPNy <sup>2</sup> | MATy <sup>2</sup> | TOGy <sup>2</sup>      | PWMy <sup>2</sup> | ECCFy <sup>2</sup> | Module Code                                                  |

| -  | 0                         | 0                  | 0                  | 0                 | 0                      | 0                 | 0                  | No Operation                                                 |

| -  | 0                         | 1                  | 0                  | 0                 | 0                      | 0                 | 0                  | 16-bit capture on positive-edge trigger at CEX[4:0]          |

| -  | 0                         | 0                  | 1                  | 0                 | 0                      | 0                 | 0                  | 16-bit capture on negative-edge trigger at CEX[4:0]          |

| -  | 0                         | 1                  | 1                  | 0                 | 0                      | 0                 | 0                  | 16-bit capture on positive/negative-edge trigger at CEX[4:0] |

| -  | 1                         | 0                  | 0                  | 1                 | 0                      | 0                 | 0                  | Compare: software timer                                      |

| -  | 1                         | 0                  | 0                  | 1                 | 1                      | 0                 | 0                  | Compare: high-speed output                                   |

| -  | 1                         | 0                  | 0                  | 0                 | 0                      | 1                 | 0                  | Compare: 8-bit PWM                                           |

| -  | 1                         | 0                  | 0                  | 1                 | 0 or<br>1 <sup>3</sup> | 0                 | 0                  | Compare: PCA WDT (CCAPM4 only) <sup>4</sup>                  |

T0-0.0 25093

1. User should not write '1's to reserved bits. The value read from a reserved bit is indeterminate.

2. y = 0, 1, 2, 3, 4

3. A 0 disables toggle function. A 1 enables toggle function on CEX[4:0] pin.

4. For PCA WDT mode, also set the WDTE bit in the CMOD register to enable the reset output signal.

| Wi | th Interrup        | t enabled          |                    |                   |                     |                   |                    |                                                                     |

|----|--------------------|--------------------|--------------------|-------------------|---------------------|-------------------|--------------------|---------------------------------------------------------------------|

| _1 | ECOMy <sup>2</sup> | CAPPy <sup>2</sup> | CAPNy <sup>2</sup> | MATy <sup>2</sup> | TOGy <sup>2</sup>   | PWMy <sup>2</sup> | ECCFy <sup>2</sup> | Module Code                                                         |

| -  | 0                  | 1                  | 0                  | 0                 | 0                   | 0                 | 1                  | 16-bit capture on positive-edge trig-<br>ger at CEX[4:0]            |

| -  | 0                  | 0                  | 1                  | 0                 | 0                   | 0                 | 1                  | 16-bit capture on negative-edge trig-<br>ger at CEX[4:0]            |

| -  | 0                  | 1                  | 1                  | 0                 | 0                   | 0                 | 1                  | 16-bit capture on positive/negative-<br>edge<br>trigger at CEX[4:0] |

| -  | 1                  | 0                  | 0                  | 1                 | 0                   | 0                 | 1                  | Compare: software timer                                             |

| -  | 1                  | 0                  | 0                  | 1                 | 1                   | 0                 | 1                  | Compare: high-speed output                                          |

| -  | 1                  | 0                  | 0                  | 0                 | 0                   | 1                 | X <sup>3</sup>     | Compare: 8-bit PWM                                                  |

| -  | 1                  | 0                  | 0                  | 1                 | 0 or 1 <sup>4</sup> | 0                 | X <sup>5</sup>     | Compare: PCA WDT (CCAPM4 only) <sup>6</sup>                         |

#### Table 23: PCA Module Modes

T0-0.0 25093

1. User should not write '1's to reserved bits. The value read from a reserved bit is indeterminate.

2. y = 0, 1, 2, 3, 4

3. No PCA interrupt is needed to generate the PWM.

4. A 0 disables toggle function. A 1 enables toggle function on CEX[4:0] pin.

5. Enabling an interrupt for the Watchdog Timer would defeat the purpose of the Watchdog Timer.

6. For PCA WDT mode, also set the WDTE bit in the CMOD register to enable the reset output signal.

Data Sheet

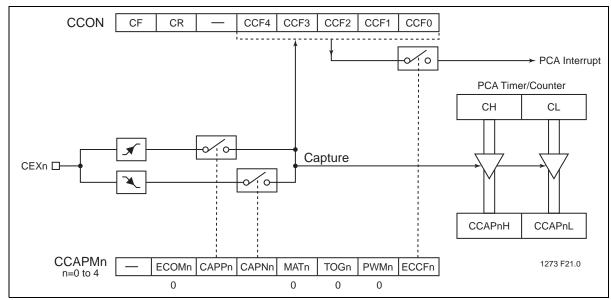

### **Capture Mode**

Capture mode is used to capture the PCA timer/counter value into a module's capture registers (CCAPnH and CCAPnL). The capture will occur on a positive edge, negative edge, or both on the corresponding module's pin. To use one of the PCA modules in the capture mode, either one or both the CCAPM bits CAPN and CAPP for that module must be set. When a valid transition occurs on the CEX pin corresponding to the module used, the PCA hardware loads the 16-bit value of the PCA counter register (CH and CL) into the module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set, then an interrupt will be generated. In the interrupt service routine, the 16-bit capture value must be saved in RAM before the next event capture occurs. If a subsequent capture occurred, the original capture values would be lost. After flag event flag has been set by hardware, the user must clear the flag in software. (See Figure 25)

Figure 25: PCA Capture Mode

Data Sheet

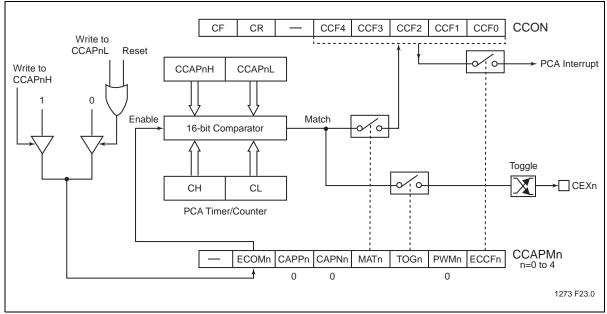

Figure 27: PCA High Speed Output Mode

### **Pulse Width Modulator**

The Pulse Width Modulator (PWM) mode is used to generate 8-bit PWMs by comparing the low byte of the PCA timer (CL) with the low byte of the compare register (CCAPnL). When CL < CCAPnL the output is low. When  $CL \ge CCAPnL$  the output is high. To activate this mode, the user must set the PWM and ECOM bits in the module's CCAPMn SFR. (See Figure 28 and Table 24)

In PWM mode, the frequency of the output depends on the source for the PCA timer. Since there is only one set of CH and CL registers, all modules share the PCA timer and frequency. Duty cycle of the output is controlled by the value loaded into the high byte (CCAPnH). Since writes to the CCAPnH register are asynchronous, a new value written to the high byte will not be shifted into CCAPnL for comparison until the next period of the output (when CL rolls over from 255 to 00).

To calculate values for CCAPnH for any duty cycle, use the following equation:

CCAPnH = 256(1 - Duty Cycle)

where CCAPnH is an 8-bit integer and Duty Cycle is a fraction.

Data Sheet

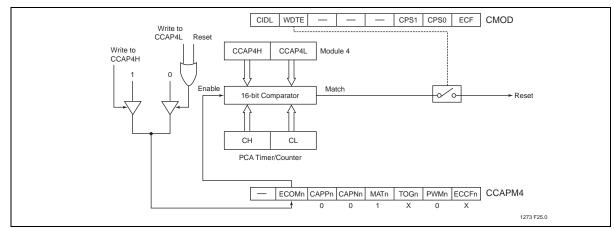

### Watchdog Timer

The Watchdog Timer mode is used to improve reliability in the system without increasing chip count (See Figure 29). Watchdog Timers are useful for systems that are susceptible to noise, power glitches, or electrostatic discharge. It can also be used to prevent a software deadlock. If during the execution of the user's code, there is a deadlock, the Watchdog Timer will time out and an internal reset will occur. Only module 4 can be programmed as a Watchdog Timer (but still can be programmed to other modes if the Watchdog Timer is not used).

To use the Watchdog Timer, the user pre-loads a 16-bit value in the compare register. Just like the other compare modes, this 16-bit value is compared to the PCA timer value. If a match is allowed to occur, an internal reset will be generated. This will not cause the RST pin to be driven high.

In order to hold off the reset, the user has three options:

- 1. periodically change the compare value so it will never match the PCA timer,

- 2. periodically change the PCA timer value so it will never match the compare values, or

- 3. disable the watchdog timer by clearing the WDTE bit before a match occurs and then reenable it.

The first two options are more reliable because the Watchdog Timer is never disabled as in option #3. If the program counter ever goes astray, a match will eventually occur and cause an internal reset. The second option is also not recommended if other PCA modules are being used. Remember, the PCA timer is the time base for all modules; changing the time base for other modules would not be a good idea. Thus, in most application the first solution is the best option.

Use the code below to initialize the Watchdog Timer. Module 4 can be configured in either compare mode, and the WDTE bit in CMOD must also be set. The user's software then must periodically change (CCAP4H, CCAP4L) to keep a match from occurring with the PCA timer (CH, CL). This code is given in the Watchdog routine below.

Init\_Watchdog:

MOVCCAPM4, #4CH; Module 4 in compare mode

MOVCCAP4L, #0FFH; Write to low byte first

MOVCCAP4H, #0FFH; Before PCA timer counts up ; to FFFF Hex, these compare ; values must be changed.

ORLCMOD, #40H; Set the WDTE bit to enable the

- ; watchdog timer without

- ; changing the other bits in

; CMOD

;Main program goes here, but call WATCHDOG periodically.

WATCHDOG:

Data Sheet

CLR EA; Hold off interrupts

MOVCCAP4L, #00; Next compare value is within

MOVCCAP4H, CH; 65,535 counts of the ; current PCA

SETBEA; timer value

RET

This routine should not be part of an interrupt service routine. If the program counter goes astray and gets stuck in an infinite loop, interrupts will still be serviced and the watchdog will keep getting reset. Thus, the purpose of the watchdog would be defeated. Instead, call this subroutine from the main program of the PCA timer.

Figure 29: PCA Watchdog Timer (Module 4 only)

Data Sheet

T0-0.0 25093

### Table 26: Security Lock Access Table

|       |           | Source               | Target               | Byte-Verify Allo           | MOVC Allowed |        |

|-------|-----------|----------------------|----------------------|----------------------------|--------------|--------|

| Level | SFST[7:5] | Address <sup>1</sup> | Address <sup>2</sup> | External Host <sup>3</sup> | IAP          | 516RDx |

|       |           | Block 0              | Y                    | Ν                          | Y            |        |

|       |           | Block 0              | Block 1              | Y                          | Y            | Y      |

|       |           |                      | External             | N/A                        | N/A          | Ν      |

| 1     | 000b      | Block 1              | Block 0              | Y                          | Y            | Y      |

| 1     | (unlock)  |                      | Block 1              | Y                          | Ν            | Y      |

|       |           |                      | External             | N/A                        | N/A          | Ν      |

|       |           | Estern el            | Block 0/1            | Y                          | Y            | Ν      |

|       |           | External             | External             | N/A                        | N/A          | Y      |

1. Location of MOVC or IAP instruction

2. Target address is the location of the byte being read

3. External host Byte-Verify access does not depend on a source address.

Data Sheet

### **Electrical Specification**

**Absolute Maximum Stress Ratings** (Applied conditions greater than those listed under "Absolute Maximum Stress Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions or conditions greater than those defined in the operational sections of this data sheet is not implied. Exposure to absolute maximum stress rating conditions may affect device reliability.)

| Ambient Temperature Under Bias                                |                               |

|---------------------------------------------------------------|-------------------------------|

| Storage Temperature                                           |                               |

| Voltage on EA# Pin to V <sub>SS</sub>                         |                               |

| D.C. Voltage on Any Pin to Ground Potential                   | 0.5V to V <sub>DD</sub> +0.5V |

| Transient Voltage (<20ns) on Any Other Pin to V <sub>SS</sub> | 1.0V to V <sub>DD</sub> +1.0V |

| Maximum I <sub>OL</sub> per I/O Pins P1.5, P1.6, P1.7         |                               |

| Maximum I <sub>OL</sub> per I/O for All Other Pins            | 15mA                          |

| Package Power Dissipation Capability (T <sub>A</sub> = 25°C)  | 1.5W                          |

| Through Hole Lead Soldering Temperature (10 Seconds)          |                               |

| Surface Mount Solder Reflow Temperature <sup>1</sup>          | 260°C for 10 seconds          |

| Output Short Circuit Current <sup>2</sup>                     | 50 mA                         |

- 1. Excluding certain with-Pb 32-PLCC units, all packages are 260°C capable in both non-Pb and with-Pb solder versions. Certain with-Pb 32-PLCC package types are capable of 240°C for 10 seconds; please consult the factory for the latest information.

- $\ensuremath{\text{2.}}$  Outputs shorted for no more than one second. No more than one output shorted at a time.

- (Based on package heat transfer limitations, not device power consumption.

- **Note:** This specification contains preliminary information on new products in production. The specifications are subject to change without notice.

| Symbol          | Description                    | Min. | Max | Unit |

|-----------------|--------------------------------|------|-----|------|

| T <sub>A</sub>  | Ambient Temperature Under Bias |      |     |      |

|                 | Standard                       | 0    | +70 | °C   |

|                 | Industrial                     | -40  | +85 | °C   |

| V <sub>DD</sub> | Supply Voltage                 |      |     |      |

|                 | SST89E516RDx                   | 4.5  | 5.5 | V    |

|                 | SST89V516RDx                   | 2.7  | 3.6 | V    |

| fosc            | Oscillator Frequency           |      |     |      |

|                 | SST89E516RDx                   | 0    | 40  | MHz  |

|                 | SST89V516RDx                   | 0    | 33  | MHz  |

|                 | Oscillator Frequency for IAP   |      |     |      |

|                 | SST89E516RDx                   | .25  | 40  | MHz  |

|                 | SST89V516RDx                   | .25  | 33  | MHz  |

#### Table 31: Operating Range

T0-0.0 25093

Data Sheet

1. Under steady state (non-transient) conditions,  $I_{OL}$  must be externally limited as follows:

Maximum I<sub>OL</sub> per port pin: 15mA Maximum I<sub>OL</sub> per 8-bit port: 26mA

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification.

Pins are not guaranteed to sink current greater than the listed test conditions.

- 2. Capacitive loading on Ports 0 and 2 may cause spurious noise to be superimposed on the V<sub>OL</sub>s of ALE and Ports 1 & 3. The noise due to external bus capacitance discharging into the Port 0 & 2 pins when the pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100pF), the noise pulse on the ALE pin may exceed 0.8V. In such cases, it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input.

- 3. Load capacitance for Port 0, ALE & PSEN#= 100pF, load capacitance for all other outputs = 80pF.

- 4. Capacitive loading on Ports 0 and 2 may cause the  $V_{OH}$  on ALE and PSEN# to momentarily fall below the  $V_{DD}$  0.7 specification when the address bits are stabilizing.

- 5. Pins of Ports 1, 2, and 3 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when V<sub>IN</sub> is approximately 2V.

- 6. Pin capacitance is characterized but not tested. EA# is 25pF (max).

Data Sheet

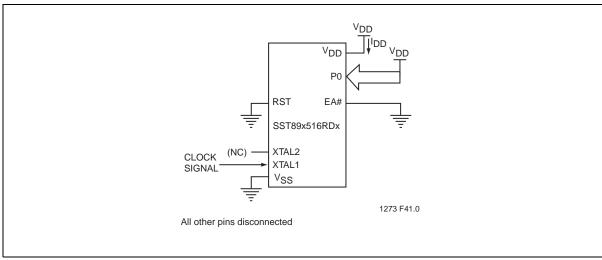

Figure 45:I<sub>DD</sub> Test Condition, Idle Mode

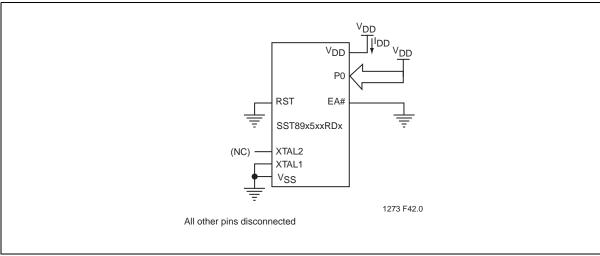

Figure 46:I<sub>DD</sub> Test Condition, Power-down Mode

| Table 41: Flash Memory Prog | ramming/Verification Parameters <sup>1</sup> |

|-----------------------------|----------------------------------------------|

|-----------------------------|----------------------------------------------|

| Parameter <sup>2</sup>              | Max | Units      |

|-------------------------------------|-----|------------|

| Chip-Erase Time                     | 150 | ms         |

| Block-Erase Time                    | 100 | ms         |

| Sector-Erase Time                   | 30  | ms         |

| Byte-Program Time <sup>3</sup>      | 50  | μs         |

| Select-Block Program Time           | 500 | ns         |

| Re-map or Security bit Program Time | 80  | μs         |

|                                     |     | T0-0.1 250 |

1. For IAP operations, the program execution overhead must be added to the above timing parameters.

2. Program and Erase times will scale inversely proportional to programming clock frequency.

3. Each byte must be erased before programming.

Data Sheet

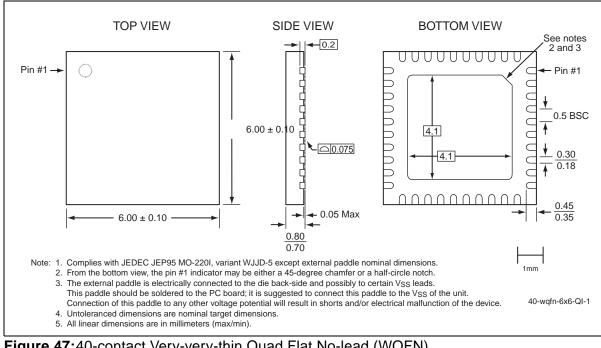

### **Packaging Diagrams**

Figure 47:40-contact Very-very-thin Quad Flat No-lead (WQFN) SST Package Code: QI

#### Data Sheet

Figure 49:44-lead Plastic Lead Chip Carrier (PLCC) SST Package Code: NJ