#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFL

| Details                    |                                                                                       |

|----------------------------|---------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                              |

| Core Processor             | 8051                                                                                  |

| Core Size                  | 8-Bit                                                                                 |

| Speed                      | 40MHz                                                                                 |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                              |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                      |

| Number of I/O              | 36                                                                                    |

| Program Memory Size        | 72KB (72K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 1K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                           |

| Data Converters            | -                                                                                     |

| Oscillator Type            | External                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 44-LCC (J-Lead)                                                                       |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89e516rd2-40-i-nje-t-nxx |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Data Sheet

| Symbol           | Description                           | Direct<br>Address | MSB       | Bit Addre | ss, Syrr | nbol, or | Alternat | ive Port | Function   | LSB      | Reset<br>Value |  |

|------------------|---------------------------------------|-------------------|-----------|-----------|----------|----------|----------|----------|------------|----------|----------------|--|

| ACC <sup>1</sup> | Accumulator                           | E0H               |           |           |          | AC       | C[7:0]   |          |            |          | 00H            |  |

| B <sup>1</sup>   | B Register                            | F0H               |           |           |          | B[       | 7:0]     |          |            |          | 00H            |  |

| PSW <sup>1</sup> | Program Sta-<br>tus<br>Word           | D0H               | CY        | AC        | F0       | RS<br>1  | RS0      | OV       | F1         | Р        | 00H            |  |

| SP               | Stack Pointer                         | 81H               |           | SP[7:0]   |          |          |          |          |            |          |                |  |

| DPL              | Data Pointer<br>Low                   | 82H               |           | DPL[7:0]  |          |          |          |          |            |          |                |  |

| DPH              | Data Pointer<br>High                  | 83H               |           | DPH[7:0]  |          |          |          |          |            |          |                |  |

| IE <sup>1</sup>  | Interrupt<br>Enable                   | A8H               | EA        | EC        | ET2      | ES       | ET1      | EX1      | ET0        | EX0      | 00H            |  |

| IEA <sup>1</sup> | Interrupt<br>Enable A                 | E8H               | -         | -         | -        | -        | EBO      | -        | -          | -        | xxxx0xxx<br>b  |  |

| IP <sup>1</sup>  | Interrupt Prior-<br>ity<br>Reg        | B8H               | -         | PPC       | PT2      | PS       | PT1      | PX1      | PT0        | PX0      | x0000000<br>b  |  |

| IPH              | Interrupt Prior-<br>ity<br>Reg High   | B7H               | -         | PPCH      | PT2<br>H | PS<br>H  | PT1H     | PX1<br>H | PT0H       | PX0<br>H | x0000000<br>b  |  |

| IP1 <sup>1</sup> | Interrupt Prior-<br>ity<br>Reg A      | F8H               | -         | -         | -        | -        | РВО      | PX3      | PX2        | -        | xxxx0xxx<br>b  |  |

| IP1H             | Interrupt Prior-<br>ity<br>Reg A High | F7H               | -         | -         | -        | -        | PBO<br>H | PX3<br>H | PX2H       | -        | xxxx0xxx<br>b  |  |

| PCON             | Power Control                         | 87H               | SMOD<br>1 | SMOD<br>0 | BOF      | PO<br>F  | GF1      | GF0      | PD         | IDL      | 00010000<br>b  |  |

| AUXR             | Auxiliary Reg                         | 8EH               | -         | -         | -        | -        | -        | -        | EXTRA<br>M | AO       | xxxxxxx0<br>0b |  |

| AUXR1            | Auxiliary Reg<br>1                    | A2H               | -         | -         | -        | -        | GF2      | 0        | -          | DPS      | xxxx00x0<br>b  |  |

| XICON            | External<br>Interrupt Con-<br>trol    | AEH               | -         | EX3       | IE3      | IT3      | 0        | EX2      | IE2        | IT2      | 00H            |  |

1. Bit Addressable SFRs

Data Sheet

|        |                            | Direct  |           | Bit Ac                                                                                    | ldress, S | Symb | ol, or Alter | native Port Fund | ction |     | Reset         |

|--------|----------------------------|---------|-----------|-------------------------------------------------------------------------------------------|-----------|------|--------------|------------------|-------|-----|---------------|

| Symbol | Description                | Address | MSB       |                                                                                           |           |      |              |                  |       | LSB | Value         |

| SFCF   | SuperFlash                 | B1H     | -         | IAPE                                                                                      | -         | -    | -            | -                | SW    | BSE | x0xxxx00      |

|        | Configuration              |         |           | Ν                                                                                         |           |      |              |                  | R     | L   | b             |

| SFCM   | SuperFlash<br>Command      | B2H     | FIE       | FIE FCM[6:0]                                                                              |           |      |              |                  |       |     |               |

| SFAL   | SuperFlash<br>Address Low  | B3H     | Super     | SuperFlash Low Order Byte Address Register - $A_7$ to $A_0$ (SFAL)                        |           |      |              |                  |       |     |               |

| SFAH   | SuperFlash<br>Address High | B4H     | Su        | SuperFlash High Order Byte Address Register - A <sub>15</sub> to A <sub>8</sub><br>(SFAH) |           |      |              |                  |       |     |               |

| SFDT   | SuperFlash<br>Data         | B5H     |           | SuperFlash Data Register                                                                  |           |      |              |                  |       |     | 00H           |

| SFST   | SuperFlash<br>Status       | B6H     | SB1<br>_i | SB2_<br>i                                                                                 | SB3<br>_i | -    | EDC_i        | FLASH_BU<br>SY   | -     | -   | 000x00xx<br>b |

## Table 7: Flash Memory Programming SFRs

T0-0.0 25093

# Table 8: Watchdog Timer SFRs

|           |                                  | Direct  | Bit Ade                    | Bit Address, Symbol, or Alternative Port Function |   |       |      |      |     |      |               |  |  |

|-----------|----------------------------------|---------|----------------------------|---------------------------------------------------|---|-------|------|------|-----|------|---------------|--|--|

| Symbol    | Description                      | Address | MSB                        |                                                   |   |       |      |      |     | LSB  | Value         |  |  |

| WDTC<br>1 | Watchdog<br>Timer<br>Control     | СОН     | -                          | -                                                 | - | WDOUT | WDRE | WDTS | WDT | SWDT | xxx00x00<br>b |  |  |

| WDTD      | Watchdog<br>Timer<br>Data/Reload | 85H     | Watchdog Timer Data/Reload |                                                   |   |       |      |      |     | 00H  |               |  |  |

1. Bit Addressable SFRs

Data Sheet

|                   |                                   | Direct  | Bit Add     | dress, Sy | ymbol, o | r Alterna | ative Port | Functio  | n         |             | Reset         |

|-------------------|-----------------------------------|---------|-------------|-----------|----------|-----------|------------|----------|-----------|-------------|---------------|

| Symbol            | Description                       | Address | MSB         |           |          |           |            |          |           | LSB         | Value         |

| TMOD              | Timer/Counter                     | 89H     |             | Tim       | er 1     |           |            | Tii      | mer 0     |             | 00H           |

|                   | Mode Control                      |         | GAT<br>E    | C/T#      | M1       | M0        | GATE       | C/<br>T# | M1        | MO          |               |

| TCON <sup>1</sup> | Timer/Counter<br>Control          | 88H     | TF1         | TR1       | TF0      | TR0       | IE1        | IT1      | IE0       | IT0         | 00H           |

| TH0               | Timer 0 MSB                       | 8CH     |             | TH0[7:0]  |          |           |            |          |           |             |               |

| TL0               | Timer 0 LSB                       | 8AH     |             | TL0[7:0]  |          |           |            |          |           |             |               |

| TH1               | Timer 1 MSB                       | 8DH     | TH1[7:0]    |           |          |           |            |          |           | 00H         |               |

| TL1               | Timer 1 LSB                       | 8BH     | TL1[7:0]    |           |          |           |            |          |           | 00H         |               |

| T2CON<br>1        | Timer / Coun-<br>ter 2<br>Control | C8H     | TF2         | EXF<br>2  | RCL<br>K | TCL<br>K  | EXEN<br>2  | TR2      | C/<br>T2# | CP/<br>RL2# | 00H           |

| T2MOD             | Timer2<br>Mode Control            | C9H     | -           | -         | -        | -         | -          | -        | T2O<br>E  | DCEN        | xxxxxx00<br>b |

| TH2               | Timer 2 MSB                       | CDH     |             |           |          | Tł        | H2[7:0]    |          |           |             | 00H           |

| TL2               | Timer 2 LSB                       | ССН     |             |           |          | TI        | _2[7:0]    |          |           |             | 00H           |

| RCAP2<br>H        | Timer 2<br>Capture MSB            | СВН     | RCAP2H[7:0] |           |          |           |            |          |           | 00H         |               |

| RCAP2<br>L        | Timer 2<br>Capture LSB            | CAH     |             |           |          | RCA       | AP2L[7:0]  |          |           |             | 00H           |

## Table 9: Timer/Counters SFRs

1. Bit Addressable SFRs

Data Sheet

# Table 11: PCA SFRs

|                   |                                            | Direct     |          | Bit Add     | dress, Syı | nbol, or A   | Alternati | ive Port | Functior | า         | RESET         |

|-------------------|--------------------------------------------|------------|----------|-------------|------------|--------------|-----------|----------|----------|-----------|---------------|

| Symbol            | Description                                | Address    | MSB      |             |            |              |           |          |          | LSB       | Value         |

| CH<br>CL          | PCA Timer/Coun-<br>ter                     | F9H<br>E9H |          |             |            | CH[7<br>CL[7 |           |          |          |           | 00H<br>00H    |

| CCON <sup>1</sup> | PCA Timer/Coun-<br>ter<br>Control Register | D8H        | CF       | CR          | -          | CCF4         | CCF<br>3  | CCF<br>2 | CCF<br>1 | CCF0      | 00x0000<br>0b |

| CMOD              | PCA Timer/Coun-<br>ter<br>Mode Register    | D9H        | CID<br>L | WDTE        | -          | -            | -         | CPS<br>1 | CPS<br>0 | ECF       | 00xxx000<br>b |

| CCAP0<br>H        | PCA Module 0<br>Compare/Cap-               | FAH        |          | CCAP0H[7:0] |            |              |           |          |          |           |               |

| CCAP0<br>L        | ture<br>Registers                          | EAH        |          | CCAP0L[7:0] |            |              |           |          |          |           |               |

| CCAP1<br>H        | PCA Module 1<br>Compare/Cap-               | FBH        |          | CCAP1H[7:0] |            |              |           |          |          |           |               |

| CCAP1<br>L        | ture<br>Registers                          | EBH        |          | CCAP1L[7:0] |            |              |           |          |          |           |               |

| CCAP2<br>H        | PCA Module 2<br>Compare/Cap-               | FCH        |          | CCAP2H[7:0] |            |              |           |          |          |           |               |

| CCAP2<br>L        | ture<br>Registers                          | ECH        |          | CCAP2L[7:0] |            |              |           |          |          |           |               |

| CCAP3<br>H        | PCA Module 3<br>Compare/Cap-               | FDH        |          |             |            | CCAP3        | H[7:0]    |          |          |           | 00H           |

| CCAP3<br>L        | ture<br>Registers                          | EDH        |          |             |            | CCAP3        | BL[7:0]   |          |          |           | 00H           |

| CCAP4<br>H        | PCA Module 4<br>Compare/Cap-               | FEH        |          |             |            | CCAP4        | H[7:0]    |          |          |           | 00H           |

| CCAP4<br>L        | ture<br>Registers                          | EEH        |          |             |            | CCAP4        | L[7:0]    |          |          |           | 00H           |

| CCAPM<br>0        | PCA<br>Compare/Cap-                        | DAH        | -        | ECOM<br>0   | CAPP<br>0  | CAPN<br>0    | MAT<br>0  | TOG<br>0 | PWM<br>0 | ECCF<br>0 | x000000<br>0b |

| CCAPM<br>1        | ture<br>Module Mode                        | DBH        | -        | ECOM<br>1   | CAPP<br>1  | CAPN<br>1    | MAT<br>1  | TOG<br>1 | PWM<br>1 | ECCF<br>1 | x000000<br>0b |

| CCAPM<br>2        | Registers                                  | DCH        | -        | ECOM<br>2   | CAPP<br>2  | CAPN<br>2    | MAT<br>2  | TOG<br>2 | PWM<br>2 | ECCF<br>2 | x000000<br>0b |

| CCAPM<br>3        |                                            | DDH        | -        | ECOM<br>3   | CAPP<br>3  | CAPN<br>3    | MAT<br>3  | TOG<br>3 | PWM<br>3 | ECCF<br>3 | x000000<br>0b |

| CCAPM<br>4        |                                            | DEH        | -        | ECOM<br>4   | CAPP<br>4  | CAPN<br>4    | MAT<br>4  | TOG<br>4 | PWM<br>4 | ECCF<br>4 | x000000<br>0b |

1. Bit Addressable SFRs

## Data Sheet

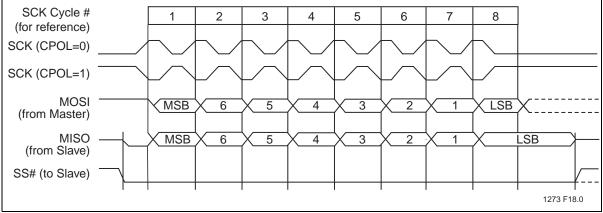

## Interrupt Priority (IP)

| ·) (·· ) |   |     |     |    |     |     |     |     |             |

|----------|---|-----|-----|----|-----|-----|-----|-----|-------------|

| Location | 7 | 6   | 5   | 4  | 3   | 2   | 1   | 0   | Reset Value |

| B8H      | - | PPC | PT2 | PS | PT1 | PX1 | PT0 | PX0 | x0000000b   |

## Symbol Function

- PT2 Timer 2 interrupt priority bit

- PS Serial Port interrupt priority bit

- PT1 Timer 1 interrupt priority bit

- PX1 External interrupt 1 priority bit

- PT0 Timer 0 interrupt priority bit

- PX0 External interrupt 0 priority bit

## Interrupt Priority High (IPH)

| Location | 7 | 6    | 5    | 4   | 3    | 2    | 1    | 0    | Reset Value |

|----------|---|------|------|-----|------|------|------|------|-------------|

| B7H      | - | PPCH | PT2H | PSH | PT1H | PX1H | PT0H | PX0H | x0000000b   |

## Symbol Function

| PPCH | PCA interrupt priority bit high         |

|------|-----------------------------------------|

| PT2H | Timer 2 interrupt priority bit high     |

| PSH  | Serial Port interrupt priority bit high |

| PT1H | Timer 1 interrupt priority bit high     |

| PX1H | External interrupt 1 priority bit high  |

| PT0H | Timer 0 interrupt priority bit high     |

| PX0H | External interrupt 0 priority bit high  |

## Interrupt Priority 1 (IP1)

| Location | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0 | Reset Value |

|----------|---|---|---|---|-----|-----|-----|---|-------------|

| F8H      | 1 | - | - | 1 | PBO | PX3 | PX2 | 1 | 1xx10001b   |

## Symbol Function

PBO Brown-out interrupt priority bit

PX2 External Interrupt 2 priority bit

PX3 External Interrupt 3 priority bit

## Interrupt Priority 1 High (IP1H)

| Location | 7 | 6 | 5 | 4 | 3    | 2    | 1    | 0 | Reset Value |

|----------|---|---|---|---|------|------|------|---|-------------|

| F7H      | 1 | - | - | 1 | PBOH | РХЗН | PX2H | 1 | 1xx10001b   |

## Symbol Function

- PBOH Brown-out Interrupt priority bit high

- PX2H External Interrupt 2 priority bit high

- PX3H External Interrupt 3 priority bit high

Data Sheet

#### Auxiliary Register (AUXR)

| Location | 7 | 6 | 5 | 4 | 3 | 2 | 1          | 0  | Reset Value |

|----------|---|---|---|---|---|---|------------|----|-------------|

| 8EH      | - | - | - | - | - | - | EXTRA<br>M | AO | xxxxxx00b   |

|          |   |   |   |   |   |   |            |    | l           |

## Symbol Function

EXTRAM Internal/External RAM access

0: Internal Expanded RAM access within range of 00H to 2FFH using MOVX @Ri / @DPTR. Beyond 300H, the MCU always accesses external data memory. For details, refer to Section, "Expanded Data RAM Addressing". 1: External data memory access.

AO D

Disable/Enable ALE

0: ALE is emitted at a constant rate of 1/3 the oscillator frequency in 6 clock mode, 1/6  $f_{\rm OSC}$  in 12 clock mode.

1: ALE is active only during a MOVX or MOVC instruction.

## Auxiliary Register 1 (AUXR1)

| Location | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0   | Reset Value |

|----------|---|---|---|---|-----|---|---|-----|-------------|

| A2H      | - | - | - | - | GF2 | 0 | - | DPS | xxxx00x0b   |

## Symbol Function

GF2 General purpose user-defined flag.

DPS DPTR registers select bit.

0: DPTR0 is selected.

1: DPTR1 is selected.

## Watchdog Timer Control Register (WDTC)

| Location | 7 | 6 | 5 | 4     | 3    | 2    | 1   | 0    | Reset Value |

|----------|---|---|---|-------|------|------|-----|------|-------------|

| C0H      | - | - | - | WDOUT | WDRE | WDTS | WDT | SWDT | xxx00000b   |

## Symbol Function

WDOUT Watchdog output enable.

0: Watchdog reset will not be exported on Reset pin.

1: Watchdog reset if enabled by WDRE, will assert Reset pin for 32 clocks.

#### WDRE Watchdog timer reset enable.

0: Disable watchdog timer reset.

1: Enable watchdog timer reset.

WDTS Watchdog timer reset flag.

0: External hardware reset or power-on reset clears the flag.

- Flag can also be cleared by writing a 1.

- Flag survives if chip reset happened because of watchdog timer overflow.

- 1: Hardware sets the flag on watchdog overflow.

## WDT Watchdog timer refresh.

0: Hardware resets the bit when refresh is done.

- 1: Software sets the bit to force a watchdog timer refresh.

- SWDT Start watchdog timer.

- 0: Stop WDT.

- 1: Start WDT.

Data Sheet

## PCA Compare/Capture Module Mode Register<sup>1</sup> (CCAPMn)

| Location | 7           | 6           | 5     | 4     | 3    | 2    | 1    | 0     | Reset Value |

|----------|-------------|-------------|-------|-------|------|------|------|-------|-------------|

| DAH      | -           | ECOM0       | CAPP0 | CAPN0 | MAT0 | TOG0 | PWM0 | ECCF0 | 00xxx000b   |

| DBH      | -           | ECOM1       | CAPP1 | CAPN1 | MAT1 | TOG1 | PWM1 | ECCF1 | 00xxx000b   |

| DCH      | -           | ECOM2       | CAPP2 | CAPN2 | MAT2 | TOG2 | PWM2 | ECCF2 | 00xxx000b   |

| DDH      | -           | ECOM3       | CAPP3 | CAPN3 | MAT3 | TOG3 | PWM3 | ECCF3 | 00xxx000b   |

| DEH      | -           | ECOM4       | CAPP4 | CAPN4 | MAT4 | TOG4 | PWM4 | ECCF4 | 00xxx000b   |

|          | 1 Not hit : | addressable |       |       |      |      |      |       | -           |

Not bit addressable

#### Symbol Function

- Not implemented, reserved for future use. Note: User should not write '1's to reserved bits. The value read from a reserved bit is indeterminate.

## ECOMn Enable Comparator

- 0: Disables the comparator function

- 1: Enables the comparator function

- CAPPn Capture Positive

- 0: Disables positive edge capture on CEX[4:0]

- 1: Enables positive edge capture on CEX[4:0]

## CAPNn Capture Negative

- 0: Disables negative edge capture on CEX[4:0]

- 1: Enables negative edge capture on CEX[4:0]

# MATn Match: Set ECOM[4:0] and MAT[4:0] to implement the software timer mode 0: Disables software timer mode

1: A match of the PCA counter with this module's compare/capture register causes the CCFn bit in CCON to be set, flagging an interrupt.

## TOGn Toggle

0: Disables toggle function

1: A match of the PCA counter with this module's compare/capture register causes the CEXn pin to toggle.

- PWMn Pulse Width Modulation mode

- 0: Disables PWM mode

1: Enables CEXn pin to be used as a pulse width modulated output

# ECCFn Enable CCF Interrupt 0: Disables compare/capture flag CCF[4:0] in the CCON register to generate an interrupt request. 1: Enables compare/capture flag CCF[4:0] in the CCON register to generate an interrupt request.

Data Sheet

|          |                                                                                                                                                               | /                                                                                                                                                                                             | -                         |                          |                           |                          |            |             | -           |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|---------------------------|--------------------------|------------|-------------|-------------|--|--|

| Location | 7                                                                                                                                                             | 6                                                                                                                                                                                             | 5                         | 4                        | 3                         | 2                        | 1          | 0           | Reset Value |  |  |

| C8H      | TF2                                                                                                                                                           | EXF2                                                                                                                                                                                          | RCLK                      | TCLK                     | EXEN2                     | TR2                      | C/T2#      | CP/<br>RL2# | 00H         |  |  |

| Symbol   | Function                                                                                                                                                      |                                                                                                                                                                                               |                           |                          |                           |                          |            |             |             |  |  |

| TF2      |                                                                                                                                                               | Fimer 2 overflow flag set by a Timer 2 overflow and must be cleared by software. TF2 will not be set when either RCLK or TCLK = 1.                                                            |                           |                          |                           |                          |            |             |             |  |  |

| EXF2     | Timer 2 ex<br>on T2EX a<br>to vector to<br>cause an i                                                                                                         | and EXEN                                                                                                                                                                                      | 2 = 1. Whe<br>r 2 interru | en Timer 2<br>pt routine | 2 interrupt<br>. EXF2 mu  | is enableo<br>st be clea | d, EXF2 =  | 1 will caus | se the CPL  |  |  |

| RCLK     |                                                                                                                                                               | Receive clock flag. When set, causes the serial port to use Timer 2 overflow pulses for its eceive clock in modes 1 and 3. RCLK = 0 causes Timer 1 overflow to be used for the receive clock. |                           |                          |                           |                          |            |             |             |  |  |

| TCLK     | Transmit c<br>transmit cl<br>transmit cl                                                                                                                      | lock in mo                                                                                                                                                                                    |                           |                          |                           |                          |            |             |             |  |  |

| EXEN2    | Timer 2 ex<br>negative tr<br>causes Tir                                                                                                                       | ransition o                                                                                                                                                                                   | n T2EX if                 | Timer 2 is               | not being                 | •                        |            |             |             |  |  |

| TR2      | Start/stop                                                                                                                                                    | control for                                                                                                                                                                                   | Timer 2.                  | A logic 1 s              | starts the ti             | imer.                    |            |             |             |  |  |

| C/T2#    | Timer or counter select (Timer 2)<br>0: Internal timer (OSC/6 in 6 clock mode, OSC/12 in 12 clock mode)<br>1: External event counter (falling edge triggered) |                                                                                                                                                                                               |                           |                          |                           |                          |            |             |             |  |  |

| CP/RL2#  | Capture/R<br>= 1. When<br>transitions<br>and the tir                                                                                                          | a cleared, a at T2EX v                                                                                                                                                                        | auto-reloa<br>vhen EXE    | ds will occ<br>N2 = 1. W | ur either w<br>hen either | vith Timer<br>RCLK = 1   | 2 overflow | s or nega   | tive        |  |  |

## Timer/Counter 2 Mode Control (T2MOD)

| Location | 7                                         | 6            | 5               | 4             | 3            | 2            | 1               | 0            | Reset Value |

|----------|-------------------------------------------|--------------|-----------------|---------------|--------------|--------------|-----------------|--------------|-------------|

| C9H      | -                                         | -            | -               | -             | -            | -            | T2OE            | DCEN         | xxxxxx00b   |

| Symbol   | Function                                  |              |                 |               |              |              |                 |              |             |

| -        | Not implemented, reserved for future use. |              |                 |               |              |              |                 |              |             |

|          | Note: User s                              | hould not wr | ite '1's to res | erved bits. T | he value rea | d from a res | erved bit is ir | ndeterminate |             |

- T2OE Timer 2 Output Enable bit.

- DCEN Down Count Enable bit. When set, this allows Timer 2 to be configured as an up/down counter.

## Data Sheet

| External Interrupt Contr |                             |              |              |             |             |            |               |            |             |

|--------------------------|-----------------------------|--------------|--------------|-------------|-------------|------------|---------------|------------|-------------|

| Location                 | 7                           | 6            | 5            | 4           | 3           | 2          | 1             | 0          | Reset Value |

| AEH                      | -                           | EX3          | IE3          | IT3         | 0           | EX2        | IE2           | IT2        | 00H         |

| Symbol                   | Function                    |              |              |             |             |            |               |            |             |

| EX2                      | External Ir<br>Enable bit   | •            |              |             |             |            |               |            |             |

| IE2                      | Interrupt E<br>If IT2=1, IE |              | leared aut   | omatically  | by hardw    | are when i | interrupt is  | s detected | l/serviced. |

| IT2                      | External Ir                 | nterrupt 2 i | is falling-e | dge/low-le  | vel trigger | ed when t  | his bit is c  | leared by  | software.   |

| EX3                      | External Ir<br>Enable bit   | •            |              |             |             |            |               |            |             |

| IE3                      | Interrupt E<br>If IT3=1, IE |              | leared aut   | omatically  | by hardw    | are when i | interrupt is  | detected   | l/serviced. |

| IT3                      | External Ir                 | nterrupt3 is | s falling-eo | dge/low-lev | el trigger  | ed when th | nis bit is cl | eared by   | software.   |

#### ©2013 Silicon Storage Technology, Inc.

Data Sheet

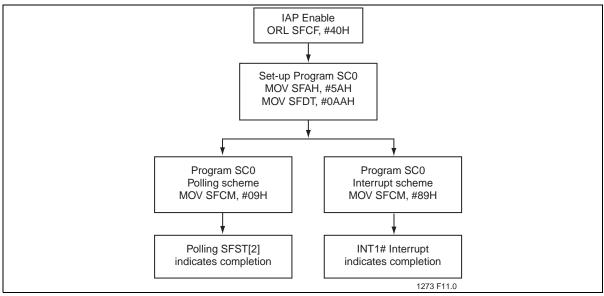

## Prog-SC0

Prog-SC0 command is used to program the SC0 bit. This command only changes the SC0 bit and has no effect on BSEL bit until after a reset cycle.

SC0 bit previously in un-programmed state can be programmed by this command. The Prog-SC0 command should reside only in Block 1 or external code memory.

# Figure 15: Prog-SC0

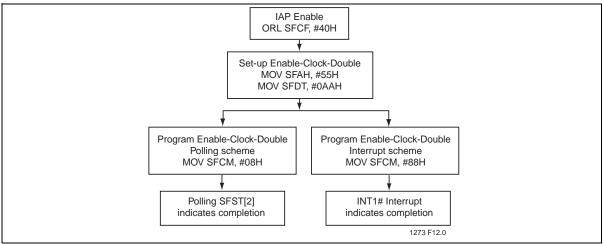

## Enable-Clock-Double

Enable-Clock-Double command is used to make the MCU run at 6 clocks per machine cycle. The standard (default) is 12 clocks per machine cycle (i.e. clock double command disabled).

# Figure 16: Enable-Clock-Double

There are no IAP counterparts for the external host commands Select-Block0 and Select-Block1.

## Data Sheet

If mode 1 is used, the stop bit takes the place of the 9th bit. Bit RI is set only when the received command frame address matches the device's address and is terminated by a valid stop bit. Note that mode 0 cannot be used. Setting SM2 bit in the SCON register in mode 0 will have no effect.

Each slave's individual address is specified by SFR SADDR. SFR SADEN is a mask byte that defines "don't care" bits to form the given address when combined with SADDR. See the example below:

#### Slave 1

| SADDR | = | 1111 0001 |

|-------|---|-----------|

| SADEN | = | 1111 1010 |

| GIVEN | = | 1111 0X0X |

#### Slave 2

| SADDR | = | 1111 0011 |

|-------|---|-----------|

| SADEN | = | 1111 1001 |

| GIVEN | = | 1111 0XX1 |

#### Using the Given Address to Select Slaves

Any bits masked off by a 0 from SADEN become a "don't care" bit for the given address. Any bit masked off by a 1, becomes ANDED with SADDR. The "don't cares" provide flexibility in the user-defined addresses to address more slaves when using the given address.

Shown in the example above, Slave 1 has been given an address of 1111 0001 (SADDR). The SADEN byte has been used to mask off bits to a given address to allow more combinations of selecting Slave 1 and Slave 2. In this case for the given addresses, the last bit (LSB) of Slave 1 is a "don't care" and the last bit of Slave 2 is a 1. To communicate with Slave 1 and Slave 2, the master would need to send an address with the last bit equal to 1 (e.g. 1111 0001) since Slave 1's last bit is a don't care and Slave 2's last bit has to be a 1. To communicate with Slave 1 alone, the master would send an address with the last bit equal to 0 (e.g. 1111 0000), since Slave 2's last bit is a 1. See the table below for other possible combinations.

| Select Slave 1 Only |               |                    |  |  |  |  |  |

|---------------------|---------------|--------------------|--|--|--|--|--|

| Slave 1             | Given Address | Possible Addresses |  |  |  |  |  |

|                     | 1111 0X0X     | 1111 0000          |  |  |  |  |  |

|                     |               | 1111 0100          |  |  |  |  |  |

| Select Slave 2 Only   |           |                    |

|-----------------------|-----------|--------------------|

| Slave 2 Given Address |           | Possible Addresses |

|                       | 1111 0XX1 | 1111 0111          |

|                       |           | 1111 0011          |

| Select Slaves 1 & 2             |           |  |

|---------------------------------|-----------|--|

| Slaves 1 & 2 Possible Addresses |           |  |

|                                 | 1111 0001 |  |

|                                 | 1111 0101 |  |

Data Sheet

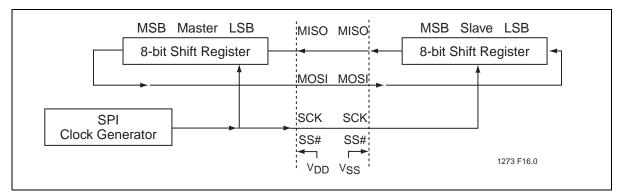

# **Serial Peripheral Interface**

# **SPI Features**

- Master or slave operation

- 10 MHz bit frequency (max)

- LSB first or MSB first data transfer

- Four programmable bit rates

- End of transmission (SPIF)

- Write collision flag protection (WCOL)

- Wake up from idle mode (slave mode only)

## **SPI** Description

The serial peripheral interface (SPI) allows high-speed synchronous data transfer between the SST89E/V516RDx and peripheral devices or between several SST89E/V516RDx devices.

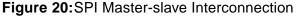

Figure 20 shows the correspondence between master and slave SPI devices. The SCK pin is the clock output and input for the master and slave modes, respectively. The SPI clock generator will start following a write to the master devices SPI data register. The written data is then shifted out of the MOSI pin on the master device into the MOSI pin of the slave device. Following a complete transmission of one byte of data, the SPI clock generator is stopped and the SPIF flag is set. An SPI interrupt request will be generated if the SPI Interrupt Enable bit (SPIE) and the Serial Port Interrupt Enable bit (ES) are both set.

An external master drives the Slave Select input pin, SS#/P1[4], low to select the SPI module as a slave. If SS#/P1[4] has not been driven low, then the slave SPI unit is not active and the MOSI/P1[5] port can also be used as an input port pin.

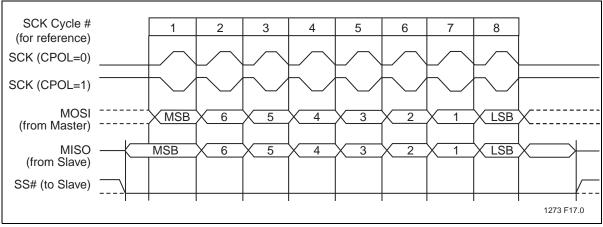

CPHA and CPOL control the phase and polarity of the SPI clock. Figures 21 and 22 show the four possible combinations of these two bits.

Data Sheet

# **SPI Transfer Formats**

Figure 21:SPI Transfer Format with CPHA = 0

Figure 22:SPI Transfer Format with CPHA = 1

Data Sheet

# **Programmable Counter Array**

The Programmable Counter Array (PCA) present on the SST89E/V516RDx is a special 16-bit timer that has five 16-bit capture/compare modules. Each of the modules can be programmed to operate in one of four modes: rising and/or falling edge capture, software timer, high-speed output, or pulse width modulator. The 5th module can be programmed as a Watchdog Timer in addition to the other four modes. Each module has a pin associated with it in port 1. Module 0 is connected to P1.3 (CEX0), module 1 to P1[4] (CEX1), module 2 to P1[5] (CEX2), module 3 to P1[6] (CEX3), and module 4 to P1[7] (CEX4). PCA configuration is shown in Figure 24.

# **PCA** Overview

PCA provides more timing capabilities with less CPU intervention than the standard timer/counter. Its advantages include reduced software overhead and improved accuracy.

The PCA consists of a dedicated timer/counter which serves as the time base for an array of five compare/capture modules. Figure 24 shows a block diagram of the PCA. External events associated with modules are shared with corresponding Port 1 pins. Modules not using the port pins can still be used for standard I/O.

Each of the five modules can be programmed in any of the following modes:

- Rising and/or falling edge capture

- Software timer

- High speed output

- Watchdog Timer (Module 4 only)

- Pulse Width Modulator (PWM)

# PCA Timer/Counter

The PCA timer is a free-running 16-bit timer consisting of registers CH and CL (the high and low bytes of the count values). The PCA timer is common time base for all five modules and can be programmed to run at: 1/6 the oscillator frequency, 1/2 the oscillator frequency, Timer 0 overflow, or the input on the ECI pin (P1.2). The timer/counter source is determined from the CPS1 and CPS0 bits in the CMOD SFR as follows (see "PCA Timer/Counter Mode Register (CMOD)" on page 28):

| CPS1 | CPS0                                  | 12 Clock Mode        | 6 Clock Mode                                                      |

|------|---------------------------------------|----------------------|-------------------------------------------------------------------|

| 0    | 0                                     | f <sub>OSC</sub> /12 | f <sub>OSC</sub> /6                                               |

| 0    | 1                                     | f <sub>OSC</sub> /4  | f <sub>OSC</sub> /2                                               |

| 1    | 0                                     | Timer 0 overflow     | Timer 0 overflow                                                  |

| 1    | · · · · · · · · · · · · · · · · · · · |                      | External clock at ECI pin<br>(maximum rate = f <sub>OSC</sub> /4) |

## Table 18: PCA Timer/Counter Source

Data Sheet

# Figure 32: Interrupt Structure

Data Sheet

# **Power-Saving Modes**

The device provides two power saving modes of operation for applications where power consumption is critical. The two modes are idle and power-down, see Table 28.

# **Idle Mode**

Idle mode is entered setting the IDL bit in the PCON register. In idle mode, the program counter (PC) is stopped. The system clock continues to run and all interrupts and peripherals remain active. The on-chip RAM and the special function registers hold their data during this mode.

The device exits idle mode through either a system interrupt or a hardware reset. Exiting idle mode via system interrupt, the start of the interrupt clears the IDL bit and exits idle mode. After exit the Interrupt Service Routine, the interrupted program resumes execution beginning at the instruction immediately following the instruction which invoked the idle mode. A hardware reset starts the device similar to a power-on reset.

# Power-down Mode

The power-down mode is entered by setting the PD bit in the PCON register. In the power-down mode, the clock is stopped and external interrupts are active for level sensitive interrupts only. SRAM contents are retained during power-down, the minimum  $V_{DD}$  level is 2.0V.

The device exits power-down mode through either an enabled external level sensitive interrupt or a hardware reset. The start of the interrupt clears the PD bit and exits power-down. Holding the external interrupt pin low restarts the oscillator, the signal must hold low at least 1024 clock cycles before bringing back high to complete the exit. Upon interrupt signal being restored to logic  $V_{IH}$ , the first instruction of the interrupt service routine will execute. A hardware reset starts the device similar to power-on reset.

To exit properly out of power-down, the reset or external interrupt should not be executed before the  $V_{DD}$  line is restored to its normal operating voltage. Be sure to hold  $V_{DD}$  voltage long enough at its normal operating level for the oscillator to restart and stabilize (normally less than 10 ms).

Data Sheet

# System Clock and Clock Options

# **Clock Input Options and Recommended Capacitor Values for Oscillator**

Shown in Figure 33 are the input and output of an internal inverting amplifier (XTAL1, XTAL2), which can be configured for use as an on-chip oscillator.

When driving the device from an external clock source, XTAL2 should be left disconnected and XTAL1 should be driven.

At start-up, the external oscillator may encounter a higher capacitive load at XTAL1 due to interaction between the amplifier and its feedback capacitance. However, the capacitance will not exceed 15 pF once the external signal meets the  $V_{IL}$  and  $V_{IH}$  specifications.

Crystal manufacturer, supply voltage, and other factors may cause circuit performance to differ from one application to another. C1 and C2 should be adjusted appropriately for each design. Table 29, shows the typical values for C1 and C2 vs. crystal type for various frequencies

## Table 29: Recommended Values for C1 and C2 by Crystal Type

| Crystal | C1 = C2 |

|---------|---------|

| Quartz  | 20-30pF |

| Ceramic | 40-50pF |

T0-0.0 25093

More specific information about on-chip oscillator design can be found in the *FlashFlex Oscillator Circuit Design Considerations* application note.

# **Clock Doubling Option**

By default, the device runs at 12 clocks per machine cycle (x1 mode). The device has a clock doubling option to speed up to 6 clocks per machine cycle. Please refer to Table 30 for detail.

Clock double mode can be enabled either via the external host mode or the IAP mode. Please refer to Table 14 for the IAP mode enabling commands (When set, the EDC# bit in SFST register will indicate 6 clock mode.).

The clock double mode is only for doubling the internal system clock and the internal flash memory, i.e. EA#=1. To access the external memory and the peripheral devices, careful consideration must be taken. Also note that the crystal output (XTAL2) will not be doubled.

Data Sheet

|                   |                                            | Oscillator |     |       |     |                           |                           |       |

|-------------------|--------------------------------------------|------------|-----|-------|-----|---------------------------|---------------------------|-------|

|                   |                                            | 12MHz      |     | 40MHz |     | Variable                  |                           |       |

| Symbol            | Parameter                                  | Min        | Max | Min   | Max | Min                       | Max                       | Units |

| T <sub>XLXL</sub> | Serial Port Clock Cycle Time               | 1.0        |     | 0.3   |     | 12T <sub>CLCL</sub>       |                           | μs    |

| T <sub>QVXH</sub> | Output Data Setup to Clock Rising Edge     | 700        |     | 117   |     | 10T <sub>CLCL</sub> - 133 |                           | ns    |

| T <sub>XHQX</sub> | Output Data Hold After Clock Ris-          | 50         |     |       |     | 2T <sub>CLCL</sub> - 117  |                           | ns    |

|                   | ing Edge                                   |            |     | 0     |     | 2T <sub>CLCL</sub> - 50   |                           | ns    |

| T <sub>XHDX</sub> | Input Data Hold After Clock Rising<br>Edge | 0          |     | 0     |     | 0                         |                           | ns    |

| T <sub>XHDV</sub> | Clock Rising Edge to Input Data<br>Valid   |            | 700 |       | 117 |                           | 10T <sub>CLCL</sub> - 133 | ns    |

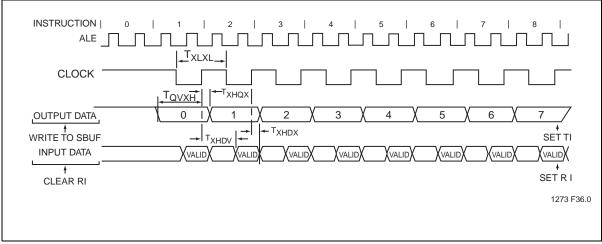

## Table 40: Serial Port Timing

T0-0.0 25093

## Figure 40: Shift Register Mode Timing Waveforms

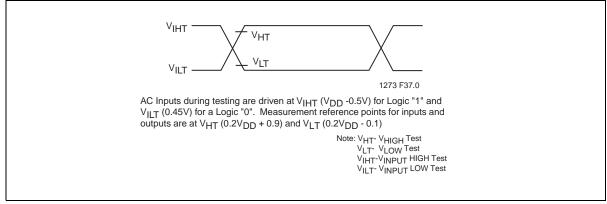

# Figure 41:AC Testing Input/Output Test Waveform

Data Sheet

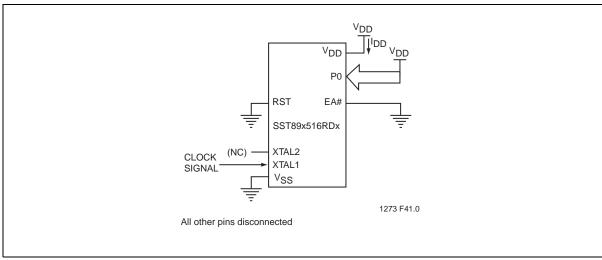

Figure 45:I<sub>DD</sub> Test Condition, Idle Mode

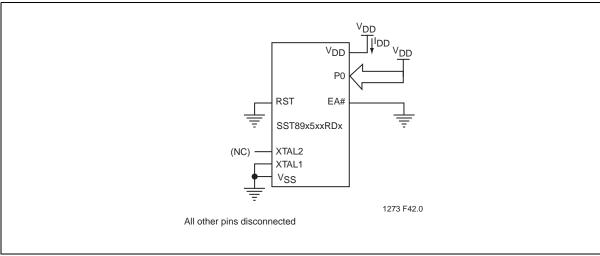

Figure 46:I<sub>DD</sub> Test Condition, Power-down Mode

| Table 41: Flash Memory Prog | ramming/Verification Parameters <sup>1</sup> |

|-----------------------------|----------------------------------------------|

|-----------------------------|----------------------------------------------|

| Parameter <sup>2</sup>              | Max | Units      |

|-------------------------------------|-----|------------|

| Chip-Erase Time                     | 150 | ms         |

| Block-Erase Time                    | 100 | ms         |

| Sector-Erase Time                   | 30  | ms         |

| Byte-Program Time <sup>3</sup>      | 50  | μs         |

| Select-Block Program Time           | 500 | ns         |

| Re-map or Security bit Program Time | 80  | μs         |

|                                     |     | T0-0.1 250 |

1. For IAP operations, the program execution overhead must be added to the above timing parameters.

2. Program and Erase times will scale inversely proportional to programming clock frequency.

3. Each byte must be erased before programming.

Data Sheet

## Table 42: Revision History

| Revision | Description                                                                                                                         | Date     |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|----------|

| 00       | <ul> <li>Initial Release of S71273 data sheet.<br/>SST89E/V516RD2 devices were previously released in S71255-00-<br/>000</li> </ul> |          |

|          | <ul> <li>S71273 and<br/>S71273(01): Added 40-WQFN (QI) package and associated MPNs</li> </ul>                                       |          |

|          | Added SST89E/V516RD PDIP devices and associated MPNs                                                                                |          |

|          | <ul> <li>Clarified the solder temperature profile under "Absolute Maximum<br/>Stress Ratings" on page 73</li> </ul>                 |          |

|          | <ul> <li>Added RoHS compliance information on page 1 and in the "Product<br/>Ordering Information" on page 88</li> </ul>            |          |

|          | <ul> <li>Removed references to External Host Mode programming</li> </ul>                                                            |          |

|          | • Corrected MPN breakdown definition for "2" to read "Port 4 present"                                                               |          |

|          | Corrected the SPI control Register definition for CPHA on page 30                                                                   |          |

| 01       | Status change from Preliminary Specifications to Data sheet                                                                         | Mar 2005 |

| 02       | Removed NJ, TQJ, and PI from Valid Combinations on page 78                                                                          | Oct 2006 |

|          | <ul> <li>Removed valid combination SST89E516RD-40-I-PIE and<br/>SST89V516RD-33-I-PIE on page 78</li> </ul>                          |          |

| 03       | Replaced FlashFlex51 with FlashFlex globally                                                                                        | Jan 2007 |

| А        | Applied new document format                                                                                                         | Nov 2011 |

|          | Released document under letter revision system                                                                                      |          |

|          | <ul> <li>Updated spec number from S71273 to DS25093</li> </ul>                                                                      |          |

| В        | • Removed "Not recommended for new designs" statement on page 1.                                                                    | Feb 2013 |

ISBN: 978-1-62076-989-8

© 2013 Silicon Storage Technology, Inc-a Microchip Technology Company. All rights reserved.

SST, Silicon Storage Technology, the SST logo, SuperFlash, MTP, and FlashFlex are registered trademarks of Silicon Storage Technology, Inc. MPF, SQI, Serial Quad I/O, and Z-Scale are trademarks of Silicon Storage Technology, Inc. All other trademarks and registered trademarks mentioned herein are the property of their respective owners.

Specifications are subject to change without notice. Refer to www.microchip.com for the most recent documentation. For the most current package drawings, please see the Packaging Specification located at http://www.microchip.com/packaging.

Memory sizes denote raw storage capacity; actual usable capacity may be less.

SST makes no warranty for the use of its products other than those expressly contained in the Standard Terms and Conditions of Sale.

For sales office locations and information, please see www.microchip.com.

#### Silicon Storage Technology, Inc. A Microchip Technology Company www.microchip.com