#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | 8051                                                                              |

| Core Size                  | 8-Bit                                                                             |

| Speed                      | 40MHz                                                                             |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                  |

| Number of I/O              | 36                                                                                |

| Program Memory Size        | 72KB (72K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 1K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                       |

| Data Converters            | -                                                                                 |

| Oscillator Type            | External                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-LCC (J-Lead)                                                                   |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89e516rd2-40-i-nje-t |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Data Sheet

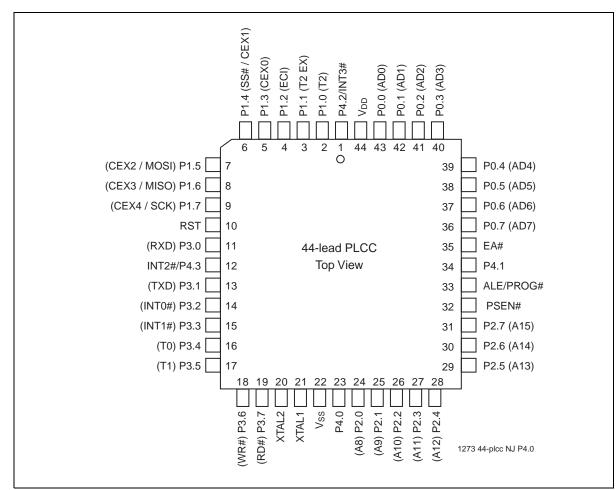

Figure 5: Pin Assignments for 44-lead PLCC

Data Sheet

| Location | 7                                        | 6                            | 5       | 4  | 3   | 2   | 1   | 0   | Reset Value |  |

|----------|------------------------------------------|------------------------------|---------|----|-----|-----|-----|-----|-------------|--|

| A8H      | EA                                       | EC                           | ET2     | ES | ET1 | EX1 | ET0 | EX0 | 00H         |  |

| Symbol   | Function                                 |                              |         |    |     |     |     |     |             |  |

| EA       | Global Inte<br>0 = Disable<br>1 = Enable |                              |         |    |     |     |     |     |             |  |

| EC       | PCA Interr                               | PCA Interrupt Enable.        |         |    |     |     |     |     |             |  |

| ET2      | Timer 2 In                               | terrupt En                   | able.   |    |     |     |     |     |             |  |

| ES       | Serial Inte                              | rrupt Enat                   | ole.    |    |     |     |     |     |             |  |

| ET1      | Timer 1 In                               | terrupt En                   | able.   |    |     |     |     |     |             |  |

| EX1      | External 1                               | External 1 Interrupt Enable. |         |    |     |     |     |     |             |  |

| ET0      | Timer 0 Interrupt Enable.                |                              |         |    |     |     |     |     |             |  |

| EX0      | External 0                               | Interrupt                    | Enable. |    |     |     |     |     |             |  |

#### Interrupt Enable A (IEA)

| Location | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0 | Reset Value |

|----------|---|---|---|---|-----|---|---|---|-------------|

| E8H      | - | - | - | - | EBO | - | - | - | xxxx0xxxb   |

### Symbol Function

EBO Brown-out Interrupt Enable.

1 = Enable the interrupt

0 = Disable the interrupt

Data Sheet

| Location            | 7           | 6                                                                                                                                                                              | 5               | 4              | 3            | 2            | 1              | 0           | Reset Value |  |  |

|---------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|--------------|--------------|----------------|-------------|-------------|--|--|

| 85H                 |             |                                                                                                                                                                                | Wa              | atchdog Tim    | er Data/Re   | load         |                |             | 00H         |  |  |

| Symbol              | Function    | unction                                                                                                                                                                        |                 |                |              |              |                |             |             |  |  |

| WDTD                | Initial/Rel | oad value                                                                                                                                                                      | in Watcho       | log Timer.     | New value    | won't be     | effective u    | intil WDT   | is set.     |  |  |

| CA Timer/Counter Co | ntrol Regi  | ster <sup>1</sup> (CCC                                                                                                                                                         | ON)             |                |              |              |                |             |             |  |  |

| Location            |             | 6                                                                                                                                                                              | 5               | 4              | 3            | 2            | 1              | 0           | Reset Value |  |  |

| D8H                 | CF          | CR                                                                                                                                                                             | -               | CCF4           | CCF3         | CCF2         | CCF1           | CCF0        | 00x00000k   |  |  |

|                     | 1. Bit add  | dressable                                                                                                                                                                      |                 |                |              |              |                |             |             |  |  |

| Symbol              | Function    | 1                                                                                                                                                                              |                 |                |              |              |                |             |             |  |  |

| CF                  |             | inter Overf                                                                                                                                                                    | •               |                |              |              |                |             |             |  |  |

|                     |             | et by hardware when the counter rolls over. CF flags an interrupt if bit ECF in CMOD is set.<br>F may be set by either hardware or software, but can only cleared by software. |                 |                |              |              |                |             |             |  |  |

| 00                  | -           | -                                                                                                                                                                              |                 | ware or so     | itware, but  | can only     | cleared by     | software    |             |  |  |

| CR                  |             | inter Run c                                                                                                                                                                    |                 | CA counter     | on Must      | he cleared   | hv softwa      | are to turn | the PCA     |  |  |

|                     | counter o   |                                                                                                                                                                                |                 | or counter     | on. Mast     |              | by solution    |             |             |  |  |

| -                   | Not imple   | emented, re                                                                                                                                                                    | eserved fo      | or future us   | e.           |              |                |             |             |  |  |

|                     | Note: User  | should not w                                                                                                                                                                   | rite '1's to re | served bits. 7 | he value rea | d from a res | erved bit is i | ndeterminat | e.          |  |  |

| CCF4                |             | dule 4 inter<br>cleared by                                                                                                                                                     |                 | Set by hare    | dware whe    | en a match   | or captur      | e occurs.   |             |  |  |

| CCF3                |             | •                                                                                                                                                                              |                 | Set by har     | dwaro whe    | n a match    | or cantur      |             |             |  |  |

| 0010                |             | cleared by                                                                                                                                                                     |                 | Set by hard    |              | a mator      | i or captur    | e occurs.   |             |  |  |

| CCF2                | PCA Mod     | lule 2 inter                                                                                                                                                                   | rupt flag.      | Set by hare    | dware whe    | n a match    | or captur      | e occurs.   |             |  |  |

|                     | Must be o   | cleared by                                                                                                                                                                     | software.       |                |              |              |                |             |             |  |  |

| CCF1                |             |                                                                                                                                                                                |                 | Set by hare    | dware whe    | en a match   | or captur      | e occurs.   |             |  |  |

| CCF0                |             | Aust be cleared by software.<br>PCA Module 0 interrupt flag. Set by hardware when a match or capture occurs.                                                                   |                 |                |              |              |                |             |             |  |  |

| CCFU                |             | cleared by                                                                                                                                                                     |                 | Set by han     | aware whe    | en a mater   | or captur      | e occurs.   |             |  |  |

|                     |             |                                                                                                                                                                                |                 |                |              |              |                |             |             |  |  |

|                     |             |                                                                                                                                                                                |                 |                |              |              |                |             |             |  |  |

| SPI Data Register (SPD | R)                                                |                                                                                                                                                           |           |              |            |              |            |            | Data Shee    |  |  |  |

|------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------|------------|--------------|------------|------------|--------------|--|--|--|

| Location               | 7                                                 | 6                                                                                                                                                         | 5         | 4            | 3          | 2            | 1          | 0          | Reset Value  |  |  |  |

| 86H                    | 86H SPDR[7:0]                                     |                                                                                                                                                           |           |              |            |              |            |            |              |  |  |  |

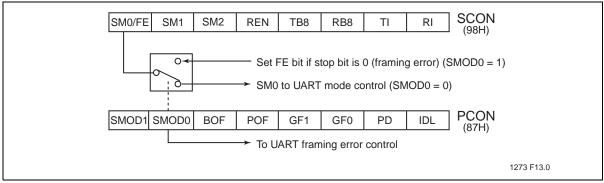

| Power Control Register | (PCON)                                            |                                                                                                                                                           |           |              |            |              |            |            |              |  |  |  |

| Location               | 7                                                 | 6                                                                                                                                                         | 5         | 4            | 3          | 2            | 1          | 0          | Reset Value  |  |  |  |

| 87H                    | SMOD1                                             | SMOD0                                                                                                                                                     | BOF       | POF          | GF1        | GF0          | PD         | IDL        | 00010000b    |  |  |  |

| Symbol                 | Function                                          |                                                                                                                                                           |           |              |            |              |            |            |              |  |  |  |

| SMOD1                  |                                                   | uble Baud rate bit. If SMOD1 = 1, Timer 1 is used to generate the baud rate, and the serial t is used in modes 1, 2, and 3.                               |           |              |            |              |            |            |              |  |  |  |

| SMOD0                  | 0: SCON[7                                         | E/SM0 Selection bit.<br>SCON[7] = SM0<br>SCON[7] = FE,                                                                                                    |           |              |            |              |            |            |              |  |  |  |

| BOF                    | cleared by<br>0: No brov                          | software.                                                                                                                                                 | Power-or  |              |            |              |            | reset. Bo  | DF should be |  |  |  |

| POF                    | Power-on<br>cleared by<br>0: No Pow<br>1: Power-o | y software.<br>er-on rese                                                                                                                                 | t.        | bit will not | be affecte | ed by any    | other rese | et. POF sl | hould be     |  |  |  |

| GF1                    | General-p                                         | urpose flag                                                                                                                                               | g bit.    |              |            |              |            |            |              |  |  |  |

| GF0                    | General-p                                         | urpose flag                                                                                                                                               | g bit.    |              |            |              |            |            |              |  |  |  |

| PD                     | 0: Power-o                                        | ower-down bit, this bit is cleared by hardware after exiting from power-down mode.<br>: Power-down mode is not activated.<br>: Activates Power-down mode. |           |              |            |              |            |            |              |  |  |  |

| IDL                    | Idle mode<br>0: Idle mo<br>1: Activate            |                                                                                                                                                           | ctivated. | d by hardv   | vare after | exiting froi | m idle mo  | de.        |              |  |  |  |

#### Data Sheet

#### Serial Port Control Register (SCON)

| Location | 7      | 6   | 5   | 4   | 3   | 2   | 1  | 0  | Reset Value |

|----------|--------|-----|-----|-----|-----|-----|----|----|-------------|

| 98H      | SM0/FE | SM1 | SM2 | REN | TB8 | RB8 | TI | RI | 0000000b    |

#### Symbol Function

| <ul> <li>FE Set SMOD0 = 1 to access FE bit.</li> <li>0: No framing error</li> <li>1: Framing Error. Set by receiver when an invalid stop bit is detected. This bit needs to be</li> </ul> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                           |

- SM0 SMOD0 = 0 to access SM0 bit. Serial Port Mode Bit 0

- SM1 Serial Port Mode Bit 1

| SM0 | SM1                    | Mode | Description    | Baud Rate <sup>1</sup>                                                                      |

|-----|------------------------|------|----------------|---------------------------------------------------------------------------------------------|

| 0   | 0                      | 0    | Shift Register | f <sub>OSC</sub> /6 (6 clock mode) or<br>f <sub>OSC</sub> /12 (12 clock mode)               |

| 0   | 1                      | 1    | 8-bit UART     | Variable                                                                                    |

| 1   | 0                      | 2    | 9-bit UART     | $f_{OSC}/32$ or $f_{OSC}/16$ (6 clock mode) or $f_{OSC}/64$ or $f_{OSC}/32$ (12 clock mode) |

| 1   | 1<br>illator fraguenov | 3    | 9-bit UART     | Variable                                                                                    |

1. f<sub>OSC</sub> = oscillator frequency

- SM2 Enables the Automatic Address Recognition feature in Modes 2 or 3. If SM2 = 1 then RI will not be set unless the received 9th data bit (RB8) is 1, indicating an address, and the received byte is a given or broadcast address. In Mode 1, if SM2 = 1 then RI will not be activated unless a valid stop bit was received. In Mode 0, SM2 should be 0.

- REN Enables serial reception. 0: to disable reception. 1: to enable reception.

- TB8 The 9th data bit that will be transmitted in Modes 2 and 3. Set or clear by software as

- desired.

- RB8 In Modes 2 and 3, the 9th data bit that was received. In Mode 1, if SM2 = 0, RB8 is the stop bit that was received. In Mode 0, RB8 is not used.

- TI Transmit interrupt flag. Set by hardware at the end of the 8th bit time in Mode 0, or at the beginning of the stop bit in the other modes, in any serial transmission, Must be cleared by software.

- RI Receive interrupt flag. Set by hardware at the end of the8th bit time in Mode 0, or halfway through the stop bit time in the other modes, in any serial reception (except see SM2). Must be cleared by software.

Data Sheet

## Flash Memory Programming

The device internal flash memory can be programmed or erased using In-Application Programming (IAP) mode

### **Product Identification**

The Read-ID command accesses the Signature Bytes that identify the device and the manufacturer as SST. External programmers primarily use these Signature Bytes in the selection of programming algorithms.

### Table 12: Product Identification

|                   | Address | Data |

|-------------------|---------|------|

| Manufacturer's ID | 30H     | BFH  |

| Device ID         |         |      |

| SST89E516RD2/RD   | 31H     | 93H  |

| SST89V516RD2/RD   | 31H     | 92H  |

T0-0.0 25093

### In-Application Programming Mode

The device offers either 72 KByte of in-application programmable flash memory. During in-application programming, the CPU of the microcontroller enters IAP mode. The two blocks of flash memory allow the CPU to execute user code from one block, while the other is being erased or reprogrammed concurrently. The CPU may also fetch code from an external memory while all internal flash is being reprogrammed. The mailbox registers (SFST, SFCM, SFAL, SFAH, SFDT and SFCF) located in the special function register (SFR), control and monitor the device's erase and program process.

Table 14 outline the commands and their associated mailbox register settings.

### In-Application Programming Mode Clock Source

During IAP mode, both the CPU core and the flash controller unit are driven off the external clock. However, an internal oscillator will provide timing references for Program and Erase operations. The internal oscillator is only turned on when required, and is turned off as soon as the flash operation is completed.

### Memory Bank Selection for In-Application Programming Mode

With the addressing range limited to 16 bit, only 64 KByte of program address space is "visible" at any one time. As shown in Table 13, the bank selection (the configuration of EA# and SFCF[1:0]), allows Block 1 memory to be overlaid on the lowest 8 KByte of Block 0 memory, making Block 1 reachable. The same concept is employed to allow both Block 0 and Block 1 flash to be accessible to IAP operations. Code from a block that is not visible may not be used as a source to program another address. However, a block that is not "visible" may be programmed by code from the other block through mailbox registers.

The device allows IAP code in one block of memory to program the other block of memory, but may not program any location in the same block. If an IAP operation originates physically from Block 0, the target of this operation is implicitly defined to be in Block 1. If the IAP operation originates physically from

Data Sheet

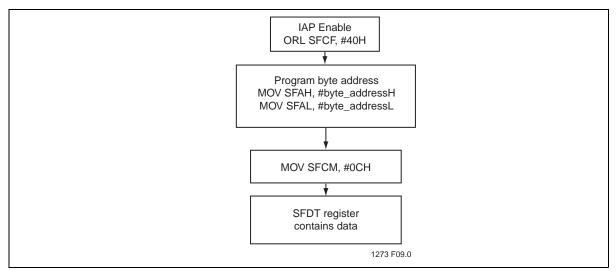

### Byte-Verify

The Byte-Verify command allows the user to verify that the device has correctly performed an Erase or Program command. Byte-Verify command returns the data byte in SFDT if the command is successful. The user is required to check that the previous flash operation has fully completed before issuing a Byte-Verify. Byte-Verify command execution time is short enough that there is no need to poll for command completion and no interrupt is generated.

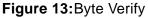

### Prog-SB3, Prog-SB2, Prog-SB1

Prog-SB3, Prog-SB2, Prog-SB1 commands are used to program the security bits (see Table 25). Completion of any of these commands, the security options will be updated immediately.

Security bits previously in un-programmed state can be programmed by these commands. Prog-SB3, Prog-SB2 and Prog-SB1 commands should only reside in Block 1 or external code memory.

### Figure 14: Prog-SB3, Prog-SB2, Prog-SB1

Data Sheet

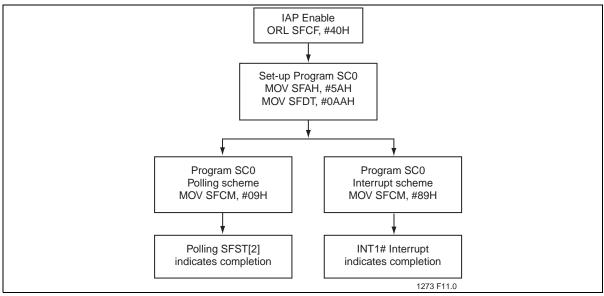

### Prog-SC0

Prog-SC0 command is used to program the SC0 bit. This command only changes the SC0 bit and has no effect on BSEL bit until after a reset cycle.

SC0 bit previously in un-programmed state can be programmed by this command. The Prog-SC0 command should reside only in Block 1 or external code memory.

### Figure 15: Prog-SC0

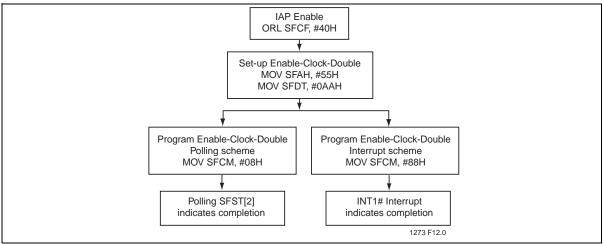

### Enable-Clock-Double

Enable-Clock-Double command is used to make the MCU run at 6 clocks per machine cycle. The standard (default) is 12 clocks per machine cycle (i.e. clock double command disabled).

### Figure 16: Enable-Clock-Double

There are no IAP counterparts for the external host commands Select-Block0 and Select-Block1.

Data Sheet

## Serial I/O

## Full-Duplex, Enhanced UART

The device serial I/O port is a full-duplex port that allows data to be transmitted and received simultaneously in hardware by the transmit and receive registers, respectively, while the software is performing other tasks. The transmit and receive registers are both located in the Serial Data Buffer (SBUF) special function register. Writing to the SBUF register loads the transmit register, and reading from the SBUF register obtains the contents of the receive register.

The UART has four modes of operation which are selected by the Serial Port Mode Specifier (SM0 and SM1) bits of the Serial Port Control (SCON) special function register. In all four modes, transmission is initiated by any instruction that uses the SBUF register as a destination register. Reception is initiated in mode 0 when the Receive Interrupt (RI) flag bit of the Serial Port Control (SCON) SFR is cleared and the Reception Enable/ Disable (REN) bit of the SCON register is set. Reception is initiated in the other modes by the incoming start bit if the REN bit of the SCON register is set.

### **Framing Error Detection**

Framing Error Detection is a feature, which allows the receiving controller to check for valid stop bits in modes 1, 2, or 3. Missing stops bits can be caused by noise in serial lines or from simultaneous transmission by two CPUs.

Framing Error Detection is selected by going to the PCON register and changing SMOD0 = 1 (see Figure 17). If a stop bit is missing, the Framing Error bit (FE) will be set. Software may examine the FE bit after each reception to check for data errors. After the FE bit has been set, it can only be cleared by software. Valid stop bits do not clear FE. When FE is enabled, RI rises on the stop bit, instead of the last data bit (see Figure 18 and Figure 19).

Figure 17: Framing Error Block Diagram

#### Data Sheet

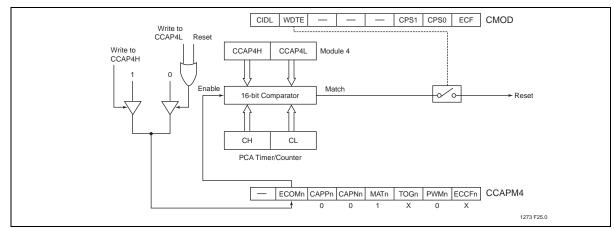

an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software. Each module has its own timer interrupt or capture interrupt flag (CCF0 for module 0, CCF4 for module 4, etc.). They are set when either a match or capture occurs. These flags can only be cleared by software. (See "PCA Timer/Counter Control Register (CCON)" on page 27.)

### **Compare/Capture Modules**

Each PCA module has an associated SFR with it. These registers are: CCAPM0 for module 0, CCAPM1 for module 1, etc. Refer to "PCA Compare/Capture Module Mode Register (CCAPMn)" on page 29 for details. The registers each contain 7 bits which are used to control the mode each module will operate in. The ECCF bit (CCAPMn.0 where n = 0, 1, 2, 3, or 4 depending on module) will enable the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs. PWM (CCAPMn.1) enables the pulse width modulation mode. The TOG bit (CCAPMn.2) when set, causes the CEX output associated with the module to toggle when there is a match between the PCA counter and the module's capture/compare register. When there is a match between the PCA counter and the module's capture/compare register, the MATn (CCAPMn.3) and the CCFn bit in the CCON register to be set.

Bits CAPN (CCAPMn.4) and CAPP (CCAPMn.5) determine whether the capture input will be active on a positive edge or negative edge. The CAPN bit enables the negative edge that a capture input will be active on, and the CAPP bit enables the positive edge. When both bits are set, both edges will be enabled and a capture will occur for either transition. The last bit in the register ECOM (CCAPMn.6) when set, enables the comparator function. Table 22 shows the CCAPMn settings for the various PCA functions.

There are two additional register associated with each of the PCA modules: CCAPnH and CCAPnL. They are registers that hold the 16-bit count value when a capture occurs or a compare occurs. When a module is used in PWM mode, these registers are used to control the duty cycle of the output. See Figure 24.

| Symbol | Description               | Direct<br>Address | Bit Address, Symbol, or Alternative Port Function MSB LSB | RESET<br>Value |

|--------|---------------------------|-------------------|-----------------------------------------------------------|----------------|

| CCAP0H | PCA Module 0              | FAH               | CCAP0H[7:0]                                               | 00H            |

| CCAP0L | Compare/Capture Registers | EAH               | CCAP0L[7:0]                                               | 00H            |

| CCAP1H | PCA Module 1              | FBH               | CCAP1H[7:0]                                               | 00H            |

| CCAP1L | Compare/Capture Registers | EBH               | CCAP1L[7:0]                                               | 00H            |

| CCAP2H | PCA Module 2              | FCH               | CCAP2H[7:0]                                               | 00H            |

| CCAP2L | Compare/Capture Registers | ECH               | CCAP2L[7:0]                                               | 00H            |

| CCAP3H | PCA Module 3              | FDH               | CCAP3H[7:0]                                               | 00H            |

| CCAP3L | Compare/Capture Registers | EDH               | CCAP3L[7:0]                                               | 00H            |

| CCAP4H | PCA Module 4              | FEH               | CCAP4H[7:0]                                               | 00H            |

| CCAP4L | Compare/Capture Registers | EEH               | CCAP4L[7:0]                                               | 00H            |

### Table 21: PCA High and Low Register Compare/Capture Modules

T0-0.0 25093

Data Sheet

### Table 22: PCA Module Modes

| W  | ithout Inte        | rrupt ena          | bled               |                   |                        |                   |                    |                                                              |

|----|--------------------|--------------------|--------------------|-------------------|------------------------|-------------------|--------------------|--------------------------------------------------------------|

| _1 | ECOMy <sup>2</sup> | CAPPy <sup>2</sup> | CAPNy <sup>2</sup> | MATy <sup>2</sup> | TOGy <sup>2</sup>      | PWMy <sup>2</sup> | ECCFy <sup>2</sup> | Module Code                                                  |

| -  | 0                  | 0                  | 0                  | 0                 | 0                      | 0                 | 0                  | No Operation                                                 |

| -  | 0                  | 1                  | 0                  | 0                 | 0                      | 0                 | 0                  | 16-bit capture on positive-edge trigger at CEX[4:0]          |

| -  | 0                  | 0                  | 1                  | 0                 | 0                      | 0                 | 0                  | 16-bit capture on negative-edge trigger at CEX[4:0]          |

| -  | 0                  | 1                  | 1                  | 0                 | 0                      | 0                 | 0                  | 16-bit capture on positive/negative-edge trigger at CEX[4:0] |

| -  | 1                  | 0                  | 0                  | 1                 | 0                      | 0                 | 0                  | Compare: software timer                                      |

| -  | 1                  | 0                  | 0                  | 1                 | 1                      | 0                 | 0                  | Compare: high-speed output                                   |

| -  | 1                  | 0                  | 0                  | 0                 | 0                      | 1                 | 0                  | Compare: 8-bit PWM                                           |

| -  | 1                  | 0                  | 0                  | 1                 | 0 or<br>1 <sup>3</sup> | 0                 | 0                  | Compare: PCA WDT (CCAPM4 only) <sup>4</sup>                  |

T0-0.0 25093

1. User should not write '1's to reserved bits. The value read from a reserved bit is indeterminate.

2. y = 0, 1, 2, 3, 4

3. A 0 disables toggle function. A 1 enables toggle function on CEX[4:0] pin.

4. For PCA WDT mode, also set the WDTE bit in the CMOD register to enable the reset output signal.

| Wi | th Interrup        | t enabled          |                    |                   |                     |                   |                    |                                                                     |

|----|--------------------|--------------------|--------------------|-------------------|---------------------|-------------------|--------------------|---------------------------------------------------------------------|

| _1 | ECOMy <sup>2</sup> | CAPPy <sup>2</sup> | CAPNy <sup>2</sup> | MATy <sup>2</sup> | TOGy <sup>2</sup>   | PWMy <sup>2</sup> | ECCFy <sup>2</sup> | Module Code                                                         |

| -  | 0                  | 1                  | 0                  | 0                 | 0                   | 0                 | 1                  | 16-bit capture on positive-edge trig-<br>ger at CEX[4:0]            |

| -  | 0                  | 0                  | 1                  | 0                 | 0                   | 0                 | 1                  | 16-bit capture on negative-edge trig-<br>ger at CEX[4:0]            |

| -  | 0                  | 1                  | 1                  | 0                 | 0                   | 0                 | 1                  | 16-bit capture on positive/negative-<br>edge<br>trigger at CEX[4:0] |

| -  | 1                  | 0                  | 0                  | 1                 | 0                   | 0                 | 1                  | Compare: software timer                                             |

| -  | 1                  | 0                  | 0                  | 1                 | 1                   | 0                 | 1                  | Compare: high-speed output                                          |

| -  | 1                  | 0                  | 0                  | 0                 | 0                   | 1                 | X <sup>3</sup>     | Compare: 8-bit PWM                                                  |

| -  | 1                  | 0                  | 0                  | 1                 | 0 or 1 <sup>4</sup> | 0                 | X <sup>5</sup>     | Compare: PCA WDT (CCAPM4 only) <sup>6</sup>                         |

#### Table 23: PCA Module Modes

T0-0.0 25093

1. User should not write '1's to reserved bits. The value read from a reserved bit is indeterminate.

2. y = 0, 1, 2, 3, 4

3. No PCA interrupt is needed to generate the PWM.

4. A 0 disables toggle function. A 1 enables toggle function on CEX[4:0] pin.

5. Enabling an interrupt for the Watchdog Timer would defeat the purpose of the Watchdog Timer.

6. For PCA WDT mode, also set the WDTE bit in the CMOD register to enable the reset output signal.

Data Sheet

CLR EA; Hold off interrupts

MOVCCAP4L, #00; Next compare value is within

MOVCCAP4H, CH; 65,535 counts of the ; current PCA

SETBEA; timer value

RET

This routine should not be part of an interrupt service routine. If the program counter goes astray and gets stuck in an infinite loop, interrupts will still be serviced and the watchdog will keep getting reset. Thus, the purpose of the watchdog would be defeated. Instead, call this subroutine from the main program of the PCA timer.

Figure 29: PCA Watchdog Timer (Module 4 only)

Data Sheet

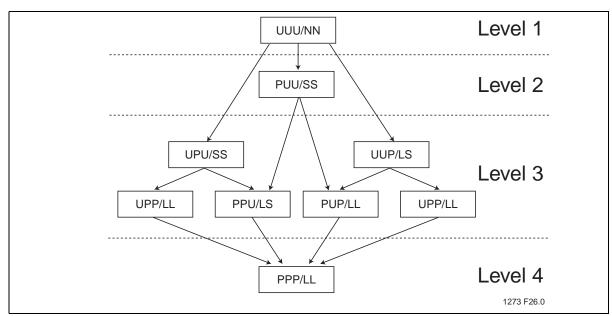

### Figure 30: Security Lock Levels

Note: P = Programmed (Bit logic state = 0), U = Unprogrammed (Bit logic state = 1), N = Not Locked, L = Hard locked, S = Soft locked

|       | Security Lock Bits <sup>1,2</sup> |        |                  | Security Status of: |           |           |                                                                                                                                                                                                                              |

|-------|-----------------------------------|--------|------------------|---------------------|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Level | SFST[7:5]                         | SB1    | SB2 <sup>1</sup> | SB3 <sup>1</sup>    | Block 1   | Block 0   | Security Type                                                                                                                                                                                                                |

| 1     | 000                               | U      | U                | U                   | Unlock    | Unlock    | No Security Features are<br>Enabled.                                                                                                                                                                                         |

| 2     | 100                               | Ρ      | U                | U                   | SoftLock  | SoftLock  | MOVC instructions executed from<br>external program memory are<br>disabled from fetching code bytes<br>from internal memory, EA# is<br>sampled and latched on Reset,<br>and further programming of the<br>flash is disabled. |

| 3     | 011<br>101                        | U<br>P | P<br>U           | P<br>P              | Hard Lock | Hard Lock | Level 2 plus Verify disabled, both blocks locked.                                                                                                                                                                            |

|       | 010                               | U      | P                | U                   | SoftLock  | SoftLock  | Level 2 plus Verify disabled. Code<br>in Block 1 may program Block 0<br>and vice versa.                                                                                                                                      |

|       | 110<br>001                        | P<br>U | P<br>U           | U<br>P              | Hard Lock | SoftLock  | Level 2 plus Verify disabled. Code<br>in Block 1 may program Block 0.                                                                                                                                                        |

| 4     | 111                               | Ρ      | Ρ                | Ρ                   | Hard Lock | Hard Lock | Same as Level 3 hard lock/hard<br>lock, but MCU will start code exe-<br>cution from the internal memory<br>regardless of EA#.                                                                                                |

#### Table 25: Security Lock Options

1. P = Programmed (Bit logic state = 0), U = Unprogrammed (Bit logic state = 1).

2. SFST[7:5] = Security Lock Status Bits (SB1\_i, SB2\_i, SB3\_i)

©2013 Silicon Storage Technology, Inc.

T0-0.0 25093

Data Sheet

## Read Operation Under Lock Condition

The status of security bits SB1, SB2, and SB3 can be read when the read command is disabled by security lock. There are three ways to read the status.

- 1. External host mode: Read-back = 00H (locked)

- 2. IAP command: Read-back = previous SFDT data

- 3. MOVC: Read-back = FFH (blank)

#### Table 26: Security Lock Access Table

|       |                                                           | Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Target               | Byte-Verify Allo           | MOVC Allowed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

|-------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Level | SFST[7:5]                                                 | Address <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Address <sup>2</sup> | External Host <sup>3</sup> | IAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 516RDx |

|       |                                                           | Dia als 0/4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Block 0/1            | N                          | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Y      |

| 4     | 111b                                                      | BIOCK 0/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | External             | N/A                        | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Ν      |

| 4     | (hard lock on both blocks)                                | FST[7:5]Address1Address2External Host3I/A111b<br>(c on both blocks)Block 0/1NNNExternal $Block 0/1$ NNNExternal $External$ $Block 0/1$ NN11b/101b<br>(c on both blocks)Block 0/1NNN $Block 0/1$ Block 0/1NNN $External$ $Block 0/1$ NNN $External$ $Block 0/1$ NNN $External$ $Block 0/1$ NNN $External$ $Block 0/1$ NNN $D1b/110b$<br>(c on both blocks) $Block 0$ NNN $D1b/110b$<br>(c on both blocks) $Block 1$ NNN $D10b/$ | Ν                    | N                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

|       |                                                           | External                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | External             | N/A                        | ernal Host <sup>3</sup> IAP         516RDx           N         N         Y           N/A         N/A         N           N         N         N           N/A         N/A         Y           N/A         N/A         Y           N/A         N/A         Y           N/A         N/A         Y           N/A         N/A         N           N/A | Ν      |

|       |                                                           | Diack 0/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Block 0/1            | N                          | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Y      |

|       | 011b/101b                                                 | BIOCK U/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | External             | N/A                        | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | N      |

|       | (hard lock on both blocks)                                | External                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Block 0/1            | N                          | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | N      |

|       |                                                           | External                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | External             | N/A                        | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Y      |

|       |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Block 0              | N                          | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Y      |

|       |                                                           | Block 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Block 1              | N                          | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | N      |

|       |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | External             | N/A                        | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | N      |

|       | 001b/110b<br>(Block 0 = SoftLock,<br>Block 1 = hard lock) | Block 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Block 0              | N                          | Υ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Y      |

|       |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Block 1              | N                          | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Y      |

| 3     |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | External             | N/A                        | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | N      |

| 3     |                                                           | External                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Block 0/1            | N                          | Ν                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | N      |

|       |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | External             | N/A                        | N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Y      |