#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                      |

|----------------------------|--------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                             |

| Core Processor             | 8051                                                                                 |

| Core Size                  | 8-Bit                                                                                |

| Speed                      | 40MHz                                                                                |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                             |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                     |

| Number of I/O              | 36                                                                                   |

| Program Memory Size        | 72KB (72K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 1K x 8                                                                               |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                          |

| Data Converters            | -                                                                                    |

| Oscillator Type            | External                                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 44-TQFP                                                                              |

| Supplier Device Package    | 44-TQFP (10x10)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89e516rd2-40-i-tqje-nxx |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Data Sheet

## **Product Description**

The SST89E516RDx and SST89V516RDx are members of the FlashFlex family of 8-bit microcontroller products designed and manufactured with SST's patented and proprietary SuperFlash CMOS semiconductor process technology. The split-gate cell design and thick-oxide tunneling injector offer significant cost and reliability benefits for SST's customers. The devices use the 8051 instruction set and are pin-for-pin compatible with standard 8051 microcontroller devices.

The devices come with 72 KByte of on-chip flash EEPROM program memory which is partitioned into 2 independent program memory blocks. The primary Block 0 occupies 64 KByte of internal program memory space and the secondary Block 1 occupies 8 KByte of internal program memory space.

The 8-KByte secondary block can be mapped to the lowest location of the 64 KByte address space; it can also be hidden from the program counter and used as an independent EEPROM-like data memory.

In addition to the 72 KByte of EEPROM program memory on-chip and 1024 x8 bits of on-chip RAM, the devices can address up to 64 KByte of external program memory and up to 64 KByte of external RAM.

The flash memory blocks can be programmed via a standard 87C5x OTP EPROM programmer fitted with a special adapter and the firmware for SST's devices. During power-on reset, the devices can be configured as either a slave to an external host for source code storage or a master to an external host for an in-application programming (IAP) operation. The devices are designed to be programmed in-system and in-application on the printed circuit board for maximum flexibility. The devices are pre-programmed with an example of the bootstrap loader in the memory, demonstrating the initial user program code loading or subsequent user code updating via the IAP operation. The sample bootstrap loader is available for the user's reference and convenience only; SST does not guarantee its functionality or usefulness. Chip-Erase or Block-Erase operations will erase the pre-programmed sample code.

Data Sheet

## **Memory Organization**

The device has separate address spaces for program and data memory.

## **Program Flash Memory**

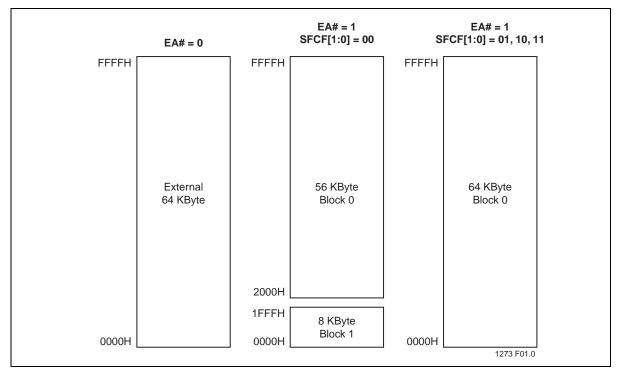

There are two internal flash memory blocks in the device. The primary flash memory block (Block 0) has 64 KByte. The secondary flash memory block (Block 1) has 8 KByte. Since the total program address space is limited to 64 KByte, the SFCF[1:0] bit are used to control program bank selection. Please refer to Figure 6 for the program memory configuration. Program bank selection is described in the next section.

The 64K x8 primary SuperFlash block is organized as 512 sectors, each sector consists of 128 Bytes.

The 8K x8 secondary SuperFlash block is organized as 64 sectors, each sector consists also of 128 Bytes.

For both blocks, the 7 least significant program address bits select the byte within the sector. The remainder of the program address bits select the sector within the block.

Figure 6: Program Memory Organization

Data Sheet

## Program Memory Block Switching

The program memory block switching feature of the device allows either Block 1 or the lowest 8 KByte of Block 0 to be used for the lowest 8 KByte of the program address space. SFCF[1:0] controls program memory block switching.

### Table 2: SFCF Values for Program Memory Block Switching

| SFCF[1:0]  | Program Memory Block Switching                                                                                                                                                                                                                                                                                                                              |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01, 10, 11 | Block 1 is not visible to the program counter (PC).<br>Block 1 is reachable only via in-application programming from 0000H - 1FFFH.                                                                                                                                                                                                                         |

| 00         | Block 1 is overlaid onto the low 8K of the program address space; occupying address locations 0000H - 1FFFH.<br>When the PC falls within 0000H - 1FFFH, the instruction will be fetched from Block 1 instead of Block 0.<br>Outside of 0000H - 1FFFH, Block 0 is used. Locations 0000H - 1FFFH of Block 0 are reachable through in-application programming. |

T0-0.0 25093

### **Reset Configuration of Program Memory Block Switching**

Program memory block switching is initialized after reset according to the state of the Start-up Configuration bit SC0. The SC0 bit is programmed via an external host mode command or an IAP Mode command. See Table 14.

Once out of reset, the SFCF[0] bit can be changed dynamically by the program for desired effects. Changing SFCF[0] will not change the SC0 bit.

Caution must be taken when dynamically changing the SFCF[0] bit. Since this will cause different physical memory to be mapped to the logical program address space. The user must avoid executing block switching instructions within the address range 0000H to 1FFFH.

|                  |                                     | State of SFCF[1:0] after:             |                   |  |  |  |  |  |  |  |

|------------------|-------------------------------------|---------------------------------------|-------------------|--|--|--|--|--|--|--|

| SC0 <sup>1</sup> | Power-on<br>or<br>External<br>Reset | WDT Reset<br>or<br>Brown-out<br>Reset | Software<br>Reset |  |  |  |  |  |  |  |

| U (1)            | 00<br>(default)                     | x0                                    | 10                |  |  |  |  |  |  |  |

| P (0)            | 01                                  | x1                                    | 11                |  |  |  |  |  |  |  |

| ·                |                                     |                                       | T0-0.0 250        |  |  |  |  |  |  |  |

**Table 3:** SFCF Values Under Different Reset Conditions

1. P = Programmed (Bit logic state = 0),

U = Unprogrammed (Bit logic state = 1)

### Data RAM Memory

The data RAM has 1024 bytes of internal memory. The RAM can be addressed up to 64KB for external data memory.

Data Sheet

high-order eight address bits (DPH), and Port 0 multiplexes the low order eight address bits (DPL) with data. Both MOVX @Ri and MOVX @DPTR generates the necessary read and write signals (P3.6 - WR# and P3.7 - RD#) for external memory use. Table 4 shows external data memory RD#, WR# operation with EXTRAM bit.

The stack pointer (SP) can be located anywhere within the 256 bytes of internal RAM (lower 128 bytes and upper 128 bytes). The stack pointer may not be located in any part of the expanded RAM.

|            | MOVX @DPTR, A or       | MOVX A, @DPTR      | MOVX @Ri, A or MOVX A, @Ri          |

|------------|------------------------|--------------------|-------------------------------------|

| AUXR       | ADDR < 0300H           | ADDR >= 0300H      | ADDR = Any                          |

| EXTRAM = 0 | RD# / WR# not asserted | RD# / WR# asserted | RD# / WR# not asserted <sup>1</sup> |

| EXTRAM = 1 | RD# / WR# asserted     | RD# / WR# asserted | RD# / WR# asserted                  |

#### Table 4: External Data Memory RD#, WR# with EXTRAM bit

1. Access limited to ERAM address within 0 to 0FFH; cannot access 100H to 02FFH.

T0-0.0 25093

Data Sheet

### Table 10: Interface SFRs

|                 |                          | Direct  | Bit Addr   | ess, Syn   | nbol, or A | Iternativ | /e Port F | unction   | 1        |                    | RESET        |

|-----------------|--------------------------|---------|------------|------------|------------|-----------|-----------|-----------|----------|--------------------|--------------|

| Symbol          | Description              | Address | MSB        |            |            |           |           |           |          | LSB                | Value        |

| SBUF            | Serial Data Buf-<br>fer  | 99H     | SBUF[7:0]  |            |            |           |           |           |          | Indetermi-<br>nate |              |

| SCON<br>1       | Serial Port Con-<br>trol | 98H     | SM0/<br>FE | SM1        | SM2        | REN       | TB8       | RB8       | ΤI       | RI                 | 00H          |

| SADD<br>R       | Slave Address            | A9H     |            | SADDR[7:0] |            |           |           |           |          |                    |              |

| SADE<br>N       | Slave Address<br>Mask    | B9H     |            | SADEN[7:0] |            |           |           |           |          |                    | 00H          |

| SPCR            | SPI Control<br>Register  | D5H     | SPIE       | SPE        | DOR<br>D   | MST<br>R  | CPO<br>L  | CPH<br>A  | SPR<br>1 | SPR<br>0           | 04H          |

| SPSR            | SPI Status<br>Register   | AAH     | SPIF       | WCO<br>L   |            |           |           |           |          |                    | 00H          |

| SPDR            | SPI Data Regis-<br>ter   | 86H     |            |            |            | SPDR[     | 7:0]      |           |          |                    | 00H          |

| P0 <sup>1</sup> | Port 0                   | 80H     |            |            |            | P0[7:     | 0]        |           |          |                    | FFH          |

| P1 <sup>1</sup> | Port 1                   | 90H     | -          | -          | -          | -         | -         | -         | T2E<br>X | T2                 | FFH          |

| P2 <sup>1</sup> | Port 2                   | A0H     |            |            | •          | P2[7:     | 0]        |           | •        | •                  | FFH          |

| P3 <sup>1</sup> | Port 3                   | B0H     | RD#        | WR#        | T1         | Т0        | INT1<br># | INT0<br># | TXD      | RXD                | FFH          |

| P4 <sup>2</sup> | Port 4                   | A5H     | 1          | 1          | 1          | 1         | P4.3      | P4.2      | P4.1     | P4.0               | FFH          |

|                 |                          | •       |            | •          |            |           |           | •         |          |                    | T0-0.0 25093 |

1. Bit Addressable SFRs

2. P4 is similar to P1 and P3 ports

Data Sheet

### Table 11: PCA SFRs

|                   |                                            | Direct     |          | Bit Add     | dress, Syı | nbol, or A   | Alternati | ive Port | Function | า         | RESET         |  |

|-------------------|--------------------------------------------|------------|----------|-------------|------------|--------------|-----------|----------|----------|-----------|---------------|--|

| Symbol            | Description                                | Address    | MSB      |             |            |              |           |          |          | LSB       | Value         |  |

| CH<br>CL          | PCA Timer/Coun-<br>ter                     | F9H<br>E9H |          |             |            | CH[7<br>CL[7 |           |          |          |           | 00H<br>00H    |  |

| CCON <sup>1</sup> | PCA Timer/Coun-<br>ter<br>Control Register | D8H        | CF       | CR          | -          | CCF4         | CCF<br>3  | CCF<br>2 | CCF<br>1 | CCF0      | 00x0000<br>0b |  |

| CMOD              | PCA Timer/Coun-<br>ter<br>Mode Register    | D9H        | CID<br>L | WDTE        | -          | -            | -         | CPS<br>1 | CPS<br>0 | ECF       | 00xxx000<br>b |  |

| CCAP0<br>H        | PCA Module 0<br>Compare/Cap-               | FAH        |          | CCAP0H[7:0] |            |              |           |          |          |           |               |  |

| CCAP0<br>L        | ture<br>Registers                          | EAH        |          | CCAP0L[7:0] |            |              |           |          |          |           |               |  |

| CCAP1<br>H        | PCA Module 1<br>Compare/Cap-               | FBH        |          | CCAP1H[7:0] |            |              |           |          |          |           |               |  |

| CCAP1<br>L        | ture<br>Registers                          | EBH        |          | CCAP1L[7:0] |            |              |           |          |          |           |               |  |

| CCAP2<br>H        | PCA Module 2<br>Compare/Cap-               | FCH        |          | CCAP2H[7:0] |            |              |           |          |          |           |               |  |

| CCAP2<br>L        | ture<br>Registers                          | ECH        |          | CCAP2L[7:0] |            |              |           |          |          |           |               |  |

| CCAP3<br>H        | PCA Module 3<br>Compare/Cap-               | FDH        |          | CCAP3H[7:0] |            |              |           |          |          |           |               |  |

| CCAP3<br>L        | ture<br>Registers                          | EDH        |          |             |            | CCAP3        | BL[7:0]   |          |          |           | 00H           |  |

| CCAP4<br>H        | PCA Module 4<br>Compare/Cap-               | FEH        |          |             |            | CCAP4        | H[7:0]    |          |          |           | 00H           |  |

| CCAP4<br>L        | ture<br>Registers                          | EEH        |          |             |            | CCAP4        | L[7:0]    |          |          |           | 00H           |  |

| CCAPM<br>0        | PCA<br>Compare/Cap-                        | DAH        | -        | ECOM<br>0   | CAPP<br>0  | CAPN<br>0    | MAT<br>0  | TOG<br>0 | PWM<br>0 | ECCF<br>0 | x000000<br>0b |  |

| CCAPM<br>1        | ture<br>Module Mode                        | DBH        | -        | ECOM<br>1   | CAPP<br>1  | CAPN<br>1    | MAT<br>1  | TOG<br>1 | PWM<br>1 | ECCF<br>1 | x000000<br>0b |  |

| CCAPM<br>2        | Registers                                  | DCH        | -        | ECOM<br>2   | CAPP<br>2  | CAPN<br>2    | MAT<br>2  | TOG<br>2 | PWM<br>2 | ECCF<br>2 | x000000<br>0b |  |

| CCAPM<br>3        |                                            | DDH        | -        | ECOM<br>3   | CAPP<br>3  | CAPN<br>3    | MAT<br>3  | TOG<br>3 | PWM<br>3 | ECCF<br>3 | x000000<br>0b |  |

| CCAPM<br>4        |                                            | DEH        | -        | ECOM<br>4   | CAPP<br>4  | CAPN<br>4    | MAT<br>4  | TOG<br>4 | PWM<br>4 | ECCF<br>4 | x000000<br>0b |  |

1. Bit Addressable SFRs

T0-0.0 25093

#### Data Sheet

#### SuperFlash Configuration Register (SFCF)

| Location | 7 | 6     | 5 | 4 | 3 | 2 | 1   | 0    | Reset Value |

|----------|---|-------|---|---|---|---|-----|------|-------------|

| B1H      | - | IAPEN | - | - | - | - | SWR | BSEL | x0xxxx00b   |

#### Symbol Function

| IAPEN | Enable IAP operation<br>0: IAP commands are disabled<br>1: IAP commands are enabled |

|-------|-------------------------------------------------------------------------------------|

| SWR   | Software Reset<br>See Section , "Software Reset"                                    |

| BSEL  | Program memory block switching bit<br>See Figure 6 and Table 3                      |

#### SuperFlash Command Register (SFCM)

| Location | 7   | 6    | 5    | 4    | 3    | 2    | 1    | 0    | Reset Value |

|----------|-----|------|------|------|------|------|------|------|-------------|

| B2H      | FIE | FCM6 | FCM5 | FCM4 | FCM3 | FCM2 | FCM1 | FCM0 | 00H         |

#### Symbol Function

FIE Flash Interrupt Enable.

0: INT1# is not reassigned.

1: INT1# is re-assigned to signal IAP operation completion. External INT1# interrupts are ignored.

FCM[6:0] Flash operation command

| 000_0001b     | Chip-Erase               |

|---------------|--------------------------|

| 000_1011b     | Sector-Erase             |

| 000_1101b     | Block-Erase              |

| 000_1100b     | Byte-Verify <sup>1</sup> |

| 000_1110b     | Byte-Program             |

| 000_1111b     | Prog-SB1                 |

| 000_0011b     | Prog-SB2                 |

| 000_0101b     | Prog-SB3                 |

| 000_1001b     | Prog-SC0                 |

| 000_1000bEr   | nable-Clock-Double       |

| All other com | binations are not im     |

All other combinations are not implemented, and reserved for future use.

1. Byte-Verify has a single machine cycle latency and will not generate any INT1# interrupt regardless of FIE.

### SuperFlash Address Registers (SFAL)

| Location | 7 | 6 | 5          | 4         | 3          | 2           | 1  | 0 | Reset Value |

|----------|---|---|------------|-----------|------------|-------------|----|---|-------------|

| B3H      |   | ŝ | SuperFlash | Low Order | Byte Addre | ess Registe | er |   | 00H         |

#### Symbol Function

SFAL

L Mailbox register for interfacing with flash memory block. (Low order address register).

Data Sheet

| Location | 7                                        | 6          | 5       | 4  | 3   | 2   | 1   | 0   | Reset Value |

|----------|------------------------------------------|------------|---------|----|-----|-----|-----|-----|-------------|

| A8H      | EA                                       | EC         | ET2     | ES | ET1 | EX1 | ET0 | EX0 | 00H         |

| Symbol   | Function                                 |            |         |    |     |     |     |     |             |

| EA       | Global Inte<br>0 = Disable<br>1 = Enable | Э          | ble.    |    |     |     |     |     |             |

| EC       | PCA Interr                               | upt Enabl  | e.      |    |     |     |     |     |             |

| ET2      | Timer 2 In                               | terrupt En | able.   |    |     |     |     |     |             |

| ES       | Serial Inte                              | rrupt Enat | ole.    |    |     |     |     |     |             |

| ET1      | Timer 1 In                               | terrupt En | able.   |    |     |     |     |     |             |

| EX1      | External 1                               | Interrupt  | Enable. |    |     |     |     |     |             |

| ET0      | Timer 0 In                               | terrupt En | able.   |    |     |     |     |     |             |

| EX0      | External 0                               | Interrupt  | Enable. |    |     |     |     |     |             |

#### Interrupt Enable A (IEA)

| Location | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0 | Reset Value |

|----------|---|---|---|---|-----|---|---|---|-------------|

| E8H      | - | - | - | - | EBO | - | - | - | xxxx0xxxb   |

### Symbol Function

EBO Brown-out Interrupt Enable.

1 = Enable the interrupt

0 = Disable the interrupt

Data Sheet

## Flash Memory Programming

The device internal flash memory can be programmed or erased using In-Application Programming (IAP) mode

## **Product Identification**

The Read-ID command accesses the Signature Bytes that identify the device and the manufacturer as SST. External programmers primarily use these Signature Bytes in the selection of programming algorithms.

#### Table 12: Product Identification

|                   | Address | Data |

|-------------------|---------|------|

| Manufacturer's ID | 30H     | BFH  |

| Device ID         |         |      |

| SST89E516RD2/RD   | 31H     | 93H  |

| SST89V516RD2/RD   | 31H     | 92H  |

T0-0.0 25093

### In-Application Programming Mode

The device offers either 72 KByte of in-application programmable flash memory. During in-application programming, the CPU of the microcontroller enters IAP mode. The two blocks of flash memory allow the CPU to execute user code from one block, while the other is being erased or reprogrammed concurrently. The CPU may also fetch code from an external memory while all internal flash is being reprogrammed. The mailbox registers (SFST, SFCM, SFAL, SFAH, SFDT and SFCF) located in the special function register (SFR), control and monitor the device's erase and program process.

Table 14 outline the commands and their associated mailbox register settings.

### In-Application Programming Mode Clock Source

During IAP mode, both the CPU core and the flash controller unit are driven off the external clock. However, an internal oscillator will provide timing references for Program and Erase operations. The internal oscillator is only turned on when required, and is turned off as soon as the flash operation is completed.

### Memory Bank Selection for In-Application Programming Mode

With the addressing range limited to 16 bit, only 64 KByte of program address space is "visible" at any one time. As shown in Table 13, the bank selection (the configuration of EA# and SFCF[1:0]), allows Block 1 memory to be overlaid on the lowest 8 KByte of Block 0 memory, making Block 1 reachable. The same concept is employed to allow both Block 0 and Block 1 flash to be accessible to IAP operations. Code from a block that is not visible may not be used as a source to program another address. However, a block that is not "visible" may be programmed by code from the other block through mailbox registers.

The device allows IAP code in one block of memory to program the other block of memory, but may not program any location in the same block. If an IAP operation originates physically from Block 0, the target of this operation is implicitly defined to be in Block 1. If the IAP operation originates physically from

Data Sheet

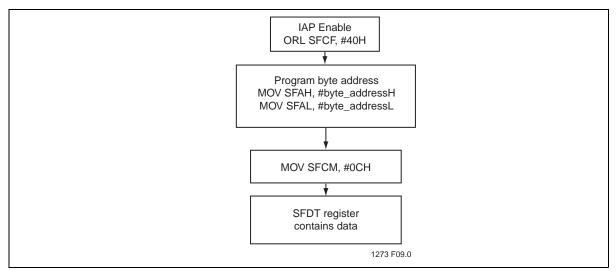

#### Byte-Verify

The Byte-Verify command allows the user to verify that the device has correctly performed an Erase or Program command. Byte-Verify command returns the data byte in SFDT if the command is successful. The user is required to check that the previous flash operation has fully completed before issuing a Byte-Verify. Byte-Verify command execution time is short enough that there is no need to poll for command completion and no interrupt is generated.

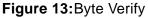

### Prog-SB3, Prog-SB2, Prog-SB1

Prog-SB3, Prog-SB2, Prog-SB1 commands are used to program the security bits (see Table 25). Completion of any of these commands, the security options will be updated immediately.

Security bits previously in un-programmed state can be programmed by these commands. Prog-SB3, Prog-SB2 and Prog-SB1 commands should only reside in Block 1 or external code memory.

### Figure 14: Prog-SB3, Prog-SB2, Prog-SB1

Data Sheet

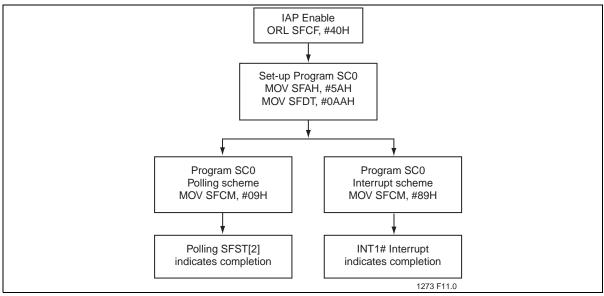

#### Prog-SC0

Prog-SC0 command is used to program the SC0 bit. This command only changes the SC0 bit and has no effect on BSEL bit until after a reset cycle.

SC0 bit previously in un-programmed state can be programmed by this command. The Prog-SC0 command should reside only in Block 1 or external code memory.

### Figure 15: Prog-SC0

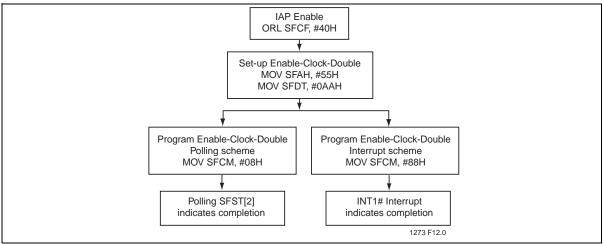

### Enable-Clock-Double

Enable-Clock-Double command is used to make the MCU run at 6 clocks per machine cycle. The standard (default) is 12 clocks per machine cycle (i.e. clock double command disabled).

### Figure 16: Enable-Clock-Double

There are no IAP counterparts for the external host commands Select-Block0 and Select-Block1.

Data Sheet

### Polling

A command that uses the polling method to detect flash operation completion should poll on the FLASH\_BUSY bit (SFST[2]). When FLASH\_BUSY de-asserts (logic 0), the device is ready for the next operation.

MOVC instruction may also be used for verification of the Programming and Erase operation of the flash memory. MOVC instruction will fail if it is directed at a flash block that is still busy.

### Interrupt Termination

If interrupt termination is selected, (SFCM[7] is set), then an interrupt (INT1) will be generated to indicate flash operation completion. Under this condition, the INT1 becomes an internal interrupt source. The INT1# pin can now be used as a general purpose port pin and it cannot be the source of External Interrupt 1 during in-application programming.

In order to use an interrupt to signal flash operation termination. EX1 and EA bits of IE register must be set. The IT1 bit of TCON register must also be set for edge trigger detection.

| SFAH [7:0]      | SFAL [7:0]      |

|-----------------|-----------------|

| X4              | Х               |

| AH              | Х               |

| AH <sup>6</sup> | AL <sup>7</sup> |

| AH              | AL              |

| AH              | AL              |

| Х               | Х               |

| Х               | Х               |

| Х               | Х               |

| 5AH             | Х               |

| 55H             | Х               |

|                 | _               |

#### Table 14: IAP Commands<sup>1</sup>

1. SFCF[6]=1 enables IAP commands; SFCF[6]=0 disables IAP commands.

2. Interrupt/Polling enable for flash operation completion

SFCM[7] =1: Interrupt enable for flash operation completion 0: polling enable for flash operation completion

3. Chip-Erase only functions in IAP mode when EA#=0 (external memory execution) and device is not in level 4 locking.

4. X can be  $V_{IL}$  or  $V_{IH}$ , but no other value.

5. Refer to Table 13 for address resolution

6. AH = Address high order byte

7. AL = Address low order byte

8. DI = Data Input, DO = Data Output, all other values are in hex.

9. Instruction must be located in Block 1 or external code memory.

Note: DISIAPL pin in PLCC or TQFP will also disable IAP commands if it is externally pulled low when reset.

#### Data Sheet

an interrupt will be generated if the ECF bit in the CMOD register is set. The CF bit can only be cleared by software. Each module has its own timer interrupt or capture interrupt flag (CCF0 for module 0, CCF4 for module 4, etc.). They are set when either a match or capture occurs. These flags can only be cleared by software. (See "PCA Timer/Counter Control Register (CCON)" on page 27.)

## **Compare/Capture Modules**

Each PCA module has an associated SFR with it. These registers are: CCAPM0 for module 0, CCAPM1 for module 1, etc. Refer to "PCA Compare/Capture Module Mode Register (CCAPMn)" on page 29 for details. The registers each contain 7 bits which are used to control the mode each module will operate in. The ECCF bit (CCAPMn.0 where n = 0, 1, 2, 3, or 4 depending on module) will enable the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs. PWM (CCAPMn.1) enables the pulse width modulation mode. The TOG bit (CCAPMn.2) when set, causes the CEX output associated with the module to toggle when there is a match between the PCA counter and the module's capture/compare register. When there is a match between the PCA counter and the module's capture/compare register, the MATn (CCAPMn.3) and the CCFn bit in the CCON register to be set.

Bits CAPN (CCAPMn.4) and CAPP (CCAPMn.5) determine whether the capture input will be active on a positive edge or negative edge. The CAPN bit enables the negative edge that a capture input will be active on, and the CAPP bit enables the positive edge. When both bits are set, both edges will be enabled and a capture will occur for either transition. The last bit in the register ECOM (CCAPMn.6) when set, enables the comparator function. Table 22 shows the CCAPMn settings for the various PCA functions.

There are two additional register associated with each of the PCA modules: CCAPnH and CCAPnL. They are registers that hold the 16-bit count value when a capture occurs or a compare occurs. When a module is used in PWM mode, these registers are used to control the duty cycle of the output. See Figure 24.

| Symbol | Description               | Direct<br>Address | Bit Address, Symbol, or Alternative Port Function MSB LSB | RESET<br>Value |

|--------|---------------------------|-------------------|-----------------------------------------------------------|----------------|

| CCAP0H | PCA Module 0              | FAH               | CCAP0H[7:0]                                               | 00H            |

| CCAP0L | Compare/Capture Registers | EAH               | CCAP0L[7:0]                                               | 00H            |

| CCAP1H | PCA Module 1              | FBH               | CCAP1H[7:0]                                               | 00H            |

| CCAP1L | Compare/Capture Registers | EBH               | CCAP1L[7:0]                                               | 00H            |

| CCAP2H | PCA Module 2              | FCH               | CCAP2H[7:0]                                               | 00H            |

| CCAP2L | Compare/Capture Registers | ECH               | CCAP2L[7:0]                                               | 00H            |

| CCAP3H | PCA Module 3              | FDH               | CCAP3H[7:0]                                               | 00H            |

| CCAP3L | Compare/Capture Registers | EDH               | CCAP3L[7:0]                                               | 00H            |

| CCAP4H | PCA Module 4              | FEH               | CCAP4H[7:0]                                               | 00H            |

| CCAP4L | Compare/Capture Registers | EEH               | CCAP4L[7:0]                                               | 00H            |

#### Table 21: PCA High and Low Register Compare/Capture Modules

T0-0.0 25093

Data Sheet

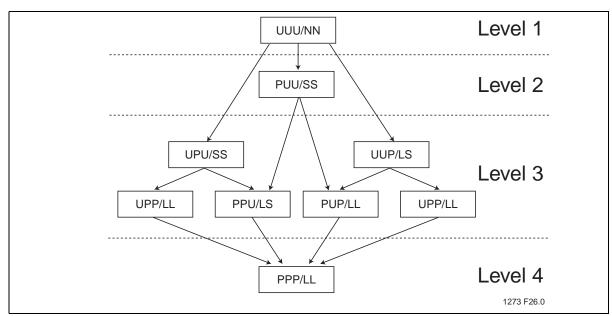

#### Figure 30: Security Lock Levels

Note: P = Programmed (Bit logic state = 0), U = Unprogrammed (Bit logic state = 1), N = Not Locked, L = Hard locked, S = Soft locked

|       | Sec        | Security Lock Bits <sup>1,2</sup> |                  | Security         | Status of: |           |                                                                                                                                                                                                                              |

|-------|------------|-----------------------------------|------------------|------------------|------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Level | SFST[7:5]  | SB1                               | SB2 <sup>1</sup> | SB3 <sup>1</sup> | Block 1    | Block 0   | Security Type                                                                                                                                                                                                                |

| 1     | 000        | U                                 | U                | U                | Unlock     | Unlock    | No Security Features are<br>Enabled.                                                                                                                                                                                         |

| 2     | 100        | Ρ                                 | U                | U                | SoftLock   | SoftLock  | MOVC instructions executed from<br>external program memory are<br>disabled from fetching code bytes<br>from internal memory, EA# is<br>sampled and latched on Reset,<br>and further programming of the<br>flash is disabled. |

| 3     | 011<br>101 | U<br>P                            | P<br>U           | P<br>P           | Hard Lock  | Hard Lock | Level 2 plus Verify disabled, both blocks locked.                                                                                                                                                                            |

|       | 010        | U                                 | P                | U                | SoftLock   | SoftLock  | Level 2 plus Verify disabled. Code<br>in Block 1 may program Block 0<br>and vice versa.                                                                                                                                      |

|       | 110<br>001 | P<br>U                            | P<br>U           | U<br>P           | Hard Lock  | SoftLock  | Level 2 plus Verify disabled. Code<br>in Block 1 may program Block 0.                                                                                                                                                        |

| 4     | 111        | Ρ                                 | Ρ                | Ρ                | Hard Lock  | Hard Lock | Same as Level 3 hard lock/hard<br>lock, but MCU will start code exe-<br>cution from the internal memory<br>regardless of EA#.                                                                                                |

#### Table 25: Security Lock Options

1. P = Programmed (Bit logic state = 0), U = Unprogrammed (Bit logic state = 1).

2. SFST[7:5] = Security Lock Status Bits (SB1\_i, SB2\_i, SB3\_i)

©2013 Silicon Storage Technology, Inc.

T0-0.0 25093

#### Data Sheet

#### Table 32: Reliability Characteristics

| Symbol                        | Parameter      | Minimum Specification | Units  | Test Method         |

|-------------------------------|----------------|-----------------------|--------|---------------------|

| N <sub>END</sub> <sup>1</sup> | Endurance      | 10,000                | Cycles | JEDEC Standard A117 |

| T <sub>DR</sub> <sup>1</sup>  | Data Retention | 100                   | Years  | JEDEC Standard A103 |

| I <sub>LTH</sub> <sup>1</sup> | Latch Up       | 100 + I <sub>DD</sub> | mA     | JEDEC Standard 78   |

T0-0.0 25093 1. This parameter is measured only for initial qualification and after a design or process change that could affect this

parameter.

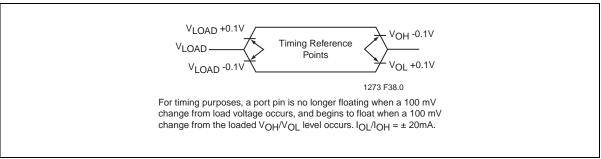

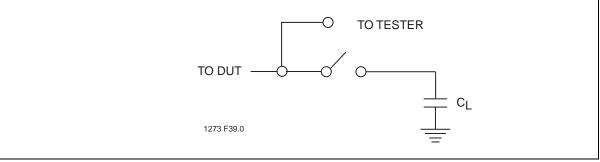

#### Table 33: AC Conditions of Test<sup>1</sup>

| Input Rise/Fall Time | Output Load             |

|----------------------|-------------------------|

| 10 ns                | C <sub>L</sub> = 100 pF |

1. See Figures 41 and 43

T33.1 25093

#### Table 34: Recommended System Power-up Timings

| Symbol                             | Parameter                   | Minimum | Units        |

|------------------------------------|-----------------------------|---------|--------------|

| T <sub>PU-READ</sub> <sup>1</sup>  | Power-up to Read Operation  | 100     | μs           |

| T <sub>PU-WRITE</sub> <sup>1</sup> | Power-up to Write Operation | 100     | μs           |

|                                    |                             |         | T0-0.0 25093 |

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter

#### Table 35: Pin Impedance (V<sub>DD</sub>=3.3V, T<sub>A</sub>=25°C, f=1 Mhz, other pins open)

| Parameter                     | Description         | Test Condition | Maximum      |

|-------------------------------|---------------------|----------------|--------------|

| C <sub>I/O</sub> <sup>1</sup> | I/O Pin Capacitance | $V_{I/O} = 0V$ | 15 pF        |

| C <sub>IN</sub> <sup>1</sup>  | Input Capacitance   | $V_{IN} = 0V$  | 12 pF        |

| L <sub>PIN</sub> <sup>2</sup> | Pin Inductance      |                | 20 nH        |

|                               | ·                   |                | T0-0.0 25093 |

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

2. Refer to PCI spec.

Data Sheet

### Figure 42: Float Waveform

### Figure 43: A Test Load Example

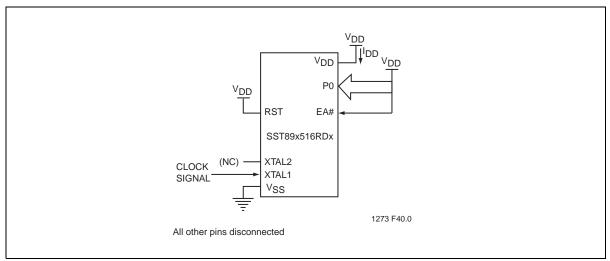

Figure 44:I<sub>DD</sub> Test Condition, Active Mode

Data Sheet

## Valid Combinations

### Valid combinations for SST89E516RD2

SST89E516RD2-40-C-NJE SST89E516RD2-40-C-TQJE

SST89E516RD2-40-I-NJE SST89E516RD2-40-I-TQJE

### Valid combinations for SST89V516RD2

SST89V516RD2-33-C-NJE SST89V516RD2-33-C-TQJE

SST89V516RD2-33-I-NJE SST89V516RD2-33-I-TQJE

### Valid combinations for SST89E516RD

SST89E516RD-40-C-PIE

SST89E516RD-40-C-QIF SST89E516RD-40-I-QIF

### Valid combinations for SST89V516RD

SST89V516RD-33-C-PIE

SST89V516RD-33-C-QIF SST89V516RD-33-I-QIF

**Note:** Valid combinations are those products in mass production or will be in mass production. Consult your SST sales representative to confirm availability of valid combinations and to determine availability of new combinations.

Data Sheet

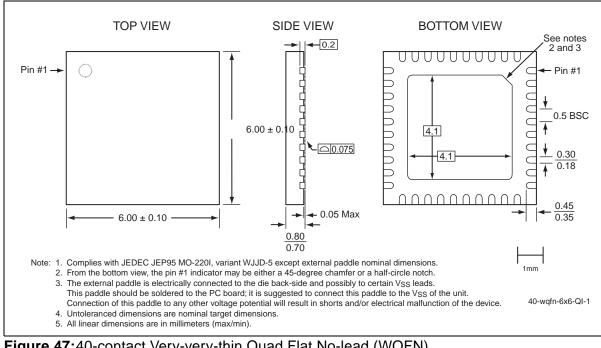

## **Packaging Diagrams**

Figure 47:40-contact Very-very-thin Quad Flat No-lead (WQFN) SST Package Code: QI

### Data Sheet

Figure 49:44-lead Plastic Lead Chip Carrier (PLCC) SST Package Code: NJ

Data Sheet

#### Table 42: Revision History

| Revision | Description                                                                                                                         | Date     |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|----------|

| 00       | <ul> <li>Initial Release of S71273 data sheet.<br/>SST89E/V516RD2 devices were previously released in S71255-00-<br/>000</li> </ul> | Mar 2005 |

|          | <ul> <li>S71273 and<br/>S71273(01): Added 40-WQFN (QI) package and associated MPNs</li> </ul>                                       |          |

|          | Added SST89E/V516RD PDIP devices and associated MPNs                                                                                |          |

|          | <ul> <li>Clarified the solder temperature profile under "Absolute Maximum<br/>Stress Ratings" on page 73</li> </ul>                 |          |

|          | <ul> <li>Added RoHS compliance information on page 1 and in the "Product<br/>Ordering Information" on page 88</li> </ul>            |          |

|          | <ul> <li>Removed references to External Host Mode programming</li> </ul>                                                            |          |

|          | • Corrected MPN breakdown definition for "2" to read "Port 4 present"                                                               |          |

|          | Corrected the SPI control Register definition for CPHA on page 30                                                                   |          |

| 01       | Status change from Preliminary Specifications to Data sheet                                                                         | Mar 2005 |

| 02       | Removed NJ, TQJ, and PI from Valid Combinations on page 78                                                                          | Oct 2006 |

|          | <ul> <li>Removed valid combination SST89E516RD-40-I-PIE and<br/>SST89V516RD-33-I-PIE on page 78</li> </ul>                          |          |

| 03       | Replaced FlashFlex51 with FlashFlex globally                                                                                        | Jan 2007 |

| А        | Applied new document format                                                                                                         | Nov 2011 |

|          | Released document under letter revision system                                                                                      |          |

|          | <ul> <li>Updated spec number from S71273 to DS25093</li> </ul>                                                                      |          |

| В        | • Removed "Not recommended for new designs" statement on page 1.                                                                    | Feb 2013 |

ISBN: 978-1-62076-989-8

© 2013 Silicon Storage Technology, Inc-a Microchip Technology Company. All rights reserved.

SST, Silicon Storage Technology, the SST logo, SuperFlash, MTP, and FlashFlex are registered trademarks of Silicon Storage Technology, Inc. MPF, SQI, Serial Quad I/O, and Z-Scale are trademarks of Silicon Storage Technology, Inc. All other trademarks and registered trademarks mentioned herein are the property of their respective owners.

Specifications are subject to change without notice. Refer to www.microchip.com for the most recent documentation. For the most current package drawings, please see the Packaging Specification located at http://www.microchip.com/packaging.

Memory sizes denote raw storage capacity; actual usable capacity may be less.

SST makes no warranty for the use of its products other than those expressly contained in the Standard Terms and Conditions of Sale.

For sales office locations and information, please see www.microchip.com.

#### Silicon Storage Technology, Inc. A Microchip Technology Company www.microchip.com