#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                               |

| Core Processor             | 8051                                                                                   |

| Core Size                  | 8-Bit                                                                                  |

| Speed                      | 40MHz                                                                                  |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                       |

| Number of I/O              | 36                                                                                     |

| Program Memory Size        | 72KB (72K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 1K x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                            |

| Data Converters            | -                                                                                      |

| Oscillator Type            | External                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 44-TQFP                                                                                |

| Supplier Device Package    | 44-TQFP (10x10)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89e516rd2-40-i-tqje-t-nxx |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Data Sheet

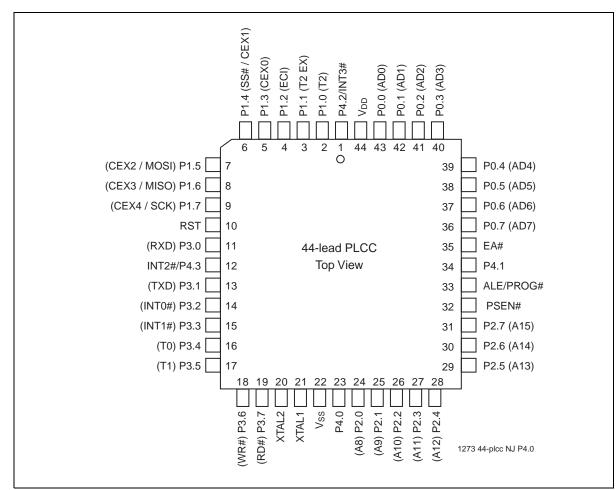

Figure 5: Pin Assignments for 44-lead PLCC

Data Sheet

## Program Memory Block Switching

The program memory block switching feature of the device allows either Block 1 or the lowest 8 KByte of Block 0 to be used for the lowest 8 KByte of the program address space. SFCF[1:0] controls program memory block switching.

## Table 2: SFCF Values for Program Memory Block Switching

| SFCF[1:0]  | Program Memory Block Switching                                                                                                                                                                                                                                                                                                                              |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01, 10, 11 | Block 1 is not visible to the program counter (PC).<br>Block 1 is reachable only via in-application programming from 0000H - 1FFFH.                                                                                                                                                                                                                         |

| 00         | Block 1 is overlaid onto the low 8K of the program address space; occupying address locations 0000H - 1FFFH.<br>When the PC falls within 0000H - 1FFFH, the instruction will be fetched from Block 1 instead of Block 0.<br>Outside of 0000H - 1FFFH, Block 0 is used. Locations 0000H - 1FFFH of Block 0 are reachable through in-application programming. |

T0-0.0 25093

## **Reset Configuration of Program Memory Block Switching**

Program memory block switching is initialized after reset according to the state of the Start-up Configuration bit SC0. The SC0 bit is programmed via an external host mode command or an IAP Mode command. See Table 14.

Once out of reset, the SFCF[0] bit can be changed dynamically by the program for desired effects. Changing SFCF[0] will not change the SC0 bit.

Caution must be taken when dynamically changing the SFCF[0] bit. Since this will cause different physical memory to be mapped to the logical program address space. The user must avoid executing block switching instructions within the address range 0000H to 1FFFH.

|                  | State of SFCF[1:0] after:           |                                       |                   |  |  |  |  |  |  |

|------------------|-------------------------------------|---------------------------------------|-------------------|--|--|--|--|--|--|

| SC0 <sup>1</sup> | Power-on<br>or<br>External<br>Reset | WDT Reset<br>or<br>Brown-out<br>Reset | Software<br>Reset |  |  |  |  |  |  |

| U (1)            | 00<br>(default)                     | x0                                    | 10                |  |  |  |  |  |  |

| P (0)            | 01                                  | x1                                    | 11                |  |  |  |  |  |  |

| ·                |                                     |                                       | T0-0.0 250        |  |  |  |  |  |  |

**Table 3:** SFCF Values Under Different Reset Conditions

1. P = Programmed (Bit logic state = 0),

U = Unprogrammed (Bit logic state = 1)

## Data RAM Memory

The data RAM has 1024 bytes of internal memory. The RAM can be addressed up to 64KB for external data memory.

Data Sheet

high-order eight address bits (DPH), and Port 0 multiplexes the low order eight address bits (DPL) with data. Both MOVX @Ri and MOVX @DPTR generates the necessary read and write signals (P3.6 - WR# and P3.7 - RD#) for external memory use. Table 4 shows external data memory RD#, WR# operation with EXTRAM bit.

The stack pointer (SP) can be located anywhere within the 256 bytes of internal RAM (lower 128 bytes and upper 128 bytes). The stack pointer may not be located in any part of the expanded RAM.

|            | MOVX @DPTR, A or       | MOVX @Ri, A or MOVX A, @Ri |                                     |  |  |

|------------|------------------------|----------------------------|-------------------------------------|--|--|

| AUXR       | ADDR < 0300H           | ADDR >= 0300H              | ADDR = Any                          |  |  |

| EXTRAM = 0 | RD# / WR# not asserted | RD# / WR# asserted         | RD# / WR# not asserted <sup>1</sup> |  |  |

| EXTRAM = 1 | RD# / WR# asserted     | RD# / WR# asserted         | RD# / WR# asserted                  |  |  |

### Table 4: External Data Memory RD#, WR# with EXTRAM bit

1. Access limited to ERAM address within 0 to 0FFH; cannot access 100H to 02FFH.

Data Sheet

|        |                            | Direct  |           | Bit Address, Symbol, or Alternative Port Function                  |           |       |                    |                 |                    |                | Reset         |

|--------|----------------------------|---------|-----------|--------------------------------------------------------------------|-----------|-------|--------------------|-----------------|--------------------|----------------|---------------|

| Symbol | Description                | Address | MSB       |                                                                    |           |       |                    |                 |                    | LSB            | Value         |

| SFCF   | SuperFlash                 | B1H     | -         | IAPE                                                               | -         | -     | -                  | -               | SW                 | BSE            | x0xxxx00      |

|        | Configuration              |         |           | Ν                                                                  |           |       |                    |                 | R                  | L              | b             |

| SFCM   | SuperFlash<br>Command      | B2H     | FIE       | FIE FCM[6:0]                                                       |           |       |                    |                 |                    |                | 00H           |

| SFAL   | SuperFlash<br>Address Low  | B3H     | Super     | SuperFlash Low Order Byte Address Register - $A_7$ to $A_0$ (SFAL) |           |       |                    |                 |                    |                | 00H           |

| SFAH   | SuperFlash<br>Address High | B4H     | Su        | perFlasł                                                           | n High (  | Order | Byte Add<br>(SFAH) | ress Register - | A <sub>15</sub> to | A <sub>8</sub> | 00H           |

| SFDT   | SuperFlash<br>Data         | B5H     |           | SuperFlash Data Register                                           |           |       |                    |                 |                    | 00H            |               |

| SFST   | SuperFlash<br>Status       | B6H     | SB1<br>_i | SB2_<br>i                                                          | SB3<br>_i | -     | EDC_i              | FLASH_BU<br>SY  | -                  | -              | 000x00xx<br>b |

## Table 7: Flash Memory Programming SFRs

T0-0.0 25093

## Table 8: Watchdog Timer SFRs

|           |                                  | Direct  | Bit Ade                    | Bit Address, Symbol, or Alternative Port Function |   |       |      |      |     |      | Reset         |

|-----------|----------------------------------|---------|----------------------------|---------------------------------------------------|---|-------|------|------|-----|------|---------------|

| Symbol    | Description                      | Address | MSB                        |                                                   |   |       |      |      |     | LSB  | Value         |

| WDTC<br>1 | Watchdog<br>Timer<br>Control     | С0Н     | -                          | -                                                 | - | WDOUT | WDRE | WDTS | WDT | SWDT | xxx00x00<br>b |

| WDTD      | Watchdog<br>Timer<br>Data/Reload | 85H     | Watchdog Timer Data/Reload |                                                   |   |       |      |      | 00H |      |               |

1. Bit Addressable SFRs

Data Sheet

## Table 10: Interface SFRs

|                 |                          | Direct  | Bit Addr   | ess, Syn   | nbol, or A | Iternativ | /e Port F | unction   | 1        |          | RESET              |

|-----------------|--------------------------|---------|------------|------------|------------|-----------|-----------|-----------|----------|----------|--------------------|

| Symbol          | Description              | Address | MSB        |            |            |           |           |           |          | LSB      | Value              |

| SBUF            | Serial Data Buf-<br>fer  | 99H     |            | SBUF[7:0]  |            |           |           |           |          |          | Indetermi-<br>nate |

| SCON<br>1       | Serial Port Con-<br>trol | 98H     | SM0/<br>FE | SM1        | SM2        | REN       | TB8       | RB8       | ΤI       | RI       | 00H                |

| SADD<br>R       | Slave Address            | A9H     |            | SADDR[7:0] |            |           |           |           |          |          |                    |

| SADE<br>N       | Slave Address<br>Mask    | B9H     |            | SADEN[7:0] |            |           |           |           |          |          | 00H                |

| SPCR            | SPI Control<br>Register  | D5H     | SPIE       | SPE        | DOR<br>D   | MST<br>R  | CPO<br>L  | CPH<br>A  | SPR<br>1 | SPR<br>0 | 04H                |

| SPSR            | SPI Status<br>Register   | AAH     | SPIF       | WCO<br>L   |            |           |           |           |          |          | 00H                |

| SPDR            | SPI Data Regis-<br>ter   | 86H     |            |            |            | SPDR[     | 7:0]      |           |          |          | 00H                |

| P0 <sup>1</sup> | Port 0                   | 80H     |            |            |            | P0[7:     | 0]        |           |          |          | FFH                |

| P1 <sup>1</sup> | Port 1                   | 90H     | -          | -          | -          | -         | -         | -         | T2E<br>X | T2       | FFH                |

| P2 <sup>1</sup> | Port 2                   | A0H     |            |            | •          | P2[7:     | 0]        |           | •        | •        | FFH                |

| P3 <sup>1</sup> | Port 3                   | B0H     | RD#        | WR#        | T1         | Т0        | INT1<br># | INT0<br># | TXD      | RXD      | FFH                |

| P4 <sup>2</sup> | Port 4                   | A5H     | 1          | 1          | 1          | 1         | P4.3      | P4.2      | P4.1     | P4.0     | FFH                |

|                 |                          | •       |            | •          |            |           |           | •         |          |          | T0-0.0 25093       |

1. Bit Addressable SFRs

2. P4 is similar to P1 and P3 ports

### Data Sheet

| SPI Control Register (S | PCR)                                                                                                    |                                                                                                                                                                                                                                                                                                       |                          |             |                          |             |           |            |              |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|--------------------------|-------------|-----------|------------|--------------|--|--|

| Location                | 7                                                                                                       | 6                                                                                                                                                                                                                                                                                                     | 5                        | 4           | 3                        | 2           | 1         | 0          | Reset Value  |  |  |

| D5H                     | SPIE                                                                                                    | SPE                                                                                                                                                                                                                                                                                                   | DORD                     | MSTR        | CPOL                     | CPHA        | SPR1      | SPR0       | 00H          |  |  |

| Symbol                  | Function                                                                                                |                                                                                                                                                                                                                                                                                                       |                          |             |                          |             |           |            |              |  |  |

| SPIE                    | If both SP                                                                                              | f both SPIE and ES are set to one, SPI interrupts are enabled.<br>SPI enable bit.<br>D: Disables SPI.<br>I: Enables SPI and connects SS#, MOSI, MISO, and SCK to pins P1.4, P1.5, P1.6, P1.7.<br>Data Transmission Order.<br>D: MSB first in data transmission.<br>I: LSB first in data transmission. |                          |             |                          |             |           |            |              |  |  |

| SPE                     | 0: Disables                                                                                             |                                                                                                                                                                                                                                                                                                       |                          |             |                          |             |           |            |              |  |  |

| DORD                    | 0: MSB fir                                                                                              |                                                                                                                                                                                                                                                                                                       |                          |             |                          |             |           |            |              |  |  |

| MSTR                    | Master/Sla<br>0: Selects<br>1: Selects                                                                  |                                                                                                                                                                                                                                                                                                       |                          |             |                          |             |           |            |              |  |  |

| CPOL                    | CPOL Clock Polarity<br>0: SCK is low when idle (Active High).<br>1: SCK is high when idle (Active Low). |                                                                                                                                                                                                                                                                                                       |                          |             |                          |             |           |            |              |  |  |

| CPHA                    | Clock Pha<br>relationshi<br>0: Shift trig<br>1: Shift trig                                              | p betweer<br>ggered on                                                                                                                                                                                                                                                                                | n master a<br>the leadin | nd slave. S | See Figure<br>the clock. | es 21 and   |           | ock and c  | lata         |  |  |

| SPR1. S                 | PR0SPI Clo                                                                                              | ock Rate S                                                                                                                                                                                                                                                                                            | Select bits.             | These tw    | o bits cont              | trol the SC | K rate of | the device | e configured |  |  |

SPR1, SPR0SPI Clock Rate Select bits. These two bits control the SCK rate of the device configured as master. SPR1 and SPR0 have no effect on the slave. The relationship between SCK and the oscillator frequency, f<sub>OSC</sub>, is as follows:

| SPR1 | SPR0 | SCK = f <sub>OSC</sub> divided by |

|------|------|-----------------------------------|

| 0    | 0    | 4                                 |

| 0    | 1    | 16                                |

| 1    | 0    | 64                                |

| 1    | 1    | 128                               |

### SPI Status Register (SPSR)

| Location | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 | Reset Value |

|----------|------|------|---|---|---|---|---|---|-------------|

| AAH      | SPIF | WCOL | - | - | - | - | - | - | 00xxxxxxb   |

### Symbol Function

| SPIF | SPI Interrupt Flag.<br>Upon completion of data transfer, this bit is set to 1.<br>If SPIE =1 and ES =1, an interrupt is then generated.<br>This bit is cleared by software. |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WCOL | Write Collision Flag.<br>Set if the SPI data register is written to during data transfer.<br>This bit is cleared by software.                                               |

### Data Sheet

| External Interrupt Control (XICON) |                             |                                                                                                               |              |             |             |            |               |           |             |  |  |  |

|------------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------|--------------|-------------|-------------|------------|---------------|-----------|-------------|--|--|--|

| Location                           | 7                           | 6                                                                                                             | 5            | 4           | 3           | 2          | 1             | 0         | Reset Value |  |  |  |

| AEH                                | -                           | EX3                                                                                                           | IE3          | IT3         | 0           | EX2        | IE2           | IT2       | 00H         |  |  |  |

| Symbol                             | Function                    | nction                                                                                                        |              |             |             |            |               |           |             |  |  |  |

| EX2                                |                             | ternal Interrupt 2<br>able bit if set                                                                         |              |             |             |            |               |           |             |  |  |  |

| IE2                                |                             | nterrupt Enable<br>f IT2=1, IE2 is set/cleared automatically by hardware when interrupt is detected/serviced. |              |             |             |            |               |           |             |  |  |  |

| IT2                                | External Ir                 | nterrupt 2 i                                                                                                  | is falling-e | dge/low-le  | vel trigger | ed when t  | his bit is c  | leared by | software.   |  |  |  |

| EX3                                |                             | External Interrupt 3<br>Enable bit if set                                                                     |              |             |             |            |               |           |             |  |  |  |

| IE3                                | Interrupt E<br>If IT3=1, IE |                                                                                                               | leared aut   | omatically  | by hardw    | are when i | interrupt is  | detectec  | l/serviced. |  |  |  |

| IT3                                | External Ir                 | nterrupt3 is                                                                                                  | s falling-eo | dge/low-lev | el trigger  | ed when th | nis bit is cl | eared by  | software.   |  |  |  |

#### ©2013 Silicon Storage Technology, Inc.

Data Sheet

## Flash Memory Programming

The device internal flash memory can be programmed or erased using In-Application Programming (IAP) mode

## **Product Identification**

The Read-ID command accesses the Signature Bytes that identify the device and the manufacturer as SST. External programmers primarily use these Signature Bytes in the selection of programming algorithms.

### Table 12: Product Identification

|                   | Address | Data |

|-------------------|---------|------|

| Manufacturer's ID | 30H     | BFH  |

| Device ID         |         |      |

| SST89E516RD2/RD   | 31H     | 93H  |

| SST89V516RD2/RD   | 31H     | 92H  |

T0-0.0 25093

## In-Application Programming Mode

The device offers either 72 KByte of in-application programmable flash memory. During in-application programming, the CPU of the microcontroller enters IAP mode. The two blocks of flash memory allow the CPU to execute user code from one block, while the other is being erased or reprogrammed concurrently. The CPU may also fetch code from an external memory while all internal flash is being reprogrammed. The mailbox registers (SFST, SFCM, SFAL, SFAH, SFDT and SFCF) located in the special function register (SFR), control and monitor the device's erase and program process.

Table 14 outline the commands and their associated mailbox register settings.

## In-Application Programming Mode Clock Source

During IAP mode, both the CPU core and the flash controller unit are driven off the external clock. However, an internal oscillator will provide timing references for Program and Erase operations. The internal oscillator is only turned on when required, and is turned off as soon as the flash operation is completed.

## Memory Bank Selection for In-Application Programming Mode

With the addressing range limited to 16 bit, only 64 KByte of program address space is "visible" at any one time. As shown in Table 13, the bank selection (the configuration of EA# and SFCF[1:0]), allows Block 1 memory to be overlaid on the lowest 8 KByte of Block 0 memory, making Block 1 reachable. The same concept is employed to allow both Block 0 and Block 1 flash to be accessible to IAP operations. Code from a block that is not visible may not be used as a source to program another address. However, a block that is not "visible" may be programmed by code from the other block through mailbox registers.

The device allows IAP code in one block of memory to program the other block of memory, but may not program any location in the same block. If an IAP operation originates physically from Block 0, the target of this operation is implicitly defined to be in Block 1. If the IAP operation originates physically from

### Data Sheet

Block 1, then the target address is implicitly defined to be in Block 0. If the IAP operation originates from external program space, then, the target will depend on the address and the state of bank selection.

### IAP Enable Bit

The IAP enable bit, SFCF[6], enables in-application programming mode. Until this bit is set, all flash programming IAP commands will be ignored.

| EA# | SFCF[1:0]  | Address of IAP Inst. | Target Address     | Block Being<br>Programmed |

|-----|------------|----------------------|--------------------|---------------------------|

| 1   | 00         | >= 2000H (Block 0)   | >= 2000H (Block 0) | None <sup>1</sup>         |

| 1   | 00         | >= 2000H (Block 0)   | < 2000H (Block 1)  | Block 1                   |

| 1   | 00         | < 2000H (Block 1)    | Any (Block 0)      | Block 0                   |

| 1   | 01, 10, 11 | Any (Block 0)        | >= 2000H (Block 0) | None <sup>1</sup>         |

| 1   | 01, 10, 11 | Any (Block 0)        | < 2000H (Block 1)  | Block 1                   |

| 0   | 00         | From external        | >= 2000H (Block 0) | Block 0                   |

| 0   | 00         | From external        | < 2000H (Block 1)  | Block 1                   |

| 0   | 01, 10, 11 | From external        | Any (Block 0)      | Block 0                   |

### Table 13: IAP Address Resolution

1. No operation is performed because code from one block may not program the same originating block

T0-0.0 25093

## In-Application Programming Mode Commands

All of the following commands can only be initiated in the IAP mode. In all situations, writing the control byte to the SFCM register will initiate all of the operations. All commands will not be enabled if the security locks are enabled on the selected memory block.

The Program command is for programming new data into the memory array. The portion of the memory array to be programmed should be in the erased state, FFH. If the memory is not erased, it should first be erased with an appropriate Erase command. Warning: Do not attempt to write (program or erase) to a block that the code is currently fetching from. This will cause unpredictable program behavior and may corrupt program data.

Data Sheet

## **Timers/Counters**

## Timers

The device has three 16-bit registers that can be used as either timers or event counters. The three timers/counters are denoted Timer 0 (T0), Timer 1 (T1), and Timer 2 (T2). Each is designated a pair of 8-bit registers in the SFRs. The pair consists of a most significant (high) byte and least significant (low) byte. The respective registers are TL0, TH0, TL1, TH1, TL2, and TH2.

## **Timer Set-up**

Refer to Table 9 for TMOD, TCON, and T2CON registers regarding timers T0, T1, and T2. The following tables provide TMOD values to be used to set up Timers T0, T1, and T2.

Except for the baud rate generator mode, the values given for T2CON do not include the setting of the TR2 bit. Therefore, bit TR2 must be set separately to turn the timer on.

|               |      |                   | TN                            | IOD                           |

|---------------|------|-------------------|-------------------------------|-------------------------------|

|               | Mode | Function          | Internal Control <sup>1</sup> | External Control <sup>2</sup> |

|               | 0    | 13-bit Timer      | 00H                           | 08H                           |

|               | 1    | 16-bit Timer      | 01H                           | 09H                           |

| Used as Timer | 2    | 8-bit Auto-Reload | 02H                           | 0AH                           |

|               | 3    | Two 8-bit Timers  | 03H                           | 0BH                           |

|               | 0    | 13-bit Timer      | 04H                           | 0CH                           |

| Used as       | 1    | 16-bit Timer      | 05H                           | 0DH                           |

| Counter       | 2    | 8-bit Auto-Reload | 06H                           | 0EH                           |

|               | 3    | Two 8-bit Timers  | 07H                           | 0FH                           |

|               |      |                   | •                             | T0-0.0 25093                  |

### Table 15: Timer/Counter 0

1. The Timer is turned ON/OFF by setting/clearing bit TR0 in the software.

2. The Timer is turned ON/OFF by the 1 to 0 transition on INT0# (P3.2) when TR0 = 1 (hardware control).

### Table 16: Timer/Counter 1

|               |      |                   | TN                            | NOD                           |

|---------------|------|-------------------|-------------------------------|-------------------------------|

|               | Mode | Function          | Internal Control <sup>1</sup> | External Control <sup>2</sup> |

|               | 0    | 13-bit Timer      | 00H                           | 80H                           |

|               | 1    | 16-bit Timer      | 10H                           | 90H                           |

| Used as Timer | 2    | 8-bit Auto-Reload | 20H                           | A0H                           |

|               | 3    | Does not run      | 30H                           | B0H                           |

|               | 0    | 13-bit Timer      | 40H                           | СОН                           |

| Used as       | 1    | 16-bit Timer      | 50H                           | D0H                           |

| Counter       | 2    | 8-bit Auto-Reload | 60H                           | E0H                           |

|               | 3    | Not available     | -                             | -                             |

1. The Timer is turned ON/OFF by setting/clearing bit TR1 in the software.

2. The Timer is turned ON/OFF by the 1 to 0 transition on INT1# (P3.3) when TR1 = 1 (hardware control).

Data Sheet

## **Programmable Counter Array**

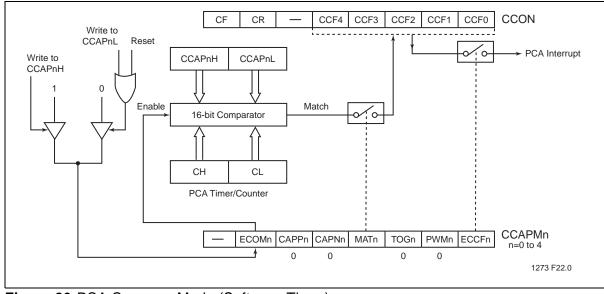

The Programmable Counter Array (PCA) present on the SST89E/V516RDx is a special 16-bit timer that has five 16-bit capture/compare modules. Each of the modules can be programmed to operate in one of four modes: rising and/or falling edge capture, software timer, high-speed output, or pulse width modulator. The 5th module can be programmed as a Watchdog Timer in addition to the other four modes. Each module has a pin associated with it in port 1. Module 0 is connected to P1.3 (CEX0), module 1 to P1[4] (CEX1), module 2 to P1[5] (CEX2), module 3 to P1[6] (CEX3), and module 4 to P1[7] (CEX4). PCA configuration is shown in Figure 24.

## **PCA** Overview

PCA provides more timing capabilities with less CPU intervention than the standard timer/counter. Its advantages include reduced software overhead and improved accuracy.

The PCA consists of a dedicated timer/counter which serves as the time base for an array of five compare/capture modules. Figure 24 shows a block diagram of the PCA. External events associated with modules are shared with corresponding Port 1 pins. Modules not using the port pins can still be used for standard I/O.

Each of the five modules can be programmed in any of the following modes:

- Rising and/or falling edge capture

- Software timer

- High speed output

- Watchdog Timer (Module 4 only)

- Pulse Width Modulator (PWM)

## PCA Timer/Counter

The PCA timer is a free-running 16-bit timer consisting of registers CH and CL (the high and low bytes of the count values). The PCA timer is common time base for all five modules and can be programmed to run at: 1/6 the oscillator frequency, 1/2 the oscillator frequency, Timer 0 overflow, or the input on the ECI pin (P1.2). The timer/counter source is determined from the CPS1 and CPS0 bits in the CMOD SFR as follows (see "PCA Timer/Counter Mode Register (CMOD)" on page 28):

| CPS1 | CPS0 | 12 Clock Mode                                                     | 6 Clock Mode                                                      |

|------|------|-------------------------------------------------------------------|-------------------------------------------------------------------|

| 0    | 0    | f <sub>OSC</sub> /12                                              | f <sub>OSC</sub> /6                                               |

| 0    | 1    | f <sub>OSC</sub> /4                                               | f <sub>OSC</sub> /2                                               |

| 1    | 0    | Timer 0 overflow                                                  | Timer 0 overflow                                                  |

| 1    | 1    | External clock at ECI pin<br>(maximum rate = f <sub>OSC</sub> /8) | External clock at ECI pin<br>(maximum rate = f <sub>OSC</sub> /4) |

## Table 18: PCA Timer/Counter Source

Data Sheet

### Table 22: PCA Module Modes

| W  | Without Interrupt enabled |                    |                    |                   |                        |                   |                    |                                                              |  |  |

|----|---------------------------|--------------------|--------------------|-------------------|------------------------|-------------------|--------------------|--------------------------------------------------------------|--|--|

| _1 | ECOMy <sup>2</sup>        | CAPPy <sup>2</sup> | CAPNy <sup>2</sup> | MATy <sup>2</sup> | TOGy <sup>2</sup>      | PWMy <sup>2</sup> | ECCFy <sup>2</sup> | Module Code                                                  |  |  |

| -  | 0                         | 0                  | 0                  | 0                 | 0                      | 0                 | 0                  | No Operation                                                 |  |  |

| -  | 0                         | 1                  | 0                  | 0                 | 0                      | 0                 | 0                  | 16-bit capture on positive-edge trigger at CEX[4:0]          |  |  |

| -  | 0                         | 0                  | 1                  | 0                 | 0                      | 0                 | 0                  | 16-bit capture on negative-edge trigger at CEX[4:0]          |  |  |

| -  | 0                         | 1                  | 1                  | 0                 | 0                      | 0                 | 0                  | 16-bit capture on positive/negative-edge trigger at CEX[4:0] |  |  |

| -  | 1                         | 0                  | 0                  | 1                 | 0                      | 0                 | 0                  | Compare: software timer                                      |  |  |

| -  | 1                         | 0                  | 0                  | 1                 | 1                      | 0                 | 0                  | Compare: high-speed output                                   |  |  |

| -  | 1                         | 0                  | 0                  | 0                 | 0                      | 1                 | 0                  | Compare: 8-bit PWM                                           |  |  |

| -  | 1                         | 0                  | 0                  | 1                 | 0 or<br>1 <sup>3</sup> | 0                 | 0                  | Compare: PCA WDT (CCAPM4 only) <sup>4</sup>                  |  |  |

T0-0.0 25093

1. User should not write '1's to reserved bits. The value read from a reserved bit is indeterminate.

2. y = 0, 1, 2, 3, 4

3. A 0 disables toggle function. A 1 enables toggle function on CEX[4:0] pin.

4. For PCA WDT mode, also set the WDTE bit in the CMOD register to enable the reset output signal.

| Wi | With Interrupt enabled |                    |                    |                   |                     |                   |                    |                                                                     |  |  |

|----|------------------------|--------------------|--------------------|-------------------|---------------------|-------------------|--------------------|---------------------------------------------------------------------|--|--|

| _1 | ECOMy <sup>2</sup>     | CAPPy <sup>2</sup> | CAPNy <sup>2</sup> | MATy <sup>2</sup> | TOGy <sup>2</sup>   | PWMy <sup>2</sup> | ECCFy <sup>2</sup> | Module Code                                                         |  |  |

| -  | 0                      | 1                  | 0                  | 0                 | 0                   | 0                 | 1                  | 16-bit capture on positive-edge trig-<br>ger at CEX[4:0]            |  |  |

| -  | 0                      | 0                  | 1                  | 0                 | 0                   | 0                 | 1                  | 16-bit capture on negative-edge trig-<br>ger at CEX[4:0]            |  |  |

| -  | 0                      | 1                  | 1                  | 0                 | 0                   | 0                 | 1                  | 16-bit capture on positive/negative-<br>edge<br>trigger at CEX[4:0] |  |  |

| -  | 1                      | 0                  | 0                  | 1                 | 0                   | 0                 | 1                  | Compare: software timer                                             |  |  |

| -  | 1                      | 0                  | 0                  | 1                 | 1                   | 0                 | 1                  | Compare: high-speed output                                          |  |  |

| -  | 1                      | 0                  | 0                  | 0                 | 0                   | 1                 | X <sup>3</sup>     | Compare: 8-bit PWM                                                  |  |  |

| -  | 1                      | 0                  | 0                  | 1                 | 0 or 1 <sup>4</sup> | 0                 | X <sup>5</sup>     | Compare: PCA WDT (CCAPM4 only) <sup>6</sup>                         |  |  |

### Table 23: PCA Module Modes

T0-0.0 25093

1. User should not write '1's to reserved bits. The value read from a reserved bit is indeterminate.

2. y = 0, 1, 2, 3, 4

3. No PCA interrupt is needed to generate the PWM.

4. A 0 disables toggle function. A 1 enables toggle function on CEX[4:0] pin.

5. Enabling an interrupt for the Watchdog Timer would defeat the purpose of the Watchdog Timer.

6. For PCA WDT mode, also set the WDTE bit in the CMOD register to enable the reset output signal.

Data Sheet

## 16-Bit Software Timer Mode

The 16-bit software timer mode is used to trigger interrupt routines, which must occur at periodic intervals. It is setup by setting both the ECOM and MAT bits in the module's CCAPMn register. The PCA timer will be compared to the module's capture registers (CCAPnL and CCAPnH) and when a match occurs, an interrupt will occur, if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set.

If necessary, a new 16-bit compare value can be loaded into CCAPnH and CCAPnL during the interrupt routine. The user should be aware that the hardware temporarily disables the comparator function while these registers are being updated so that an invalid match will not occur. Thus, it is recommended that the user write to the low byte first (CCAPnL) to disable the comparator, then write to the high byte (CCAPnH) to re-enable it. If any updates to the registers are done, the user may want to hold off any interrupts from occurring by clearing the EA bit. (See Figure 26)

Figure 26: PCA Compare Mode (Software Timer)

## **High Speed Output Mode**

The high speed output mode is used to toggle a port pin when a match occurs between the PCA timer and the preloaded value in the compare registers. In this mode, the CEX output pin (on port 1) associated with the PCA module will toggle every time there is a match between the PCA counter (CH and CL) and the capture registers (CCAPnH and CCAPnL). To activate this mode, the user must set TOG, MAT, and ECOM bits in the module's CCAPMn SFR.

High speed output mode is much more accurate than toggling pins since the toggle occurs before branching to an interrupt. In this case, interrupt latency will not affect the accuracy of the output. When using high speed output, using an interrupt is optional. Only if the user wishes to change the time for the next toggle is it necessary to update the compare registers. Otherwise, the next toggle will occur when the PCA timer rolls over and matches the last compare value. (See Figure 27)

Data Sheet

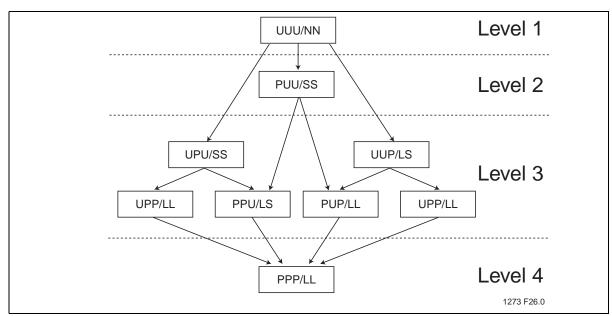

### Figure 30: Security Lock Levels

Note: P = Programmed (Bit logic state = 0), U = Unprogrammed (Bit logic state = 1), N = Not Locked, L = Hard locked, S = Soft locked

|       | Security Lock Bits <sup>1,2</sup> |        |                  |                  | Security  | Status of: |                                                                                                                                                                                                                            |  |

|-------|-----------------------------------|--------|------------------|------------------|-----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Level | SFST[7:5]                         | SB1    | SB2 <sup>1</sup> | SB3 <sup>1</sup> | Block 1   | Block 0    | Security Type                                                                                                                                                                                                              |  |

| 1     | 000                               | U      | U                | U                | Unlock    | Unlock     | No Security Features are<br>Enabled.                                                                                                                                                                                       |  |

| 2     | 100                               | Ρ      | U                | U                | SoftLock  | SoftLock   | MOVC instructions executed fro<br>external program memory are<br>disabled from fetching code byte<br>from internal memory, EA# is<br>sampled and latched on Reset,<br>and further programming of the<br>flash is disabled. |  |

| 3     | 011<br>101                        | U<br>P | P<br>U           | P<br>P           | Hard Lock | Hard Lock  | Level 2 plus Verify disabled, both blocks locked.                                                                                                                                                                          |  |

|       | 010                               | U      | P                | U                | SoftLock  | SoftLock   | Level 2 plus Verify disabled. Code<br>in Block 1 may program Block 0<br>and vice versa.                                                                                                                                    |  |

|       | 110<br>001                        | P<br>U | P<br>U           | U<br>P           | Hard Lock | SoftLock   | Level 2 plus Verify disabled. Code<br>in Block 1 may program Block 0.                                                                                                                                                      |  |

| 4     | 111                               | Ρ      | Р                | Ρ                | Hard Lock | Hard Lock  | Same as Level 3 hard lock/hard<br>lock, but MCU will start code exe-<br>cution from the internal memory<br>regardless of EA#.                                                                                              |  |

### Table 25: Security Lock Options

1. P = Programmed (Bit logic state = 0), U = Unprogrammed (Bit logic state = 1).

2. SFST[7:5] = Security Lock Status Bits (SB1\_i, SB2\_i, SB3\_i)

©2013 Silicon Storage Technology, Inc.

Data Sheet

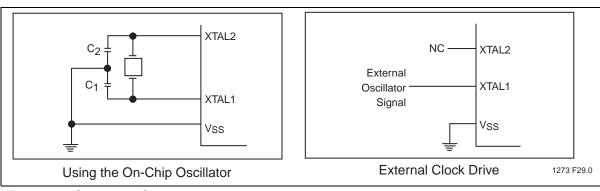

## Figure 33:Oscillator Characteristics

## Table 30: Clock Doubling Features

| Device       | Sta                            | ndard Mode (x1)                           | Clock Double Mode (x2)         |                                           |  |

|--------------|--------------------------------|-------------------------------------------|--------------------------------|-------------------------------------------|--|

|              | Clocks per<br>Machine<br>Cycle | Max. External Clock<br>Frequency<br>(MHz) | Clocks per<br>Machine<br>Cycle | Max. External Clock<br>Frequency<br>(MHz) |  |

| SST89E516RDx | 12                             | 40                                        | 6                              | 20                                        |  |

| SST89V516RDx | 12                             | 33                                        | 6                              | 16                                        |  |

Data Sheet

## **DC Electrical Characteristics**

| Symbol           | Parameter                                                      | Test Conditions                        | Min                         | Max                         | Units |

|------------------|----------------------------------------------------------------|----------------------------------------|-----------------------------|-----------------------------|-------|

| VIL              | Input Low Voltage                                              | 4.5 < V <sub>DD</sub> < 5.5            | -0.5                        | 0.2V <sub>DD</sub> -<br>0.1 | V     |

| V <sub>IH</sub>  | Input High Voltage                                             | 4.5 < V <sub>DD</sub> < 5.5            | 0.2V <sub>DD</sub> +<br>0.9 | V <sub>DD</sub> + 0.5       | V     |

| V <sub>IH1</sub> | Input High Voltage (XTAL1, RST)                                | $4.5 < V_{DD} < 5.5$                   | $0.7V_{DD}$                 | V <sub>DD</sub> + 0.5       | V     |

| V <sub>OL</sub>  | Output Low Voltage (Ports 1.5, 1.6, 1.7)                       | $V_{DD} = 4.5V$                        |                             |                             |       |

|                  |                                                                | $I_{OL} = 16 \text{mA}$                |                             | 1.0                         | V     |

| V <sub>OL</sub>  | Output Low Voltage (Ports 1, 2, 3) <sup>1</sup>                | $V_{DD} = 4.5V$                        |                             |                             |       |

|                  |                                                                | $I_{OL} = 100 \mu A^2$                 |                             | 0.3                         | V     |

|                  |                                                                | $I_{OL} = 1.6 m A^2$                   |                             | 0.45                        | V     |

|                  |                                                                | $I_{OL} = 3.5 \text{mA}^2$             |                             | 1.0                         | V     |

| V <sub>OL1</sub> | Output Low Voltage (Port 0, ALE,                               | $V_{DD} = 4.5V$                        |                             |                             |       |

|                  | PSEN#) <sup>1,3</sup>                                          | $I_{OL} = 200 \mu A^2$                 |                             | 0.3                         | V     |

|                  |                                                                | $I_{OL} = 3.2 \text{mA}^2$             |                             | 0.45                        | V     |

| V <sub>OH</sub>  | Output High Voltage (Ports 1, 2, 3, ALE,                       | $V_{DD} = 4.5V$                        |                             |                             |       |

|                  | PSEN#) <sup>4</sup>                                            | I <sub>OH</sub> = -10μA                | V <sub>DD</sub> - 0.3       |                             | V     |

|                  |                                                                | I <sub>OH</sub> = -30μA                | V <sub>DD</sub> - 0.7       |                             | V     |

|                  |                                                                | I <sub>OH</sub> = -60μA                | V <sub>DD</sub> - 1.5       |                             | V     |

| V <sub>OH1</sub> | Output High Voltage (Port 0 in External                        | $V_{DD} = 4.5V$                        |                             |                             |       |

|                  | Bus Mode) <sup>4</sup>                                         | I <sub>OH</sub> = -200μA               | V <sub>DD</sub> - 0.3       |                             | V     |

|                  |                                                                | I <sub>OH</sub> = -3.2mA               | V <sub>DD</sub> - 0.7       |                             | V     |

| V <sub>BOD</sub> | Brown-out Detection Voltage                                    |                                        | 3.85                        | 4.15                        | V     |

| IIL              | Logical 0 Input Current (Ports 1, 2, 3)                        | $V_{IN} = 0.4V$                        |                             | -75                         | μA    |

| I <sub>TL</sub>  | Logical 1-to-0 Transition Current (Ports 1, 2, 3) <sup>5</sup> | $V_{IN} = 2V$                          |                             | -650                        | μA    |

| ILI              | Input Leakage Current (Port 0)                                 | $0.45 < V_{IN} < V_{DD}$ -0.3          |                             | ±10                         | μA    |

| R <sub>RST</sub> | RST Pull-down Resistor                                         |                                        | 40                          | 225                         | KΩ    |

| C <sub>IO</sub>  | Pin Capacitance <sup>6</sup>                                   | @ 1 MHz, 25°C                          |                             | 15                          | pF    |

| I <sub>DD</sub>  | Power Supply Current                                           |                                        |                             |                             |       |

|                  | IAP Mode                                                       |                                        |                             |                             |       |

|                  | @ 40 MHz                                                       |                                        |                             | 88                          | mA    |

|                  | Active Mode                                                    |                                        |                             |                             |       |

|                  | @ 40 MHz                                                       |                                        |                             | 50                          | mA    |

|                  | Idle Mode                                                      |                                        |                             |                             |       |

|                  | @ 40 MHz                                                       |                                        |                             | 42                          | mA    |

|                  | Power-down Mode (min. $V_{DD} = 2V$ )                          | $T_A = 0^{\circ}C$ to +70°C            |                             | 80                          | μA    |

|                  |                                                                | $T_A = -40^{\circ}C$ to $+85^{\circ}C$ |                             | 90                          | μA    |

### **Table 36:** DC Electrical Characteristics for SST89E516RDx $T_{A} = -40^{\circ}$ C to $+85^{\circ}$ C: $V_{DD} = 4.5 \cdot 5.5$ V: $V_{SS} = 0$ V

T0-0.1 25093

Data Sheet

### **Table 37:** DC Electrical Characteristics for SST89V516RDx $T_A = -40^{\circ}$ C to +85°C; $V_{DD} = 2.7-3.6$ V; $V_{SS} = 0$ V

| Symbo            | Denometer                                                      | Test Canditians                                 | Min                         | Max                      | Unit |

|------------------|----------------------------------------------------------------|-------------------------------------------------|-----------------------------|--------------------------|------|

| <b>I</b>         | Parameter                                                      | Test Conditions                                 | Min                         | Max                      | S    |

| VIL              | Input Low Voltage                                              | 2.7 < V <sub>DD</sub> < 3.6                     | -0.5                        | 0.7                      | V    |

| Vih              | Input High Voltage                                             | $2.7 < V_{DD} < 3.6$                            | 0.2V <sub>DD</sub> +<br>0.9 | V <sub>DD</sub> +<br>0.5 | V    |

| V <sub>IH1</sub> | Input High Voltage (XTAL1, RST)                                | $2.7 < V_{DD} < 3.6$                            | $0.7V_{DD}$                 | V <sub>DD</sub> +<br>0.5 | V    |

| V <sub>OL</sub>  | Output Low Voltage (Ports 1.5, 1.6, 1.7)                       | V <sub>DD</sub> = 2.7V                          |                             |                          |      |

|                  |                                                                | I <sub>OL</sub> = 16mA                          |                             | 1.0                      | V    |

| V <sub>OL</sub>  | Output Low Voltage (Ports 1, 2, 3) <sup>1</sup>                | V <sub>DD</sub> = 2.7V                          |                             |                          |      |

|                  |                                                                | $I_{OL} = 100 \mu A^2$                          |                             | 0.3                      | V    |

|                  |                                                                | $I_{OL} = 1.6 \text{mA}^2$                      |                             | 0.45                     | V    |

|                  |                                                                | $I_{OL} = 3.5 \text{mA}^2$                      |                             | 1.0                      | V    |

| V <sub>OL1</sub> | Output Low Voltage (Port 0, ALE, PSEN#) <sup>1,3</sup>         | $V_{DD} = 2.7V$                                 |                             |                          |      |

|                  |                                                                | $I_{OL} = 200 \mu A^2$                          |                             | 0.3                      | V    |

|                  |                                                                | $I_{OL} = 3.2 \text{mA}^2$                      |                             | 0.45                     | V    |

| Voн              | Output High Voltage (Ports 1, 2, 3, ALE,                       | $V_{DD} = 2.7V$                                 |                             |                          |      |

|                  | PSEN#) <sup>4</sup>                                            | I <sub>OH</sub> = -10μA                         | V <sub>DD</sub> - 0.3       |                          | V    |

|                  |                                                                | I <sub>OH</sub> = -30µА                         | V <sub>DD</sub> - 0.7       |                          | V    |

|                  |                                                                | I <sub>OH</sub> = -60μA                         | V <sub>DD</sub> - 1.5       |                          | V    |

| V <sub>OH1</sub> | Output High Voltage (Port 0 in External Bus                    | V <sub>DD</sub> = 2.7V                          |                             |                          |      |

|                  | Mode) <sup>4</sup>                                             | I <sub>OH</sub> = -200μA                        | V <sub>DD</sub> - 0.3       |                          | V    |

|                  |                                                                | I <sub>OH</sub> = -3.2mA                        | V <sub>DD</sub> - 0.7       |                          | V    |

| V <sub>BOD</sub> | Brown-out Detection Voltage                                    |                                                 | 2.35                        | 2.55                     | V    |

| IIL              | Logical 0 Input Current (Ports 1, 2, 3)                        | $V_{IN} = 0.4V$                                 |                             | -75                      | μA   |

| I <sub>TL</sub>  | Logical 1-to-0 Transition Current (Ports 1, 2, 3) <sup>5</sup> | $V_{IN} = 2V$                                   |                             | -650                     | μA   |

| ILI              | Input Leakage Current (Port 0)                                 | $0.45 < V_{IN} < V_{DD}$ -0.3                   |                             | ±10                      | μA   |

| R <sub>RST</sub> | RST Pull-down Resistor                                         |                                                 |                             | 225                      | KΩ   |

| C <sub>IO</sub>  | Pin Capacitance <sup>6</sup>                                   | @ 1 MHz, 25°C                                   |                             | 15                       | pF   |

| I <sub>DD</sub>  | Power Supply Current                                           |                                                 |                             |                          |      |

|                  | IAP Mode                                                       |                                                 |                             |                          |      |

|                  | @ 33 MHz                                                       |                                                 |                             | 47                       | mA   |

|                  | Active Mode                                                    |                                                 |                             |                          |      |

|                  | @ 33 MHz                                                       |                                                 |                             | 30                       | mA   |

|                  | Idle Mode                                                      |                                                 |                             |                          |      |

|                  | @ 33 MHz                                                       |                                                 |                             | 21                       | mA   |

|                  | Power-down Mode (min. V <sub>DD</sub> = 2V)                    | $T_A = 0^{\circ}C$ to +70°C                     |                             | 45                       | μA   |

|                  |                                                                | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$ |                             | 55                       | μA   |

T0-0.1 25093

Data Sheet

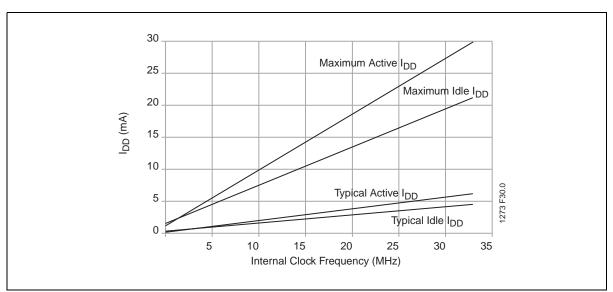

Figure 34:I<sub>DD</sub> vs. Frequency for 3V SST89V516RDx

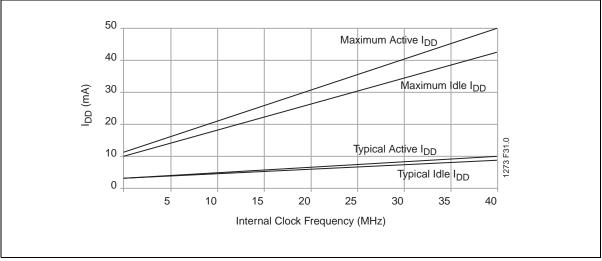

Figure 35:I<sub>DD</sub> vs. Frequency for 5V SST89E516RDx

Data Sheet

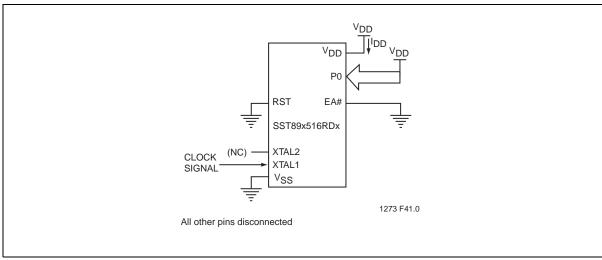

Figure 45:I<sub>DD</sub> Test Condition, Idle Mode

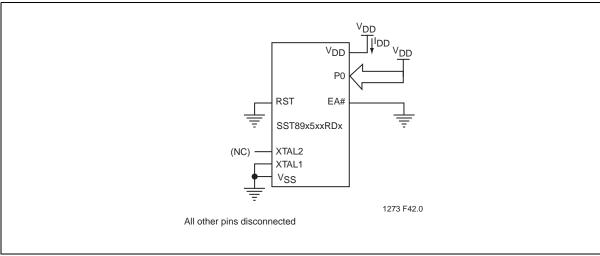

Figure 46:I<sub>DD</sub> Test Condition, Power-down Mode

| Table 41: Flash Memory Prog | ramming/Verification Parameters <sup>1</sup> |

|-----------------------------|----------------------------------------------|

|-----------------------------|----------------------------------------------|

| Parameter <sup>2</sup>              | Max | Units      |

|-------------------------------------|-----|------------|

| Chip-Erase Time                     | 150 | ms         |

| Block-Erase Time                    | 100 | ms         |

| Sector-Erase Time                   | 30  | ms         |

| Byte-Program Time <sup>3</sup>      | 50  | μs         |

| Select-Block Program Time           | 500 | ns         |

| Re-map or Security bit Program Time | 80  | μs         |

|                                     |     | T0-0.1 250 |

1. For IAP operations, the program execution overhead must be added to the above timing parameters.

2. Program and Erase times will scale inversely proportional to programming clock frequency.

3. Each byte must be erased before programming.

Data Sheet

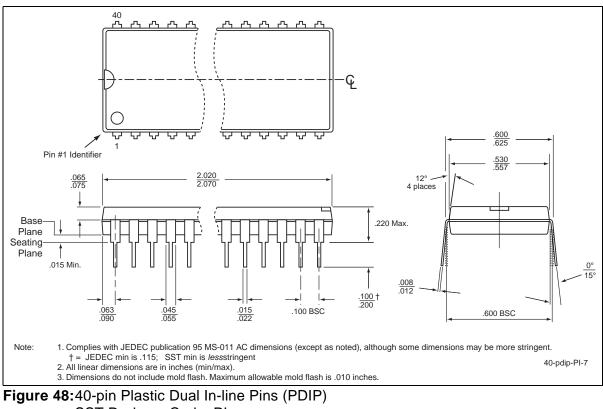

SST Package Code: PI