#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                               |

| Core Processor             | 8051                                                                                   |

| Core Size                  | 8-Bit                                                                                  |

| Speed                      | 40MHz                                                                                  |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                               |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                       |

| Number of I/O              | 36                                                                                     |

| Program Memory Size        | 72KB (72K x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 1K x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                            |

| Data Converters            | -                                                                                      |

| Oscillator Type            | External                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 44-TQFP                                                                                |

| Supplier Device Package    | 44-TQFP (10x10)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89e516rd2-40-i-tqje-zz134 |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Data Sheet

## **Pin Assignments**

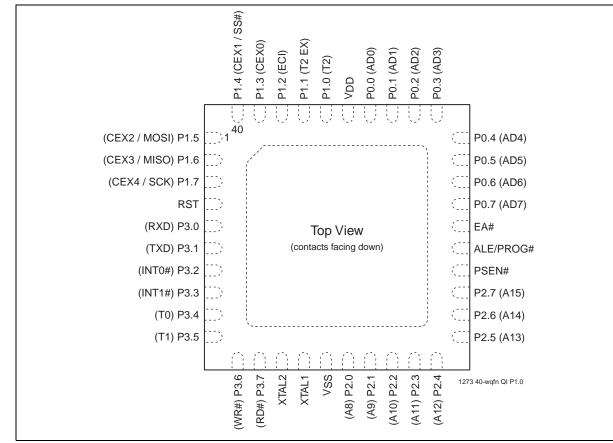

Figure 2: Pin Assignments for 40-Contact WQFN

Data Sheet

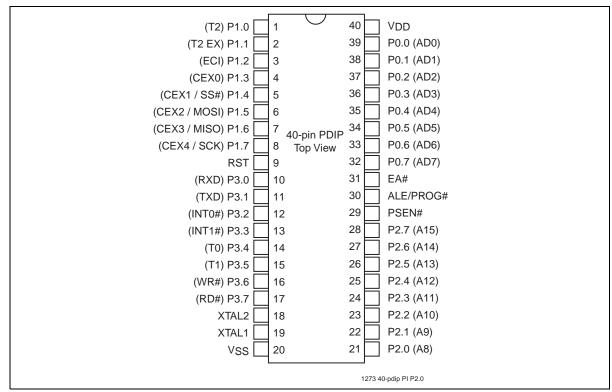

Figure 3: Pin Assignments for 40-pin PDIP

Data Sheet

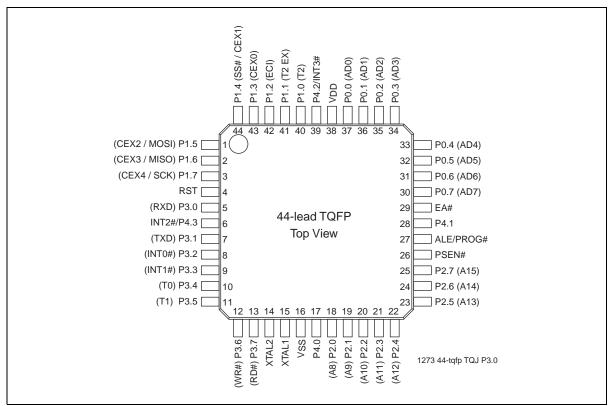

Figure 4: Pin Assignments for 44-lead TQFP

Data Sheet

## Program Memory Block Switching

The program memory block switching feature of the device allows either Block 1 or the lowest 8 KByte of Block 0 to be used for the lowest 8 KByte of the program address space. SFCF[1:0] controls program memory block switching.

## Table 2: SFCF Values for Program Memory Block Switching

| SFCF[1:0]  | Program Memory Block Switching                                                                                                                                                                                                                                                                                                                              |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01, 10, 11 | Block 1 is not visible to the program counter (PC).<br>Block 1 is reachable only via in-application programming from 0000H - 1FFFH.                                                                                                                                                                                                                         |

| 00         | Block 1 is overlaid onto the low 8K of the program address space; occupying address locations 0000H - 1FFFH.<br>When the PC falls within 0000H - 1FFFH, the instruction will be fetched from Block 1 instead of Block 0.<br>Outside of 0000H - 1FFFH, Block 0 is used. Locations 0000H - 1FFFH of Block 0 are reachable through in-application programming. |

T0-0.0 25093

## **Reset Configuration of Program Memory Block Switching**

Program memory block switching is initialized after reset according to the state of the Start-up Configuration bit SC0. The SC0 bit is programmed via an external host mode command or an IAP Mode command. See Table 14.

Once out of reset, the SFCF[0] bit can be changed dynamically by the program for desired effects. Changing SFCF[0] will not change the SC0 bit.

Caution must be taken when dynamically changing the SFCF[0] bit. Since this will cause different physical memory to be mapped to the logical program address space. The user must avoid executing block switching instructions within the address range 0000H to 1FFFH.

|                  | State of SFCF[1:0] after:           |                                       |                   |  |  |  |  |

|------------------|-------------------------------------|---------------------------------------|-------------------|--|--|--|--|

| SC0 <sup>1</sup> | Power-on<br>or<br>External<br>Reset | WDT Reset<br>or<br>Brown-out<br>Reset | Software<br>Reset |  |  |  |  |

| U (1)            | 00<br>(default)                     | x0                                    | 10                |  |  |  |  |

| P (0)            | 01                                  | x1                                    | 11                |  |  |  |  |

| ·                |                                     |                                       | T0-0.0 250        |  |  |  |  |

**Table 3:** SFCF Values Under Different Reset Conditions

1. P = Programmed (Bit logic state = 0),

U = Unprogrammed (Bit logic state = 1)

## Data RAM Memory

The data RAM has 1024 bytes of internal memory. The RAM can be addressed up to 64KB for external data memory.

Data Sheet

|                   |                                   | Direct  | Bit Add     | Bit Address, Symbol, or Alternative Port Function |          |          |           |          | Reset     |             |               |

|-------------------|-----------------------------------|---------|-------------|---------------------------------------------------|----------|----------|-----------|----------|-----------|-------------|---------------|

| Symbol            | Description                       | Address | MSB         |                                                   |          |          |           |          |           | LSB         | Value         |

| TMOD              | Timer/Counter                     | 89H     |             | Timer 1 Timer 0                                   |          |          |           |          |           |             | 00H           |

|                   | Mode Control                      |         | GAT<br>E    | C/T#                                              | M1       | M0       | GATE      | C/<br>T# | M1        | MO          |               |

| TCON <sup>1</sup> | Timer/Counter<br>Control          | 88H     | TF1         | TR1                                               | TF0      | TR0      | IE1       | IT1      | IE0       | IT0         | 00H           |

| TH0               | Timer 0 MSB                       | 8CH     |             |                                                   |          | Tł       | H0[7:0]   |          |           |             | 00H           |

| TL0               | Timer 0 LSB                       | 8AH     |             |                                                   |          | TI       | _0[7:0]   |          |           |             | 00H           |

| TH1               | Timer 1 MSB                       | 8DH     |             |                                                   |          | Tł       | H1[7:0]   |          |           |             | 00H           |

| TL1               | Timer 1 LSB                       | 8BH     |             |                                                   |          | TI       | L1[7:0]   |          |           |             | 00H           |

| T2CON<br>1        | Timer / Coun-<br>ter 2<br>Control | C8H     | TF2         | EXF<br>2                                          | RCL<br>K | TCL<br>K | EXEN<br>2 | TR2      | C/<br>T2# | CP/<br>RL2# | 00H           |

| T2MOD             | Timer2<br>Mode Control            | C9H     | -           | -                                                 | -        | -        | -         | -        | T2O<br>E  | DCEN        | xxxxxx00<br>b |

| TH2               | Timer 2 MSB                       | CDH     |             | TH2[7:0]                                          |          |          |           |          |           |             | 00H           |

| TL2               | Timer 2 LSB                       | ССН     |             | TL2[7:0]                                          |          |          |           |          |           | 00H         |               |

| RCAP2<br>H        | Timer 2<br>Capture MSB            | СВН     | RCAP2H[7:0] |                                                   |          |          |           | 00H      |           |             |               |

| RCAP2<br>L        | Timer 2<br>Capture LSB            | CAH     |             |                                                   |          | RCA      | AP2L[7:0] |          |           |             | 00H           |

#### Table 9: Timer/Counters SFRs

1. Bit Addressable SFRs

T0-0.0 25093

Data Sheet

| Location            | 7           | 6                                                                                                            | 5               | 4              | 3            | 2            | 1              | 0           | Reset Value |

|---------------------|-------------|--------------------------------------------------------------------------------------------------------------|-----------------|----------------|--------------|--------------|----------------|-------------|-------------|

| 85H                 |             | Watchdog Timer Data/Reload                                                                                   |                 |                |              |              |                |             | 00H         |

| Symbol              | Function    | 1                                                                                                            |                 |                |              |              |                |             |             |

| WDTD                | Initial/Rel | oad value                                                                                                    | in Watcho       | log Timer.     | New value    | won't be     | effective u    | intil WDT   | is set.     |

| CA Timer/Counter Co | ntrol Regi  | ster <sup>1</sup> (CCC                                                                                       | ON)             |                |              |              |                |             |             |

| Location            |             | 6                                                                                                            | 5               | 4              | 3            | 2            | 1              | 0           | Reset Value |

| D8H                 | CF          | CR                                                                                                           | -               | CCF4           | CCF3         | CCF2         | CCF1           | CCF0        | 00x00000k   |

|                     | 1. Bit add  | dressable                                                                                                    |                 |                |              |              |                |             |             |

| Symbol              | Function    | 1                                                                                                            |                 |                |              |              |                |             |             |

| CF                  |             | inter Overf                                                                                                  | •               |                |              |              |                |             |             |

|                     |             |                                                                                                              |                 |                |              |              |                |             | CMOD is set |

| 05                  | -           | -                                                                                                            |                 | ware or so     | itware, but  | can only     | cleared by     | software    |             |

| CR                  |             | inter Run c                                                                                                  |                 | CA counter     | on Must      | he cleared   | hv softwa      | are to turn | the PCA     |

|                     | counter o   |                                                                                                              |                 | or counter     | on. Mast     |              | by solution    |             |             |

| -                   | Not imple   | emented, re                                                                                                  | eserved fo      | or future us   | e.           |              |                |             |             |

|                     | Note: User  | should not w                                                                                                 | rite '1's to re | served bits. 7 | he value rea | d from a res | erved bit is i | ndeterminat | e.          |

| CCF4                |             | dule 4 inter<br>cleared by                                                                                   |                 | Set by hare    | dware whe    | en a match   | or captur      | e occurs.   |             |

| CCF3                |             | •                                                                                                            |                 | Set by har     | dwaro whe    | n a match    | or cantur      |             |             |

| 0010                |             | cleared by                                                                                                   |                 | Set by hard    |              | a mator      | i or captur    | e occurs.   |             |

| CCF2                | PCA Mod     | lule 2 inter                                                                                                 | rupt flag.      | Set by hare    | dware whe    | n a match    | or captur      | e occurs.   |             |

|                     | Must be o   | PCA Module 2 interrupt flag. Set by hardware when a match or capture occurs.<br>Must be cleared by software. |                 |                |              |              |                |             |             |

| CCF1                |             |                                                                                                              |                 | Set by hare    | dware whe    | en a match   | or captur      | e occurs.   |             |

| CCF0                |             | cleared by                                                                                                   |                 | Cathylar       |              | n a matak    |                |             |             |

| CCFU                |             | cleared by                                                                                                   |                 | Set by har     | aware whe    | en a mater   | or captur      | e occurs.   |             |

|                     |             |                                                                                                              |                 |                |              |              |                |             |             |

|                     |             |                                                                                                              |                 |                |              |              |                |             |             |

Data Sheet

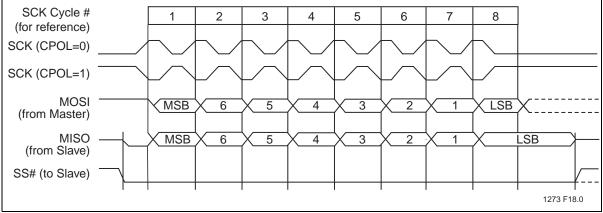

#### PCA Compare/Capture Module Mode Register<sup>1</sup> (CCAPMn)

| Location | 7           | 6           | 5     | 4     | 3    | 2    | 1    | 0     | Reset Value |

|----------|-------------|-------------|-------|-------|------|------|------|-------|-------------|

| DAH      | -           | ECOM0       | CAPP0 | CAPN0 | MAT0 | TOG0 | PWM0 | ECCF0 | 00xxx000b   |

| DBH      | -           | ECOM1       | CAPP1 | CAPN1 | MAT1 | TOG1 | PWM1 | ECCF1 | 00xxx000b   |

| DCH      | -           | ECOM2       | CAPP2 | CAPN2 | MAT2 | TOG2 | PWM2 | ECCF2 | 00xxx000b   |

| DDH      | -           | ECOM3       | CAPP3 | CAPN3 | MAT3 | TOG3 | PWM3 | ECCF3 | 00xxx000b   |

| DEH      | -           | ECOM4       | CAPP4 | CAPN4 | MAT4 | TOG4 | PWM4 | ECCF4 | 00xxx000b   |

|          | 1 Not hit : | addressable |       |       |      |      |      |       | -           |

Not bit addressable

#### Symbol Function

- Not implemented, reserved for future use. Note: User should not write '1's to reserved bits. The value read from a reserved bit is indeterminate.

#### ECOMn Enable Comparator

- 0: Disables the comparator function

- 1: Enables the comparator function

- CAPPn Capture Positive

- 0: Disables positive edge capture on CEX[4:0]

- 1: Enables positive edge capture on CEX[4:0]

#### CAPNn Capture Negative

- 0: Disables negative edge capture on CEX[4:0]

- 1: Enables negative edge capture on CEX[4:0]

## MATn Match: Set ECOM[4:0] and MAT[4:0] to implement the software timer mode 0: Disables software timer mode

1: A match of the PCA counter with this module's compare/capture register causes the CCFn bit in CCON to be set, flagging an interrupt.

#### TOGn Toggle

0: Disables toggle function

1: A match of the PCA counter with this module's compare/capture register causes the CEXn pin to toggle.

- PWMn Pulse Width Modulation mode

- 0: Disables PWM mode

1: Enables CEXn pin to be used as a pulse width modulated output

# ECCFn Enable CCF Interrupt 0: Disables compare/capture flag CCF[4:0] in the CCON register to generate an interrupt request. 1: Enables compare/capture flag CCF[4:0] in the CCON register to generate an interrupt request.

#### Data Sheet

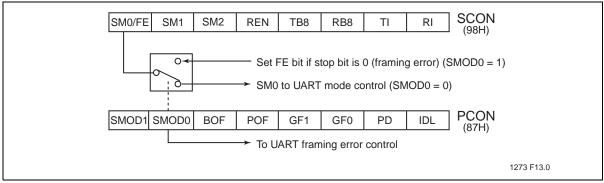

#### Serial Port Control Register (SCON)

| Location | 7      | 6   | 5   | 4   | 3   | 2   | 1  | 0  | Reset Value |

|----------|--------|-----|-----|-----|-----|-----|----|----|-------------|

| 98H      | SM0/FE | SM1 | SM2 | REN | TB8 | RB8 | TI | RI | 0000000b    |

#### Symbol Function

| <ul> <li>FE Set SMOD0 = 1 to access FE bit.</li> <li>0: No framing error</li> <li>1: Framing Error. Set by receiver when an invalid stop bit is detected. This bit needs to be</li> </ul> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                           |

- SM0 SMOD0 = 0 to access SM0 bit. Serial Port Mode Bit 0

- SM1 Serial Port Mode Bit 1

| SM0 | SM1                    | Mode | Description    | Baud Rate <sup>1</sup>                                                                      |

|-----|------------------------|------|----------------|---------------------------------------------------------------------------------------------|

| 0   | 0                      | 0    | Shift Register | f <sub>OSC</sub> /6 (6 clock mode) or<br>f <sub>OSC</sub> /12 (12 clock mode)               |

| 0   | 1                      | 1    | 8-bit UART     | Variable                                                                                    |

| 1   | 0                      | 2    | 9-bit UART     | $f_{OSC}/32$ or $f_{OSC}/16$ (6 clock mode) or $f_{OSC}/64$ or $f_{OSC}/32$ (12 clock mode) |

| 1   | 1<br>illator fraguenov | 3    | 9-bit UART     | Variable                                                                                    |

1. f<sub>OSC</sub> = oscillator frequency

- SM2 Enables the Automatic Address Recognition feature in Modes 2 or 3. If SM2 = 1 then RI will not be set unless the received 9th data bit (RB8) is 1, indicating an address, and the received byte is a given or broadcast address. In Mode 1, if SM2 = 1 then RI will not be activated unless a valid stop bit was received. In Mode 0, SM2 should be 0.

- REN Enables serial reception. 0: to disable reception. 1: to enable reception.

- TB8 The 9th data bit that will be transmitted in Modes 2 and 3. Set or clear by software as

- desired.

- RB8 In Modes 2 and 3, the 9th data bit that was received. In Mode 1, if SM2 = 0, RB8 is the stop bit that was received. In Mode 0, RB8 is not used.

- TI Transmit interrupt flag. Set by hardware at the end of the 8th bit time in Mode 0, or at the beginning of the stop bit in the other modes, in any serial transmission, Must be cleared by software.

- RI Receive interrupt flag. Set by hardware at the end of the8th bit time in Mode 0, or halfway through the stop bit time in the other modes, in any serial reception (except see SM2). Must be cleared by software.

## Data Sheet

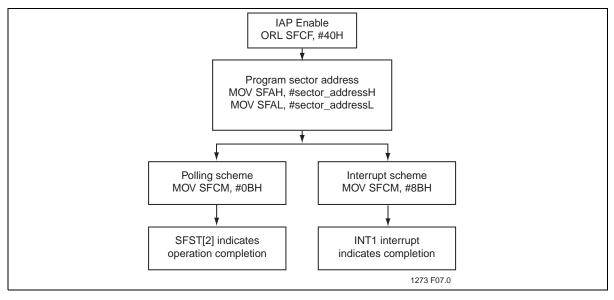

#### Sector-Erase

The Sector-Erase command erases all of the bytes in a sector. The sector size for the flash memory blocks is 128 Bytes. The selection of the sector to be erased is determined by the contents of SFAH and SFAL.

#### Figure 11:Sector Erase

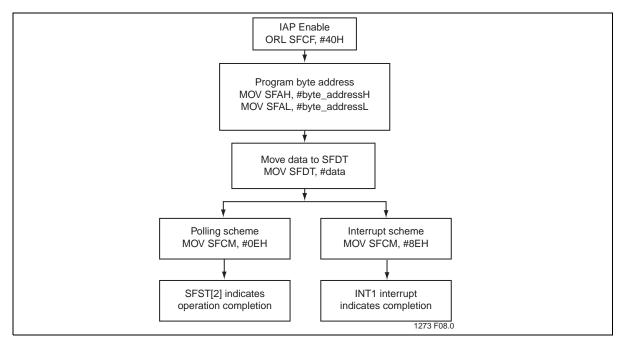

#### **Byte-Program**

The Byte-Program command programs data into a single byte. The address is determined by the contents of SFAH and SFAL. The data byte is in SFDT.

## Figure 12:Byte Program

Data Sheet

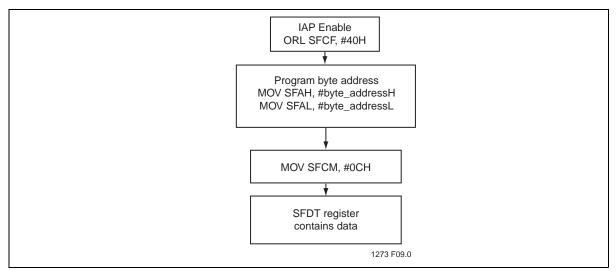

#### Byte-Verify

The Byte-Verify command allows the user to verify that the device has correctly performed an Erase or Program command. Byte-Verify command returns the data byte in SFDT if the command is successful. The user is required to check that the previous flash operation has fully completed before issuing a Byte-Verify. Byte-Verify command execution time is short enough that there is no need to poll for command completion and no interrupt is generated.

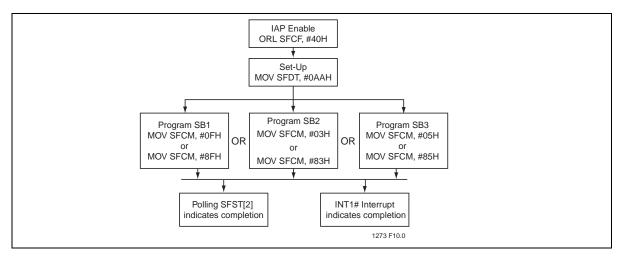

## Prog-SB3, Prog-SB2, Prog-SB1

Prog-SB3, Prog-SB2, Prog-SB1 commands are used to program the security bits (see Table 25). Completion of any of these commands, the security options will be updated immediately.

Security bits previously in un-programmed state can be programmed by these commands. Prog-SB3, Prog-SB2 and Prog-SB1 commands should only reside in Block 1 or external code memory.

## Figure 14: Prog-SB3, Prog-SB2, Prog-SB1

Data Sheet

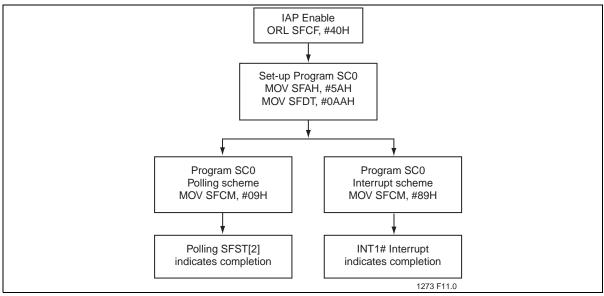

#### Prog-SC0

Prog-SC0 command is used to program the SC0 bit. This command only changes the SC0 bit and has no effect on BSEL bit until after a reset cycle.

SC0 bit previously in un-programmed state can be programmed by this command. The Prog-SC0 command should reside only in Block 1 or external code memory.

## Figure 15: Prog-SC0

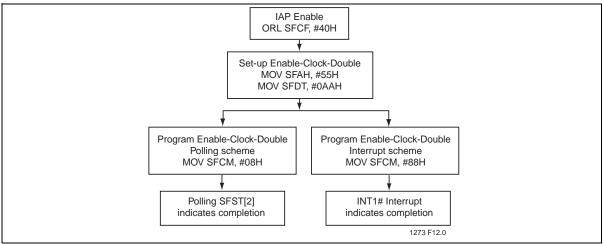

## Enable-Clock-Double

Enable-Clock-Double command is used to make the MCU run at 6 clocks per machine cycle. The standard (default) is 12 clocks per machine cycle (i.e. clock double command disabled).

## Figure 16: Enable-Clock-Double

There are no IAP counterparts for the external host commands Select-Block0 and Select-Block1.

Data Sheet

## Serial I/O

## Full-Duplex, Enhanced UART

The device serial I/O port is a full-duplex port that allows data to be transmitted and received simultaneously in hardware by the transmit and receive registers, respectively, while the software is performing other tasks. The transmit and receive registers are both located in the Serial Data Buffer (SBUF) special function register. Writing to the SBUF register loads the transmit register, and reading from the SBUF register obtains the contents of the receive register.

The UART has four modes of operation which are selected by the Serial Port Mode Specifier (SM0 and SM1) bits of the Serial Port Control (SCON) special function register. In all four modes, transmission is initiated by any instruction that uses the SBUF register as a destination register. Reception is initiated in mode 0 when the Receive Interrupt (RI) flag bit of the Serial Port Control (SCON) SFR is cleared and the Reception Enable/ Disable (REN) bit of the SCON register is set. Reception is initiated in the other modes by the incoming start bit if the REN bit of the SCON register is set.

## **Framing Error Detection**

Framing Error Detection is a feature, which allows the receiving controller to check for valid stop bits in modes 1, 2, or 3. Missing stops bits can be caused by noise in serial lines or from simultaneous transmission by two CPUs.

Framing Error Detection is selected by going to the PCON register and changing SMOD0 = 1 (see Figure 17). If a stop bit is missing, the Framing Error bit (FE) will be set. Software may examine the FE bit after each reception to check for data errors. After the FE bit has been set, it can only be cleared by software. Valid stop bits do not clear FE. When FE is enabled, RI rises on the stop bit, instead of the last data bit (see Figure 18 and Figure 19).

Figure 17: Framing Error Block Diagram

Data Sheet

If the user added a third slave such as the example below:

Slave 3

SADDR

=

1111

1001

SADEN

=

1111

0101

GIVEN

=

1111

X0X1

| Select Slave 3 Only                      |           |                        |  |  |  |  |  |

|------------------------------------------|-----------|------------------------|--|--|--|--|--|

| Slave 2 Given Address Possible Addresses |           |                        |  |  |  |  |  |

|                                          | 1111 X0X1 | 1111 1011<br>1111 1001 |  |  |  |  |  |

The user could use the possible addresses above to select slave 3 only. Another combination could be to select slave 2 and 3 only as shown below.

| Select Slaves 2 & 3 Only |                    |  |  |  |  |

|--------------------------|--------------------|--|--|--|--|

| Slaves 2 & 3             | Possible Addresses |  |  |  |  |

|                          | 1111 0011          |  |  |  |  |

More than one slave may have the same SADDR address as well, and a given address could be used to modify the address so that it is unique.

#### Using the Broadcast Address to Select Slaves

Using the broadcast address, the master can communicate with all the slaves at once. It is formed by performing a logical OR of SADDR and SADEN with '0's in the result treated as "don't cares".

#### Slave 1

1111 0001 = SADDR +1111 1010 = SADEN 1111 1X11 = Broadcast

"Don't cares" allow for a wider range in defining the broadcast address, but in most cases, the broadcast address will be FFH.

On reset, SADDR and SADEN are "0". This produces an given address of all "don't cares" as well as a broadcast address of all "don't cares." This effectively disables Automatic Addressing mode and allows the microcontroller to function as a standard 8051, which does not make use of this feature.

Data Sheet

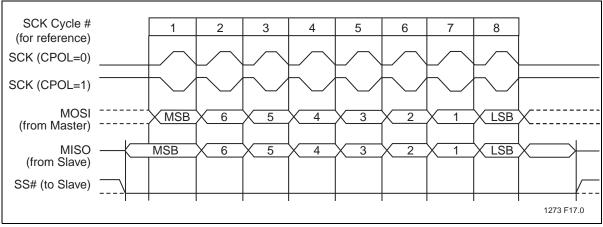

## **SPI Transfer Formats**

Figure 21:SPI Transfer Format with CPHA = 0

Figure 22:SPI Transfer Format with CPHA = 1

Data Sheet

Figure 27: PCA High Speed Output Mode

## **Pulse Width Modulator**

The Pulse Width Modulator (PWM) mode is used to generate 8-bit PWMs by comparing the low byte of the PCA timer (CL) with the low byte of the compare register (CCAPnL). When CL < CCAPnL the output is low. When  $CL \ge CCAPnL$  the output is high. To activate this mode, the user must set the PWM and ECOM bits in the module's CCAPMn SFR. (See Figure 28 and Table 24)

In PWM mode, the frequency of the output depends on the source for the PCA timer. Since there is only one set of CH and CL registers, all modules share the PCA timer and frequency. Duty cycle of the output is controlled by the value loaded into the high byte (CCAPnH). Since writes to the CCAPnH register are asynchronous, a new value written to the high byte will not be shifted into CCAPnL for comparison until the next period of the output (when CL rolls over from 255 to 00).

To calculate values for CCAPnH for any duty cycle, use the following equation:

CCAPnH = 256(1 - Duty Cycle)

where CCAPnH is an 8-bit integer and Duty Cycle is a fraction.

Data Sheet

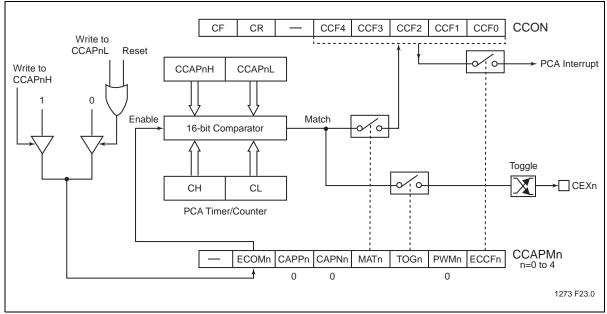

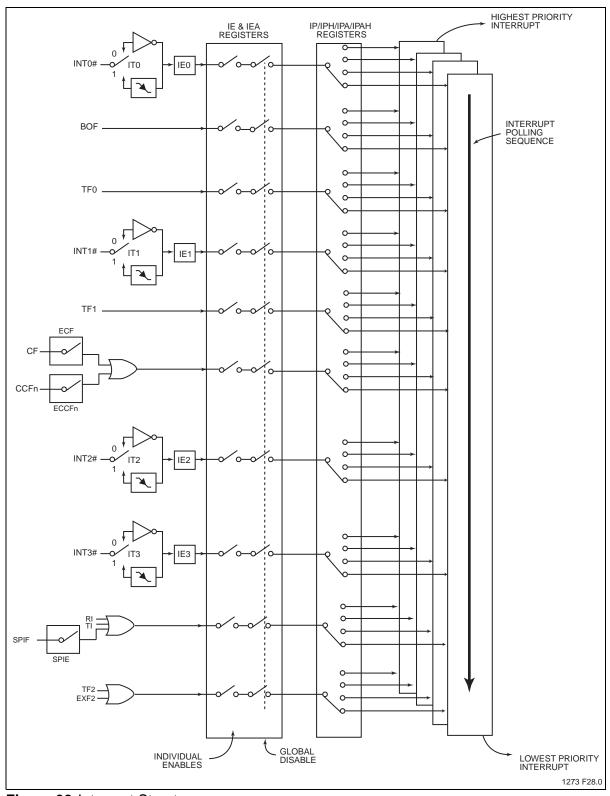

## Figure 32: Interrupt Structure

Data Sheet

## Figure 33:Oscillator Characteristics

## Table 30: Clock Doubling Features

| Device       | Sta                                                     | ndard Mode (x1) | Clock Double Mode (x2)         |                                           |  |

|--------------|---------------------------------------------------------|-----------------|--------------------------------|-------------------------------------------|--|

|              | Clocks perMax. External ClockMachineFrequencyCycle(MHz) |                 | Clocks per<br>Machine<br>Cycle | Max. External Clock<br>Frequency<br>(MHz) |  |

| SST89E516RDx | 12                                                      | 40              | 6                              | 20                                        |  |

| SST89V516RDx | 12                                                      | 33              | 6                              | 16                                        |  |

T0-0.0 25093

Data Sheet

- 1. Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

- Maximum IOL per port pin: 15mA 26mA

- Maximum IOL per 8-bit port: Maximum IOL total for all outputs: 71mA

- If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 2. Capacitive loading on Ports 0 and 2 may cause spurious noise to be superimposed on the Vols of ALE and Ports 1 & 3. The noise due to external bus capacitance discharging into the Port 0 & 2 pins when the pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100pF), the noise pulse on the ALE pin may exceed 0.8V. In such cases, it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input.

- 3. Load capacitance for Port 0, ALE & PSEN#= 100pF, load capacitance for all other outputs = 80pF.

- 4. Capacitive loading on Ports 0 & 2 may cause the V<sub>OH</sub> on ALE and PSEN# to momentarily fall below the V<sub>DD</sub> 0.7 specification when the address bits are stabilizing.

- 5. Pins of Ports 1, 2, and 3 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when V<sub>IN</sub> is approximately 2V.

- 6. Pin capacitance is characterized but not tested. EA# is 25pF (max).

Data Sheet

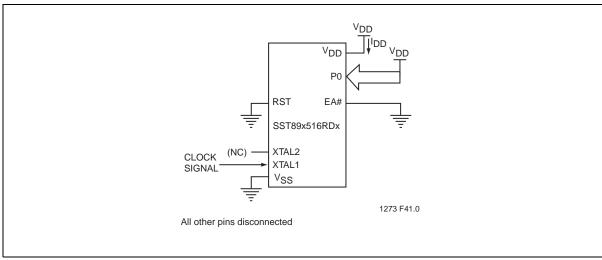

Figure 45:I<sub>DD</sub> Test Condition, Idle Mode

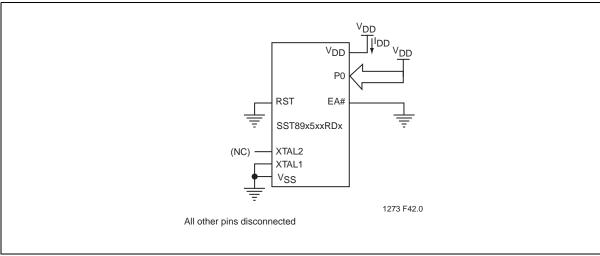

Figure 46:I<sub>DD</sub> Test Condition, Power-down Mode

| Table 41: Flash Memory Prog | ramming/Verification Parameters <sup>1</sup> |

|-----------------------------|----------------------------------------------|

|-----------------------------|----------------------------------------------|

| Parameter <sup>2</sup>              | Max | Units      |

|-------------------------------------|-----|------------|

| Chip-Erase Time                     | 150 | ms         |

| Block-Erase Time                    | 100 | ms         |

| Sector-Erase Time                   | 30  | ms         |

| Byte-Program Time <sup>3</sup>      | 50  | μs         |

| Select-Block Program Time           | 500 | ns         |

| Re-map or Security bit Program Time | 80  | μs         |

|                                     |     | T0-0.1 250 |

1. For IAP operations, the program execution overhead must be added to the above timing parameters.

2. Program and Erase times will scale inversely proportional to programming clock frequency.

3. Each byte must be erased before programming.

Data Sheet

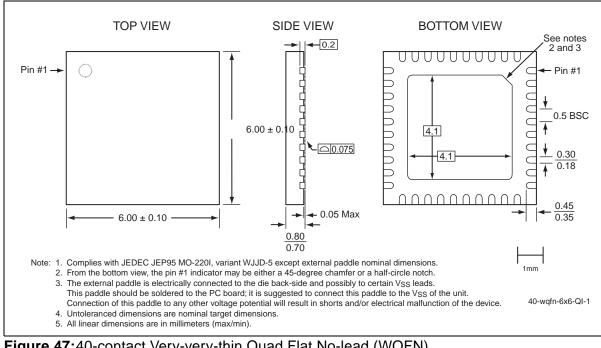

## **Packaging Diagrams**

Figure 47:40-contact Very-very-thin Quad Flat No-lead (WQFN) SST Package Code: QI