Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | 8051                                                                             |

| Core Size                  | 8-Bit                                                                            |

| Speed                      | 40MHz                                                                            |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                 |

| Number of I/O              | 36                                                                               |

| Program Memory Size        | 72KB (72K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | <u>.</u>                                                                         |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Data Converters            |                                                                                  |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89e516rd2-40-i-tqje |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Data Sheet

# **Product Description**

The SST89E516RDx and SST89V516RDx are members of the FlashFlex family of 8-bit microcontroller products designed and manufactured with SST's patented and proprietary SuperFlash CMOS semiconductor process technology. The split-gate cell design and thick-oxide tunneling injector offer significant cost and reliability benefits for SST's customers. The devices use the 8051 instruction set and are pin-for-pin compatible with standard 8051 microcontroller devices.

The devices come with 72 KByte of on-chip flash EEPROM program memory which is partitioned into 2 independent program memory blocks. The primary Block 0 occupies 64 KByte of internal program memory space and the secondary Block 1 occupies 8 KByte of internal program memory space.

The 8-KByte secondary block can be mapped to the lowest location of the 64 KByte address space; it can also be hidden from the program counter and used as an independent EEPROM-like data memory.

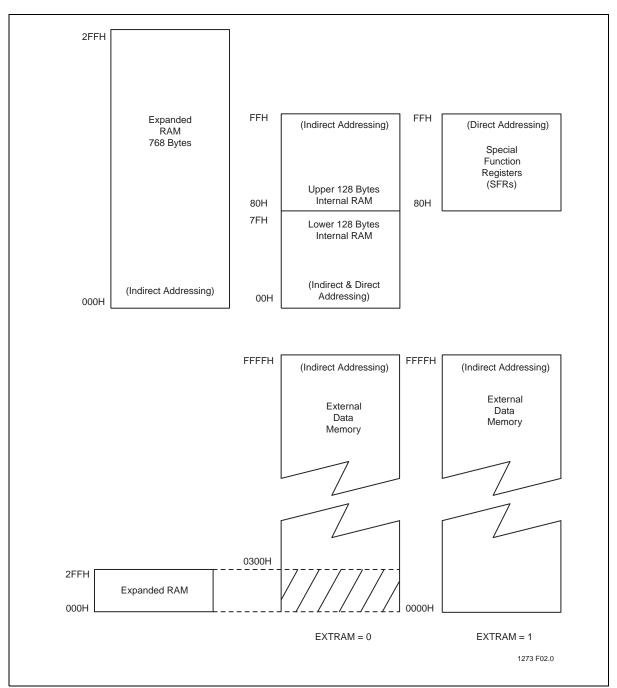

In addition to the 72 KByte of EEPROM program memory on-chip and 1024 x8 bits of on-chip RAM, the devices can address up to 64 KByte of external program memory and up to 64 KByte of external RAM.

The flash memory blocks can be programmed via a standard 87C5x OTP EPROM programmer fitted with a special adapter and the firmware for SST's devices. During power-on reset, the devices can be configured as either a slave to an external host for source code storage or a master to an external host for an in-application programming (IAP) operation. The devices are designed to be programmed in-system and in-application on the printed circuit board for maximum flexibility. The devices are pre-programmed with an example of the bootstrap loader in the memory, demonstrating the initial user program code loading or subsequent user code updating via the IAP operation. The sample bootstrap loader is available for the user's reference and convenience only; SST does not guarantee its functionality or usefulness. Chip-Erase or Block-Erase operations will erase the pre-programmed sample code.

Data Sheet

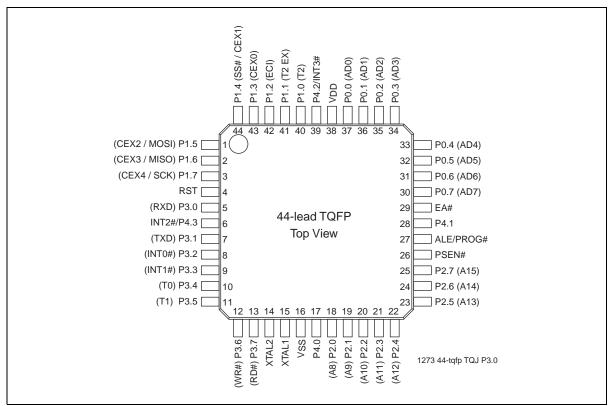

Figure 4: Pin Assignments for 44-lead TQFP

### Data Sheet

### Figure 7: Internal and External Data Memory Structure

Data Sheet

| Symbol           | Description                           | Direct<br>Address | MSB       | Bit Addre | ss, Syrr | nbol, or | Alternat | ive Port | Function   | LSB      | Reset<br>Value |

|------------------|---------------------------------------|-------------------|-----------|-----------|----------|----------|----------|----------|------------|----------|----------------|

| ACC <sup>1</sup> | Accumulator                           | E0H               |           |           |          | AC       | C[7:0]   |          |            |          | 00H            |

| B <sup>1</sup>   | B Register                            | F0H               |           |           |          |          | 7:0]     |          |            |          | 00H            |

| PSW <sup>1</sup> | Program Sta-<br>tus<br>Word           | D0H               | CY        | AC        | F0       | RS<br>1  | RS0      | OV       | F1         | Р        | 00H            |

| SP               | Stack Pointer                         | 81H               |           |           |          | SP       | [7:0]    |          |            |          | 07H            |

| DPL              | Data Pointer<br>Low                   | 82H               |           |           |          | DP       | L[7:0]   |          |            |          | 00H            |

| DPH              | Data Pointer<br>High                  | 83H               |           |           |          | DPI      | H[7:0]   |          |            |          | 00H            |

| IE <sup>1</sup>  | Interrupt<br>Enable                   | A8H               | EA        | EC        | ET2      | ES       | ET1      | EX1      | ET0        | EX0      | 00H            |

| IEA <sup>1</sup> | Interrupt<br>Enable A                 | E8H               | -         | -         | -        | -        | EBO      | -        | -          | -        | xxxx0xxx<br>b  |

| IP <sup>1</sup>  | Interrupt Prior-<br>ity<br>Reg        | B8H               | -         | PPC       | PT2      | PS       | PT1      | PX1      | PT0        | PX0      | x0000000<br>b  |

| IPH              | Interrupt Prior-<br>ity<br>Reg High   | B7H               | -         | PPCH      | PT2<br>H | PS<br>H  | PT1H     | PX1<br>H | PT0H       | PX0<br>H | x0000000<br>b  |

| IP1 <sup>1</sup> | Interrupt Prior-<br>ity<br>Reg A      | F8H               | -         | -         | -        | -        | РВО      | PX3      | PX2        | -        | xxxx0xxx<br>b  |

| IP1H             | Interrupt Prior-<br>ity<br>Reg A High | F7H               | -         | -         | -        | -        | PBO<br>H | PX3<br>H | PX2H       | -        | xxxx0xxx<br>b  |

| PCON             | Power Control                         | 87H               | SMOD<br>1 | SMOD<br>0 | BOF      | PO<br>F  | GF1      | GF0      | PD         | IDL      | 00010000<br>b  |

| AUXR             | Auxiliary Reg                         | 8EH               | -         | -         | -        | -        | -        | -        | EXTRA<br>M | AO       | xxxxxxx0<br>0b |

| AUXR1            | Auxiliary Reg<br>1                    | A2H               | -         | -         | -        | -        | GF2      | 0        | -          | DPS      | xxxx00x0<br>b  |

| XICON            | External<br>Interrupt Con-<br>trol    | AEH               | -         | EX3       | IE3      | IT3      | 0        | EX2      | IE2        | IT2      | 00H            |

1. Bit Addressable SFRs

Data Sheet

|        | D                          | Direct  |           | Bit Address, Symbol, or Alternative Port Function                                    |           |       |                    |                 |                    |                |               |

|--------|----------------------------|---------|-----------|--------------------------------------------------------------------------------------|-----------|-------|--------------------|-----------------|--------------------|----------------|---------------|

| Symbol | Description                | Address | MSB       |                                                                                      |           |       |                    |                 |                    | LSB            | Value         |

| SFCF   | SuperFlash                 | B1H     | -         | IAPE                                                                                 | -         | -     | -                  | -               | SW                 | BSE            | x0xxxx00      |

|        | Configuration              |         |           | Ν                                                                                    |           |       |                    |                 | R                  | L              | b             |

| SFCM   | SuperFlash<br>Command      | B2H     | FIE       | FIE FCM[6:0]                                                                         |           |       |                    |                 |                    | 00H            |               |

| SFAL   | SuperFlash<br>Address Low  | B3H     | Super     | SuperFlash Low Order Byte Address Register - A <sub>7</sub> to A <sub>0</sub> (SFAL) |           |       |                    |                 | 00H                |                |               |

| SFAH   | SuperFlash<br>Address High | B4H     | Su        | perFlash                                                                             | n High (  | Order | Byte Add<br>(SFAH) | ress Register - | A <sub>15</sub> to | A <sub>8</sub> | 00H           |

| SFDT   | SuperFlash<br>Data         | B5H     |           | SuperFlash Data Register                                                             |           |       |                    |                 | 00H                |                |               |

| SFST   | SuperFlash<br>Status       | B6H     | SB1<br>_i | SB2_<br>i                                                                            | SB3<br>_i | -     | EDC_i              | FLASH_BU<br>SY  | -                  | -              | 000x00xx<br>b |

### Table 7: Flash Memory Programming SFRs

T0-0.0 25093

### Table 8: Watchdog Timer SFRs

|           |                                  | Direct  | Bit Ade | dress, | Symb | ool, or Alterr | native Port | Function |     |      | Reset         |

|-----------|----------------------------------|---------|---------|--------|------|----------------|-------------|----------|-----|------|---------------|

| Symbol    | Description                      | Address | MSB     |        |      |                |             |          |     | LSB  | Value         |

| WDTC<br>1 | Watchdog<br>Timer<br>Control     | C0H     | -       | -      | -    | WDOUT          | WDRE        | WDTS     | WDT | SWDT | xxx00x00<br>b |

| WDTD      | Watchdog<br>Timer<br>Data/Reload | 85H     |         |        | ١    | Watchdog T     | imer Data   | a/Reload |     |      | 00H           |

1. Bit Addressable SFRs

### Data Sheet

| counter Mod | ie Registe                                                                                              |             | )           |            |              |         |           |     |             |

|-------------|---------------------------------------------------------------------------------------------------------|-------------|-------------|------------|--------------|---------|-----------|-----|-------------|

| Location    | 7                                                                                                       | 6           | 5           | 4          | 3            | 2       | 1         | 0   | Reset Value |

| D9H         | CIDL                                                                                                    | WDTE        | -           | -          | -            | CPS1    | CPS0      | ECF | 00xxx000b   |

|             | 1. Not bit a                                                                                            | addressable |             |            |              |         |           |     | -           |

| Symbol      | Function                                                                                                |             |             |            |              |         |           |     |             |

| CIDL        | Counter Id                                                                                              | lle Control | :           |            |              |         |           |     |             |

|             | 0: Progran                                                                                              |             |             |            |              | 0 0     | idle mode | e   |             |

|             | 1: Progran                                                                                              | ns the PC   | A Counter   | to be gate | ed off durir | ng idle |           |     |             |

| WDTE        | Watchdog                                                                                                |             |             |            |              |         |           |     |             |

|             | 0: Disable                                                                                              |             | •           |            |              |         |           |     |             |

|             | 1: Enables                                                                                              |             | •           |            |              | ule 4   |           |     |             |

| -           | Not implemented, reserved for future use.                                                               |             |             |            |              |         |           |     |             |

|             | Note: User should not write '1's to reserved bits. The value read from a reserved bit is indeterminate. |             |             |            |              |         |           |     |             |

| CPS1        | PCA Cour                                                                                                | nt Pulse Se | elect bit 1 |            |              |         |           |     |             |

| CPS0        | PCA Cour                                                                                                | nt Pulse Se | elect bit 2 |            |              |         |           |     |             |

|             |                                                                                                         |             |             |            |              |         |           |     |             |

| CPS1 | CPS0 | Selected<br>PCA Input <sup>1</sup> |                                                                                             |

|------|------|------------------------------------|---------------------------------------------------------------------------------------------|

| 0    | 0    | 0                                  | Internal clock, f <sub>OSC</sub> /6 in 6 clock mode (f <sub>OSC</sub> /12 in 12 clock mode) |

| 0    | 1    | 1                                  | Internal clock, $f_{OSC}/2$ in 6 clock mode ( $f_{OSC}/4$ in 12 clock mode)                 |

| 1    | 0    | 2                                  | Timer 0 overflow                                                                            |

| 1    | 1    | 3                                  | External clock at ECI/P1.2 pin                                                              |

|      |      |                                    | (max. rate = $f_{OSC}/4$ in 6 clock mode, $f_{OSC}/8$ in 12 clock mode)                     |

1. f<sub>OSC</sub> = oscillator frequency

ECF PCA Enable Counter Overflow interrupt:

0: Disables the CF bit in CCON

1: Enables CF bit in CCON to generate an interrupt

### Data Sheet

| Location | 7                                                                                                                                                                               | 6                                                                                                                                                      | 5                        | 4                        | 3                        | 2          | 1           | 0           | Reset Value |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|------------|-------------|-------------|-------------|

| D5H      | SPIE                                                                                                                                                                            | SPE                                                                                                                                                    | DORD                     | MSTR                     | CPOL                     | CPHA       | SPR1        | SPR0        | 00H         |

| Symbol   | Function                                                                                                                                                                        |                                                                                                                                                        |                          |                          |                          |            |             |             |             |

| SPIE     | If both SPI                                                                                                                                                                     | E and ES                                                                                                                                               | are set to               | one, SPI                 | interrupts               | are enable | ed.         |             |             |

| -        | SPI enable<br>0: Disables<br>1: Enables                                                                                                                                         | SPI.                                                                                                                                                   | onnects SS               | S#, MOSI, N              | VISO, and                | SCK to pin | ns P1.4, P1 | .5, P1.6, F | P1.7.       |

| DORD     | Data Trans<br>0: MSB firs                                                                                                                                                       | I: Enables SPI and connects SS#, MOSI, MISO, and SCK to pins P1.4, P1.5, P1.6, P1.7.<br>Data Transmission Order.<br>D: MSB first in data transmission. |                          |                          |                          |            |             |             |             |

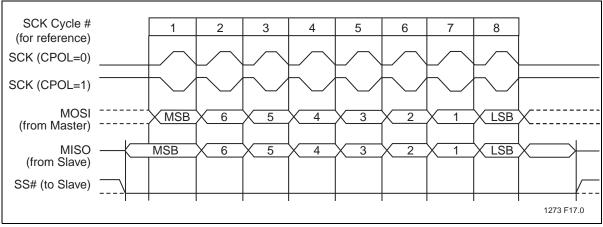

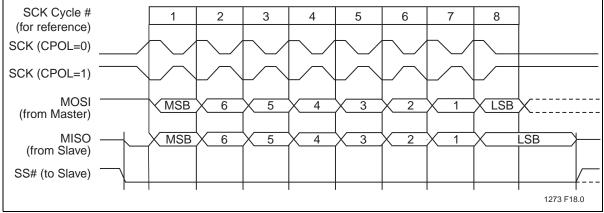

|          | Master/Slave select.<br>0: Selects Slave mode.<br>1: Selects Master mode.<br>Clock Polarity<br>0: SCK is low when idle (Active High).<br>1: SCK is high when idle (Active Low). |                                                                                                                                                        |                          |                          |                          |            |             |             |             |

|          |                                                                                                                                                                                 |                                                                                                                                                        |                          |                          |                          |            |             |             |             |

|          | Clock Pha<br>relationshi<br>0: Shift trig<br>1: Shift trig                                                                                                                      | p betweer<br>Igered on                                                                                                                                 | n master a<br>the leadin | nd slave. S<br>g edge of | See Figure<br>the clock. |            |             | ock and c   | lata        |

SPR1, SPR0SPI Clock Rate Select bits. These two bits control the SCK rate of the device configured as master. SPR1 and SPR0 have no effect on the slave. The relationship between SCK and the oscillator frequency, f<sub>OSC</sub>, is as follows:

| SPR1 | SPR0 | SCK = f <sub>OSC</sub> divided by |

|------|------|-----------------------------------|

| 0    | 0    | 4                                 |

| 0    | 1    | 16                                |

| 1    | 0    | 64                                |

| 1    | 1    | 128                               |

#### SPI Status Register (SPSR)

| Location | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 | Reset Value |

|----------|------|------|---|---|---|---|---|---|-------------|

| AAH      | SPIF | WCOL | - | - | - | - | - | - | 00xxxxxxb   |

#### Symbol Function

| SPIF | SPI Interrupt Flag.<br>Upon completion of data transfer, this bit is set to 1.<br>If SPIE =1 and ES =1, an interrupt is then generated.<br>This bit is cleared by software. |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WCOL | Write Collision Flag.<br>Set if the SPI data register is written to during data transfer.<br>This bit is cleared by software.                                               |

#### Data Sheet

Block 1, then the target address is implicitly defined to be in Block 0. If the IAP operation originates from external program space, then, the target will depend on the address and the state of bank selection.

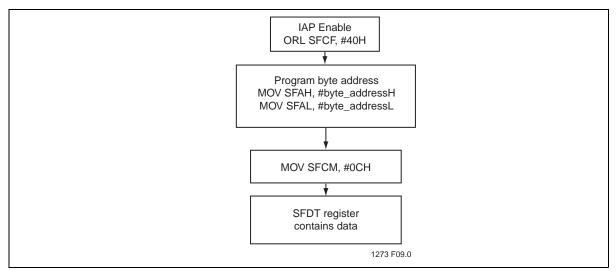

### IAP Enable Bit

The IAP enable bit, SFCF[6], enables in-application programming mode. Until this bit is set, all flash programming IAP commands will be ignored.

| EA# | SFCF[1:0]  | Address of IAP Inst. | Target Address     | Block Being<br>Programmed |

|-----|------------|----------------------|--------------------|---------------------------|

| 1   | 00         | >= 2000H (Block 0)   | >= 2000H (Block 0) | None <sup>1</sup>         |

| 1   | 00         | >= 2000H (Block 0)   | < 2000H (Block 1)  | Block 1                   |

| 1   | 00         | < 2000H (Block 1)    | Any (Block 0)      | Block 0                   |

| 1   | 01, 10, 11 | Any (Block 0)        | >= 2000H (Block 0) | None <sup>1</sup>         |

| 1   | 01, 10, 11 | Any (Block 0)        | < 2000H (Block 1)  | Block 1                   |

| 0   | 00         | From external        | >= 2000H (Block 0) | Block 0                   |

| 0   | 00         | From external        | < 2000H (Block 1)  | Block 1                   |

| 0   | 01, 10, 11 | From external        | Any (Block 0)      | Block 0                   |

#### Table 13: IAP Address Resolution

1. No operation is performed because code from one block may not program the same originating block

T0-0.0 25093

### In-Application Programming Mode Commands

All of the following commands can only be initiated in the IAP mode. In all situations, writing the control byte to the SFCM register will initiate all of the operations. All commands will not be enabled if the security locks are enabled on the selected memory block.

The Program command is for programming new data into the memory array. The portion of the memory array to be programmed should be in the erased state, FFH. If the memory is not erased, it should first be erased with an appropriate Erase command. Warning: Do not attempt to write (program or erase) to a block that the code is currently fetching from. This will cause unpredictable program behavior and may corrupt program data.

Data Sheet

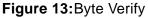

### Byte-Verify

The Byte-Verify command allows the user to verify that the device has correctly performed an Erase or Program command. Byte-Verify command returns the data byte in SFDT if the command is successful. The user is required to check that the previous flash operation has fully completed before issuing a Byte-Verify. Byte-Verify command execution time is short enough that there is no need to poll for command completion and no interrupt is generated.

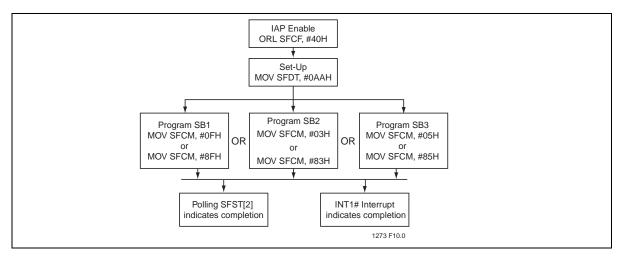

### Prog-SB3, Prog-SB2, Prog-SB1

Prog-SB3, Prog-SB2, Prog-SB1 commands are used to program the security bits (see Table 25). Completion of any of these commands, the security options will be updated immediately.

Security bits previously in un-programmed state can be programmed by these commands. Prog-SB3, Prog-SB2 and Prog-SB1 commands should only reside in Block 1 or external code memory.

### Figure 14: Prog-SB3, Prog-SB2, Prog-SB1

Data Sheet

### Polling

A command that uses the polling method to detect flash operation completion should poll on the FLASH\_BUSY bit (SFST[2]). When FLASH\_BUSY de-asserts (logic 0), the device is ready for the next operation.

MOVC instruction may also be used for verification of the Programming and Erase operation of the flash memory. MOVC instruction will fail if it is directed at a flash block that is still busy.

### Interrupt Termination

If interrupt termination is selected, (SFCM[7] is set), then an interrupt (INT1) will be generated to indicate flash operation completion. Under this condition, the INT1 becomes an internal interrupt source. The INT1# pin can now be used as a general purpose port pin and it cannot be the source of External Interrupt 1 during in-application programming.

In order to use an interrupt to signal flash operation termination. EX1 and EA bits of IE register must be set. The IT1 bit of TCON register must also be set for edge trigger detection.

| SFAH [7:0]      | SFAL [7:0]      |

|-----------------|-----------------|

| X4              | Х               |

| AH              | Х               |

| AH <sup>6</sup> | AL <sup>7</sup> |

| AH              | AL              |

| AH              | AL              |

| Х               | Х               |

| Х               | Х               |

| Х               | Х               |

| 5AH             | Х               |

| 55H             | Х               |

|                 | _               |

#### Table 14: IAP Commands<sup>1</sup>

1. SFCF[6]=1 enables IAP commands; SFCF[6]=0 disables IAP commands.

2. Interrupt/Polling enable for flash operation completion

SFCM[7] =1: Interrupt enable for flash operation completion 0: polling enable for flash operation completion

3. Chip-Erase only functions in IAP mode when EA#=0 (external memory execution) and device is not in level 4 locking.

4. X can be  $V_{IL}$  or  $V_{IH}$ , but no other value.

5. Refer to Table 13 for address resolution

6. AH = Address high order byte

7. AL = Address low order byte

8. DI = Data Input, DO = Data Output, all other values are in hex.

9. Instruction must be located in Block 1 or external code memory.

Note: DISIAPL pin in PLCC or TQFP will also disable IAP commands if it is externally pulled low when reset.

Data Sheet

# **Timers/Counters**

### Timers

The device has three 16-bit registers that can be used as either timers or event counters. The three timers/counters are denoted Timer 0 (T0), Timer 1 (T1), and Timer 2 (T2). Each is designated a pair of 8-bit registers in the SFRs. The pair consists of a most significant (high) byte and least significant (low) byte. The respective registers are TL0, TH0, TL1, TH1, TL2, and TH2.

### **Timer Set-up**

Refer to Table 9 for TMOD, TCON, and T2CON registers regarding timers T0, T1, and T2. The following tables provide TMOD values to be used to set up Timers T0, T1, and T2.

Except for the baud rate generator mode, the values given for T2CON do not include the setting of the TR2 bit. Therefore, bit TR2 must be set separately to turn the timer on.

|               |      | ТМ                |                               | IOD                           |  |

|---------------|------|-------------------|-------------------------------|-------------------------------|--|

|               | Mode | Function          | Internal Control <sup>1</sup> | External Control <sup>2</sup> |  |

|               | 0    | 13-bit Timer      | 00H                           | 08H                           |  |

|               | 1    | 16-bit Timer      | 01H                           | 09H                           |  |

| Used as Timer | 2    | 8-bit Auto-Reload | 02H                           | 0AH                           |  |

|               | 3    | Two 8-bit Timers  | 03H                           | 0BH                           |  |

|               | 0    | 13-bit Timer      | 04H                           | 0CH                           |  |

| Used as       | 1    | 16-bit Timer      | 05H                           | 0DH                           |  |

| Counter       | 2    | 8-bit Auto-Reload | 06H                           | 0EH                           |  |

|               | 3    | Two 8-bit Timers  | 07H                           | 0FH                           |  |

|               |      |                   | •                             | T0-0.0 25093                  |  |

#### Table 15: Timer/Counter 0

1. The Timer is turned ON/OFF by setting/clearing bit TR0 in the software.

2. The Timer is turned ON/OFF by the 1 to 0 transition on INT0# (P3.2) when TR0 = 1 (hardware control).

#### Table 16: Timer/Counter 1

|               |      |                   | TMOD                          |                               |

|---------------|------|-------------------|-------------------------------|-------------------------------|

|               | Mode | Function          | Internal Control <sup>1</sup> | External Control <sup>2</sup> |

|               | 0    | 13-bit Timer      | 00H                           | 80H                           |

|               | 1    | 16-bit Timer      | 10H                           | 90H                           |

| Used as Timer | 2    | 8-bit Auto-Reload | 20H                           | A0H                           |

|               | 3    | Does not run      | 30H                           | B0H                           |

|               | 0    | 13-bit Timer      | 40H                           | СОН                           |

| Used as       | 1    | 16-bit Timer      | 50H                           | D0H                           |

| Counter       | 2    | 8-bit Auto-Reload | 60H                           | E0H                           |

|               | 3    | Not available     | -                             | -                             |

1. The Timer is turned ON/OFF by setting/clearing bit TR1 in the software.

2. The Timer is turned ON/OFF by the 1 to 0 transition on INT1# (P3.3) when TR1 = 1 (hardware control).

Data Sheet

### **SPI Transfer Formats**

Figure 21:SPI Transfer Format with CPHA = 0

Figure 22:SPI Transfer Format with CPHA = 1

Data Sheet

# **Security Lock**

The security lock protects against software piracy and prevents the contents of the flash from being read by unauthorized parties. It also protects against code corruption resulting from accidental erasing and programming to the internal flash memory. There are two different types of security locks in the device security lock system: hard lock and SoftLock.

# Hard Lock

When hard lock is activated, MOVC or IAP instructions executed from an unlocked or soft locked program address space, are disabled from reading code bytes in hard locked memory blocks (See Table 26). Hard lock can either lock both flash memory blocks or just lock the 8 KByte flash memory block (Block 1). All external host and IAP commands except for Chip-Erase are ignored for memory blocks that are hard locked.

### SoftLock

SoftLock allows flash contents to be altered under a secure environment. This lock option allows the user to update program code in the soft locked memory block through in-application programming mode under a predetermined secure environment. For example, if Block 1 (8K) memory block is locked (hard locked or soft locked), and Block 0 memory block is soft locked, code residing in Block 1 can program Block 0. The following IAP mode commands issued through the command mailbox register, SFCM, executed from a Locked (hard locked or soft locked) block, can be operated on a soft locked block: Block-Erase, Sector-Erase, Byte-Program and Byte-Verify.

In external host mode, SoftLock behaves the same as a hard lock.

### Security Lock Status

The three bits that indicate the device security lock status are located in SFST[7:5]. As shown in Figure 30 and Table 25, the three security lock bits control the lock status of the primary and secondary blocks of memory. There are four distinct levels of security lock status. In the first level, none of the security lock bits are programmed and both blocks are unlocked. In the second level, although both blocks are now locked and cannot be programmed, they are available for read operation via Byte-Verify. In the third level, three different options are available: Block 1 hard lock / Block 0 SoftLock, SoftLock on both blocks, and hard lock on both blocks. Locking both blocks is the same as Level 2, Block 1 except read operation isn't available. The fourth level of security is the most secure level. It doesn't allow read/program of internal memory or boot from external memory. For details on how to program the security lock bits refer to the external host mode and in-application programming sections.

Data Sheet

### Software Reset

The software reset is executed by changing SFCF[1] (SWR) from "0" to "1". A software reset will reset the program counter to address 0000H. All SFR registers will be set to their reset values, except SFCF[1] (SWR), WDTC[2] (WDTS), and RAM data will not be altered.

### **Brown-out Detection Reset**

The device includes a brown-out detection circuit to protect the system from severed supplied voltage  $V_{DD}$  fluctuations. SST89E516RDx internal brown-out detection threshold is 3.85V, SST89V516RDx brown-out detection threshold is 2.35V. For brown-out voltage parameters, please refer to Table 36.

When  $V_{DD}$  drops below this voltage threshold, the brown-out detector triggers the circuit to generate a brown-out interrupt but the CPU still runs until the supplied voltage returns to the brown-out detection voltage  $V_{BOD}$ . The default operation for a brown-out detection is to cause a processor reset.

$V_{\text{DD}}$  must stay below  $V_{\text{BOD}}$  at least four oscillator clock periods before the brown-out detection circuit will respond.

Brown-out interrupt can be enabled by setting the EBO bit in IEA register (address E8H, bit 3). If EBO bit is set and a brown-out condition occurs, a brown-out interrupt will be generated to execute the program at location 004BH. It is required that the EBO bit be cleared by software after the brown-out interrupt is serviced. Clearing EBO bit when the brown-out condition is active will properly reset the device. If brown-out interrupt is not enabled, a brown-out condition will reset the program to resume execution at location 0000H.

Data Sheet

| Mode               | Initiated by                                         | State of MCU                                                                                                                                                                                                             | Exited by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Idle Mode          | Software<br>(Set IDL bit in PCON)<br>MOV PCON, #01H; | CLK is running.<br>Interrupts, serial port and<br>timers/counters are active.<br>Program Counter is<br>stopped. ALE and PSEN#<br>signals at a HIGH level<br>during Idle. All registers<br>remain unchanged.              | Enabled interrupt or hardware<br>reset. Start of interrupt clears IDL<br>bit and exits idle mode, after the<br>ISR RETI instruction, program<br>resumes execution beginning at<br>the instruction following the one<br>that invoked idle mode. A user<br>could consider placing two or three<br>NOP instructions after the instruc-<br>tion that invokes idle mode to elim-<br>inate any problems. A hardware<br>reset restarts the device similar to<br>a power-on reset.                                               |

| Power-down<br>Mode | Software<br>(Set PD bit in PCON)<br>MOV PCON, #02H;  | CLK is stopped. On-chip<br>SRAM and SFR data is<br>maintained. ALE and<br>PSEN# signals at a LOW<br>level during power -down.<br>External Interrupts are<br>only active for level sensi-<br>tive interrupts, if enabled. | Enabled external level sensitive<br>interrupt or hardware reset. Start<br>of interrupt clears PD bit and exits<br>power-down mode, after the ISR<br>RETI instruction program resumes<br>execution beginning at the instruc-<br>tion following the one that invoked<br>power-down mode. A user could<br>consider placing two or three NOP<br>instructions after the instruction<br>that invokes power-down mode to<br>eliminate any problems. A hard-<br>ware reset restarts the device sim-<br>ilar to a power-on reset. |

### Table 28: Power Saving Modes

Data Sheet

# **Electrical Specification**

**Absolute Maximum Stress Ratings** (Applied conditions greater than those listed under "Absolute Maximum Stress Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions or conditions greater than those defined in the operational sections of this data sheet is not implied. Exposure to absolute maximum stress rating conditions may affect device reliability.)

| Ambient Temperature Under Bias                                               |                               |

|------------------------------------------------------------------------------|-------------------------------|

| Storage Temperature                                                          | 65°C to +150°C                |

| Voltage on EA# Pin to V <sub>SS</sub>                                        | 0.5V to +14.0V                |

| D.C. Voltage on Any Pin to Ground Potential                                  | 0.5V to V <sub>DD</sub> +0.5V |

| Transient Voltage (<20ns) on Any Other Pin to V <sub>SS</sub>                | 1.0V to V <sub>DD</sub> +1.0V |

| Maximum I <sub>OL</sub> per I/O Pins P1.5, P1.6, P1.7                        | 20mA                          |

| Maximum I <sub>OL</sub> per I/O for All Other Pins                           | 15mA                          |

| Package Power Dissipation Capability $(T_A = 25^{\circ}C) \dots \dots \dots$ | 1.5W                          |

| Through Hole Lead Soldering Temperature (10 Seconds)                         |                               |

| Surface Mount Solder Reflow Temperature <sup>1</sup>                         | 260°C for 10 seconds          |

| Output Short Circuit Current <sup>2</sup>                                    | 50 mA                         |

- 1. Excluding certain with-Pb 32-PLCC units, all packages are 260°C capable in both non-Pb and with-Pb solder versions. Certain with-Pb 32-PLCC package types are capable of 240°C for 10 seconds; please consult the factory for the latest information.

- 2. Outputs shorted for no more than one second. No more than one output shorted at a time.

- (Based on package heat transfer limitations, not device power consumption.

- **Note:** This specification contains preliminary information on new products in production. The specifications are subject to change without notice.

| Symbol           | Description                    | Min. | Max | Unit |

|------------------|--------------------------------|------|-----|------|

| T <sub>A</sub>   | Ambient Temperature Under Bias |      |     |      |

|                  | Standard                       | 0    | +70 | °C   |

|                  | Industrial                     | -40  | +85 | °C   |

| V <sub>DD</sub>  | Supply Voltage                 |      |     |      |

|                  | SST89E516RDx                   | 4.5  | 5.5 | V    |

|                  | SST89V516RDx                   | 2.7  | 3.6 | V    |

| f <sub>OSC</sub> | Oscillator Frequency           |      |     |      |

|                  | SST89E516RDx                   | 0    | 40  | MHz  |

|                  | SST89V516RDx                   | 0    | 33  | MHz  |

|                  | Oscillator Frequency for IAP   |      |     |      |

|                  | SST89E516RDx                   | .25  | 40  | MHz  |

|                  | SST89V516RDx                   | .25  | 33  | MHz  |

### Table 31: Operating Range

Data Sheet

# **AC Electrical Characteristics**

### **AC Characteristics:**

(Over Operating Conditions: Load Capacitance for Port 0, ALE#, and PSEN# = 100pF; Load Capacitance for All Other Outputs = 80pF)

| Table 38: AC Electrical Characteristics (1 of 2)                                         |

|------------------------------------------------------------------------------------------|

| $T_A = -40^{\circ}C$ to +85°C, $V_{DD} = 2.7-3.6V@33MHz$ , 4.5-5.5V@40MHz, $V_{SS} = 0V$ |

|                      |                                   |                                                         | Oscillator |                                                         |     |                                                                    |                              |       |

|----------------------|-----------------------------------|---------------------------------------------------------|------------|---------------------------------------------------------|-----|--------------------------------------------------------------------|------------------------------|-------|

|                      |                                   | 33 MHz (x1<br>Mode)<br>16 MHz (x2<br>Mode) <sup>1</sup> |            | 40 MHz (x1<br>Mode)<br>20 MHz (x2<br>Mode) <sup>1</sup> |     | Variable                                                           |                              |       |

| Symbol               | Parameter                         | Min                                                     | Max        | Min                                                     | Max | Min                                                                | Max                          | Units |

| 1/T <sub>CLCL</sub>  | x1 Mode Oscillator Fre-<br>quency | 0                                                       | 33         | 0                                                       | 40  | 0                                                                  | 40                           | MHz   |

| 1/2T <sub>CLCL</sub> | x2 Mode Oscillator Fre-<br>quency | 0                                                       | 16         | 0                                                       | 20  | 0                                                                  | 20                           | MHz   |

| T <sub>LHLL</sub>    | ALE Pulse Width                   | 46                                                      |            | 35                                                      |     | 2T <sub>CLCL</sub> - 15                                            |                              | ns    |

| T <sub>AVLL</sub>    | Address Valid to ALE Low          | 5                                                       |            |                                                         |     | T <sub>CLCL</sub> - 25 (3V)                                        |                              | ns    |

|                      |                                   |                                                         |            | 10                                                      |     | T <sub>CLCL</sub> - 15 (5V)                                        |                              | ns    |

| T <sub>LLAX</sub>    | Address Hold After ALE<br>Low     | 5                                                       |            |                                                         |     | T <sub>CLCL</sub> - 25 (3V)                                        |                              | ns    |

|                      |                                   |                                                         |            | 10                                                      |     | T <sub>CLCL</sub> - 15 (5V)                                        |                              | ns    |

| T <sub>LLIV</sub>    | ALE Low to Valid Instr In         |                                                         | 56         |                                                         |     |                                                                    | 4T <sub>CLCL</sub> - 65 (3V) | ns    |

|                      |                                   |                                                         |            |                                                         | 55  |                                                                    | 4T <sub>CLCL</sub> - 45 (5V) | ns    |

| T <sub>LLPL</sub>    | ALE Low to PSEN# Low              | 5                                                       |            |                                                         |     | T <sub>CLCL</sub> - 25 (3V)                                        |                              | ns    |

|                      |                                   |                                                         |            | 10                                                      |     | T <sub>CLCL</sub> - 15 (5V)                                        |                              | ns    |

| T <sub>PLPH</sub>    | PSEN# Pulse Width                 | 66                                                      |            | 60                                                      |     | 3T <sub>CLCL</sub> - 25<br>(3V)<br>3T <sub>CLCL</sub> - 15<br>(5V) |                              | ns    |

| T <sub>PLIV</sub>    | PSEN# Low to Valid Instr<br>In    |                                                         | 35         |                                                         |     |                                                                    | 3T <sub>CLCL</sub> - 55 (3V) | ns    |

|                      |                                   |                                                         |            |                                                         | 25  |                                                                    | 3T <sub>CLCL</sub> - 50 (5V) | ns    |

| T <sub>PXIX</sub>    | Input Instr Hold After<br>PSEN#   |                                                         |            |                                                         |     | 0                                                                  |                              | ns    |

| T <sub>PXIZ</sub>    | Input Instr Float After<br>PSEN#  |                                                         | 25         |                                                         |     |                                                                    | T <sub>CLCL</sub> - 5 (3V)   | ns    |

|                      |                                   |                                                         |            |                                                         | 10  |                                                                    | T <sub>CLCL</sub> - 15 (5V)  | ns    |

| T <sub>PXAV</sub>    | PSEN# to Address valid            | 22                                                      |            | 17                                                      |     | T <sub>CLCL</sub> - 8                                              |                              | ns    |

| T <sub>AVIV</sub>    | Address to Valid Instr In         |                                                         | 72         |                                                         |     |                                                                    | 5T <sub>CLCL</sub> - 80 (3V) | ns    |

|                      |                                   |                                                         |            |                                                         | 65  |                                                                    | 5T <sub>CLCL</sub> - 60 (5V) | ns    |

| T <sub>PLAZ</sub>    | PSEN# Low to Address<br>Float     |                                                         | 10         |                                                         | 10  |                                                                    | 10                           | ns    |

| T <sub>RLRH</sub>    | RD# Pulse Width                   | 142                                                     |            | 120                                                     |     | 6T <sub>CLCL</sub> - 40 (3V)<br>6T <sub>CLCL</sub> - 30 (5V)       |                              | ns    |

| T <sub>WLWH</sub>    | Write Pulse Width (WE#)           | 142                                                     |            | 120                                                     |     | 6T <sub>CLCL</sub> - 40 (3V)<br>6T <sub>CLCL</sub> - 30 (5V)       |                              | ns    |

| T <sub>RLDV</sub>    | RD# Low to Valid Data In          |                                                         | 62         |                                                         |     |                                                                    | 5T <sub>CLCL</sub> - 90 (3V) | ns    |

Data Sheet

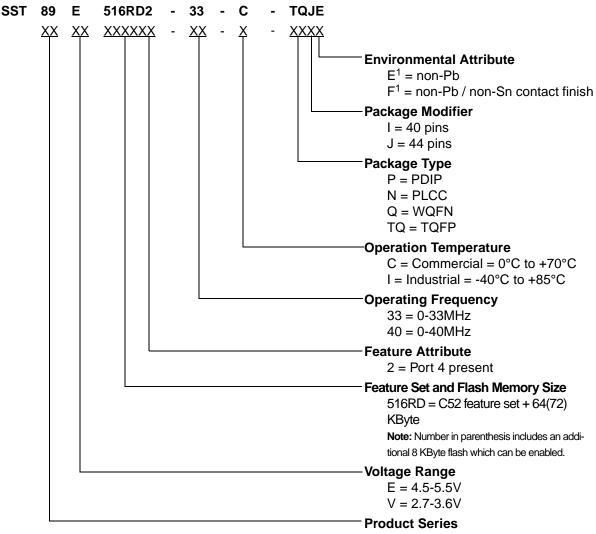

# **Product Ordering Information**

89 = C51 Core

1. Environmental suffix "E" denotes non-Pb solder. Environmental suffix "F" denote non-Pb /non-Sn solder. SST non-Pb / non-Sn solder devices are "RoHS Compliant".

Data Sheet

## Valid Combinations

### Valid combinations for SST89E516RD2

SST89E516RD2-40-C-NJE SST89E516RD2-40-C-TQJE

SST89E516RD2-40-I-NJE SST89E516RD2-40-I-TQJE

### Valid combinations for SST89V516RD2

SST89V516RD2-33-C-NJE SST89V516RD2-33-C-TQJE

SST89V516RD2-33-I-NJE SST89V516RD2-33-I-TQJE

### Valid combinations for SST89E516RD

SST89E516RD-40-C-PIE

SST89E516RD-40-C-QIF SST89E516RD-40-I-QIF

### Valid combinations for SST89V516RD

SST89V516RD-33-C-PIE

SST89V516RD-33-C-QIF SST89V516RD-33-I-QIF

**Note:** Valid combinations are those products in mass production or will be in mass production. Consult your SST sales representative to confirm availability of valid combinations and to determine availability of new combinations.

Data Sheet

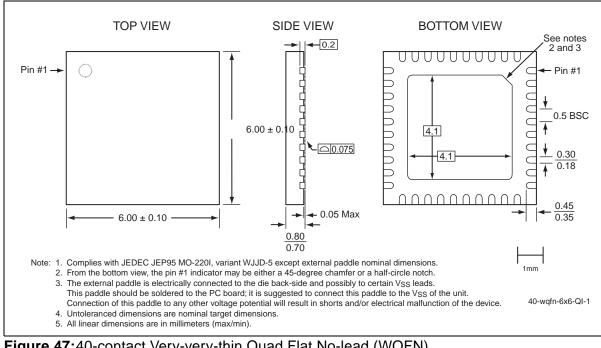

# **Packaging Diagrams**

Figure 47:40-contact Very-very-thin Quad Flat No-lead (WQFN) SST Package Code: QI