#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                     |

|----------------------------|-------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                            |

| Core Processor             | 8051                                                                                |

| Core Size                  | 8-Bit                                                                               |

| Speed                      | 33MHz                                                                               |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                    |

| Number of I/O              | 36                                                                                  |

| Program Memory Size        | 72KB (72K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 1K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                         |

| Data Converters            | -                                                                                   |

| Oscillator Type            | External                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 44-LCC (J-Lead)                                                                     |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89v516rd2-33-i-nje-nxx |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Data Sheet

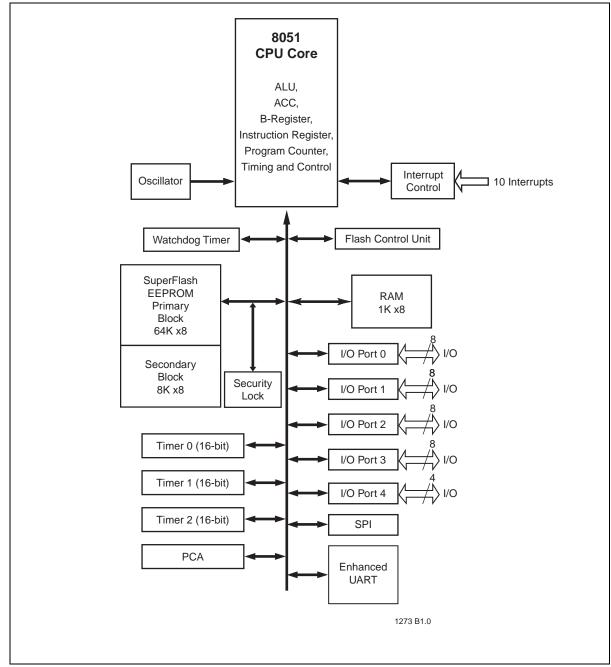

## **Functional Blocks**

Figure 1: Functional Block Diagram

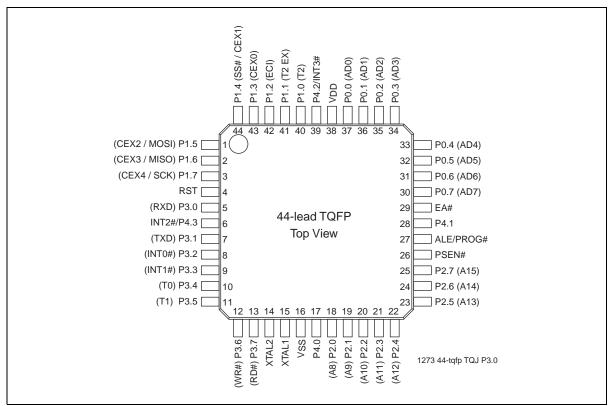

Figure 4: Pin Assignments for 44-lead TQFP

Data Sheet

| Symbol           | Description                           | Direct<br>Address | MSB       | Bit Addre | ss, Syrr | nbol, or | Alternat | ive Port | Function   | LSB      | Reset<br>Value |

|------------------|---------------------------------------|-------------------|-----------|-----------|----------|----------|----------|----------|------------|----------|----------------|

| ACC <sup>1</sup> | Accumulator                           | E0H               |           |           |          | AC       | C[7:0]   |          |            |          | 00H            |

| B <sup>1</sup>   | B Register                            | F0H               |           |           |          | B[       | 7:0]     |          |            |          | 00H            |

| PSW <sup>1</sup> | Program Sta-<br>tus<br>Word           | D0H               | CY        | AC        | F0       | RS<br>1  | RS0      | OV       | F1         | Р        | 00H            |

| SP               | Stack Pointer                         | 81H               |           |           |          | SP       | [7:0]    |          |            | •        | 07H            |

| DPL              | Data Pointer<br>Low                   | 82H               |           |           |          | DPI      | L[7:0]   |          |            |          | 00H            |

| DPH              | Data Pointer<br>High                  | 83H               |           |           |          | DPI      | H[7:0]   |          |            |          | 00H            |

| IE <sup>1</sup>  | Interrupt<br>Enable                   | A8H               | EA        | EC        | ET2      | ES       | ET1      | EX1      | ET0        | EX0      | 00H            |

| IEA <sup>1</sup> | Interrupt<br>Enable A                 | E8H               | -         | -         | -        | -        | EBO      | -        | -          | -        | xxxx0xxx<br>b  |

| IP <sup>1</sup>  | Interrupt Prior-<br>ity<br>Reg        | B8H               | -         | PPC       | PT2      | PS       | PT1      | PX1      | PT0        | PX0      | x0000000<br>b  |

| IPH              | Interrupt Prior-<br>ity<br>Reg High   | B7H               | -         | PPCH      | PT2<br>H | PS<br>H  | PT1H     | PX1<br>H | PT0H       | PX0<br>H | x0000000<br>b  |

| IP1 <sup>1</sup> | Interrupt Prior-<br>ity<br>Reg A      | F8H               | -         | -         | -        | -        | РВО      | PX3      | PX2        | -        | xxxx0xxx<br>b  |

| IP1H             | Interrupt Prior-<br>ity<br>Reg A High | F7H               | -         | -         | -        | -        | PBO<br>H | PX3<br>H | PX2H       | -        | xxxx0xxx<br>b  |

| PCON             | Power Control                         | 87H               | SMOD<br>1 | SMOD<br>0 | BOF      | PO<br>F  | GF1      | GF0      | PD         | IDL      | 00010000<br>b  |

| AUXR             | Auxiliary Reg                         | 8EH               | -         | -         | -        | -        | -        | -        | EXTRA<br>M | AO       | xxxxxxx0<br>0b |

| AUXR1            | Auxiliary Reg<br>1                    | A2H               | -         | -         | -        | -        | GF2      | 0        | -          | DPS      | xxxx00x0<br>b  |

| XICON            | External<br>Interrupt Con-<br>trol    | AEH               | -         | EX3       | IE3      | IT3      | 0        | EX2      | IE2        | IT2      | 00H            |

1. Bit Addressable SFRs

Data Sheet

|                   |                                   | Direct  | Bit Add  | dress, Sy   | ymbol, o | r Alterna | ative Port | Functio  | n         |             | Reset         |

|-------------------|-----------------------------------|---------|----------|-------------|----------|-----------|------------|----------|-----------|-------------|---------------|

| Symbol            | Description                       | Address | MSB      |             |          |           |            |          |           | LSB         | Value         |

| TMOD              | Timer/Counter                     | 89H     |          | Tim         | er 1     |           |            | Tii      | mer 0     |             | 00H           |

|                   | Mode Control                      |         | GAT<br>E | C/T#        | M1       | M0        | GATE       | C/<br>T# | M1        | MO          |               |

| TCON <sup>1</sup> | Timer/Counter<br>Control          | 88H     | TF1      | TR1         | TF0      | TR0       | IE1        | IT1      | IE0       | IT0         | 00H           |

| TH0               | Timer 0 MSB                       | 8CH     |          |             |          | Tł        | H0[7:0]    |          |           |             | 00H           |

| TL0               | Timer 0 LSB                       | 8AH     |          | TL0[7:0]    |          |           |            |          | 00H       |             |               |

| TH1               | Timer 1 MSB                       | 8DH     |          | TH1[7:0]    |          |           |            |          | 00H       |             |               |

| TL1               | Timer 1 LSB                       | 8BH     |          | TL1[7:0]    |          |           |            |          | 00H       |             |               |

| T2CON<br>1        | Timer / Coun-<br>ter 2<br>Control | C8H     | TF2      | EXF<br>2    | RCL<br>K | TCL<br>K  | EXEN<br>2  | TR2      | C/<br>T2# | CP/<br>RL2# | 00H           |

| T2MOD             | Timer2<br>Mode Control            | C9H     | -        | -           | -        | -         | -          | -        | T2O<br>E  | DCEN        | xxxxxx00<br>b |

| TH2               | Timer 2 MSB                       | CDH     |          |             |          | Tł        | H2[7:0]    |          |           |             | 00H           |

| TL2               | Timer 2 LSB                       | ССН     |          | TL2[7:0]    |          |           |            |          | 00H       |             |               |

| RCAP2<br>H        | Timer 2<br>Capture MSB            | CBH     |          | RCAP2H[7:0] |          |           |            | 00H      |           |             |               |

| RCAP2<br>L        | Timer 2<br>Capture LSB            | CAH     |          |             |          | RCA       | AP2L[7:0]  |          |           |             | 00H           |

#### Table 9: Timer/Counters SFRs

1. Bit Addressable SFRs

Data Sheet

### Table 10: Interface SFRs

|                 |                          | Direct  | Bit Addr   | ess, Syn   | nbol, or A | Iternativ | /e Port F | unction   | 1        |          | RESET              |

|-----------------|--------------------------|---------|------------|------------|------------|-----------|-----------|-----------|----------|----------|--------------------|

| Symbol          | Description              | Address | MSB        |            |            |           |           |           |          | LSB      | Value              |

| SBUF            | Serial Data Buf-<br>fer  | 99H     |            |            |            | SBUF[     | 7:0]      |           |          |          | Indetermi-<br>nate |

| SCON<br>1       | Serial Port Con-<br>trol | 98H     | SM0/<br>FE | SM1        | SM2        | REN       | TB8       | RB8       | ΤI       | RI       | 00H                |

| SADD<br>R       | Slave Address            | A9H     |            | SADDR[7:0] |            |           |           |           | 00H      |          |                    |

| SADE<br>N       | Slave Address<br>Mask    | B9H     |            | SADEN[7:0] |            |           |           | 00H       |          |          |                    |

| SPCR            | SPI Control<br>Register  | D5H     | SPIE       | SPE        | DOR<br>D   | MST<br>R  | CPO<br>L  | CPH<br>A  | SPR<br>1 | SPR<br>0 | 04H                |

| SPSR            | SPI Status<br>Register   | AAH     | SPIF       | WCO<br>L   |            |           |           |           |          |          | 00H                |

| SPDR            | SPI Data Regis-<br>ter   | 86H     |            |            |            | SPDR[     | 7:0]      |           |          |          | 00H                |

| P0 <sup>1</sup> | Port 0                   | 80H     |            |            |            | P0[7:     | 0]        |           |          |          | FFH                |

| P1 <sup>1</sup> | Port 1                   | 90H     | -          | -          | -          | -         | -         | -         | T2E<br>X | T2       | FFH                |

| P2 <sup>1</sup> | Port 2                   | A0H     |            | P2[7:0]    |            |           |           | FFH       |          |          |                    |

| P3 <sup>1</sup> | Port 3                   | B0H     | RD#        | WR#        | T1         | Т0        | INT1<br># | INT0<br># | TXD      | RXD      | FFH                |

| P4 <sup>2</sup> | Port 4                   | A5H     | 1          | 1          | 1          | 1         | P4.3      | P4.2      | P4.1     | P4.0     | FFH                |

|                 |                          | •       |            | •          |            |           |           | •         |          |          | T0-0.0 25093       |

1. Bit Addressable SFRs

2. P4 is similar to P1 and P3 ports

#### SuperFlash Address Registers (SFAH) **Reset Value** Location 7 6 5 4 3 2 1 0 B4H SuperFlash High Order Byte Address Register 00H Symbol Function SFAH Mailbox register for interfacing with flash memory block. (High order address register). SuperFlash Data Register (SFDT) Location

| Location | 7 | 6 | 5 | 4           | 3           | 2  | 1 | 0 | Reset Value |

|----------|---|---|---|-------------|-------------|----|---|---|-------------|

| B5H      |   |   | S | uperFlash [ | Data Regist | er |   |   | 00H         |

#### Symbol Function

SFDT Mailbox register for interfacing with flash memory block. (Data register).

#### SuperFlash Status Register (SFST) (Read Only Register)

| Location | 7     | 6     | 5     | 4 | 3     | 2              | 1 | 0 | Reset Value |

|----------|-------|-------|-------|---|-------|----------------|---|---|-------------|

| B6H      | SB1_i | SB2_i | SB3_i | - | EDC_i | FLASH_BU<br>SY | - | - | xxxxx0xxb   |

### Symbol Function

| SB1_i | Security Bit 1 statu | us (inverse of SB1 bit) |

|-------|----------------------|-------------------------|

|-------|----------------------|-------------------------|

- SB2\_i Security Bit 2 status (inverse of SB2 bit)

- SB3\_i Security Bit 3 status (inverse of SB3 bit) Please refer to Table 25 for security lock options.

### EDC\_i Double Clock Status

- 0: 12 clocks per machine cycle

- 1: 6 clocks per machine cycle

#### FLASH\_BUSYFlash operation completion polling bit.

- 0: Device has fully completed the last IAP command.

- 1: Device is busy with flash operation.

Data Sheet

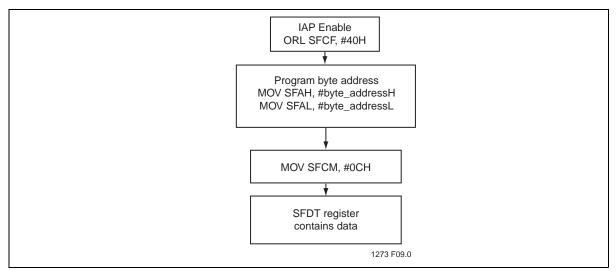

### Byte-Verify

The Byte-Verify command allows the user to verify that the device has correctly performed an Erase or Program command. Byte-Verify command returns the data byte in SFDT if the command is successful. The user is required to check that the previous flash operation has fully completed before issuing a Byte-Verify. Byte-Verify command execution time is short enough that there is no need to poll for command completion and no interrupt is generated.

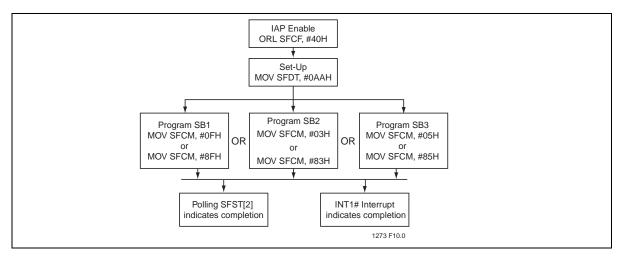

### Prog-SB3, Prog-SB2, Prog-SB1

Prog-SB3, Prog-SB2, Prog-SB1 commands are used to program the security bits (see Table 25). Completion of any of these commands, the security options will be updated immediately.

Security bits previously in un-programmed state can be programmed by these commands. Prog-SB3, Prog-SB2 and Prog-SB1 commands should only reside in Block 1 or external code memory.

### Figure 14: Prog-SB3, Prog-SB2, Prog-SB1

Data Sheet

### **Timers/Counters**

### Timers

The device has three 16-bit registers that can be used as either timers or event counters. The three timers/counters are denoted Timer 0 (T0), Timer 1 (T1), and Timer 2 (T2). Each is designated a pair of 8-bit registers in the SFRs. The pair consists of a most significant (high) byte and least significant (low) byte. The respective registers are TL0, TH0, TL1, TH1, TL2, and TH2.

### **Timer Set-up**

Refer to Table 9 for TMOD, TCON, and T2CON registers regarding timers T0, T1, and T2. The following tables provide TMOD values to be used to set up Timers T0, T1, and T2.

Except for the baud rate generator mode, the values given for T2CON do not include the setting of the TR2 bit. Therefore, bit TR2 must be set separately to turn the timer on.

|               |      |                   | TN                            | IOD                           |

|---------------|------|-------------------|-------------------------------|-------------------------------|

|               | Mode | Function          | Internal Control <sup>1</sup> | External Control <sup>2</sup> |

|               | 0    | 13-bit Timer      | 00H                           | 08H                           |

| Used as Timer | 1    | 16-bit Timer      | 01H                           | 09H                           |

| Used as Timer | 2    | 8-bit Auto-Reload | 02H                           | 0AH                           |

|               | 3    | Two 8-bit Timers  | 03H                           | 0BH                           |

|               | 0    | 13-bit Timer      | 04H                           | 0CH                           |

| Used as       | 1    | 16-bit Timer      | 05H                           | 0DH                           |

| Counter       | 2    | 8-bit Auto-Reload | 06H                           | 0EH                           |

|               | 3    | Two 8-bit Timers  | 07H                           | 0FH                           |

|               |      |                   | •                             | T0-0.0 25093                  |

#### Table 15: Timer/Counter 0

1. The Timer is turned ON/OFF by setting/clearing bit TR0 in the software.

2. The Timer is turned ON/OFF by the 1 to 0 transition on INT0# (P3.2) when TR0 = 1 (hardware control).

#### Table 16: Timer/Counter 1

|               |      |                   | TN                            | NOD                           |

|---------------|------|-------------------|-------------------------------|-------------------------------|

|               | Mode | Function          | Internal Control <sup>1</sup> | External Control <sup>2</sup> |

|               | 0    | 13-bit Timer      | 00H                           | 80H                           |

|               | 1    | 16-bit Timer      | 10H                           | 90H                           |

| Used as Timer | 2    | 8-bit Auto-Reload | 20H                           | A0H                           |

|               | 3    | Does not run      | 30H                           | B0H                           |

|               | 0    | 13-bit Timer      | 40H                           | СОН                           |

| Used as       | 1    | 16-bit Timer      | 50H                           | D0H                           |

| Counter       | 2    | 8-bit Auto-Reload | 60H                           | E0H                           |

|               | 3    | Not available     | -                             | -                             |

1. The Timer is turned ON/OFF by setting/clearing bit TR1 in the software.

2. The Timer is turned ON/OFF by the 1 to 0 transition on INT1# (P3.3) when TR1 = 1 (hardware control).

Data Sheet

### Serial I/O

### Full-Duplex, Enhanced UART

The device serial I/O port is a full-duplex port that allows data to be transmitted and received simultaneously in hardware by the transmit and receive registers, respectively, while the software is performing other tasks. The transmit and receive registers are both located in the Serial Data Buffer (SBUF) special function register. Writing to the SBUF register loads the transmit register, and reading from the SBUF register obtains the contents of the receive register.

The UART has four modes of operation which are selected by the Serial Port Mode Specifier (SM0 and SM1) bits of the Serial Port Control (SCON) special function register. In all four modes, transmission is initiated by any instruction that uses the SBUF register as a destination register. Reception is initiated in mode 0 when the Receive Interrupt (RI) flag bit of the Serial Port Control (SCON) SFR is cleared and the Reception Enable/ Disable (REN) bit of the SCON register is set. Reception is initiated in the other modes by the incoming start bit if the REN bit of the SCON register is set.

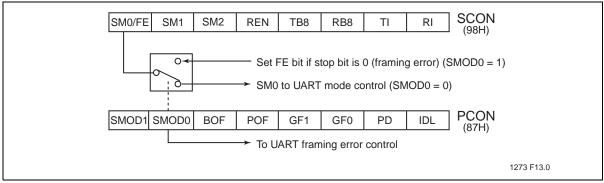

### **Framing Error Detection**

Framing Error Detection is a feature, which allows the receiving controller to check for valid stop bits in modes 1, 2, or 3. Missing stops bits can be caused by noise in serial lines or from simultaneous transmission by two CPUs.

Framing Error Detection is selected by going to the PCON register and changing SMOD0 = 1 (see Figure 17). If a stop bit is missing, the Framing Error bit (FE) will be set. Software may examine the FE bit after each reception to check for data errors. After the FE bit has been set, it can only be cleared by software. Valid stop bits do not clear FE. When FE is enabled, RI rises on the stop bit, instead of the last data bit (see Figure 18 and Figure 19).

Figure 17: Framing Error Block Diagram

Data Sheet

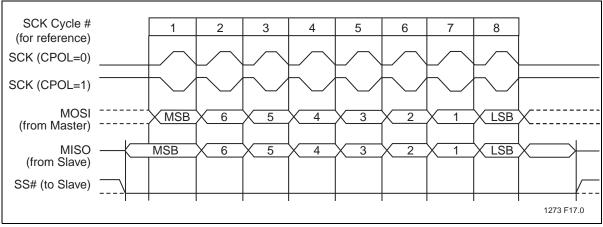

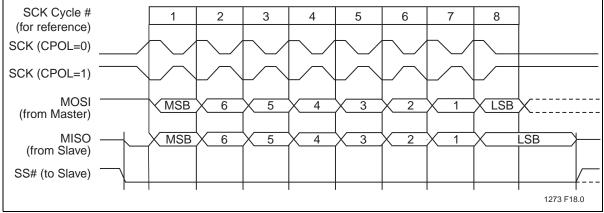

### **SPI Transfer Formats**

Figure 21:SPI Transfer Format with CPHA = 0

Figure 22:SPI Transfer Format with CPHA = 1

Data Sheet

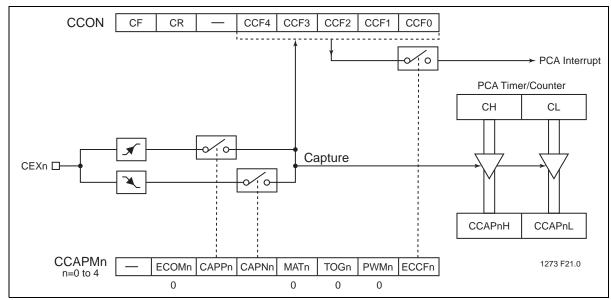

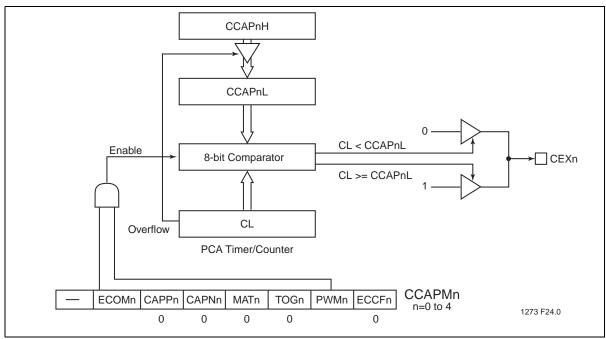

### **Capture Mode**

Capture mode is used to capture the PCA timer/counter value into a module's capture registers (CCAPnH and CCAPnL). The capture will occur on a positive edge, negative edge, or both on the corresponding module's pin. To use one of the PCA modules in the capture mode, either one or both the CCAPM bits CAPN and CAPP for that module must be set. When a valid transition occurs on the CEX pin corresponding to the module used, the PCA hardware loads the 16-bit value of the PCA counter register (CH and CL) into the module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set, then an interrupt will be generated. In the interrupt service routine, the 16-bit capture value must be saved in RAM before the next event capture occurs. If a subsequent capture occurred, the original capture values would be lost. After flag event flag has been set by hardware, the user must clear the flag in software. (See Figure 25)

Figure 25: PCA Capture Mode

Data Sheet

### Figure 28: PCA Pulse Width Modulator Mode

| Table 24: Pulse Width | n Modulator F | Frequencies |

|-----------------------|---------------|-------------|

|-----------------------|---------------|-------------|

|                           | PWM Frequency      |                    |  |  |  |  |

|---------------------------|--------------------|--------------------|--|--|--|--|

| PCA Timer Mode            | 12 MHz             | 16 MHz             |  |  |  |  |

| 1/12 Oscillator Frequency | 3.9 KHz            | 5.2 KHz            |  |  |  |  |

| 1/4 Oscillator Frequency  | 11.8 KHz           | 15.6 KHz           |  |  |  |  |

| Timer 0 Overflow:         |                    |                    |  |  |  |  |

| 8-bit                     | 15.5 Hz            | 20.3 Hz            |  |  |  |  |

| 16-bit                    | 0.06 Hz            | 0.08 Hz            |  |  |  |  |

| 8-bit Auto-Reload         | 3.9 KHz to 15.3 Hz | 5.2 KHz to 20.3 Hz |  |  |  |  |

| External Input (Max)      | 5.9 KHz            | 7.8 KHz            |  |  |  |  |

Data Sheet

T0-0.0 25093

### Table 26: Security Lock Access Table

|       |                  | Source               | Target               | Byte-Verify Allo           | MOVC Allowed |        |

|-------|------------------|----------------------|----------------------|----------------------------|--------------|--------|

| Level | SFST[7:5]        | Address <sup>1</sup> | Address <sup>2</sup> | External Host <sup>3</sup> | IAP          | 516RDx |

|       | 000b<br>(unlock) | Block 0              | Block 0              | Y                          | Ν            | Y      |

|       |                  |                      | Block 1              | Y                          | Y            | Y      |

|       |                  |                      | External             | N/A                        | N/A          | Ν      |

| 1     |                  | Block 1              | Block 0              | Y                          | Y            | Y      |

| I     |                  |                      | Block 1              | Y                          | Ν            | Y      |

|       |                  |                      | External             | N/A                        | N/A          | Ν      |

|       |                  | External             | Block 0/1            | Y                          | Y            | Ν      |

|       |                  |                      | External             | N/A                        | N/A          | Y      |

1. Location of MOVC or IAP instruction

2. Target address is the location of the byte being read

3. External host Byte-Verify access does not depend on a source address.

Data Sheet

| Mode               | Initiated by                                         | State of MCU                                                                                                                                                                                                             | Exited by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Idle Mode          | Software<br>(Set IDL bit in PCON)<br>MOV PCON, #01H; | CLK is running.<br>Interrupts, serial port and<br>timers/counters are active.<br>Program Counter is<br>stopped. ALE and PSEN#<br>signals at a HIGH level<br>during Idle. All registers<br>remain unchanged.              | Enabled interrupt or hardware<br>reset. Start of interrupt clears IDL<br>bit and exits idle mode, after the<br>ISR RETI instruction, program<br>resumes execution beginning at<br>the instruction following the one<br>that invoked idle mode. A user<br>could consider placing two or three<br>NOP instructions after the instruc-<br>tion that invokes idle mode to elim-<br>inate any problems. A hardware<br>reset restarts the device similar to<br>a power-on reset.                                               |

| Power-down<br>Mode | Software<br>(Set PD bit in PCON)<br>MOV PCON, #02H;  | CLK is stopped. On-chip<br>SRAM and SFR data is<br>maintained. ALE and<br>PSEN# signals at a LOW<br>level during power -down.<br>External Interrupts are<br>only active for level sensi-<br>tive interrupts, if enabled. | Enabled external level sensitive<br>interrupt or hardware reset. Start<br>of interrupt clears PD bit and exits<br>power-down mode, after the ISR<br>RETI instruction program resumes<br>execution beginning at the instruc-<br>tion following the one that invoked<br>power-down mode. A user could<br>consider placing two or three NOP<br>instructions after the instruction<br>that invokes power-down mode to<br>eliminate any problems. A hard-<br>ware reset restarts the device sim-<br>ilar to a power-on reset. |

### Table 28: Power Saving Modes

Data Sheet

## System Clock and Clock Options

### **Clock Input Options and Recommended Capacitor Values for Oscillator**

Shown in Figure 33 are the input and output of an internal inverting amplifier (XTAL1, XTAL2), which can be configured for use as an on-chip oscillator.

When driving the device from an external clock source, XTAL2 should be left disconnected and XTAL1 should be driven.

At start-up, the external oscillator may encounter a higher capacitive load at XTAL1 due to interaction between the amplifier and its feedback capacitance. However, the capacitance will not exceed 15 pF once the external signal meets the  $V_{IL}$  and  $V_{IH}$  specifications.

Crystal manufacturer, supply voltage, and other factors may cause circuit performance to differ from one application to another. C1 and C2 should be adjusted appropriately for each design. Table 29, shows the typical values for C1 and C2 vs. crystal type for various frequencies

#### Table 29: Recommended Values for C1 and C2 by Crystal Type

| Crystal | C1 = C2 |

|---------|---------|

| Quartz  | 20-30pF |

| Ceramic | 40-50pF |

T0-0.0 25093

More specific information about on-chip oscillator design can be found in the *FlashFlex Oscillator Circuit Design Considerations* application note.

### **Clock Doubling Option**

By default, the device runs at 12 clocks per machine cycle (x1 mode). The device has a clock doubling option to speed up to 6 clocks per machine cycle. Please refer to Table 30 for detail.

Clock double mode can be enabled either via the external host mode or the IAP mode. Please refer to Table 14 for the IAP mode enabling commands (When set, the EDC# bit in SFST register will indicate 6 clock mode.).

The clock double mode is only for doubling the internal system clock and the internal flash memory, i.e. EA#=1. To access the external memory and the peripheral devices, careful consideration must be taken. Also note that the crystal output (XTAL2) will not be doubled.

Data Sheet

### **Table 37:** DC Electrical Characteristics for SST89V516RDx $T_A = -40^{\circ}$ C to +85°C; $V_{DD} = 2.7-3.6$ V; $V_{SS} = 0$ V

| Symbo            | Denometer                                                         | Test Canditians                               | Min                         | Max                      | Unit |

|------------------|-------------------------------------------------------------------|-----------------------------------------------|-----------------------------|--------------------------|------|

| I                | Parameter                                                         | Test Conditions                               | Min                         | Max                      | S    |

| VIL              | Input Low Voltage                                                 | 2.7 < V <sub>DD</sub> < 3.6                   | -0.5                        | 0.7                      | V    |

| VIH              | Input High Voltage                                                | 2.7 < V <sub>DD</sub> < 3.6                   | 0.2V <sub>DD</sub> +<br>0.9 | V <sub>DD</sub> +<br>0.5 | V    |

| V <sub>IH1</sub> | Input High Voltage (XTAL1, RST)                                   | $2.7 < V_{DD} < 3.6$                          | $0.7V_{DD}$                 | V <sub>DD</sub> +<br>0.5 | V    |

| V <sub>OL</sub>  | Output Low Voltage (Ports 1.5, 1.6, 1.7)                          | V <sub>DD</sub> = 2.7V                        |                             |                          |      |

|                  |                                                                   | I <sub>OL</sub> = 16mA                        |                             | 1.0                      | V    |

| V <sub>OL</sub>  | Output Low Voltage (Ports 1, 2, 3) <sup>1</sup>                   | V <sub>DD</sub> = 2.7V                        |                             |                          |      |

|                  |                                                                   | $I_{OL} = 100 \mu A^2$                        |                             | 0.3                      | V    |

|                  |                                                                   | $I_{OL} = 1.6 \text{mA}^2$                    |                             | 0.45                     | V    |

|                  |                                                                   | $I_{OL} = 3.5 \text{mA}^2$                    |                             | 1.0                      | V    |

| V <sub>OL1</sub> | Output Low Voltage (Port 0, ALE, PSEN#) <sup>1,3</sup>            | V <sub>DD</sub> = 2.7V                        |                             |                          |      |

|                  |                                                                   | $I_{OL} = 200 \mu A^2$                        |                             | 0.3                      | V    |

|                  |                                                                   | $I_{OL} = 3.2 \text{mA}^2$                    |                             | 0.45                     | V    |

| Vон              | Output High Voltage (Ports 1, 2, 3, ALE,                          | V <sub>DD</sub> = 2.7V                        |                             |                          |      |

|                  | PSEN#) <sup>4</sup>                                               | I <sub>OH</sub> = -10μA                       | V <sub>DD</sub> - 0.3       |                          | V    |

|                  |                                                                   | I <sub>OH</sub> = -30μA                       | V <sub>DD</sub> - 0.7       |                          | V    |

|                  |                                                                   | I <sub>OH</sub> = -60μA                       | V <sub>DD</sub> - 1.5       |                          | V    |

| V <sub>OH1</sub> | Output High Voltage (Port 0 in External Bus                       | V <sub>DD</sub> = 2.7V                        |                             |                          |      |

|                  | Mode) <sup>4</sup>                                                | I <sub>OH</sub> = -200μA                      | V <sub>DD</sub> - 0.3       |                          | V    |

|                  | Dutput High Voltage (Port 0 in External Bus<br>Mode) <sup>4</sup> | I <sub>OH</sub> = -3.2mA                      | V <sub>DD</sub> - 0.7       |                          | V    |

| V <sub>BOD</sub> | Brown-out Detection Voltage                                       |                                               | 2.35                        | 2.55                     | V    |

| IIL              | Logical 0 Input Current (Ports 1, 2, 3)                           | $V_{IN} = 0.4V$                               |                             | -75                      | μA   |

| I <sub>TL</sub>  | Logical 1-to-0 Transition Current (Ports 1, 2, 3) <sup>5</sup>    | $V_{IN} = 2V$                                 |                             | -650                     | μA   |

| ILI              | Input Leakage Current (Port 0)                                    | $0.45 < V_{IN} < V_{DD}$ -0.3                 |                             | ±10                      | μA   |

| R <sub>RST</sub> | RST Pull-down Resistor                                            |                                               |                             | 225                      | KΩ   |

| C <sub>IO</sub>  | Pin Capacitance <sup>6</sup>                                      | @ 1 MHz, 25°C                                 |                             | 15                       | pF   |

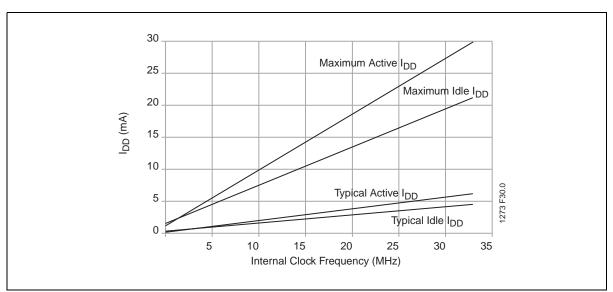

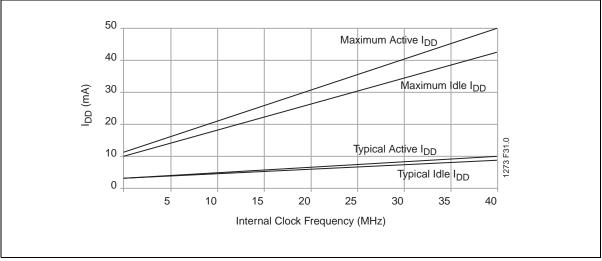

| I <sub>DD</sub>  | Power Supply Current                                              |                                               |                             |                          |      |

|                  | IAP Mode                                                          |                                               |                             |                          |      |

|                  | @ 33 MHz                                                          |                                               |                             | 47                       | mA   |

|                  | Active Mode                                                       |                                               |                             |                          |      |

|                  | @ 33 MHz                                                          |                                               |                             | 30                       | mA   |

|                  | Idle Mode                                                         |                                               |                             |                          |      |

|                  | @ 33 MHz                                                          |                                               |                             | 21                       | mA   |

|                  | Power-down Mode (min. V <sub>DD</sub> = 2V)                       | $T_A = 0^{\circ}C$ to +70°C                   |                             | 45                       | μA   |

|                  |                                                                   | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |                             | 55                       | μA   |

T0-0.1 25093

Figure 34:I<sub>DD</sub> vs. Frequency for 3V SST89V516RDx

Figure 35:I<sub>DD</sub> vs. Frequency for 5V SST89E516RDx

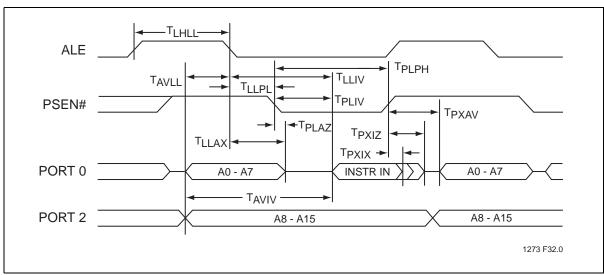

Figure 36: External Program Memory Read Cycle

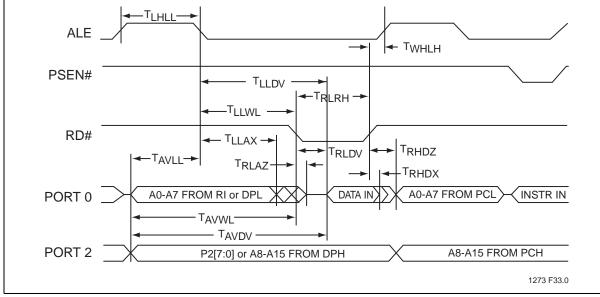

Figure 37: External Data Memory Read Cycle

Data Sheet

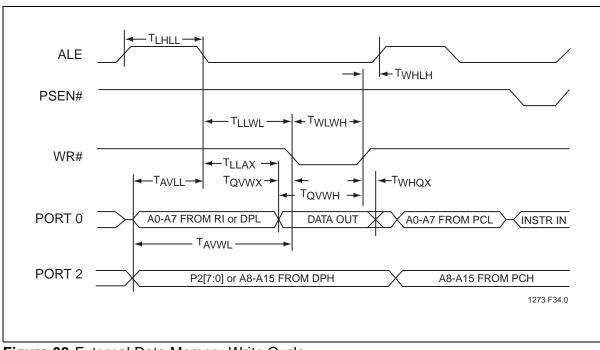

### Figure 38: External Data Memory Write Cycle

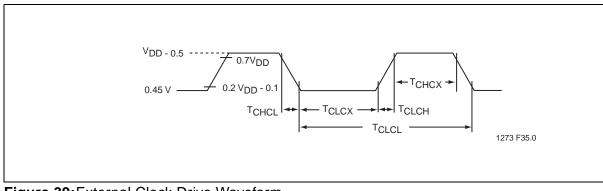

### Table 39: External Clock Drive

|                     |                      |       | Oscillator |       |     |                       |                       |       |

|---------------------|----------------------|-------|------------|-------|-----|-----------------------|-----------------------|-------|

|                     |                      | 12MHz |            | 40MHz |     | Variable              |                       |       |

| Symbol              | Parameter            | Min   | Max        | Min   | Max | Min                   | Max                   | Units |

| 1/T <sub>CLCL</sub> | Oscillator Frequency |       |            |       |     | 0                     | 40                    | MHz   |

| T <sub>CLCL</sub>   |                      | 83    |            | 25    |     |                       |                       | ns    |

| T <sub>CHCX</sub>   | High Time            |       |            | 8.75  |     | 0.35T <sub>CLCL</sub> | 0.65T <sub>CLCL</sub> | ns    |

| T <sub>CLCX</sub>   | Low Time             |       |            | 8.75  |     | 0.35T <sub>CLCL</sub> | 0.65T <sub>CLCL</sub> | ns    |

| T <sub>CLCH</sub>   | Rise Time            |       | 20         |       | 10  |                       |                       | ns    |

| T <sub>CHCL</sub>   | Fall Time            |       | 20         |       | 10  |                       |                       | ns    |

T0-0.0 25093

### Figure 39: External Clock Drive Waveform

Figure 49:44-lead Plastic Lead Chip Carrier (PLCC) SST Package Code: NJ