Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | 8051                                                                             |

| Core Size                  | 8-Bit                                                                            |

| Speed                      | 33MHz                                                                            |

| Connectivity               | EBI/EMI, SPI, UART/USART                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                                 |

| Number of I/O              | 36                                                                               |

| Program Memory Size        | 72KB (72K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                      |

| Data Converters            | -                                                                                |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | -40°C ~ 85°C                                                                     |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/sst89v516rd2-33-i-tqje |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Data Sheet

## Program Memory Block Switching

The program memory block switching feature of the device allows either Block 1 or the lowest 8 KByte of Block 0 to be used for the lowest 8 KByte of the program address space. SFCF[1:0] controls program memory block switching.

### Table 2: SFCF Values for Program Memory Block Switching

| SFCF[1:0]  | Program Memory Block Switching                                                                                                                                                                                                                                                                                                                              |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01, 10, 11 | Block 1 is not visible to the program counter (PC).<br>Block 1 is reachable only via in-application programming from 0000H - 1FFFH.                                                                                                                                                                                                                         |

| 00         | Block 1 is overlaid onto the low 8K of the program address space; occupying address locations 0000H - 1FFFH.<br>When the PC falls within 0000H - 1FFFH, the instruction will be fetched from Block 1 instead of Block 0.<br>Outside of 0000H - 1FFFH, Block 0 is used. Locations 0000H - 1FFFH of Block 0 are reachable through in-application programming. |

T0-0.0 25093

### **Reset Configuration of Program Memory Block Switching**

Program memory block switching is initialized after reset according to the state of the Start-up Configuration bit SC0. The SC0 bit is programmed via an external host mode command or an IAP Mode command. See Table 14.

Once out of reset, the SFCF[0] bit can be changed dynamically by the program for desired effects. Changing SFCF[0] will not change the SC0 bit.

Caution must be taken when dynamically changing the SFCF[0] bit. Since this will cause different physical memory to be mapped to the logical program address space. The user must avoid executing block switching instructions within the address range 0000H to 1FFFH.

|                  | State of SFCF[1:0] after:           |                                       |                   |  |  |  |

|------------------|-------------------------------------|---------------------------------------|-------------------|--|--|--|

| SC0 <sup>1</sup> | Power-on<br>or<br>External<br>Reset | WDT Reset<br>or<br>Brown-out<br>Reset | Software<br>Reset |  |  |  |

| U (1)            | 00<br>(default)                     | x0                                    | 10                |  |  |  |

| P (0)            | 01                                  | x1                                    | 11                |  |  |  |

| ·                |                                     |                                       | T0-0.0 250        |  |  |  |

**Table 3:** SFCF Values Under Different Reset Conditions

1. P = Programmed (Bit logic state = 0),

U = Unprogrammed (Bit logic state = 1)

### Data RAM Memory

The data RAM has 1024 bytes of internal memory. The RAM can be addressed up to 64KB for external data memory.

Data Sheet

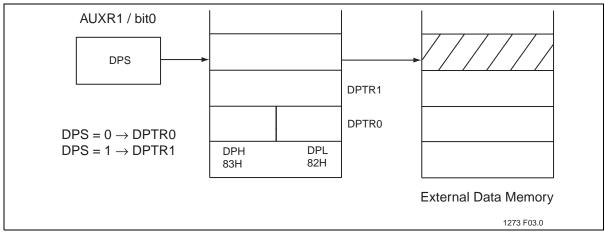

### **Dual Data Pointers**

The device has two 16-bit data pointers. The DPTR Select (DPS) bit in AUXR1 determines which of the two data pointers is accessed. When DPS=0, DPTR0 is selected; when DPS=1, DPTR1 is selected. Quickly switching between the two data pointers can be accomplished by a single INC instruction on AUXR1. (See Figure 8)

Figure 8: Dual Data Pointer Organization

## **Special Function Registers**

Most of the unique features of the FlashFlex microcontroller family are controlled by bits in special function registers (SFRs) located in the SFR memory map shown in Table 5. Individual descriptions of each SFR are provided and reset values indicated in Tables 6 to 10.

|     | 8 BYTES            |       |        |        |        |        |        |      |  |

|-----|--------------------|-------|--------|--------|--------|--------|--------|------|--|

| F8H | IP1 <sup>1</sup>   | CH    | CCAP0H | CCAP1H | CCAP2H | CCAP3H | CCAP4H |      |  |

| F0H | B <sup>1</sup>     |       |        |        |        |        |        | IP1H |  |

| E8H | IEA <sup>1</sup>   | CL    | CCAP0L | CCAP1L | CCAP2L | CCAP3L | CCAP4L |      |  |

| E0H | ACC <sup>1</sup>   |       |        |        |        |        |        |      |  |

| D8H | CCON <sup>1</sup>  | CMOD  | CCAPM0 | CCAPM1 | CCAPM2 | CCAPM3 | CCAPM4 |      |  |

| D0H | PSW <sup>1</sup>   |       |        |        |        | SPCR   |        |      |  |

| C8H | T2CON <sup>1</sup> | T2MOD | RCAP2L | RCAP2H | TL2    | TH2    |        |      |  |

| C0H | WDTC <sup>1</sup>  |       |        |        |        |        |        |      |  |

| B8H | IP <sup>1</sup>    | SADEN |        |        |        |        |        |      |  |

| B0H | P3 <sup>1</sup>    | SFCF  | SFCM   | SFAL   | SFAH   | SFDT   | SFST   | IPH  |  |

| A8H | IE <sup>1</sup>    | SADDR | SPSR   |        |        |        | XICON  |      |  |

| A0H | P2 <sup>1</sup>    |       | AUXR1  |        |        | P4     |        |      |  |

| 98H | SCON <sup>1</sup>  | SBUF  |        |        |        |        |        |      |  |

| 90H | P1 <sup>1</sup>    |       |        |        |        |        |        |      |  |

| 88H | TCON <sup>1</sup>  | TMOD  | TL0    | TL1    | TH0    | TH1    | AUXR   |      |  |

| 80H | P0 <sup>1</sup>    | SP    | DPL    | DPH    |        | WDTD   | SPDR   | PCON |  |

Table 5:

FlashFlex SFR Memory Map

1. Bit addressable SFRs

Data Sheet

### Table 11: PCA SFRs

|                   |                                            | Direct     |          | Bit Add     | dress, Syı | nbol, or A   | Alternati | ive Port | Functior | า         | RESET         |

|-------------------|--------------------------------------------|------------|----------|-------------|------------|--------------|-----------|----------|----------|-----------|---------------|

| Symbol            | Description                                | Address    | MSB      |             |            |              |           |          |          | LSB       | Value         |

| CH<br>CL          | PCA Timer/Coun-<br>ter                     | F9H<br>E9H |          |             |            | CH[7<br>CL[7 |           |          |          |           | 00H<br>00H    |

| CCON <sup>1</sup> | PCA Timer/Coun-<br>ter<br>Control Register | D8H        | CF       | CR          | -          | CCF4         | CCF<br>3  | CCF<br>2 | CCF<br>1 | CCF0      | 00x0000<br>0b |

| CMOD              | PCA Timer/Coun-<br>ter<br>Mode Register    | D9H        | CID<br>L | WDTE        | -          | -            | -         | CPS<br>1 | CPS<br>0 | ECF       | 00xxx000<br>b |

| CCAP0<br>H        | PCA Module 0<br>Compare/Cap-               | FAH        |          |             |            | CCAP0        | H[7:0]    |          |          |           | 00H           |

| CCAP0<br>L        | ture<br>Registers                          | EAH        |          |             |            | CCAPO        | 0L[7:0]   |          |          |           | 00H           |

| CCAP1<br>H        | PCA Module 1<br>Compare/Cap-               | FBH        |          | CCAP1H[7:0] |            |              |           |          | 00H      |           |               |

| CCAP1<br>L        | ture<br>Registers                          | EBH        |          | CCAP1L[7:0] |            |              |           |          | 00H      |           |               |

| CCAP2<br>H        | PCA Module 2<br>Compare/Cap-               | FCH        |          | CCAP2H[7:0] |            |              |           |          | 00H      |           |               |

| CCAP2<br>L        | ture<br>Registers                          | ECH        |          | CCAP2L[7:0] |            |              |           |          | 00H      |           |               |

| CCAP3<br>H        | PCA Module 3<br>Compare/Cap-               | FDH        |          |             |            | CCAP3        | H[7:0]    |          |          |           | 00H           |

| CCAP3<br>L        | ture<br>Registers                          | EDH        |          |             |            | CCAP3        | BL[7:0]   |          |          |           | 00H           |

| CCAP4<br>H        | PCA Module 4<br>Compare/Cap-               | FEH        |          |             |            | CCAP4        | H[7:0]    |          |          |           | 00H           |

| CCAP4<br>L        | ture<br>Registers                          | EEH        |          |             |            | CCAP4        | L[7:0]    |          |          |           | 00H           |

| CCAPM<br>0        | PCA<br>Compare/Cap-                        | DAH        | -        | ECOM<br>0   | CAPP<br>0  | CAPN<br>0    | MAT<br>0  | TOG<br>0 | PWM<br>0 | ECCF<br>0 | x000000<br>0b |

| CCAPM<br>1        | ture<br>Module Mode                        | DBH        | -        | ECOM<br>1   | CAPP<br>1  | CAPN<br>1    | MAT<br>1  | TOG<br>1 | PWM<br>1 | ECCF<br>1 | x000000<br>0b |

| CCAPM<br>2        | Registers                                  | DCH        | -        | ECOM<br>2   | CAPP<br>2  | CAPN<br>2    | MAT<br>2  | TOG<br>2 | PWM<br>2 | ECCF<br>2 | x000000<br>0b |

| CCAPM<br>3        |                                            | DDH        | -        | ECOM<br>3   | CAPP<br>3  | CAPN<br>3    | MAT<br>3  | TOG<br>3 | PWM<br>3 | ECCF<br>3 | x000000<br>0b |

| CCAPM<br>4        |                                            | DEH        | -        | ECOM<br>4   | CAPP<br>4  | CAPN<br>4    | MAT<br>4  | TOG<br>4 | PWM<br>4 | ECCF<br>4 | x000000<br>0b |

1. Bit Addressable SFRs

#### Data Sheet

| ounter mode Register' (CMOD) |                                                                                                         |                              |             |            |              |         |           |     |             |

|------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------|-------------|------------|--------------|---------|-----------|-----|-------------|

| Location                     | 7                                                                                                       | 6                            | 5           | 4          | 3            | 2       | 1         | 0   | Reset Value |

| D9H                          | CIDL                                                                                                    | WDTE                         | -           | -          | -            | CPS1    | CPS0      | ECF | 00xxx000b   |

|                              | 1. Not bit a                                                                                            | addressable                  |             |            |              |         |           |     | -           |

| Symbol                       | Function                                                                                                |                              |             |            |              |         |           |     |             |

| CIDL                         | Counter Id                                                                                              | lle Control                  | :           |            |              |         |           |     |             |

|                              | 0: Progran                                                                                              |                              |             |            |              | 0 0     | idle mode | 9   |             |

|                              | 1: Progran                                                                                              | ns the PC                    | A Counter   | to be gate | ed off durir | ng idle |           |     |             |

| WDTE                         | Watchdog                                                                                                |                              |             |            |              |         |           |     |             |

|                              | 0: Disable                                                                                              |                              | •           |            |              |         |           |     |             |

|                              | 1: Enables                                                                                              |                              | •<br>•      |            |              | uie 4   |           |     |             |

| -                            | Not implemented, reserved for future use.                                                               |                              |             |            |              |         |           |     |             |

|                              | Note: User should not write '1's to reserved bits. The value read from a reserved bit is indeterminate. |                              |             |            |              |         |           |     |             |

| CPS1                         | PCA Cour                                                                                                | PCA Count Pulse Select bit 1 |             |            |              |         |           |     |             |

| CPS0                         | PCA Cour                                                                                                | nt Pulse Se                  | elect bit 2 |            |              |         |           |     |             |

|                              |                                                                                                         |                              |             |            |              |         |           |     |             |

| CPS1 | CPS0 | Selected<br>PCA Input <sup>1</sup> |                                                                                             |

|------|------|------------------------------------|---------------------------------------------------------------------------------------------|

| 0    | 0    | 0                                  | Internal clock, f <sub>OSC</sub> /6 in 6 clock mode (f <sub>OSC</sub> /12 in 12 clock mode) |

| 0    | 1    | 1                                  | Internal clock, $f_{OSC}/2$ in 6 clock mode ( $f_{OSC}/4$ in 12 clock mode)                 |

| 1    | 0    | 2                                  | Timer 0 overflow                                                                            |

| 1    | 1    | 3                                  | External clock at ECI/P1.2 pin                                                              |

|      |      |                                    | (max. rate = $f_{OSC}/4$ in 6 clock mode, $f_{OSC}/8$ in 12 clock mode)                     |

1. f<sub>OSC</sub> = oscillator frequency

ECF PCA Enable Counter Overflow interrupt:

0: Disables the CF bit in CCON

1: Enables CF bit in CCON to generate an interrupt

Data Sheet

## Flash Memory Programming

The device internal flash memory can be programmed or erased using In-Application Programming (IAP) mode

### **Product Identification**

The Read-ID command accesses the Signature Bytes that identify the device and the manufacturer as SST. External programmers primarily use these Signature Bytes in the selection of programming algorithms.

#### Table 12: Product Identification

|                   | Address | Data |

|-------------------|---------|------|

| Manufacturer's ID | 30H     | BFH  |

| Device ID         |         |      |

| SST89E516RD2/RD   | 31H     | 93H  |

| SST89V516RD2/RD   | 31H     | 92H  |

T0-0.0 25093

### In-Application Programming Mode

The device offers either 72 KByte of in-application programmable flash memory. During in-application programming, the CPU of the microcontroller enters IAP mode. The two blocks of flash memory allow the CPU to execute user code from one block, while the other is being erased or reprogrammed concurrently. The CPU may also fetch code from an external memory while all internal flash is being reprogrammed. The mailbox registers (SFST, SFCM, SFAL, SFAH, SFDT and SFCF) located in the special function register (SFR), control and monitor the device's erase and program process.

Table 14 outline the commands and their associated mailbox register settings.

### In-Application Programming Mode Clock Source

During IAP mode, both the CPU core and the flash controller unit are driven off the external clock. However, an internal oscillator will provide timing references for Program and Erase operations. The internal oscillator is only turned on when required, and is turned off as soon as the flash operation is completed.

### Memory Bank Selection for In-Application Programming Mode

With the addressing range limited to 16 bit, only 64 KByte of program address space is "visible" at any one time. As shown in Table 13, the bank selection (the configuration of EA# and SFCF[1:0]), allows Block 1 memory to be overlaid on the lowest 8 KByte of Block 0 memory, making Block 1 reachable. The same concept is employed to allow both Block 0 and Block 1 flash to be accessible to IAP operations. Code from a block that is not visible may not be used as a source to program another address. However, a block that is not "visible" may be programmed by code from the other block through mailbox registers.

The device allows IAP code in one block of memory to program the other block of memory, but may not program any location in the same block. If an IAP operation originates physically from Block 0, the target of this operation is implicitly defined to be in Block 1. If the IAP operation originates physically from

#### Data Sheet

Block 1, then the target address is implicitly defined to be in Block 0. If the IAP operation originates from external program space, then, the target will depend on the address and the state of bank selection.

#### IAP Enable Bit

The IAP enable bit, SFCF[6], enables in-application programming mode. Until this bit is set, all flash programming IAP commands will be ignored.

| EA# | SFCF[1:0]  | Address of IAP Inst. | Target Address     | Block Being<br>Programmed |

|-----|------------|----------------------|--------------------|---------------------------|

| 1   | 00         | >= 2000H (Block 0)   | >= 2000H (Block 0) | None <sup>1</sup>         |

| 1   | 00         | >= 2000H (Block 0)   | < 2000H (Block 1)  | Block 1                   |

| 1   | 00         | < 2000H (Block 1)    | Any (Block 0)      | Block 0                   |

| 1   | 01, 10, 11 | Any (Block 0)        | >= 2000H (Block 0) | None <sup>1</sup>         |

| 1   | 01, 10, 11 | Any (Block 0)        | < 2000H (Block 1)  | Block 1                   |

| 0   | 00         | From external        | >= 2000H (Block 0) | Block 0                   |

| 0   | 00         | From external        | < 2000H (Block 1)  | Block 1                   |

| 0   | 01, 10, 11 | From external        | Any (Block 0)      | Block 0                   |

#### Table 13: IAP Address Resolution

1. No operation is performed because code from one block may not program the same originating block

T0-0.0 25093

### In-Application Programming Mode Commands

All of the following commands can only be initiated in the IAP mode. In all situations, writing the control byte to the SFCM register will initiate all of the operations. All commands will not be enabled if the security locks are enabled on the selected memory block.

The Program command is for programming new data into the memory array. The portion of the memory array to be programmed should be in the erased state, FFH. If the memory is not erased, it should first be erased with an appropriate Erase command. Warning: Do not attempt to write (program or erase) to a block that the code is currently fetching from. This will cause unpredictable program behavior and may corrupt program data.

Data Sheet

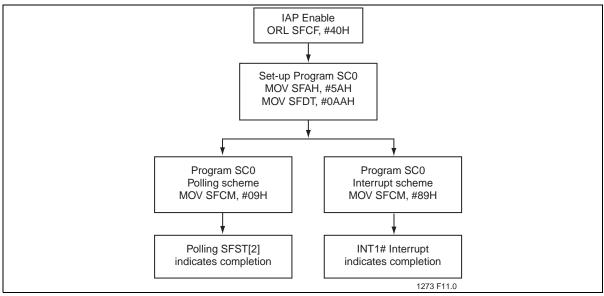

#### Prog-SC0

Prog-SC0 command is used to program the SC0 bit. This command only changes the SC0 bit and has no effect on BSEL bit until after a reset cycle.

SC0 bit previously in un-programmed state can be programmed by this command. The Prog-SC0 command should reside only in Block 1 or external code memory.

### Figure 15: Prog-SC0

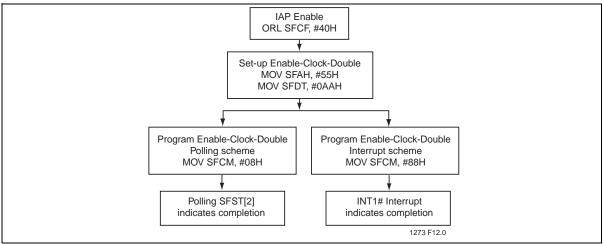

### Enable-Clock-Double

Enable-Clock-Double command is used to make the MCU run at 6 clocks per machine cycle. The standard (default) is 12 clocks per machine cycle (i.e. clock double command disabled).

### Figure 16: Enable-Clock-Double

There are no IAP counterparts for the external host commands Select-Block0 and Select-Block1.

Data Sheet

## **Timers/Counters**

### Timers

The device has three 16-bit registers that can be used as either timers or event counters. The three timers/counters are denoted Timer 0 (T0), Timer 1 (T1), and Timer 2 (T2). Each is designated a pair of 8-bit registers in the SFRs. The pair consists of a most significant (high) byte and least significant (low) byte. The respective registers are TL0, TH0, TL1, TH1, TL2, and TH2.

## **Timer Set-up**

Refer to Table 9 for TMOD, TCON, and T2CON registers regarding timers T0, T1, and T2. The following tables provide TMOD values to be used to set up Timers T0, T1, and T2.

Except for the baud rate generator mode, the values given for T2CON do not include the setting of the TR2 bit. Therefore, bit TR2 must be set separately to turn the timer on.

|               |      |                   | TMOD                          |                               |  |  |

|---------------|------|-------------------|-------------------------------|-------------------------------|--|--|

|               | Mode | Function          | Internal Control <sup>1</sup> | External Control <sup>2</sup> |  |  |

|               | 0    | 13-bit Timer      | 00H                           | 08H                           |  |  |

|               | 1    | 16-bit Timer      | 01H                           | 09H                           |  |  |

| Used as Timer | 2    | 8-bit Auto-Reload | 02H                           | 0AH                           |  |  |

|               | 3    | Two 8-bit Timers  | 03H                           | 0BH                           |  |  |

|               | 0    | 13-bit Timer      | 04H                           | 0CH                           |  |  |

| Used as       | 1    | 16-bit Timer      | 05H                           | 0DH                           |  |  |

| Counter       | 2    | 8-bit Auto-Reload | 06H                           | 0EH                           |  |  |

|               | 3    | Two 8-bit Timers  | 07H                           | 0FH                           |  |  |

|               |      |                   | •                             | T0-0.0 25093                  |  |  |

#### Table 15: Timer/Counter 0

1. The Timer is turned ON/OFF by setting/clearing bit TR0 in the software.

2. The Timer is turned ON/OFF by the 1 to 0 transition on INT0# (P3.2) when TR0 = 1 (hardware control).

#### Table 16: Timer/Counter 1

|               |      |                   | тмор                          |                               |

|---------------|------|-------------------|-------------------------------|-------------------------------|

|               | Mode | Function          | Internal Control <sup>1</sup> | External Control <sup>2</sup> |

|               | 0    | 13-bit Timer      | 00H                           | 80H                           |

|               | 1    | 16-bit Timer      | 10H                           | 90H                           |

| Used as Timer | 2    | 8-bit Auto-Reload | 20H                           | A0H                           |

|               | 3    | Does not run      | 30H                           | B0H                           |

|               | 0    | 13-bit Timer      | 40H                           | СОН                           |

| Used as       | 1    | 16-bit Timer      | 50H                           | D0H                           |

| Counter       | 2    | 8-bit Auto-Reload | 60H                           | E0H                           |

|               | 3    | Not available     | -                             | -                             |

1. The Timer is turned ON/OFF by setting/clearing bit TR1 in the software.

2. The Timer is turned ON/OFF by the 1 to 0 transition on INT1# (P3.3) when TR1 = 1 (hardware control).

Data Sheet

|                 |                                                         | T20                           | CON                           |

|-----------------|---------------------------------------------------------|-------------------------------|-------------------------------|

|                 | Mode                                                    | Internal Control <sup>1</sup> | External Control <sup>2</sup> |

|                 | 16-bit Auto-Reload                                      | 00H                           | 08H                           |

|                 | 16-bit Capture                                          | 01H                           | 09H                           |

| Used as Timer   | Baud rate generator receive and transmit same baud rate | 34H                           | 36H                           |

|                 | Receive only                                            | 24H                           | 26H                           |

|                 | Transmit only                                           | 14H                           | 16H                           |

| Used as Counter | 16-bit Auto-Reload                                      | 02H                           | 0AH                           |

| Useu as Counter | 16-bit Capture                                          | 03H                           | 0BH                           |

#### Table 17: Timer/Counter 2

1. Capture/Reload occurs only on timer/counter overflow.

T0-0.0 25093

2. Capture/Reload occurs on timer/counter overflow and a 1 to 0 transition on T2EX (P1.1) pin except when Timer 2 is used in the baud rate generating mode.

## **Programmable Clock-Out**

A 50% duty cycle clock can be programmed to come out on P1.0. This pin, besides being a regular I/O pin, has two alternate functions. It can be programmed:

- 1. to input the external clock for Timer/Counter 2, or

- 2. to output a 50% duty cycle clock ranging from 122 Hz to 8 MHz at a 16 MHz operating frequency (61 Hz to 4 MHz in 12 clock mode).

To configure Timer/Counter 2 as a clock generator, bit

C/#T2 (in T2CON) must be cleared and bit T20E in T2MOD must be set. Bit TR2 (T2CON.2) also must be set to start the timer.

The Clock-Out frequency depends on the oscillator frequency and the reload value of Timer 2 capture registers (RCAP2H, RCAP2L) as shown in this equation:

n =2 (in 6 clock mode) 4 (in 12 clock mode)

Where (RCAP2H, RCAP2L) = the contents of RCAP2H and RCAP2L taken as a 16-bit unsigned integer.

In the Clock-Out mode, Timer 2 roll-overs will not generate an interrupt. This is similar to when it is used as a baud-rate generator. It is possible to use Timer 2 as a baud-rate generator and a clock generator simultaneously. Note, however, that the baud-rate and the Clock-Out frequency will not be the same.

Data Sheet

## Serial I/O

## Full-Duplex, Enhanced UART

The device serial I/O port is a full-duplex port that allows data to be transmitted and received simultaneously in hardware by the transmit and receive registers, respectively, while the software is performing other tasks. The transmit and receive registers are both located in the Serial Data Buffer (SBUF) special function register. Writing to the SBUF register loads the transmit register, and reading from the SBUF register obtains the contents of the receive register.

The UART has four modes of operation which are selected by the Serial Port Mode Specifier (SM0 and SM1) bits of the Serial Port Control (SCON) special function register. In all four modes, transmission is initiated by any instruction that uses the SBUF register as a destination register. Reception is initiated in mode 0 when the Receive Interrupt (RI) flag bit of the Serial Port Control (SCON) SFR is cleared and the Reception Enable/ Disable (REN) bit of the SCON register is set. Reception is initiated in the other modes by the incoming start bit if the REN bit of the SCON register is set.

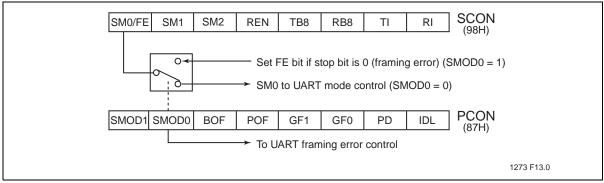

### **Framing Error Detection**

Framing Error Detection is a feature, which allows the receiving controller to check for valid stop bits in modes 1, 2, or 3. Missing stops bits can be caused by noise in serial lines or from simultaneous transmission by two CPUs.

Framing Error Detection is selected by going to the PCON register and changing SMOD0 = 1 (see Figure 17). If a stop bit is missing, the Framing Error bit (FE) will be set. Software may examine the FE bit after each reception to check for data errors. After the FE bit has been set, it can only be cleared by software. Valid stop bits do not clear FE. When FE is enabled, RI rises on the stop bit, instead of the last data bit (see Figure 18 and Figure 19).

Figure 17: Framing Error Block Diagram

Data Sheet

If the user added a third slave such as the example below:

Slave 3

SADDR

=

1111

1001

SADEN

=

1111

0101

GIVEN

=

1111

X0X1

| Select Slave 3 Only |               |                        |  |  |

|---------------------|---------------|------------------------|--|--|

| Slave 2             | Given Address | Possible Addresses     |  |  |

|                     | 1111 X0X1     | 1111 1011<br>1111 1001 |  |  |

The user could use the possible addresses above to select slave 3 only. Another combination could be to select slave 2 and 3 only as shown below.

| Select Slaves 2 & 3 Only        |           |  |  |  |  |

|---------------------------------|-----------|--|--|--|--|

| Slaves 2 & 3 Possible Addresses |           |  |  |  |  |

|                                 | 1111 0011 |  |  |  |  |

More than one slave may have the same SADDR address as well, and a given address could be used to modify the address so that it is unique.

#### Using the Broadcast Address to Select Slaves

Using the broadcast address, the master can communicate with all the slaves at once. It is formed by performing a logical OR of SADDR and SADEN with '0's in the result treated as "don't cares".

#### Slave 1

1111 0001 = SADDR +1111 1010 = SADEN 1111 1X11 = Broadcast

"Don't cares" allow for a wider range in defining the broadcast address, but in most cases, the broadcast address will be FFH.

On reset, SADDR and SADEN are "0". This produces an given address of all "don't cares" as well as a broadcast address of all "don't cares." This effectively disables Automatic Addressing mode and allows the microcontroller to function as a standard 8051, which does not make use of this feature.

Data Sheet

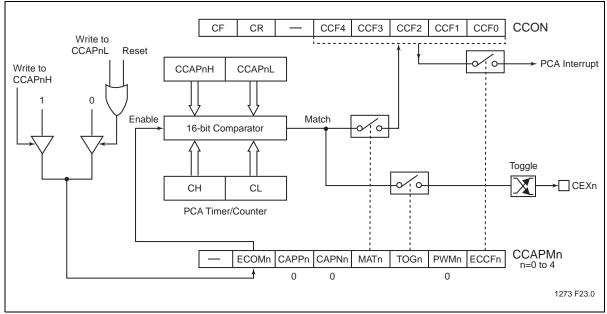

## **Programmable Counter Array**

The Programmable Counter Array (PCA) present on the SST89E/V516RDx is a special 16-bit timer that has five 16-bit capture/compare modules. Each of the modules can be programmed to operate in one of four modes: rising and/or falling edge capture, software timer, high-speed output, or pulse width modulator. The 5th module can be programmed as a Watchdog Timer in addition to the other four modes. Each module has a pin associated with it in port 1. Module 0 is connected to P1.3 (CEX0), module 1 to P1[4] (CEX1), module 2 to P1[5] (CEX2), module 3 to P1[6] (CEX3), and module 4 to P1[7] (CEX4). PCA configuration is shown in Figure 24.

## **PCA** Overview

PCA provides more timing capabilities with less CPU intervention than the standard timer/counter. Its advantages include reduced software overhead and improved accuracy.

The PCA consists of a dedicated timer/counter which serves as the time base for an array of five compare/capture modules. Figure 24 shows a block diagram of the PCA. External events associated with modules are shared with corresponding Port 1 pins. Modules not using the port pins can still be used for standard I/O.

Each of the five modules can be programmed in any of the following modes:

- Rising and/or falling edge capture

- Software timer

- High speed output

- Watchdog Timer (Module 4 only)

- Pulse Width Modulator (PWM)

## PCA Timer/Counter

The PCA timer is a free-running 16-bit timer consisting of registers CH and CL (the high and low bytes of the count values). The PCA timer is common time base for all five modules and can be programmed to run at: 1/6 the oscillator frequency, 1/2 the oscillator frequency, Timer 0 overflow, or the input on the ECI pin (P1.2). The timer/counter source is determined from the CPS1 and CPS0 bits in the CMOD SFR as follows (see "PCA Timer/Counter Mode Register (CMOD)" on page 28):

| CPS1 | CPS0 | 12 Clock Mode                                                     | 6 Clock Mode                                                      |

|------|------|-------------------------------------------------------------------|-------------------------------------------------------------------|

| 0    | 0    | f <sub>OSC</sub> /12                                              | f <sub>OSC</sub> /6                                               |

| 0    | 1    | f <sub>OSC</sub> /4                                               | f <sub>OSC</sub> /2                                               |

| 1    | 0    | Timer 0 overflow                                                  | Timer 0 overflow                                                  |

| 1    | 1    | External clock at ECI pin<br>(maximum rate = f <sub>OSC</sub> /8) | External clock at ECI pin<br>(maximum rate = f <sub>OSC</sub> /4) |

### Table 18: PCA Timer/Counter Source

Data Sheet

The table below summarizes various clock inputs at two common frequencies.

| Table 19: PCA | imer/Counter | Inputs |  |

|---------------|--------------|--------|--|

|               |              |        |  |

| Clock Increments |                                                                                                         |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------|--|--|--|

| 12 MHz           | 16 MHz                                                                                                  |  |  |  |

| 1 µsec           | 0.75 µsec                                                                                               |  |  |  |

| 330 nsec         | 250 nsec                                                                                                |  |  |  |

|                  |                                                                                                         |  |  |  |

|                  |                                                                                                         |  |  |  |

| 256 µsec         | 192 µsec                                                                                                |  |  |  |

| 65 msec          | 49 µsec                                                                                                 |  |  |  |

| 1 to 255 µsec    | 0.75 to 191 µsec                                                                                        |  |  |  |

| 0.66 µsec        | 0.50 µsec                                                                                               |  |  |  |

|                  | 12 MHz           1 μsec           330 nsec           256 μsec           65 msec           1 to 255 μsec |  |  |  |

1. In Mode 2, the overflow interrupt for Timer 0 does not need to be enabled.

T0-0.0 25093

The four possible CMOD timer modes with and without the overflow interrupt enabled are shown below. This list assumes that PCA will be left running during idle mode.

#### Table 20: CMOD Values

|                                      | CMOD Value                |                        |  |  |  |

|--------------------------------------|---------------------------|------------------------|--|--|--|

| PCA Count Pulse Selected             | Without Interrupt Enabled | With Interrupt Enabled |  |  |  |

| Internal clock, f <sub>OSC</sub> /12 | 00H                       | 01H                    |  |  |  |

| Internal clock, f <sub>OSC</sub> /4  | 02H                       | 03H                    |  |  |  |

| Timer 0 overflow                     | 04H                       | 05H                    |  |  |  |

| External clock at P1.2               | 06H                       | 07H                    |  |  |  |

T0-0.0 25093

The CCON register is associated with all PCA timer functions. It contains run control bits and flags for the PCA timer (CF) and all modules. To run the PCA the CR bit (CCON.6) must be set by software. Clearing the bit, will turn off PCA. When the PCA counter overflows, the CF (CCON.7) will be set, and

Data Sheet

Figure 27: PCA High Speed Output Mode

### **Pulse Width Modulator**

The Pulse Width Modulator (PWM) mode is used to generate 8-bit PWMs by comparing the low byte of the PCA timer (CL) with the low byte of the compare register (CCAPnL). When CL < CCAPnL the output is low. When  $CL \ge CCAPnL$  the output is high. To activate this mode, the user must set the PWM and ECOM bits in the module's CCAPMn SFR. (See Figure 28 and Table 24)

In PWM mode, the frequency of the output depends on the source for the PCA timer. Since there is only one set of CH and CL registers, all modules share the PCA timer and frequency. Duty cycle of the output is controlled by the value loaded into the high byte (CCAPnH). Since writes to the CCAPnH register are asynchronous, a new value written to the high byte will not be shifted into CCAPnL for comparison until the next period of the output (when CL rolls over from 255 to 00).

To calculate values for CCAPnH for any duty cycle, use the following equation:

CCAPnH = 256(1 - Duty Cycle)

where CCAPnH is an 8-bit integer and Duty Cycle is a fraction.

Data Sheet

T0-0.0 25093

### Table 26: Security Lock Access Table

|       |                  | Source               | Target               | Byte-Verify Allo           | MOVC Allowed |        |

|-------|------------------|----------------------|----------------------|----------------------------|--------------|--------|

| Level | SFST[7:5]        | Address <sup>1</sup> | Address <sup>2</sup> | External Host <sup>3</sup> | IAP          | 516RDx |

| 1     |                  | Block 0              | Block 0              | Y                          | Ν            | Y      |

|       |                  |                      | Block 1              | Y                          | Y            | Y      |

|       | 000b<br>(unlock) |                      | External             | N/A                        | N/A          | Ν      |

|       |                  | Block 1              | Block 0              | Y                          | Y            | Y      |

|       |                  |                      | Block 1              | Y                          | Ν            | Y      |

|       |                  |                      | External             | N/A                        | N/A          | Ν      |

|       |                  | External             | Block 0/1            | Y                          | Y            | Ν      |

|       |                  | External             | External             | N/A                        | N/A          | Y      |

1. Location of MOVC or IAP instruction

2. Target address is the location of the byte being read

3. External host Byte-Verify access does not depend on a source address.

Data Sheet

## Interrupts

## **Interrupt Priority and Polling Sequence**

The device supports eight interrupt sources under a four level priority scheme. Table 27 summarizes the polling sequence of the supported interrupts. Note that the SPI serial interface and the UART share the same interrupt vector. (See Figure 32)

| Description | Interrupt<br>Flag | Vector<br>Address | Interrupt<br>Enable | Interrupt<br>Priority | Service<br>Priority | Wake-Up<br>Power-down |

|-------------|-------------------|-------------------|---------------------|-----------------------|---------------------|-----------------------|

| Ext. Int0   | IE0               | 0003H             | EX0                 | PX0/H                 | 1(highest)          | yes                   |

| Brown-out   | -                 | 004BH             | EBO                 | PBO/H                 | 2                   | no                    |

| Т0          | TF0               | 000BH             | ET0                 | PT0/H                 | 3                   | no                    |

| Ext. Int1   | IE1               | 0013H             | EX1                 | PX1/H                 | 4                   | yes                   |

| T1          | TF1               | 001BH             | ET1                 | PT1/H                 | 5                   | no                    |

| PCA         | CF/CCFn           | 0033H             | EC                  | PPCH                  | 6                   | no                    |

| Ext. Int. 2 | IE2               | 003BH             | EX2                 | PX2/H                 | 7                   | no                    |

| Ext. Int. 3 | IE3               | 0043H             | EX3                 | PX3/H                 | 8                   | no                    |

| UART/SPI    | TI/RI/SPIF        | 0023H             | ES                  | PS/H                  | 9                   | no                    |

| T2          | TF2, EXF2         | 002BH             | ET2                 | PT2/H                 | 10                  | no                    |

#### Table 27: Interrupt Polling Sequence

Data Sheet

## System Clock and Clock Options

## **Clock Input Options and Recommended Capacitor Values for Oscillator**

Shown in Figure 33 are the input and output of an internal inverting amplifier (XTAL1, XTAL2), which can be configured for use as an on-chip oscillator.

When driving the device from an external clock source, XTAL2 should be left disconnected and XTAL1 should be driven.

At start-up, the external oscillator may encounter a higher capacitive load at XTAL1 due to interaction between the amplifier and its feedback capacitance. However, the capacitance will not exceed 15 pF once the external signal meets the  $V_{IL}$  and  $V_{IH}$  specifications.

Crystal manufacturer, supply voltage, and other factors may cause circuit performance to differ from one application to another. C1 and C2 should be adjusted appropriately for each design. Table 29, shows the typical values for C1 and C2 vs. crystal type for various frequencies

#### Table 29: Recommended Values for C1 and C2 by Crystal Type

| Crystal | C1 = C2 |

|---------|---------|

| Quartz  | 20-30pF |

| Ceramic | 40-50pF |

T0-0.0 25093

More specific information about on-chip oscillator design can be found in the *FlashFlex Oscillator Circuit Design Considerations* application note.

## **Clock Doubling Option**

By default, the device runs at 12 clocks per machine cycle (x1 mode). The device has a clock doubling option to speed up to 6 clocks per machine cycle. Please refer to Table 30 for detail.

Clock double mode can be enabled either via the external host mode or the IAP mode. Please refer to Table 14 for the IAP mode enabling commands (When set, the EDC# bit in SFST register will indicate 6 clock mode.).

The clock double mode is only for doubling the internal system clock and the internal flash memory, i.e. EA#=1. To access the external memory and the peripheral devices, careful consideration must be taken. Also note that the crystal output (XTAL2) will not be doubled.

Data Sheet

- 1. Under steady state (non-transient) conditions, I<sub>OL</sub> must be externally limited as follows:

- Maximum IOL per port pin: 15mA 26mA

- Maximum IOL per 8-bit port: Maximum IOL total for all outputs: 71mA

- If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test conditions.

- 2. Capacitive loading on Ports 0 and 2 may cause spurious noise to be superimposed on the Vols of ALE and Ports 1 & 3. The noise due to external bus capacitance discharging into the Port 0 & 2 pins when the pins make 1-to-0 transitions during bus operations. In the worst cases (capacitive loading > 100pF), the noise pulse on the ALE pin may exceed 0.8V. In such cases, it may be desirable to qualify ALE with a Schmitt Trigger, or use an address latch with a Schmitt Trigger STROBE input.

- 3. Load capacitance for Port 0, ALE & PSEN#= 100pF, load capacitance for all other outputs = 80pF.

- 4. Capacitive loading on Ports 0 & 2 may cause the V<sub>OH</sub> on ALE and PSEN# to momentarily fall below the V<sub>DD</sub> 0.7 specification when the address bits are stabilizing.

- 5. Pins of Ports 1, 2, and 3 source a transition current when they are being externally driven from 1 to 0. The transition current reaches its maximum value when V<sub>IN</sub> is approximately 2V.

- 6. Pin capacitance is characterized but not tested. EA# is 25pF (max).

Data Sheet

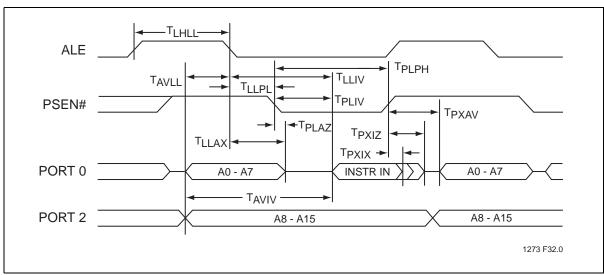

Figure 36: External Program Memory Read Cycle

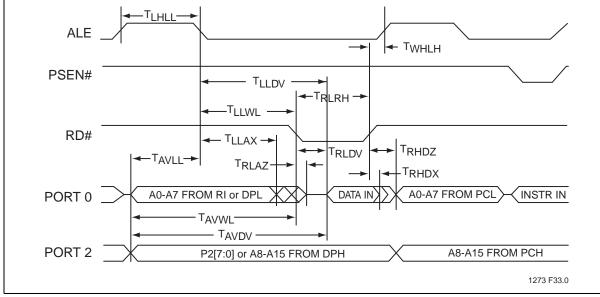

Figure 37: External Data Memory Read Cycle

Data Sheet

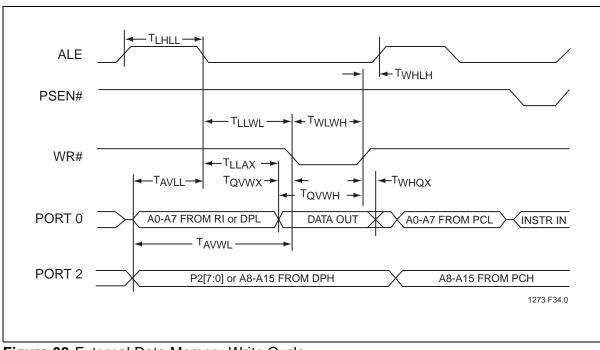

## Figure 38: External Data Memory Write Cycle

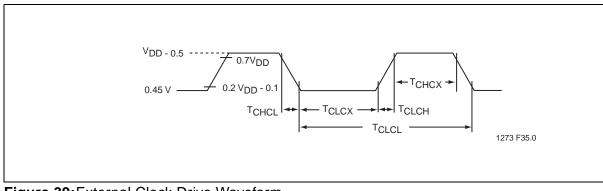

#### Table 39: External Clock Drive

|                     |                      | Oscillator |     |             |     |                       |                       |       |

|---------------------|----------------------|------------|-----|-------------|-----|-----------------------|-----------------------|-------|

|                     |                      | 12MHz      |     | 12MHz 40MHz |     | Variable              |                       |       |

| Symbol              | Parameter            | Min        | Max | Min         | Max | Min                   | Max                   | Units |

| 1/T <sub>CLCL</sub> | Oscillator Frequency |            |     |             |     | 0                     | 40                    | MHz   |

| T <sub>CLCL</sub>   |                      | 83         |     | 25          |     |                       |                       | ns    |

| T <sub>CHCX</sub>   | High Time            |            |     | 8.75        |     | 0.35T <sub>CLCL</sub> | 0.65T <sub>CLCL</sub> | ns    |

| T <sub>CLCX</sub>   | Low Time             |            |     | 8.75        |     | 0.35T <sub>CLCL</sub> | 0.65T <sub>CLCL</sub> | ns    |

| T <sub>CLCH</sub>   | Rise Time            |            | 20  |             | 10  |                       |                       | ns    |

| T <sub>CHCL</sub>   | Fall Time            |            | 20  |             | 10  |                       |                       | ns    |

T0-0.0 25093

### Figure 39: External Clock Drive Waveform