#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014                       |                                                                     |

|----------------------------|---------------------------------------------------------------------|

| Product Status             | Active                                                              |

| Core Processor             | -                                                                   |

| Core Size                  | 8/16-Bit                                                            |

| Speed                      | 50MHz                                                               |

| Connectivity               | UART/USART                                                          |

| Peripherals                | -                                                                   |

| Number of I/O              | 16                                                                  |

| Program Memory Size        | -                                                                   |

| Program Memory Type        | ROMIess                                                             |

| EEPROM Size                | -                                                                   |

| RAM Size                   | ·                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                           |

| Data Converters            | -                                                                   |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 80-BQFP                                                             |

| Supplier Device Package    | 80-PQFP (20x14)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/ia188ebpqf80ir2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# LIST OF TABLES

| Table 1. IA186EB 84-Pin PLCC Pin Listing                                             | 11 |

|--------------------------------------------------------------------------------------|----|

| Table 2. IA188EB 84-Pin PLCC Pin Listing                                             | 13 |

| Table 3. IA186EB 80-Pin PQFP Pin Listing                                             | 16 |

| Table 4. IA188EB 80-Pin PQFP Pin Listing                                             | 18 |

| Table 5. IA186EB 80-Pin LQFP Pin Listing                                             | 21 |

| Table 6. IA188EB 80-Pin LQFP Pin Listing                                             | 23 |

| Table 7. IA186EB Pin/Signal Descriptions                                             | 25 |

| Table 8. IA188EB Pin/Signal Descriptions                                             | 34 |

| Table 9. IA186EB and IA188EB Absolute Maximum Ratings                                |    |

| Table 10. IA186EB and IA188EB Thermal Characteristics                                | 42 |

| Table 11. IA186EB and IA188EB DC Parameters                                          | 43 |

| Table 12. Peripheral Control Block Registers                                         | 49 |

| Table 13. AC Input Characteristics for 5.0-Volt Operation                            | 52 |

| Table 14. AC Input Characteristics for 3.3-Volt Operation                            | 52 |

| Table 15. AC Output Characteristics for 5.0-Volt Operation                           | 53 |

| Table 16. AC Output Characteristics for 3.3-Volt Operation                           | 53 |

| Table 17. Relative Timing Characteristics                                            | 55 |

| Table 18. Clock Input and Clock Output Timing Characteristics for 5.0-Volt Operation | 56 |

| Table 19. Clock Input and Output Characteristics for 3.3-Volt Operation              | 57 |

| Table 20.    Serial Port Mode 0 Timing Characteristics                               | 58 |

| Table 21. Instruction Set Timing                                                     |    |

| Table 22. Innovasic Part Number Cross-Reference for the PLCC                         | 74 |

| Table 23. Innovasic Part Number Cross-Reference for the PQFP                         | 75 |

| Table 24. Innovasic Part Number Cross-Reference for the LQFP                         | 76 |

| Table 25. Summary of Errata                                                          | 77 |

| Table 26. Revision History                                                           | 83 |

# 1. Introduction

The Innovasic Semiconductor IA186EB and IA188EB microcontrollers are form, fit, and function replacements for the original Intel<sup>®</sup> 80C186EB, 80C188EB, 80L186EB, and 80L188EB 16-bit high-integration embedded processors.

These devices are produced using Innovasic's Managed IC Lifetime Extension System (MILES<sup>TM</sup>). This cloning technology, which produces replacement ICs beyond simple emulations, ensures complete compatibility with the original device, including any "undocumented features." Additionally, the MILES process captures the clone design in such a way that production of the clone can continue even as silicon technology advances.

The IA186EB and IA188EB microcontrollers replace the obsolete Intel 80C186EB and 80C188EB devices, allowing users to retain existing board designs, software compilers/assemblers, and emulation tools, thereby avoiding expensive redesign efforts.

### 1.1 General Description

The Innovasic Semiconductor IA186EB and IA188EB microcontrollers are an upgrade for the 80C186EB/80C188EB microcontroller designs with integrated peripherals to provide increased functionality and reduce system costs. The IA186EB and IA188EB devices are designed to satisfy requirements of embedded products designed for telecommunications, office automation and storage, and industrial controls.

The IA186EB and IA188EB microcontrollers have a set of base peripherals beneficial to many embedded applications and include a standard numeric interface, an interrupt control unit, a chip-select unit, a DRAM refresh control unit, a power management unit, and three 16-bit timer/counters.

The IA186EB and IA188EB microcontrollers are capable of operating at 5.0 or 3.3 volts. This datasheet discusses both modes of operation. Where applicable, characteristics specific to either 3.3 or 5.0 volt operation are identified separately throughout this datasheet.

Additionally, the IA186EB and IA188EB include two integrated serial ports that support both synchronous and asynchronous communications, simplifying inter-processor and display communications. The IA186EB and IA188EB also have an enhanced chip-select unit and two multiplexed I/O ports. The enhanced chip-select unit offers 10 general chip selects, each with the ability to address up to 1 Mbyte. This enhanced unit enables memory-bank switching to expand the IA186EB/IA188EB 1 Mbyte address space. The I/O ports allow for basic functions such as scanning keypads for input. The ports can also be used to control system power consumption, disabling unneeded components.

The serial ports, I/O capabilities, and enhanced chip selects make the IA186EB/IA188EB an excellent processor for portable data acquisition or communication applications.

# 2. Packaging, Pin Descriptions, and Physical Dimensions

Information on the packages and pin descriptions for the IA186EB and the IA188EB is provided separately. Refer to sections, figures, and tables for information on the device of interest.

### 2.1 Packages and Pinouts

The Innovasic Semiconductor IA186EB and IA188EB microcontroller is available in the following packages:

- 84-Pin Plastic Leaded Chip Carrier (PLCC), equivalent to original PLCC package

- 80-Pin Plastic Quad Flat Pack (PQFP), equivalent to original PQFP package

- 80-Pin Low-Profile Quad Flat Pack (LQFP), equivalent to original SQFP package

| Pin              | Name            |

|------------------|-----------------|

| 1                | V <sub>cc</sub> |

| 1<br>2<br>3<br>4 | V <sub>ss</sub> |

| 3                | error_n         |

|                  | rd_n            |

| 5                | wr_n            |

| 6<br>7           | ale             |

|                  | bhe_n           |

| 8                | s2_n            |

| 9                | s1_n            |

| 10               | s0_n            |

| 11               | den_n           |

| 12               | hlda            |

| 13               | hold            |

| 14               | test_n/busy     |

| 15               | lock_n          |

| 16               | dt/r_n          |

| 17               | nmi             |

| 18               | ready           |

| 19               | p1.7/gcs7_n     |

| 20               | p1.6/gcs6_n     |

| 21               | p1.5/gcs5_n     |

# Table 1. IA186EB 84-Pin PLCC Pin Listing

Pin

22

23 24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

| Name            | Pin | Name            |

|-----------------|-----|-----------------|

| V <sub>ss</sub> | 43  | V <sub>ss</sub> |

| V <sub>cc</sub> | 44  | clkout          |

| p1.4/gcs4_n     | 45  | t0out           |

| p1.3/gcs3_n     | 46  | t0in            |

| p1.2/gcs2_n     | 47  | t1out           |

| p1.1/gcs1_n     | 48  | t1in            |

| p1.0/gcs0_n     | 49  | p2.7            |

| lcs_n           | 50  | p2.6            |

| ucs_n           | 51  | cts0_n          |

| int0            | 52  | txd0            |

| int1            | 53  | rxd0            |

| int2/inta0_n    | 54  | p2.5/bclk0      |

| int3/inta1_n    | 55  | p2.3/sint1      |

| int4            | 56  | p2.4/cts1_n     |

| pdtmr           | 57  | p2.0/rxd1       |

| resin_n         | 58  | p2.1/txd1       |

| resout          | 59  | p2.2/bclk1      |

| pereq           | 60  | ncs_n           |

| oscout          | 61  | ad0             |

| clkin           | 62  | ad8             |

| V <sub>cc</sub> | 63  | V <sub>ss</sub> |

| е   | Pin | Name            |

|-----|-----|-----------------|

|     | 64  | V <sub>cc</sub> |

|     | 65  | V <sub>ss</sub> |

|     | 66  | ad1             |

|     | 67  | ad9             |

|     | 68  | ad2             |

|     | 69  | ad10            |

|     | 70  | ad3             |

|     | 71  | ad11            |

|     | 72  | ad4             |

|     | 73  | ad12            |

|     | 74  | ad5             |

| k0  | 75  | ad13            |

| t1  | 76  | ad6             |

| 1_n | 77  | ad14            |

| 1   | 78  | ad7             |

| 1   | 79  | ad15            |

| k1  | 80  | a16             |

|     | 81  | a17             |

|     | 82  | a18             |

|     | 83  | a19/once_n      |

|     | 84  | V <sub>ss</sub> |

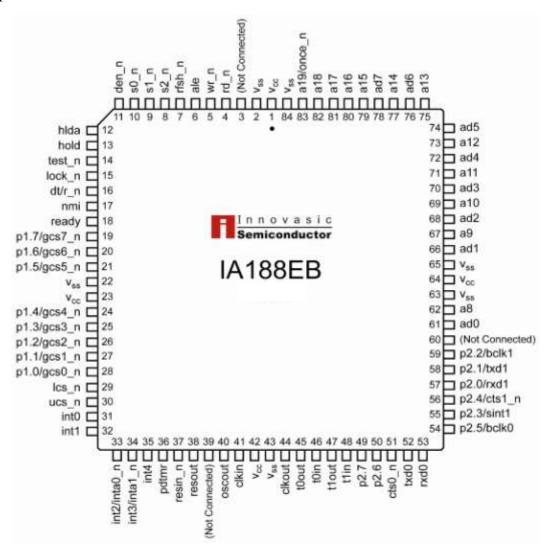

#### 2.1.2 IA188EB 84 PLCC Package

The pinout for the IA188EB 84 PLCC Package is as shown in Figure 2. The corresponding pinout is provided in Table 2.

Figure 2. IA188EB 84-Pin PLCC Package Diagram

| Pin | Name            | Pin | Name            | Pin | Name            | Pin | Name            |

|-----|-----------------|-----|-----------------|-----|-----------------|-----|-----------------|

| 1   | hlda            | 21  | int2/inta0_n    | 41  | p2.5/bclk0      | 61  | ad13            |

| 2   | hold            | 22  | int3/inta1_n    | 42  | p2.3/sint1      | 62  | ad6             |

| 3   | test_n          | 23  | int4            | 43  | p2.4/cts1_n     | 63  | ad14            |

| 4   | lock_n          | 24  | pdtmr           | 44  | p2.0/rxd1       | 64  | ad7             |

| 5   | nmi             | 25  | resin_n         | 45  | p2.1/txd1       | 65  | ad15            |

| 6   | ready           | 26  | resout          | 46  | p2.2/bclk1      | 66  | a16             |

| 7   | p1.7/gcs7_n     | 27  | oscout          | 47  | ad0             | 67  | a17             |

| 8   | p1.6/gcs6_n     | 28  | clkin           | 48  | ad8             | 68  | a18             |

| 9   | p1.5/gcs5_n     | 29  | V <sub>cc</sub> | 49  | V <sub>ss</sub> | 69  | a19/once_n      |

| 10  | V <sub>ss</sub> | 30  | V <sub>ss</sub> | 50  | V <sub>cc</sub> | 70  | V <sub>ss</sub> |

| 11  | V <sub>cc</sub> | 31  | clkout          | 51  | V <sub>ss</sub> | 71  | V <sub>cc</sub> |

| 12  | p1.4/gcs4_n     | 32  | t0out           | 52  | ad1             | 72  | V <sub>ss</sub> |

| 13  | p1.3/gcs3_n     | 33  | t0in            | 53  | ad9             | 73  | rd_n            |

| 14  | p1.2/gcs2_n     | 34  | t1out           | 54  | ad2             | 74  | wr_n            |

| 15  | p1.1/gcs1_n     | 35  | t1in            | 55  | ad10            | 75  | ale             |

| 16  | p1.0/gcs0_n     | 36  | p2.7            | 56  | ad3             | 76  | bhe_n           |

| 17  | lcs_n           | 37  | p2.6            | 57  | ad11            | 77  | s2_n            |

| 18  | ucs_n           | 38  | cts0_n          | 58  | ad4             | 78  | s1_n            |

| 19  | int0            | 39  | txd0            | 59  | ad12            | 79  | s0_n            |

| 20  | int1            | 40  | rxd0            | 60  | ad5             | 80  | den_n           |

## Table 5. IA186EB 80-Pin LQFP Pin Listing

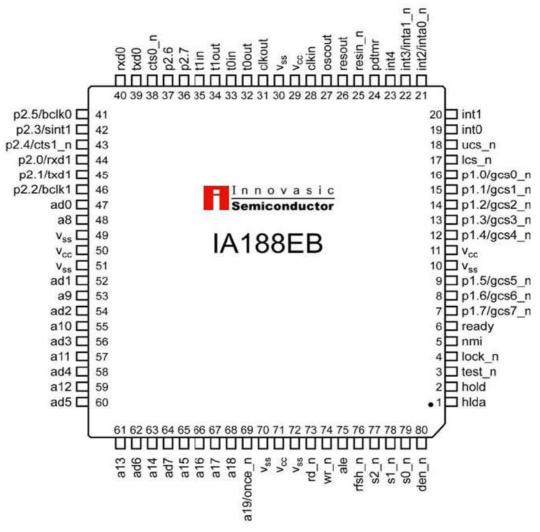

#### 2.1.8 IA188EB 80 LQFP Package

The pinout for the IA188EB 80 LQFP Package is as shown in Figure 8. The corresponding pinout is provided in Table 6.

Figure 8. IA188EB 80-Pin LQFP Package Diagram

| Pin    | Name            |

|--------|-----------------|

| 1      | hlda            |

| 2<br>3 | hold            |

| 3      | test_n          |

| 4      | lock_n          |

| 5      | nmi             |

| 6      | ready           |

| 7      | p1.7/gcs7_n     |

| 8      | p1.6/gcs6_n     |

| 9      | p1.5/gcs5_n     |

| 10     | V <sub>ss</sub> |

| 11     | V <sub>cc</sub> |

| 12     | p1.4/gcs4_n     |

| 13     | p1.3/gcs3_n     |

| 14     | p1.2/gcs2_n     |

| 15     | p1.1/gcs1_n     |

| 16     | p1.0/gcs0_n     |

| 17     | lcs_n           |

| 18     | ucs_n           |

| 19     | int0            |

| 20     | int1            |

# Table 6. IA188EB 80-Pin LQFP Pin Listing

Pin

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

| Name            | Pin | Name            |

|-----------------|-----|-----------------|

| int2/inta0_n    | 41  | p2.5/bclk0      |

| int3/inta1_n    | 42  | p2.3/sint1      |

| int4            | 43  | p2.4/cts1_n     |

| pdtmr           | 44  | p2.0/rxd1       |

| resin_n         | 45  | p2.1/txd1       |

| resout          | 46  | p2.2/bclk1      |

| oscout          | 47  | ad0             |

| clkin           | 48  | a8              |

| V <sub>cc</sub> | 49  | V <sub>ss</sub> |

| V <sub>ss</sub> | 50  | V <sub>cc</sub> |

| clkout          | 51  | V <sub>ss</sub> |

| t0out           | 52  | ad1             |

| t0in            | 53  | a9              |

| t1out           | 54  | ad2             |

| t1in            | 55  | a10             |

| p2.7            | 56  | ad3             |

| p2.6            | 57  | a11             |

| cts0_n          | 58  | ad4             |

| txd0            | 59  | a12             |

| rxd0            | 60  | ad5             |

|                 |     |                 |

| 1               |

|-----------------|

| Name            |

| a13             |

| ad6             |

| a14             |

| ad7             |

| a15             |

| a16             |

| a17             |

| a18             |

| a19/once_n      |

| V <sub>ss</sub> |

| V <sub>cc</sub> |

| V <sub>ss</sub> |

| rd_n            |

| wr_n            |

| ale             |

| rfsh_n          |

| s2_n            |

| s1_n            |

| s0_n            |

| den_n           |

|                 |

|                              |                                   | Pin  |      |      |                                                                                                                                                                                                                                                                                               |  |  |  |

|------------------------------|-----------------------------------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Signal                       | Name                              | PLCC | LQFP | PQFP | Description                                                                                                                                                                                                                                                                                   |  |  |  |

| ale                          | ale                               | 6    | 75   | 38   | <b>a</b> ddress latch <b>e</b> nable. Output. Active High.<br>This signal is used to latch the address<br>information during the address portion of a bus<br>cycle.                                                                                                                           |  |  |  |

| bclk0                        | p2.5/ <b>bclk0</b>                | 54   | 41   | 4    | <b>b</b> aud <b>c</b> lock, Serial Port <b>0</b> . Input. The <b>bclk0</b> pin<br>can be used to provide an alternate clock<br>source for Serial Port 0. The input clock rate<br>cannot be greater than one-half the operating<br>frequency of the IA186EB.                                   |  |  |  |

| bclk1                        | p2.2/ <b>bclk1</b>                | 59   | 46   | 9    | <b>b</b> aud <b>clock</b> , Serial Port <b>1</b> . Input. The <b>bclk1</b> pin<br>can be used to provide an alternate clock<br>source for Serial Port <b>1</b> . The input clock rate<br>cannot be greater than one-half the operating<br>frequency of the IA186EB.                           |  |  |  |

| bhe_n                        | bhe_n                             | 7    | 76   | 39   | byte high enable. Output. Active Low. When<br>bhe_n is asserted (low), it indicates that the<br>bus cycle in progress is transferring data over<br>the upper half of the data bus.                                                                                                            |  |  |  |

| bhe_n is<br>multi-<br>plexed | bhe_n is<br>multi-<br>plexed with |      |      |      | Additionally, <b>bhe_n</b> and <b>ad0</b> encode the following bus information:                                                                                                                                                                                                               |  |  |  |

| with<br>refresh_n            | refresh_n                         |      |      |      | ad0 bhe_n Bus Status                                                                                                                                                                                                                                                                          |  |  |  |

|                              |                                   |      |      |      | 00Word Transfer01Even Byte Transfer10Odd Byte Transfer11Refresh Operation                                                                                                                                                                                                                     |  |  |  |

|                              |                                   |      |      |      | Note: bhe_n is multiplexed with refresh_n.                                                                                                                                                                                                                                                    |  |  |  |

| busy                         | test_n/ <b>busy</b>               | 14   | NA   | NA   | <b>busy</b> . Input. Active High. When the <b>busy</b> input is asserted, it causes the IA186EB to suspend operation during the execution of the Intel 80C187 Numerics Coprocessor instructions. Operation resumes when the pin is sampled low. <i>This applies to the PLCC package only.</i> |  |  |  |

### Table 7. IA186EB Pin/Signal Descriptions (Continued)

|        |                     | Pin  |      |      |                                                                                                                                               |

|--------|---------------------|------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Signal | Name                | PLCC | LQFP | PQFP | Description                                                                                                                                   |

| p1.0   | <b>p1.0</b> /gcs0_n | 28   | 16   | 59   | <b>p</b> ort <b>1</b> , Bit [N] (N = <b>0</b> – <b>7</b> ). Output. Each pin of                                                               |

| p1.1   | <b>p1.1</b> /gcs1_n | 27   | 15   | 58   | Port 1, <b>p1.0–p1.7</b> , can function individually as a                                                                                     |

| p1.2   | <b>p1.2</b> /gcs2_n | 26   | 14   | 57   | general-purpose output line.                                                                                                                  |

| p1.3   | <b>p1.3</b> /gcs3_n | 25   | 13   | 56   |                                                                                                                                               |

| p1.4   | <b>p1.4</b> /gcs4_n | 24   | 12   | 55   |                                                                                                                                               |

| p1.5   | <b>p1.5</b> /gcs5_n | 21   | 9    | 52   |                                                                                                                                               |

| p1.6   | <b>p1.6</b> /gcs6_n | 20   | 8    | 51   |                                                                                                                                               |

| p1.7   | <b>p1.7</b> /gcs7_n | 19   | 7    | 50   |                                                                                                                                               |

| p2.0   | <b>p2.0</b> /rxd1   | 57   | 44   | 7    | <b>p</b> ort <b>2</b> , Bit [ <b>0</b> ]. Input/Output. This pin functions as a general-purpose I/O line.                                     |

| p2.1   | <b>p2.1</b> /txd1   | 58   | 45   | 8    | <b>p</b> ort <b>2</b> , Bit [ <b>1</b> ]. Output. This pin functions as a general-purpose output line.                                        |

| p2.2   | <b>p2.2</b> /bclk1  | 59   | 46   | 9    | <b>p</b> ort <b>2</b> , Bit [ <b>2</b> ]. Input. This pin functions as a general-purpose input line.                                          |

| p2.3   | p2.3/sint1          | 55   | 42   | 5    | <b>p</b> ort <b>2</b> , Bit [ <b>3</b> ]. Output. This pin functions as a general-purpose output line.                                        |

| p2.4   | <b>p2.4</b> /cts1_n | 56   | 43   | 6    | <b>p</b> ort <b>2</b> , Bit [ <b>4</b> ]. Input. This pin functions as a general-purpose input line.                                          |

| p2.5   | <b>p2.5</b> /bclk0  | 54   | 41   | 4    | <b>p</b> ort <b>2</b> , Bit [ <b>5</b> ]. Input. This pin functions as a general-purpose input line.                                          |

| p2.6   | p2.6                | 50   | 37   | 80   | <b>p</b> ort <b>2</b> , Bit [ <b>6</b> ]. Input/Output (open drain). This pin functions as a general-purpose bidirectional input/output line. |

| p2.7   | p2.7                | 49   | 36   | 79   | <b>p</b> ort <b>2</b> , Bit [ <b>7</b> ]. Input/Output (open drain). This pin functions as a general-purpose bidirectional input/output line. |

### Table 8. IA188EB Pin/Signal Descriptions (Continued)

• Power Management Unit

The registers associated with each integrated peripheral are contained within a  $128 \times 16$  register file called the Peripheral Control Block (PCB). The PCB can be located in either memory or I/O space on any 256-byte address boundary.

Table 12 provides a list of the registers associated with the PCB.

| Table 12. | Peripheral Control Block Registers |

|-----------|------------------------------------|

|-----------|------------------------------------|

| PCB    |                      | PCB    |                     | PCB    |            | PCB    |          |

|--------|----------------------|--------|---------------------|--------|------------|--------|----------|

| Offset | Function             | Offset | Function            | Offset | Function   | Offset | Function |

| 00H    | Reserved             | 40H    | Timer2<br>Count     | 80H    | GCS0 Start | C0H    | Reserved |

| 02H    | End Of<br>Interrupt  | 42H    | Timer2<br>Compare   | 82H    | GCS0 Stop  | C2H    | Reserved |

| 04H    | Poll                 | 44H    | Reserved            | 84H    | GCS1 Start | C4H    | Reserved |

| 06H    | Poll Status          | 46H    | Timer2<br>Control   | 86H    | GCS1 Stop  | C6H    | Reserved |

| 08H    | Interrupt<br>Mask    | 48H    | Reserved            | 88H    | GCS2 Start | C8H    | Reserved |

| 0AH    | Priority<br>Mask     | 4AH    | Reserved            | 8AH    | GCS2 Stop  | CAH    | Reserved |

| 0CH    | In-Service           | 4CH    | Reserved            | 8CH    | GCS3 Start | CCH    | Reserved |

| 0EH    | Interrupt<br>Request | 4EH    | Reserved            | 8EH    | GCS3 Stop  | CEH    | Reserved |

| 10H    | Interrupt<br>Status  | 50H    | Port 1<br>Direction | 90H    | GCS4 Start | D0H    | Reserved |

| 12H    | Timer<br>Control     | 52H    | Port 1 Pin          | 92H    | GCS4 Stop  | D2H    | Reserved |

| 14H    | Serial<br>Control    | 54H    | Port 1<br>Control   | 94H    | GCS5 Start | D4H    | Reserved |

| 16H    | INT4<br>Control      | 56H    | Port 1 Latch        | 96H    | GCS5 Stop  | D6H    | Reserved |

| 18H    | INT0<br>Control      | 58H    | Port 2<br>Direction | 98H    | GCS6 Start | D8H    | Reserved |

| 1AH    | INT1<br>Control      | 5AH    | Port 2 Pin          | 9AH    | GCS6 Stop  | DAH    | Reserved |

| 1CH    | INT2<br>Control      | 5CH    | Port 2<br>Control   | 9CH    | GCS7 Start | DCH    | Reserved |

| 1EH    | INT3<br>Control      | 5EH    | Port 2 Latch        | 9EH    | GCS7 Stop  | DEH    | Reserved |

### 4.3 Reference Documents

Additional information on the operation and programming of the 80C186EB/80C188EB can be found in the following Intel publications:

- 80C186EB/80C188EB and 80L186EB/80L188EB 16-Bit High-Integration Embedded Processors (272433-006)

- 80C186EB/80C188EB Microprocessor User's Manual (270830-00n)

# 5. AC Specifications

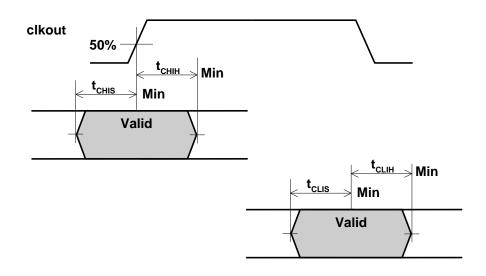

This chapter defines the AC specifications of the IA186EB/IA188EB. Input characteristics are provided in Figure 12 and Tables 13 and 14. Output characteristics are provided in Figure 13 and Tables 15 and 16. Relative timing characteristics are provided in Figure 14 and Table 17. Clock input and clock output timing characteristics are provided in Figure 18 and Tables 18 and 19. Additional timing information is provided in Chapter 7, Bus Timing, and Chapter 8, Instruction Execution Times.

The following test conditions were used to derive the values in Tables 13 - 16: Rev. 0 was tested at 100C and 4.75V; Rev. 2 was tested at 100C and 4.5V.

Figure 12. AC Input Characteristics

IA211080314-13 UNCONTROLLED WHEN PRINTED OR COPIED Page 51 of 85 http://www.Innovasic.com Customer Support: 1-888-824-4184

|                   | _                                  |          |     |       |

|-------------------|------------------------------------|----------|-----|-------|

| Symbol            | Parameter                          | Min      | Max | Units |

| t <sub>LHLL</sub> | ale Rising to ale Falling          | t – 15   | -   | ns    |

| t <sub>AVLL</sub> | Address Valid to ale Falling       | ½t −10   | -   | ns    |

| t <sub>PLLL</sub> | Chip Selects Valid to ale Falling  | ½t –10   | _   | ns    |

| t <sub>LLAX</sub> | Address Hold from ale Falling      | ½t −10   | 1   | ns    |

| t <sub>LLWL</sub> | ale Falling to wr_n Falling        | ½t –15   | -   | ns    |

| t <sub>LLRL</sub> | ale Falling to rd_n Falling        | ½t –15   | -   | ns    |

| t <sub>WHLH</sub> | wr_n Rising to ale Rising          | ½t −10   | 1   | ns    |

| t <sub>AFRL</sub> | Address Float to rd_n Falling      | 0        | 1   | ns    |

| t <sub>RLRH</sub> | rd_n Falling to rd_n Rising        | (2t) – 5 | 1   | ns    |

| t <sub>wLWH</sub> | wr_n Falling to wr_n Rising        | (2t) – 5 | 1   | ns    |

| t <sub>RHAV</sub> | rd_n Rising to Address Active      | t – 15   | 1   | ns    |

| t <sub>WHDX</sub> | Output Data Hold after wr_n Rising | t – 15   | 1   | ns    |

| t <sub>WHPH</sub> | wr_n Rising to Chip Select Rising  | ½t −10   | 1   | ns    |

| t <sub>RHPH</sub> | rd_n Rising to Chip Select Rising  | ½t −10   | 1   | ns    |

| t <sub>PHPL</sub> | cs_n inactive to cs_n active       | ½t −10   | _   | ns    |

| t <sub>ovrh</sub> | once_n Active to resin_n Rising    | t        | _   | ns    |

| t <sub>RHOX</sub> | once_n Hold to resin_n Rising      | t        | _   | Ns    |

## Table 17. Relative Timing Characteristics

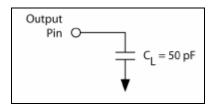

### 5.1 AC Test Conditions

The AC specifications are tested with the 50-pF load shown in Figure 15. Specifications are measured at the  $V_{CC}/2$  crossing point unless otherwise specified.

Figure 15. AC Test Load

# 6. Reset Operation

The IA186EB/IA188EB will perform a reset operation any time the resin\_n pin is active. Figure 18 shows the reset sequence when power is applied to the IA186EB/IA188EB. An external clock connected to clkin must not exceed the  $V_{CC}$  threshold being applied to the processor. This is normally not a problem if the clock driver is supplied with the same  $V_{CC}$  that supplies the processor. When attaching a crystal to the device, resin\_n must remain active until both  $V_{CC}$  and clkout are stable (the length of time is application-specific and depends on the startup characteristics of the crystal circuit). The resin\_n pin is designed to operate correctly using an RC reset circuit, but the designer must ensure that the ramp time for  $V_{CC}$  is not so long that resin\_n is never really sampled at a logic low level when  $V_{CC}$  reaches minimum operating conditions.

*Note:* Failure to assert resin\_n while the device is powering up will result in unpredictable operation.

Figure 19, Warm Reset Timing, shows the timing sequence when resin\_n is applied after  $V_{cc}$  is stable and the device has been operating. Any bus operation that is in progress at the time resin\_n is asserted will terminate immediately.

While resin\_n is active, bus signals lock\_n, a19/once\_n, and a18–a16 are configured as inputs and weakly held high by internal pull-up transistors. Only a19/once\_n can be overdriven to a low-to-enable ONCE Mode.

# 7. Bus Timing

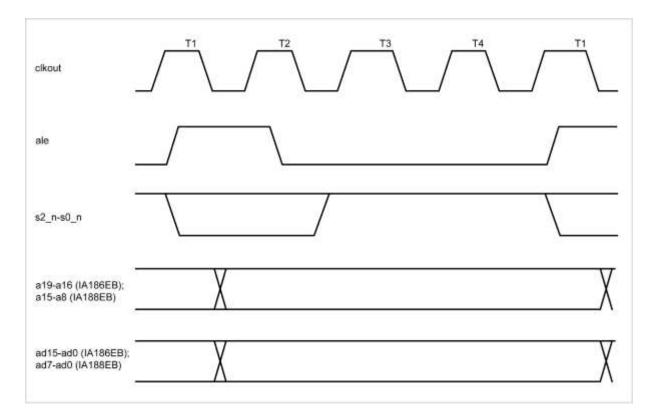

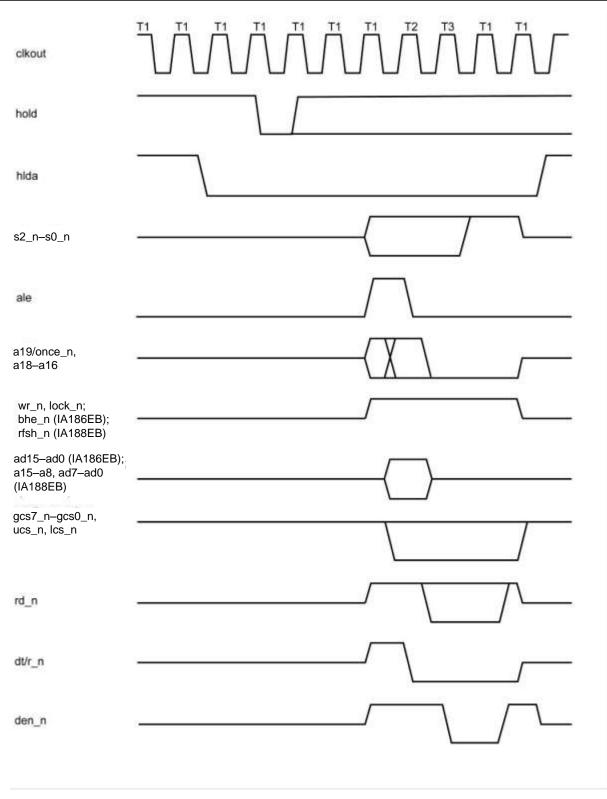

Figures 18 through 26 on the following pages present the various bus cycles that are generated by the processor. The figures show the relationship of the various bus signals to clkout. Together with the information present in AC Characteristics, the figures allow the user to determine all the critical timing analysis needed for a given application.

IA211080314-13 UNCONTROLLED WHEN PRINTED OR COPIED Page 59 of 85

Figure 22. Halt Cycle Timing

#### IA186EB/IA188EB 8-Bit/16-Bit Microcontrollers

# Figure 25. Refresh During Hold Acknowledge Timing

IA211080314-13 UNCONTROLLED WHEN PRINTED OR COPIED Page 67 of 85 http://www.Innovasic.com Customer Support: 1-888-824-4184

| Clock Cycles                   |                  |                |                                       |  |

|--------------------------------|------------------|----------------|---------------------------------------|--|

| Instruction                    | IA186EB          | IA188EB        | Comments                              |  |

| JNS                            | 3/5              | 3/5            | Jump not taken/Jump taken             |  |

| JNZ                            | 3/5              | 3/5            | 1                                     |  |

| JO                             | 3/5              | 3/5            | -                                     |  |

| JP                             | 3/5              | 3/5            | 1                                     |  |

| JPE                            | 3/5              | 3/5            | -                                     |  |

| JPO                            | 3/5              | 3/5            | 1                                     |  |

| JS                             | 3/5              | 3/5            | -                                     |  |

| JZ                             | 3/5              | 3/5            | 1                                     |  |

| LAHF                           | 2                | 2              | _                                     |  |

| LDS                            | 1/24             | 1/33           | register/memory                       |  |

| LEA                            | 3                | 3              | _                                     |  |

| LEAVE                          | 12               | 12             | _                                     |  |

| LES                            | 12               | 32             | _                                     |  |

| LOCK                           | 1                | 1              | _                                     |  |

| LODS                           | 8                | 12             | _                                     |  |

| LODS (repeated <i>n</i> times) | 8+8 <i>n</i>     | 12+12 <i>n</i> | _                                     |  |

| LOOP                           | 3/4              | 3/4            | Loop not taken/Loop taken             |  |

| LOOPE                          | 3/4              | 3/4            | Loop not taken/Loop taken             |  |

| LOOPNE                         | 3/4              | 3/4            |                                       |  |

| LOOPNZ                         | 3/4              | 3/4            | -                                     |  |

| LOOPZ                          | 3/4              | 3/4            | -                                     |  |

| MOV Accumulator to memory      | 5                | 8/12           | 8-bit/16-bit                          |  |

| MOV Immediate to register      | 1                | 1              | -                                     |  |

| MOV Immediate to               | 1/5              | 1/12           | register/memory                       |  |

| register/memory                |                  | .,             |                                       |  |

| MOV Memory to accumulator      | 5                | 8/12           | 8-bit/16-bit                          |  |

| MOV Register to                | 2/5              | 2/20           | register/memory                       |  |

| Register/Memory                |                  |                | , , , , , , , , , , , , , , , , , , , |  |

| MOV Register/memory to         | 2/5              | 2/20           |                                       |  |

| register                       |                  |                |                                       |  |

| MOV Register/memory to         | 2/5              | 2/20           |                                       |  |

| segment register               | - / <del>-</del> |                | _                                     |  |

| MOV Segment register to        | 2/5              | 2/20           |                                       |  |

| register/memory                | 0.4              |                |                                       |  |

| MOVS                           | 24               | 32             | -                                     |  |

| MOVS (repeated <i>n</i> times) | 24+24n           | 32+32n         | -                                     |  |

| MUL Memory-Byte                | 16               | 20             | -                                     |  |

| MUL Memory-Word                | 15               | 25             | -                                     |  |

| MUL Register-Byte              | 5                | 5              | -                                     |  |

| MUL Register-Word              | 5                | 5              |                                       |  |

| NEG                            | 1/32             | 1/15           | register/memory                       |  |

| NOP                            | 1                | 1              | _                                     |  |

| NOT                            | 1/24             | 1/24           | register/memory                       |  |

| OR Immediate to accumulator    | 1                | 1              | -                                     |  |

## Table 21. Instruction Set Timing (Continued)

## Table 21. Instruction Set Timing (Continued)

|                                | Clock Cycles  |                    |                 |  |

|--------------------------------|---------------|--------------------|-----------------|--|

| Instruction                    | IA186EB       | IA188EB            | Comments        |  |

| OR Immediate to                | 1/32          | 1/32               | register/memory |  |

| register/memory                |               |                    |                 |  |

| OR Register/memory and         | 1/32          | 1/24               |                 |  |

| register to either             |               |                    |                 |  |

| OUT Fixed port                 | 5             | 8/12               | 8-bit/16-bit    |  |

| OUT Variable port              | 5             | 12                 | _               |  |

| OUTS                           | 8             | 12/20              | 8-bit/16-bit    |  |

| OUTS (repeated <i>n</i> times) | 8+8 <i>n</i>  | 12/20+12/20n       | 8-bit/16-bit    |  |

| POP Memory                     | 10            | 20                 | _               |  |

| POP Register                   | 10            | 12                 | _               |  |

| POP Segment register           | 16            | 12                 | _               |  |

| POPA                           | 80            | 93                 | _               |  |

| POPF                           | 13            | 13                 | _               |  |

| PUSH Immediate                 | 8             | 12                 | _               |  |

| PUSH Memory                    | 15            | 28                 | _               |  |

| PUSH Register                  | 4             | 12                 | _               |  |

| PUSH Segment register          | 4             | 12                 | _               |  |

| PUSHA                          | 64            | 72                 | _               |  |

| PUSHF                          | 4             | 16                 | _               |  |

| RET Inter-segment              | 14            | 21                 | _               |  |

| RET Inter-segment adding       | 25            | 21                 | _               |  |

| immediate to SP                |               |                    |                 |  |

| RET Within segment             | 14            | 13                 | _               |  |

| RET Within segment adding      | 16            | 13                 | _               |  |

| immediate to SP                |               |                    |                 |  |

| ROL Register/Memory by 1       | 1/8           | 1/16               | register/memory |  |

| ROL Register/Memory by CL      | 1/8           | 1/16               |                 |  |

| ROL Register/Memory by         | 1/8           | 1/24               |                 |  |

| Count                          |               |                    |                 |  |

| ROR Register/Memory by 1       | 1/8           | 1/16               |                 |  |

| ROR Register/Memory by CL      | 1/8           | 1/16               |                 |  |

| ROR Register/Memory by         | 1/8           | 1/24               |                 |  |

| Count                          |               |                    |                 |  |

| SAHF                           | 2             | 2                  | _               |  |

| SBB Immediate from             | 1             | 1                  | _               |  |

| accumulator                    |               |                    |                 |  |

| SBB Immediate from             | 1/15          | 1/28               | register/memory |  |

| register/memory                |               |                    |                 |  |

| SBB Register/memory and        | 1/11          | 1/40               | register/memory |  |

| register to either             |               | 0/// 2             |                 |  |

| SCAS                           | 11            | 8/12               | 8-bit/16-bit    |  |

| SCAS (repeated <i>n</i> times) | 11+8 <i>n</i> | 8/12+8/12 <i>n</i> | 8-bit/16-bit    |  |

| SHL Register/Memory by 1       | 5             | 1/32               | register/memory |  |

#### **Innovasic Part Number Cross-Reference**

Tables 22 through 24 cross-reference the Innovasic part number with the corresponding Intel part number.

#### Table 22. Innovasic Part Number Cross-Reference for the PLCC

| Innovasic Part Number      | Intel Part Number | Package Type | Temperature Grades |

|----------------------------|-------------------|--------------|--------------------|

| IA186EBPLC84IR2            | EE80C186EB25      | 84-Pin PLCC  | Commercial and     |

| lead free (RoHS-compliant) | EE80C186EB20      |              | industrial         |

|                            | EN80C186EB25      |              |                    |

|                            | EN80C186EB20      |              |                    |

|                            | EN80C186EB13      |              |                    |

|                            | N80C186EB25       |              |                    |

|                            | N80C186EB20       |              |                    |

|                            | N80C186EB13       |              |                    |

|                            | TN80C186EB25      |              |                    |

|                            | TN80C186EB20      |              |                    |

|                            | TN80C186EB13      |              |                    |

|                            | N80L186EB16       |              |                    |

|                            | N80L186EB13       |              |                    |

|                            | TN80L186EB16      |              |                    |

|                            | TN80L186EB13      |              |                    |

|                            | EN80L186EB13      |              |                    |

| IA188EBPLC84IR2            | EE80C188EB25      | 84-Pin PLCC  | Commercial and     |

| lead free (RoHS-compliant) | EE80C188EB20      |              | industrial         |

|                            | EE80C188EB13      |              |                    |

|                            | EN80C188EB25      |              |                    |

|                            | EN80C188EB20      |              |                    |

|                            | EN80C188EB13      |              |                    |

|                            | N80C188EB25       |              |                    |

|                            | N80C188EB20       |              |                    |

|                            | N80C188EB13       |              |                    |

|                            | TN80C188EB25      |              |                    |

|                            | TN80C188EB20      |              |                    |

|                            | TN80C188EB13      |              |                    |

|                            | EE80L188EB16      |              |                    |

|                            | EN80L188EB13      |              |                    |

|                            | N80L188EB16       |              |                    |

|                            | N80L188EB13       |              |                    |

|                            | TN80L188EB16      |              |                    |

|                            | TN80L188EB13      |              |                    |

| Date              | Revision | Description                                                              | Page(s)    |

|-------------------|----------|--------------------------------------------------------------------------|------------|

| September 4, 2009 | 08       | Added a note to Table 12 regarding the Step ID register.                 | 50         |

| February 25, 2011 | 09       | Elimination of pages with SnPb lead plating options                      | 74-76      |

| March 23, 2011    | 10       | Updated Instruction Set Timing Table to incorporate DIV and IDIV values. | 70         |

| June 12, 2011     | 11       | Added Errata 11 and 12.                                                  | 77, 78, 81 |

| July 5, 2011      | 12       | Added Errata 13.                                                         | 78, 82     |

| July 10, 2011     | 13       | Added Errata 14.                                                         | 78, 82     |