Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | ОТР                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 6x12b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c773-e-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

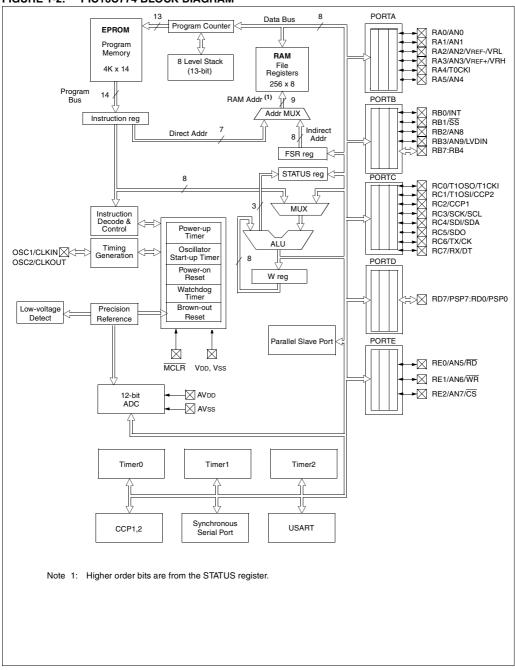

FIGURE 1-2: PIC16C774 BLOCK DIAGRAM

## 2.0 MEMORY ORGANIZATION

There are two memory blocks in each of these PICmicro® microcontrollers. Each block (Program Memory and Data Memory) has its own bus so that concurrent access can occur.

Additional information on device memory may be found in the  $PICmicro^{TM}$  Mid-Range Reference Manual, (DS33023).

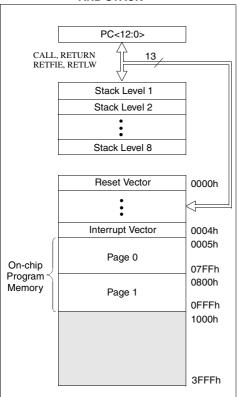

## 2.1 Program Memory Organization

The PIC16C77X PICmicros have a 13-bit program counter capable of addressing an 8K x 14 program memory space. Each device has 4K x 14 words of program memory. Accessing a location above the physically implemented address will cause a wraparound.

The reset vector is at 0000h and the interrupt vector is at 0004h.

FIGURE 2-1: PROGRAM MEMORY MAP AND STACK

## 2.2 <u>Data Memory Organization</u>

The data memory is partitioned into multiple banks which contain the General Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank select bits.

| RP1 | RP0 | (STATUS<6:5>) |

|-----|-----|---------------|

|     |     |               |

$= 00 \rightarrow Bank0$

$= 01 \rightarrow Bank1$

$= 10 \rightarrow Bank2$

= 11 → Bank3

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are General Purpose Registers, implemented as static RAM. All implemented banks contain special function registers. Some "high use" special function registers from one bank may be mirrored in another bank for code reduction and quicker access.

## 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly, or indirectly through the File Select Register FSR.

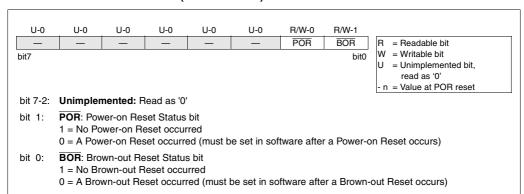

## 2.2.2.8 PCON REGISTER

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external MCLR Reset or WDT Reset. Those devices with brown-out detection circuitry contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

## FIGURE 2-10: PCON REGISTER (ADDRESS 8Eh)

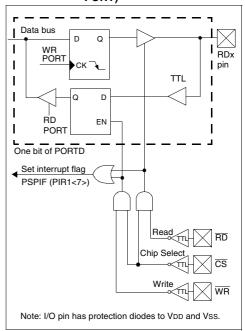

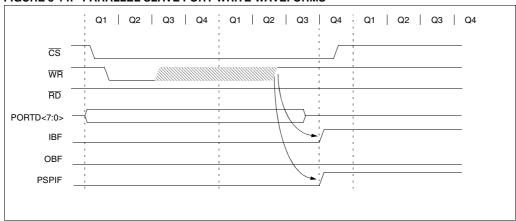

## 3.6 Parallel Slave Port

The Parallel Slave Port is implemented on the 40/44-pin devices only.

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{\text{RD}}$  control input pin RE0/ $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  control input pin RE1/ $\overline{\text{WR}}$ .

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/ $\overline{RD}$  to be the  $\overline{RD}$  input, RE1/ $\overline{WR}$  to be the  $\overline{WR}$  input and RE2/ $\overline{CS}$  to be the  $\overline{CS}$  (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The configuration bits, PCFG3:PCFG0 (ADCON1<3:0>) must be configured to make pins RE2:RE0 as digital I/O.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low.

FIGURE 3-13: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

FIGURE 3-14: PARALLEL SLAVE PORT WRITE WAVEFORMS

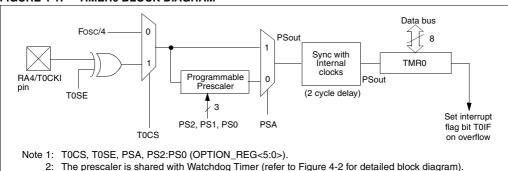

## 4.0 TIMERO MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- · Readable and writable

- · Internal or external clock select

- · Edge select for external clock

- · 8-bit software programmable prescaler

- Interrupt on overflow from FFh to 00h

Figure 4-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PICmicro™ Mid-Range Reference Manual, (DS33023).

## 4.1 Timer0 Operation

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit TOCS (OPTION\_REG<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/TOCKI. The incrementing edge is determined by the Timer0 Source Edge Select bit TOSE (OPTION\_REG<4>). Clearing bit TOSE selects the rising edge. Restrictions on the external clock input are discussed in below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the PICmicro™ Mid-Range Reference Manual, (DS33023).

## 4.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 4-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

## FIGURE 4-1: TIMERO BLOCK DIAGRAM

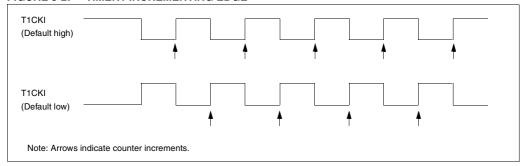

#### 5.1.1 TIMER1 COUNTER OPERATION

In this mode, Timer1 is being incremented via an external source. Increments occur on a rising edge. After Timer1 is enabled in counter mode, the module must first have a falling edge before the counter begins to increment.

#### FIGURE 5-2: **TIMER1 INCREMENTING EDGE**

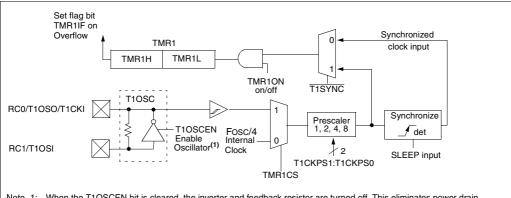

#### FIGURE 5-3: **TIMER1 BLOCK DIAGRAM**

Note 1: When the T1OSCEN bit is cleared, the inverter and feedback resistor are turned off. This eliminates power drain.

## 8.2.13 ACKNOWLEDGE SEQUENCE TIMING

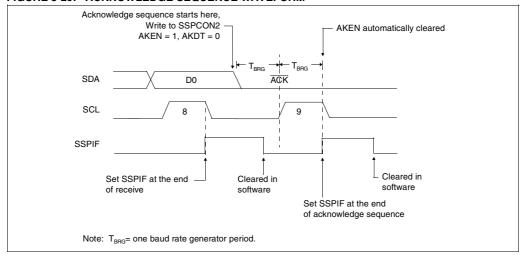

An acknowledge sequence is enabled by setting the acknowledge sequence enable bit, AKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the acknowledge data bit is presented on the SDA pin. If the user wishes to generate an acknowledge, then the AKDT bit should be cleared. If not, the user should set the AKDT bit before starting an acknowledge sequence. The baud rate generator then counts for one rollover period (T<sub>BRG</sub>), and the SCL pin is de-asserted (pulled high). When the SCL pin is sampled high (clock arbitration), the baud

rate generator counts for  $T_{BRG}$ . The SCL pin is then pulled low. Following this, the AKEN bit is automatically cleared, the baud rate generator is turned off, and the SSP module then goes into IDLE mode. (Figure 8-29)

### 8.2.13.13 WCOL STATUS FLAG

If the user writes the SSPBUF when an acknowledege sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

FIGURE 8-29: ACKNOWLEDGE SEQUENCE WAVEFORM

## FIGURE 8-30: ACKNOWLEDGE FLOWCHART Idle mode Set AKEN Force SCL = 0 BRG Yes rollover? No SCL = 0? Force SCL = 0, Clear AKEN, Set SSPIF SCL = 0? Reset BRG Yes Drive AKDT bit No (SSPCON2<5>) onto SDA pin, Load BRG with SSPADD<6:0>, start count. No AKDT = 1? Yes No BRG Yes SDA = 1? Force SCL = 1 Bus collision detected, Set BCLIF, Release SCL, Clear AKEN SCL = 1? (Clock Arbitration) Load BRG with SSPADD <6:0>, start count.

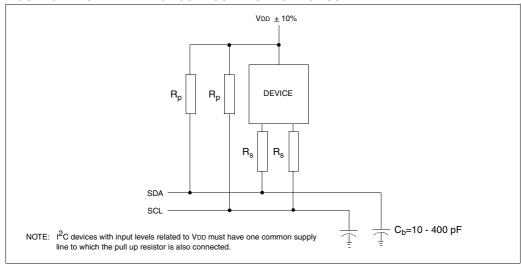

# 8.3 Connection Considerations for I<sup>2</sup>C Bus

For standard-mode  $I^2C$  bus devices, the values of resistors  ${\it R_p\,R_s}$  in Figure 8-42 depends on the following parameters

- · Supply voltage

- · Bus capacitance

- Number of connected devices (input current + leakage current).

The supply voltage limits the minimum value of resistor  $R_p$  due to the specified minimum sink current of 3 mA at Vol max = 0.4V for the specified output stages. For

example, with a supply voltage of VDD =  $5V\pm10\%$  and VOL max = 0.4V at 3 mA, R<sub>p min</sub> = (5.5-0.4)/0.003 = 1.7 k $\Omega$ . VDD as a function of  $\emph{R}_p$  is shown in Figure 8-42. The desired noise margin of 0.1VDD for the low level limits the maximum value of  $\emph{R}_s$ . Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections, and pins. This capacitance limits the maximum value of  ${\it R}_{\it p}$  due to the specified rise time (Figure 8-42).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register, and controls the slew rate of the I/O pins when in I<sup>2</sup>C mode (master or slave).

## FIGURE 8-42: SAMPLE DEVICE CONFIGURATION FOR I<sup>2</sup>C BUS

# 9.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI). The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc.

The USART can be configured in the following modes:

- · Asynchronous (full duplex)

- · Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>), and bits TRISC<7:6>, have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

## FIGURE 9-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

| R/W-0        | R/W-0                                   | R/W-0        | R/W-0       | U-0        | R/W-0               | R-1  | R/W-0        |                                                          |

|--------------|-----------------------------------------|--------------|-------------|------------|---------------------|------|--------------|----------------------------------------------------------|

| CSRC<br>bit7 | TX9                                     | TXEN         | SYNC        |            | BRGH                | TRMT | TX9D<br>bit0 | R = Readable bit W = Writable bit U = Unimplemented bit, |

|              |                                         |              |             |            |                     |      |              | read as '0'                                              |

| bit 7:       | CSRC: Clo                               | ole Couran   | Coloot bit  |            |                     |      |              | - n =Value at POR reset                                  |

| DIL 7.       |                                         |              | Select bit  |            |                     |      |              |                                                          |

|              | Asynchron<br>Don't care                 |              |             |            |                     |      |              |                                                          |

|              | Synchrono                               |              |             |            |                     |      |              |                                                          |

|              | 1 = Master<br>0 = Slave r               |              |             |            | illy from BR<br>ce) | (G)  |              |                                                          |

| bit 6:       | <b>TX9</b> : 9-bit 1                    |              |             |            |                     |      |              |                                                          |

|              | 0 = Selects                             |              |             |            |                     |      |              |                                                          |

| bit 5:       | TXEN: Trai                              |              | ole bit     |            |                     |      |              |                                                          |

|              | 1 = Transm<br>0 = Transm                |              |             |            |                     |      |              |                                                          |

|              | Note: SRE                               | N/CREN o     | verrides TX | EN in SY   | NC mode.            |      |              |                                                          |

| bit 4:       | SYNC: US                                |              |             |            |                     |      |              |                                                          |

|              | 1 = Synchr<br>0 = Asynch                |              |             |            |                     |      |              |                                                          |

| bit 3:       | Unimplem                                |              |             |            |                     |      |              |                                                          |

| bit 2:       | BRGH: Hig                               |              |             | oit        |                     |      |              |                                                          |

| Z. Z.        | Asynchron                               | •            | 00.001 2    |            |                     |      |              |                                                          |

|              | 1 = High sp                             |              |             |            |                     |      |              |                                                          |

|              | 0 = Low sp                              | eed          |             |            |                     |      |              |                                                          |

|              | Synchrono<br>Unused in                  |              |             |            |                     |      |              |                                                          |

| bit 1:       | TRMT: Trans<br>1 = TSR er<br>0 = TSR fu | mpty         | Register S  | tatus bit  |                     |      |              |                                                          |

| bit 0:       | <b>TX9D</b> : 9th                       | bit of trans | mit data. C | an be pari | ity bit.            |      |              |                                                          |

|              |                                         |              |             | 20 pan     | -, ~                |      |              |                                                          |

## PIC16C77X

## 9.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 9-6. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc.

The USART module has a special provision for multi-processor communication. When the RX9 bit is set in the RCSTA register, 9-bits are received and the ninth bit is placed in the RX9D status bit of the RSTA register. The port can be programmed such that when the stop bit is received, the serial port interrupt will only be activated if the RX9D bit = 1. This feature is enabled by setting the ADDEN bit RCSTA<3> in the RCSTA register. This feature can be used in a multi-processor system as follows:

A master processor intends to transmit a block of data to one of many slaves. It must first send out an address byte that identifies the target slave. An address byte is identified by the RX9D bit being a '1' (instead of a '0' for a data byte). If the ADDEN bit is set in the slave's RCSTA register, all data bytes will be ignored. However, if the ninth received bit is equal to a '1', indicating that the received byte is an address, the slave will be interrupted and the contents of the RSR register will be transferred into the receive buffer. This allows the slave to be interrupted only by addresses, so that the slave can examine the received byte to see if it is addressed. The addressed slave will then clear its ADDEN bit and prepare to receive data bytes from the master.

When ADDEN is set, all data bytes are ignored. Following the STOP bit, the data will not be loaded into the receive buffer, and no interrupt will occur. If another byte is shifted into the RSR register, the previous data byte will be lost.

The ADDEN bit will only take effect when the receiver is configured in 9-bit mode.

The receiver block diagram is shown in Figure 9-6.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

## 9.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

Steps to follow when setting up an Asynchronous Reception with Address Detect Enabled:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- If interrupts are desired, then set enable bit RCIE.

- · Set bit RX9 to enable 9-bit reception.

- · Set ADDEN to enable address detect.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register, to determine if the device is being addressed.

- If any error occurred, clear the error by clearing enable bit CREN.

- If the device has been addressed, clear the ADDEN bit to allow data bytes and address bytes to be read into the receive buffer, and interrupt the CPU.

## FIGURE 10-2: REFCON: VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0                                                                                                                                                                                         | R/W-0                                      | R/W-0        | R/W-0         | U-0        | U-0      | U-0       | U-0      |                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------|---------------|------------|----------|-----------|----------|------------------------------------------------------------|

| VRHEN                                                                                                                                                                                         | VRLEN                                      | VRHOEN       | VRLOEN        | _          | _        | _         | _        | R = Readable bit W = Writable bit                          |

| bit7                                                                                                                                                                                          |                                            |              |               |            |          |           | bit0     | U = Unimplemented bit, read as '0' - n =Value at POR reset |

| bit 7: VRHEN: Voltage Reference High Enable bit (VRH = 4.096V)  1 = Enabled, powers up reference generator  0 = Disabled, powers down reference generator if unused by LVD, BOR, or VRL       |                                            |              |               |            |          |           |          |                                                            |

| bit 6: VRLEN: Voltage Reference Low Enable bit (VRL = 2.048V)  1 = Enabled, powers up reference generator  0 = Disabled, powers down reference generator if unused by LVD, BOR, or VRH        |                                            |              |               |            |          |           |          |                                                            |

| bit 5: VRHOEN: High Voltage Reference Output Enable bit  1 = Enabled, VRH analog reference is presented on RA3 if enabled (VRHEN = 1)  0 = Disabled, analog reference is used internally only |                                            |              |               |            |          |           |          |                                                            |

| bit 4:                                                                                                                                                                                        | VRLOEN: Lo<br>1 = Enabled,<br>0 = Disabled | , VRL analoເ | g reference i | s presente | d on RA2 | if enable | d (VRLEN | I = 1)                                                     |

## 10.1 Bandgap Voltage Reference

bit 3-0: Unimplemented: Read as '0'

The bandgap module generates a stable voltage reference of 1.22V over a range of temperatures and device supply voltages. This module is enabled anytime any of the following are enabled:

- · Brown-out Reset

- Low-voltage Detect

- Either of the internal analog references (VRH, VRL)

Whenever the above are all disabled, the bandgap module is disabled and draws no current.

## 10.2 Internal VREF for A/D Converter

The bandgap output voltage is used to generate two stable references for the A/D converter module. These references are enabled in software to provide the user with the means to turn them on and off in order to minimize current consumption. Each reference can be individually enabled.

The 4.096V reference (VRH) is enabled with control bit VRHEN (REFCON<7>). When this bit is set, the gain amplifier is enabled. After a specified start-up time a stable reference of 4.096V is generated and can be used by the A/D converter as the VRH input.

The 2.048V reference (VRL) is enabled by setting control bit VRLEN (REFCON<6>). When this bit is set, the gain amplifier is enabled. After a specified start up time a stable reference of 2.048V is generated and can be used by the A/D converter as the VRL input.

Each voltage reference can source/sink up to 5 mA of current.

Each reference, if enabled, can be presented on an external pin by setting the VRHOEN (high reference output enable) or VRLOEN (low reference output enable) control bit. If the reference is not enabled, the VRHOEN and VRLOEN bits will have no effect on the corresponding pin. The device specific pin can then be used as general purpose I/O.

Note: If VRH or VRL is enabled and the other reference (VRL or VRH), the BOR, and the LVD modules are not enabled, the bandgap will require a start-up time of no more than 50 μs before the bandgap reference is stable. Before using the internal VRH or VRL reference, ensure that the bandgap reference voltage is stable by monitoring the BGST bit in the LVDCON register. The voltage references will not be reliable until the bandgap is stable as shown by BGST being set.

# 12.0 SPECIAL FEATURES OF THE CPU

These PICmicro devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- · Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- · Low-voltage detection

- SLEEP

- · Code protection

- · ID locations

- · In-circuit serial programming

These devices have a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up type resets only (POR, BOR), designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

Additional information on special features is available in the PICmicro™ Mid-Range Reference Manual, (DS33023).

## 12.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

Some of the core features provided may not be necessary to each application that a device may be used for. The configuration word bits allow these features to be configured/enabled/disabled as necessary. These features include code protection, brown-out reset and its trippoint, the power-up timer, the watchdog timer and the devices oscillator mode. As can be seen in Figure 12-1, some additional configuration word bits have been provided for brown-out reset trippoint selection.

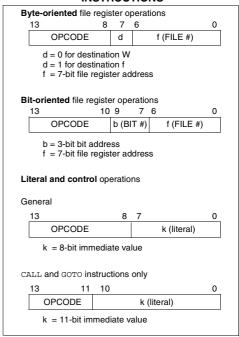

## 13.0 INSTRUCTION SET SUMMARY

Each PIC16CXXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 13-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 13-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

TABLE 13-1 OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                        |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                               |

| W     | Working register (accumulator)                                                                                                                                     |

| b     | Bit address within an 8-bit file register                                                                                                                          |

| k     | Literal field, constant data or label                                                                                                                              |

| x     | Don't care location (= 0 or 1) The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                       |

| PC    | Program Counter                                                                                                                                                    |

| TO    | Time-out bit                                                                                                                                                       |

| PD    | Power-down bit                                                                                                                                                     |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- · Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu s$ . If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu s$ .

Table 13-2 lists the instructions recognized by the MPASM assembler.

Figure 13-1 shows the general formats that the instructions can have.

Note: To maintain upward compatibility with future PIC16CXXX products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

**0xhh**

where h signifies a hexadecimal digit.

## FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

A description of each instruction is available in the  $PICmicro^{TM}$  Mid-Range Reference Manual, (DS33023).

## 14.0 DEVELOPMENT SUPPORT

## 14.1 Development Tools

The PICmicro® microcontrollers are supported with a full range of hardware and software development tools:

- MPLAB™ -ICE Real-Time In-Circuit Emulator

- ICEPIC™ Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- SIMICE

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB™ SIM Software Simulator

- MPLAB-C17 (C Compiler)

- Fuzzy Logic Development System (fuzzyTECH<sup>®</sup>-MP)

- KEELOQ<sup>®</sup> Evaluation Kits and Programmer

# 14.2 MPLAB-ICE: High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers (MCUs). MPLAB-ICE is supplied with the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support all new Microchip microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x or Windows 95 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE is available in two versions. MPLAB-ICE 1000 is a basic, low-cost emulator system with simple trace capabilities. It shares processor modules with the MPLAB-ICE 2000. This is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems will operate across the entire operating speed reange of the PICmicro MCU.

## 14.3 <u>ICEPIC: Low-Cost PICmicro</u> In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC12CXXX, PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 386 through Pentium™ based machines under Windows 3.x, Windows 95, or Windows NT environment. ICEPIC features real time, non-intrusive emulation.

## 14.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices. It can also set configuration and code-protect bits in this mode.

## 14.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, low-cost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923, PIC16C924 and PIC17C756 may be supported with an adapter socket. PICSTART Plus is CE compliant.

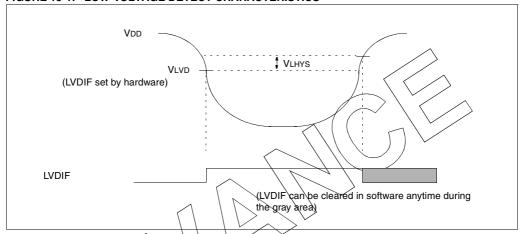

FIGURE 15-1: LOW-VOLTAGE DETECT CHARACTERISTICS

TABLE 15-3 ELECTRICAL CHARACTER STICS: LVD

|         |                                         | Standard Opera    | ating Condit | ione (u | nless (  | therwi  | se stater   | 1)                          |

|---------|-----------------------------------------|-------------------|--------------|---------|----------|---------|-------------|-----------------------------|

|         |                                         | Operating temper  |              |         |          |         | for industr |                             |

| DC CHAI | RACTERISTICS                            | Operating tempe   |              | °C      |          |         | for comme   |                             |

|         |                                         | Operating voltage | -            | -       |          |         |             | on 15.1 and Section 15.2.   |

| Barra   | $\overline{}$                           | porating voitage  | le voo range | uo uco  | CIIDCA I | 11 00 3 | pec occin   | 011 10:1 una Occiloti 10:2: |

| Param   | Charact                                 | eristic           | Symbol       | Min     | Typ†     | Max     | Units       | Conditions                  |

| No.     |                                         | <u>/</u>          | -            |         |          |         |             |                             |

| D420    | LVD Voltage                             | LVV = 0100        |              | 2.5     | 2.58     | 2.66    | V           |                             |

| \       |                                         | LVV = 0101        |              | 2.7     | 2.78     | 2.86    | V           |                             |

| \       |                                         | LVV = 0110        |              | 2.8     | 2.89     | 2.98    | V           |                             |

| \       |                                         | LVV = 0111        |              | 3.0     | 3.1      | 3.2     | V           |                             |

|         |                                         | LVV = 1000        |              | 3.3     | 3.41     | 3.52    | V           |                             |

|         |                                         | LVV = 1001        |              | 3.5     | 3.61     | 3.72    | V           |                             |

|         |                                         | LVV = 1010        |              | 3.6     | 3.72     | 3.84    | V           |                             |

|         |                                         | LVV = 1011        |              | 3.8     | 3.92     | 4.04    | V           |                             |

|         |                                         | LVV = 1100        |              | 4.0     | 4.13     | 4.26    | V           |                             |

|         |                                         | LVV = 1101        |              | 4.2     | 4.33     | 4.46    | V           |                             |

|         |                                         | LVV = 1110        |              | 4.5     | 4.64     | 4.78    | V           |                             |

| D421    | Supply Current                          |                   | ΔİLVD        | _       | 10       | 20      | μΑ          |                             |

| D422*   | 122* LVD Voltage Drift Temperature      |                   | TCVout       | _       | 15       | 50      | ppm/°C      |                             |

|         | coefficient                             |                   |              |         |          |         |             |                             |

| D423*   | D423* LVD Voltage Drift with respect to |                   | ΔVLVD/       | _       | _        | 50      | μV/V        |                             |

|         | VDD Regulation                          |                   |              |         |          |         |             |                             |

| D424*   | Low-voltage Detec                       | t Hysteresis      | VLHYS        | TBD     | _        | 100     | mV          |                             |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Production tested at Tamb = 25°C. Specifications over temp limits ensured by characterization.

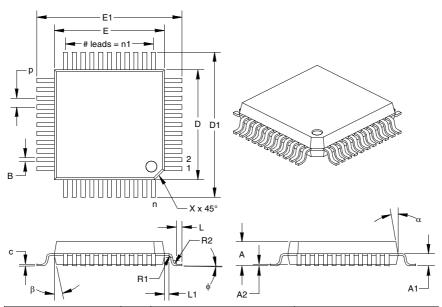

## 17.9 K04-071 44-Lead Plastic Quad Flatpack (PQ) 10x10x2 mm Body, 1.6/0.15 mm Lead Form

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                   |                |       | INCHES |       | MI    | LLIMETERS | *     |

|-------------------------|----------------|-------|--------|-------|-------|-----------|-------|

| Dimension Limits        |                | MIN   | NOM    | MAX   | MIN   | NOM       | MAX   |

| Pitch                   | р              |       | 0.031  |       |       | 0.80      |       |

| Number of Pins          | n              |       | 44     |       |       | 44        |       |

| Pins along Width        | n1             |       | 11     |       |       | 11        |       |

| Overall Pack. Height    | Α              | 0.079 | 0.086  | 0.093 | 2.00  | 2.18      | 2.35  |

| Shoulder Height         | A1             | 0.032 | 0.044  | 0.056 | 0.81  | 1.11      | 1.41  |

| Standoff                | A2             | 0.002 | 0.006  | 0.010 | 0.05  | 0.15      | 0.25  |

| Shoulder Radius         | R1             | 0.005 | 0.005  | 0.010 | 0.13  | 0.13      | 0.25  |

| Gull Wing Radius        | R2             | 0.005 | 0.012  | 0.015 | 0.13  | 0.30      | 0.38  |

| Foot Length             | L              | 0.015 | 0.020  | 0.025 | 0.38  | 0.51      | 0.64  |

| Foot Angle              | ф              | 0     | 3.5    | 7     | 0     | 3.5       | 7     |

| Radius Centerline       | L1             | 0.011 | 0.016  | 0.021 | 0.28  | 0.41      | 0.53  |

| Lead Thickness          | С              | 0.005 | 0.007  | 0.009 | 0.13  | 0.18      | 0.23  |

| Lower Lead Width        | В <sup>†</sup> | 0.012 | 0.015  | 0.018 | 0.30  | 0.37      | 0.45  |

| Outside Tip Length      | D1             | 0.510 | 0.520  | 0.530 | 12.95 | 13.20     | 13.45 |

| Outside Tip Width       | E1             | 0.510 | 0.520  | 0.530 | 12.95 | 13.20     | 13.45 |

| Molded Pack. Length     | D <sup>‡</sup> | 0.390 | 0.394  | 0.398 | 9.90  | 10.00     | 10.10 |

| Molded Pack. Width      | E <sup>‡</sup> | 0.390 | 0.394  | 0.398 | 9.90  | 10.00     | 10.10 |

| Pin 1 Corner Chamfer    | Χ              | 0.025 | 0.035  | 0.045 | 0.635 | 0.89      | 1.143 |

| Mold Draft Angle Top    | α              | 5     | 10     | 15    | 5     | 10        | 15    |

| Mold Draft Angle Bottom | β              | 5     | 12     | 15    | 5     | 12        | 15    |

Controlling Parameter.

<sup>&</sup>lt;sup>†</sup> Dimension "B" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B."

<sup>&</sup>lt;sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E." JEDEC equivalent:MS-022 AB

| INDEX                                             | С                                             |        |

|---------------------------------------------------|-----------------------------------------------|--------|

| A                                                 | Capture (CCP Module)                          | 48     |

|                                                   | Block Diagram                                 | 48     |

| A/D                                               | CCP Pin Configuration                         |        |

| A/D Converter Enable (ADIE Bit)                   | CCPR1H:CCPR1L Registers                       | 48     |

| A/D Converter Flag (ADIF Bit)                     | Changing Between Capture Prescalers           | 48     |

| ADCONG Register                                   | Software Interrupt                            | 48     |

| ADCON1 Register                                   | Timer1 Mode Selection                         |        |

| ADRES Register                                    | Capture/Compare/PWM (CCP)                     |        |

| Analog Port Pins                                  | CCP1                                          |        |

| Block Diagram120 Configuring Analog Port119       | CCP1CON Register                              |        |

| Conversion time                                   | CCPR1H Register                               |        |

| Conversions                                       | CCPR1L Register                               |        |

| converter characteristics                         | Enable (CCP1IE Bit)                           |        |

| Faster Conversion - Lower Resolution Tradeoff 125 | Flag (CCP1IF Bit)                             |        |

| Internal Sampling Switch (Rss) Impedence          | RC2/CCP1 Pin                                  | , -    |

| Operation During Sleep126                         | CCP2                                          |        |

| Sampling Requirements123                          | CCP2CON Register                              |        |

| Sampling Time                                     | CCPR2H Register                               |        |

| Source Impedance                                  | CCPR2L Register                               |        |

| Special Event Trigger (CCP)49                     | Enable (CCP2IE Bit)                           |        |

| A/D Conversion Clock121                           | Flag (CCP2IF Bit)<br>RC1/T1OSI/CCP2 Pin       |        |

| ACK64                                             | Interaction of Two CCP Modules                |        |

| Acknowledge Data bit, AKD56                       | Timer Resources                               |        |

| Acknowledge Pulse64                               | CCP1CON                                       |        |

| Acknowledge Sequence Enable bit, AKE56            | CCP1CON Register                              |        |

| Acknowledge Status bit, AKS56                     | CCP1M3:CCP1M0 Bits                            |        |

| ADCON0 Register117                                | CCP1X:CCP1Y Bits                              |        |

| ADCON1 Register117, 118                           | CCP2CON                                       |        |

| ADRES117                                          | CCP2CON Register                              |        |

| ADRES Register 13, 14, 117, 126                   | CCP2M3:CCP2M0 Bits                            |        |

| AKD56                                             | CCP2X:CCP2Y Bits                              |        |

| AKE56                                             | CCPR1H Register                               |        |

| AKS56, 79                                         | CCPR1L Register                               |        |

| Application Note AN578, "Use of the SSP           | CCPR2H Register                               | 13, 15 |

| Module in the I2C Multi-Master Environment." 63   | CCPR2L Register                               | 13, 15 |

| Architecture                                      | CKE                                           | 54     |

| PIC16C63A/PIC16C73B Block Diagram5                | CKP                                           | 55     |

| PIC16C65B/PIC16C74B Block Diagram6                | Clock Polarity Select bit, CKP                | 55     |

| Assembler                                         | Code Examples                                 |        |

| MPASM Assembler147                                | Loading the SSPBUF register                   |        |

| В                                                 | Code Protection                               |        |

| Banking, Data Memory11, 16                        | Compare (CCP Module)                          |        |

| Baud Rate Generator73                             | Block Diagram                                 |        |

| BF54, 64, 79, 82                                  | CCP Pin Configuration                         |        |

| Block Diagrams                                    | CCPR1H:CCPR1L Registers                       |        |

| Baud Rate Generator73                             | Software Interrupt                            |        |

| I <sup>2</sup> C Master Mode71                    | Special Event Trigger                         | ,      |

| I <sup>2</sup> C Module63                         | Timer1 Mode Selection                         |        |

| SSP (I <sup>2</sup> C Mode)63                     | Configuration Bits  Conversion Considerations |        |

| SSP (SPI Mode)57                                  | Conversion Considerations                     | 107    |

| BOR. See Brown-out Reset                          | D                                             |        |

| BRG73                                             | D/ <del>A</del>                               | 54     |

| Brown-out Reset (BOR)127, 131, 132, 133, 134      | Data Memory                                   |        |

| BOR Status (BOR Bit)23                            | Bank Select (RP1:RP0 Bits)                    |        |

| Buffer Full bit, BF64                             | General Purpose Registers                     |        |

| Buffer Full Status bit, BF54                      | Register File Map                             |        |

| Bus Arbitration90                                 | Special Function Registers                    |        |

| Bus Collision                                     | Data/Address bit, D/A                         |        |

| Section                                           | DC Characteristics                            |        |

| Bus Collision During a RESTART Condition          | PIC16C73                                      | 152    |

| Bus Collision During a Start Condition            | PIC16C74                                      | 152    |

| Bus Collision During a Stop Condition94           | Development Support                           |        |

|                                                   | Development Tools                             |        |

|                                                   | Device Differences                            |        |

|                                                   | Direct Addressing                             | 25     |

# **PIC16C77X**

| E                                                             |

|---------------------------------------------------------------|

| Errata                                                        |

| F                                                             |

| Firmware Instructions                                         |

| Acknowledge86                                                 |

| Master Receiver83                                             |

| Master Transmit80                                             |

| Restart Condition                                             |

| Start Condition                                               |

| Stop Condition                                                |

| Fuzzy Logic Dev. System (fuzzyTECH®-MP)147                    |

|                                                               |

| G                                                             |

| GCE56                                                         |

| General Call Address Sequence69                               |

| General Call Address Support69                                |

| General Call Enable bit, GCE56                                |

| I                                                             |

| I/O Ports27                                                   |

| 1 <sup>2</sup> C                                              |

| I <sup>2</sup> C Master Mode Receiver Flowchart83             |

| I <sup>2</sup> C Master Mode Reception82                      |

| I <sup>2</sup> C Master Mode Restart Condition                |

| I <sup>2</sup> C Mode Selection                               |

| I <sup>2</sup> C Module                                       |

| Acknowledge Flowchart86                                       |

| Acknowledge Sequence timing85                                 |

| Addressing64                                                  |

| Baud Rate Generator73                                         |

| Block Diagram71                                               |

| BRG Block Diagram73                                           |

| BRG Reset due to SDA Collision92                              |

| BRG Timing                                                    |

| Bus Arbitration                                               |

| Bus Collision                                                 |

| Restart Condition93                                           |

| Restart Condition Timing (Case1)93                            |

| Restart Condition Timing (Case2)93                            |

| Start Condition91                                             |

| Start Condition Timing91, 92                                  |

| Stop Condition94                                              |

| Stop Condition Timing (Case1)94                               |

| Stop Condition Timing (Case2)94                               |

| Transmit Timing90                                             |

| Bus Collision timing90                                        |

| Clock Arbitration89                                           |

| Clock Arbitration Timing (Master Transmit)89                  |

| Conditions to not give ACK Pulse64                            |

| General Call Address Support69  Master Mode71                 |

| Master Mode71  Master Mode 7-bit Reception timing84           |

| Master Mode 7-bit Reception timing84  Master Mode Operation72 |

| Master Mode Operation                                         |

| Master Mode Transmission79                                    |

| Master Mode Transmit Sequence79                               |

| Master Transmit Flowchart80                                   |

| Multi-Master Communication90                                  |

| Multi-master Mode72                                           |

| Operation63                                                   |

| Repeat Start Condition timing76                               |

| Restart Condition Flowchart                                            |           |

|------------------------------------------------------------------------|-----------|

| Slave Mode                                                             |           |

| Slave Reception                                                        | 65        |

| Slave Transmission                                                     |           |

| SSPBUF                                                                 |           |

| Start Condition Flowchart                                              |           |

| Stop Condition Flowchart                                               |           |

| Stop Condition Receive or Transmit timing                              | 87        |

| Stop Condition timing                                                  | 87        |

| Waveforms for 7-bit Reception                                          |           |

| Waveforms for 7-bit Transmission                                       | 66        |

| <sup>2</sup> C Module Address Register, SSPADD                         | 64        |

| <sup>2</sup> C Slave Mode                                              | 64        |

| CEPIC Low-Cost PIC16CXXX In-Circuit Emulator .                         |           |

| D Locations                                                            | 127, 141  |

| n-Circuit Serial Programming (ICSP)                                    | 127, 141  |

| NDF                                                                    | 15        |

| NDF Register                                                           | 13, 14    |

| ndirect Addressing                                                     | 25        |

| FSR Register                                                           | 11        |

| nstruction Format                                                      | 143       |

| nstruction Set                                                         | 143       |

| Summary Table                                                          | 144       |

| NTCON                                                                  | 15        |

| NTCON Register                                                         |           |

| GIE Bit                                                                | 18        |

| INTE Bit                                                               | 18        |

| INTF Bit                                                               |           |

| PEIE Bit                                                               | 18        |

| RBIE Bit                                                               | 18        |

| RBIF Bit                                                               |           |

| T0IE Bit                                                               | 18        |

| TOIF Bit                                                               | 18        |

| nter-Integrated Circuit (I <sup>2</sup> C)                             | 53        |

| nternal sampling switch (Rss) impedence                                | 123       |

| nterrupt Sources                                                       | 127, 137  |

| Block Diagram                                                          | 137       |

| Capture Complete (CCP)                                                 | 48        |

| Compare Complete (CCP)                                                 | 49        |

| Interrupt on Change (RB7:RB4)                                          | 30        |

| RB0/INT Pin, External                                                  | 7, 8, 138 |

| TMR0 Overflow                                                          |           |

| TMR1 Overflow                                                          |           |

| TMR2 to PR2 Match                                                      | 46        |

| TMR2 to PR2 Match (PWM)                                                |           |

| USART Receive/Transmit Complete                                        | 97        |

| nterrupts, Context Saving During                                       | 138       |

| nterrupts, Enable Bits                                                 |           |

| A/D Converter Enable (ADIE Bit)                                        | 19        |

| CCP1 Enable (CCP1IE Bit)                                               | 19, 48    |

| CCP2 Enable (CCP2IE Bit)                                               | 21        |

| Global Interrupt Enable (GIE Bit)                                      | 18, 137   |

| Interrupt on Change (RB7:RB4) Enable                                   |           |

| (RBIE Bit)                                                             | 18, 138   |

| Peripheral Interrupt Enable (PEIE Bit)                                 | 18        |

| PSP Read/Write Enable (PSPIE Bit)                                      |           |

| RB0/INT Enable (INTE Bit)                                              | 18        |

| SSP Enable (SSPIE Bit)                                                 | 19        |

| TMR0 Overflow Enable (T0IE Bit)                                        | 18        |

| TMR1 Overflow Enable (TMR1IE Bit)TMR2 to PR2 Match Enable (TMR2IE Bit) | 19        |

| TMR2 to PR2 Match Enable (TMR2IE Bit)                                  | 19        |

| USART Receive Enable (RCIE Bit)                                        | 19        |

| USART Receive Enable (RCIE Bit)USART Transmit Enable (TXIE Bit)        | 19        |

|                                                                        |           |

# **PIC16C77X**

| S                                            | SSP Module                                |        |

|----------------------------------------------|-------------------------------------------|--------|

| SAE56                                        | SPI Master Mode                           |        |

| SCK57                                        | SPI Master./Slave Connection              |        |

| SCL64                                        | SPI Slave Mode                            |        |

| SDA                                          | SSPCON1 Register                          |        |

| SDI57                                        | SSP Overflow Detect bit, SSPOV            |        |

| SDO57                                        | SSPADD Register                           |        |

| SEEVAL® Evaluation and Programming System147 | SSPBUF                                    |        |

| Serial Clock, SCK57                          | SSPBUF Register                           |        |

| Serial Clock, SCL64                          | SSPCON Register                           |        |

| Serial Data Address, SDA64                   | SSPCON1                                   |        |

| Serial Data In, SDI57                        | SSPCON2<br>SSPEN                          |        |

| Serial Data Out, SDO57                       |                                           |        |

| Slave Select Synchronization60               | SSPIF<br>SSPM3:SSPM0                      |        |

| Slave Select, SS57                           | SSPOV                                     |        |

| SLEEP127, 131, 140                           | SSPSTAT                                   |        |

| SMP54                                        | SSPSTAT Register                          | ,      |

| Software Simulator (MPLAB-SIM)147            | Stack                                     |        |

| SPBRG Register                               | Start bit (S)                             |        |

| SPE                                          | Start Condition Enabled bit, SAE          |        |

| Special Features of the CPU                  | STATUS Register                           |        |

| Special Function Registers                   | C Bit                                     |        |

| PIC16C73                                     | DC Bit                                    |        |

| PIC16C73A                                    | IRP Bit                                   |        |

| PIC16C74                                     | PD Bit                                    |        |

| PIC16C74A                                    | RP1:RP0 Bits                              | 16     |

| PIC16C76                                     | TO Bit                                    | 16     |

| PIC16C77                                     | Z Bit                                     | 16     |

| Speed, Operating                             | Stop bit (P)                              | 54     |

| Master Mode59                                | Stop Condition Enable bit                 | 56     |

| Serial Clock                                 | Synchronous Serial Port                   | 53     |

| Serial Data In                               | Synchronous Serial Port Enable bit, SSPEN | 55     |

| Serial Data Out                              | Synchronous Serial Port Mode Select bits, |        |

| Serial Peripheral Interface (SPI)            | SSPM3:SSPM0                               | 55     |

| Slave Select                                 | Т                                         |        |

| SPI clock                                    | -                                         |        |

| SPI Mode57                                   | T1CON                                     |        |

| SPI Clock Edge Select, CKE54                 | T1CON Register                            |        |

| SPI Data Input Sample Phase Select, SMP54    | T1CKPS1:T1CKPS0 Bits                      |        |

| SPI Master/Slave Connection                  | T10SCEN Bit                               |        |

| SPI Module                                   | T1SYNC Bit                                |        |

| Master/Slave Connection58                    | TMR1CS Bit                                |        |

| Slave Mode 60                                | TMR10N Bit                                |        |

| Slave Select Synchronization60               | T2CON Register                            |        |

| Slave Synch Timnig60                         | T2CKPS1:T2CKPS0 Bits TMR2ON Bit           |        |

| SS57                                         | TOUTPS3:TOUTPS0 Bits                      |        |

| SSP53                                        | Timer0                                    |        |

| Block Diagram (SPI Mode)57                   | Block Diagram                             |        |

| Enable (SSPIE Bit)19                         | Clock Source Edge Select (T0SE Bit)       |        |

| Flag (SSPIF Bit)20                           | Clock Source Select (TOCS Bit)            |        |

| RA5/SS/AN4 Pin8                              | Overflow Enable (T0IE Bit)                |        |

| RC3/SCK/SCL Pin                              | Overflow Flag (T0IF Bit)                  |        |

| RC4/SDI/SDA Pin                              | Overflow Interrupt4                       |        |

| RC5/SDO Pin                                  | RA4/T0CKI Pin, External Clock             |        |

| SPI Mode57                                   | Timer1                                    |        |

| SSPADD                                       | Block Diagram                             |        |

| SSPBUF                                       | Capacitor Selection                       |        |

| SSPCON1                                      | Clock Source Select (TMR1CS Bit)          |        |

| SSPCON2                                      | External Clock Input Sync (T1SYNC Bit)    |        |

| SSPSR                                        | Module On/Off (TMR1ON Bit)                |        |

| SSPSTAT                                      | Oscillator                                | 41, 43 |

| SSP I <sup>2</sup> C                         | Oscillator Enable (T1OSCEN Bit)           | 41     |

| SSP I <sup>2</sup> C Operation               | Overflow Enable (TMR1IE Bit)              |        |

| 001 1 0 Operation                            | Overflow Flag (TMR1IF Bit)                | 20     |