Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 6x12b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c773-e-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.1 STATUS REGISTER

The STATUS register, shown in Figure 2-3, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register because these instructions do not affect the Z, C or DC bits from the STATUS register. For other instructions, not affecting any status bits, see the "Instruction Set Summary."

Note 1: The C and DC bits operate as a borrow and digit borrow bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

## FIGURE 2-3: STATUS REGISTER (ADDRESS 03h, 83h, 103h, 183h)

| R/W-0    | R/W-0                                                                                                                                                                                                                                                   | R/W-0                                                  | R-1                                  | R-1                                       | R/W-x                          | R/W-x                                      | R/W-x                       |                                                                         |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------|-------------------------------------------|--------------------------------|--------------------------------------------|-----------------------------|-------------------------------------------------------------------------|--|

| IRP      | RP1                                                                                                                                                                                                                                                     | RP0                                                    | TO                                   | PD                                        | Z                              | DC                                         | C                           | R = Readable bit<br>W = Writable bit                                    |  |

| bit7     |                                                                                                                                                                                                                                                         |                                                        |                                      |                                           |                                |                                            | bit0                        | U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset       |  |

| bit 7:   | IRP: Regis<br>1 = Bank 2<br>0 = Bank 0                                                                                                                                                                                                                  | 2, 3 (100h                                             | - 1FFh)                              | (used for ir                              | ndirect addr                   | essing)                                    |                             |                                                                         |  |

| bit 6-5: | <b>RP1:RP0:</b><br>11 = Bank<br>10 = Bank<br>01 = Bank<br>00 = Bank<br>Each bank                                                                                                                                                                        | 3 (180h -<br>2 (100h -<br>1 (80h - F<br>0 (00h - 7     | 1FFh)<br>17Fh)<br>FFh)<br>7Fh)       | ct bits (use                              | ed for direct                  | addressin                                  | g)                          |                                                                         |  |

| bit 4:   | $\overline{\mathbf{TO}}$ : Time-<br>1 = After p<br>0 = A WD                                                                                                                                                                                             | ower-up,                                               |                                      | struction,                                | or SLEEP in                    | struction                                  |                             |                                                                         |  |

| bit 3:   | <b>PD</b> : Power<br>1 = After p<br>0 = By exe                                                                                                                                                                                                          | ower-up c                                              |                                      |                                           |                                |                                            |                             |                                                                         |  |

| bit 2:   |                                                                                                                                                                                                                                                         | sult of an                                             |                                      |                                           | peration is z<br>peration is r |                                            |                             |                                                                         |  |

| bit 1:   | 1: <b>DC</b> : Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow the polarity is reversed)<br>1 = A carry-out from the 4th low order bit of the result occurred<br>0 = No carry-out from the 4th low order bit of the result |                                                        |                                      |                                           |                                |                                            |                             |                                                                         |  |

| bit 0:   | 1 = A carry<br>0 = No car<br>Note: For                                                                                                                                                                                                                  | y-out from<br>rry-out from<br>borrow the<br>perand. Fo | the most<br>n the mos<br>polarity is | significant<br>t significar<br>s reversed |                                | esult occuri<br>result occu<br>ion is exec | red<br>irred<br>uted by ado | ling the two's complement of the<br>either the high or low order bit of |  |

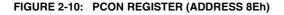

#### 2.2.2.8 PCON REGISTER

The Power Control (PCON) register contains a flag bit to allow differentiation between a Power-on Reset (POR) to an external  $\overline{\text{MCLR}}$  Reset or WDT Reset. Those devices with brown-out detection circuitry contain an additional bit to differentiate a Brown-out Reset condition from a Power-on Reset condition.

Note: BOR is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOR is clear, indicating a brown-out has occurred. The BOR status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by clearing the BODEN bit in the Configuration word).

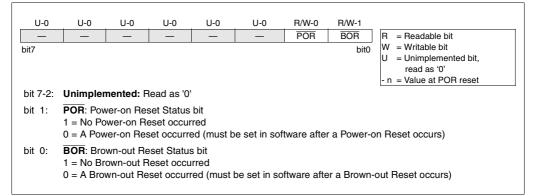

## 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (=1) will make the corresponding PORTC pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISC bit (=0) will make the corresponding PORTC pin an output, i.e., put the contents of the output latch on the selected pin.

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

#### EXAMPLE 3-1: INITIALIZING PORTC

| BCF<br>CLRF | STATUS,<br>PORTC | RPO | ;; | Select Bank 0<br>Initialize PORTC by<br>clearing output |

|-------------|------------------|-----|----|---------------------------------------------------------|

|             |                  |     | ;  | data latches                                            |

| BSF         | STATUS,          | RP0 | ;  | Select Bank 1                                           |

| MOVLW       | 0xCF             |     | ;  | Value used to                                           |

|             |                  |     | ;  | initialize data                                         |

|             |                  |     | ;  | direction                                               |

| MOVWF       | TRISC            |     | ;  | Set RC<3:0> as inputs                                   |

|             |                  |     | ;  | RC<5:4> as outputs                                      |

|             |                  |     | ;  | RC<7:6> as inputs                                       |

#### FIGURE 3-9: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

- Port/Peripheral select signal selects between port data and peripheral output.

- 3: Peripheral OE (output enable) is only activated if peripheral select is active.

# PIC16C77X

## TABLE 3-9 PORTE FUNCTIONS

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                         |

|------------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or read control input in parallel slave port mode or<br>analog input:<br>RD<br>1 = Not a read operation<br>0 = Read operation. Reads PORTD register (if chip selected)     |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or write control input in parallel slave port mode or<br>analog input:<br>WR<br>1 = Not a write operation<br>0 = Write operation. Writes PORTD register (if chip selected) |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or chip select control input in parallel slave port<br>mode or analog input:<br>CS<br>1 = Device is not selected<br>0 = Device is selected                                 |

Legend: ST = Schmitt Trigger input TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port Mode.

| Addr | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1       | Bit 0    | Value on:<br>POR,<br>BOR | Value on all other resets |

|------|--------|-------|-------|-------|---------|-------|---------|-------------|----------|--------------------------|---------------------------|

| 09h  | PORTE  | —     |       | _     | —       | —     | RE2     | RE1         | RE0      | xxx                      | uuu                       |

| 89h  | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | —     | PORTE D | Data Direct | ion Bits | 0000 -111                | 0000 -111                 |

| 9Fh  | ADCON1 | ADFM  | VCFG2 | VCFG1 | VCFG0   | PCFG3 | PCFG2   | PCFG1       | PCFG0    | 0000 0000                | 0000 0000                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTE.

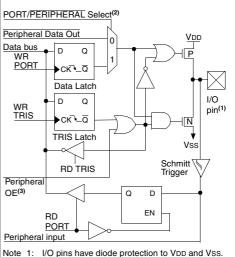

# FIGURE 3-15: PARALLEL SLAVE PORT READ WAVEFORMS

## TABLE 3-11 REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7    | Bit 6     | Bit 5      | Bit 4          | Bit 3    | Bit 2   | Bit 1       | Bit 0    | Value<br>PC<br>BC | R,   | Value<br>other |      |

|---------|--------|----------|-----------|------------|----------------|----------|---------|-------------|----------|-------------------|------|----------------|------|

| 08h     | PORTD  | Port dat | a latch w | hen writte | n: Port pins v | hen read |         |             | xxxx     | xxxx              | uuuu | uuuu           |      |

| 09h     | PORTE  | _        | _         | _          | _              | —        | RE2     | RE1         | RE0      |                   | -xxx |                | -uuu |

| 89h     | TRISE  | IBF      | OBF       | IBOV       | PSPMODE        |          | PORTE I | Data Direct | ion Bits | 0000              | -111 | 0000           | -111 |

| 0Ch     | PIR1   | PSPIF    | ADIF      | RCIF       | TXIF           | SSPIF    | CCP1IF  | TMR2IF      | TMR1IF   | 0000              | 0000 | 0000           | 0000 |

| 8Ch     | PIE1   | PSPIE    | ADIE      | RCIE       | TXIE           | SSPIE    | CCP1IE  | TMR2IE      | TMR1IE   | 0000              | 0000 | 0000           | 0000 |

| 9Fh     | ADCON1 | ADFM     | VCFG2     | VCFG1      | VCFG0          | PCFG3    | PCFG2   | PCFG1       | PCFG0    | 0000              | 0000 | 0000           | 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Parallel Slave Port.

# 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE(S)

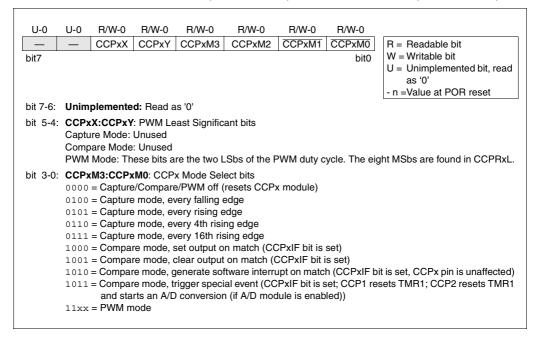

Each CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Table 7-1 shows the timer resources of the CCP module modes.

The operation of CCP1 is identical to that of CCP2, with the exception of the special trigger. Therefore, operation of a CCP module in the following sections is described with respect to CCP1.

Table 7-2 shows the interaction of the CCP modules.

#### CCP1 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

## CCP2 Module

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. All are readable and writable.

Additional information on the CCP module is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

## TABLE 7-1 CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

| CCPx Mode | CCPy Mode | Interaction                                                                           |

|-----------|-----------|---------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base.                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM       | The PWMs will have the same frequency, and update rate (TMR2 interrupt).              |

| PWM       | Capture   | None                                                                                  |

| PWM       | Compare   | None                                                                                  |

## TABLE 7-2 INTERACTION OF TWO CCP MODULES

## FIGURE 7-1: CCP1CON REGISTER (ADDRESS 17h) / CCP2CON REGISTER (ADDRESS 1Dh)

#### 7.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- driven High

- driven Low

- remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

## FIGURE 7-3: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 7.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

| Note: | Clearing the CCP1CON register will force       |

|-------|------------------------------------------------|

|       | the RC2/CCP1 compare output latch to the       |

|       | default low level. This is not the data latch. |

#### 7.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 7.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

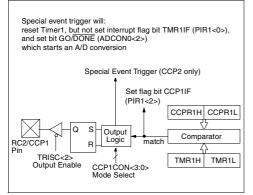

#### 7.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1.

The special trigger output of CCP2 resets the TMR1 register pair, and starts an A/D conversion (if the A/D module is enabled).

Note: The special event trigger from the CCP2 module will not set interrupt flag bit TMR1IF (PIR1<0>).

## TABLE 7-3 REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address               | Name    | Bit 7                               | Bit 6     | Bit 5        | Bit 4       | Bit 3         | Bit 2      | Bit 1      | Bit 0  | PC   | e on:<br>)R,<br>)R | allo | e on<br>other<br>sets |

|-----------------------|---------|-------------------------------------|-----------|--------------|-------------|---------------|------------|------------|--------|------|--------------------|------|-----------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                                 | PEIE      | TOIE         | INTE        | RBIE          | TOIF       | INTF       | RBIF   | 0000 | 000x               | 0000 | 000u                  |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup>                | ADIF      | RCIF         | TXIF        | SSPIF         | CCP1IF     | TMR2IF     | TMR1IF | 0000 | 0000               | 0000 | 0000                  |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup>                | ADIE      | RCIE         | TXIE        | SSPIE         | CCP1IE     | TMR2IE     | TMR1IE | 0000 | 0000               | 0000 | 0000                  |

| 87h                   | TRISC   | PORTC Da                            | ata Dire  | ction Regis  | ster        |               |            |            |        | 1111 | 1111               | 1111 | 1111                  |

| 0Eh                   | TMR1L   | Holding reg                         | gister fo | or the Least | Significant | Byte of the   | 16-bit TMF | 1 register |        | xxxx | xxxx               | uuuu | uuuu                  |

| 0Fh                   | TMR1H   | Holding reg                         | gister fo | or the Most  | Significant | Byte of the 1 | 6-bit TMR  | 1register  |        | xxxx | xxxx               | uuuu | uuuu                  |

| 10h                   | T1CON   | —                                   | _         | T1CKPS1      | T1CKPS0     | T1OSCEN       | T1SYNC     | TMR1CS     | TMR10N | 00   | 0000               | uu   | uuuu                  |

| 15h                   | CCPR1L  | Capture/Compare/PWM register1 (LSB) |           |              |             |               |            |            |        | xxxx | xxxx               | uuuu | uuuu                  |

| 16h                   | CCPR1H  | Capture/Compare/PWM register1 (MSB) |           |              |             |               |            |            |        | xxxx | xxxx               | uuuu | uuuu                  |

| 17h                   | CCP1CON | —                                   |           | CCP1X        | CCP1Y       | CCP1M3        | CCP1M2     | CCP1M1     | CCP1M0 | 00   | 0000               | 00   | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin, always maintain these bits clear.

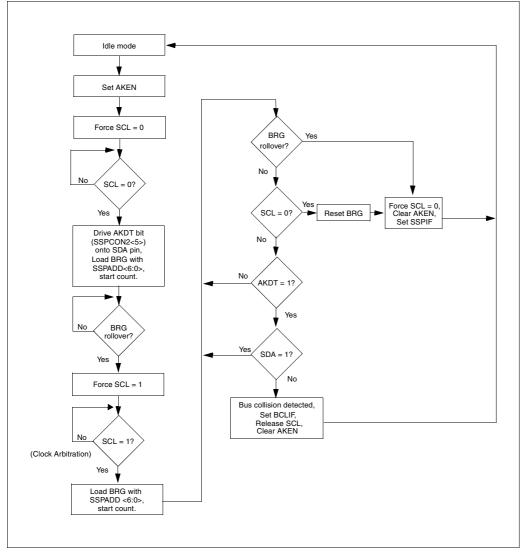

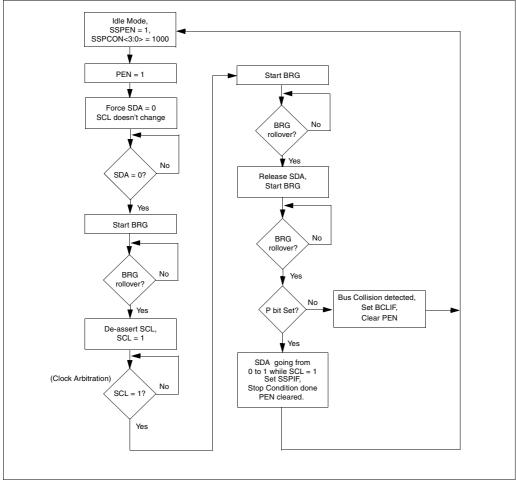

#### 8.2.6 MULTI-MASTER OPERATION

In multi-master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored, for abitration, to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

#### 8.2.7 I<sup>2</sup>C MASTER OPERATION SUPPORT

Master Mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON and by setting the SSPEN bit. Once master mode is enabled, the user has six options.

- Assert a start condition on SDA and SCL.

- Assert a Repeated Start condition on SDA and SCL.

- Write to the SSPBUF register initiating transmission of data/address.

- Generate a stop condition on SDA and SCL.

- Configure the I<sup>2</sup>C port to receive data.

- Generate an Acknowledge condition at the end of a received byte of data.

- Note: The MSSP Module, when configured in I<sup>2</sup>C Master Mode, does not allow queueing of events. For instance: The user is not allowed to initiate a start condition, and immediately write the SSPBUF register to initiate transmission before the START condition is complete. In this case the SSPBUF will not be written to, and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

#### 8.2.7.4 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the  $l^2C$  bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write ( $R/\overline{W}$ ) bit. In this case, the  $R/\overline{W}$  bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

In Master receive mode the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/ $\overline{W}$  bit. In this case the R/ $\overline{W}$  bit will be logic '1'. Thus the first byte transmitted is a 7-bit slave address followed by a '1' to indicate receive bit. Serial data is received via SDA while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions indicate the beginning and end of transmission.

The baud rate generator used for SPI mode operation is now used to set the SCL clock frequency for either 100 kHz, 400 kHz, or 1 MHz  $I^2C$  operation. The baud rate generator reload value is contained in the lower 7 bits of the SSPADD register. The baud rate generator will automatically begin counting on a write to the SSP-BUF. Once the given operation is complete (i.e. transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state

A typical transmit sequence would go as follows:

- a) The user generates a Start Condition by setting the START enable bit (SEN) in SSPCON2.

- SSPIF is set. The module will wait the required start time before any other operation takes place.

- c) The user loads the SSPBUF with address to transmit.

- d) Address is shifted out the SDA pin until all 8 bits are transmitted.

- e) The MSSP Module shifts in the ACK bit from the slave device, and writes its value into the SSPCON2 register (SSPCON2<6>).

- f) The module generates an interrupt at the end of the ninth clock cycle by setting SSPIF.

- g) The user loads the SSPBUF with eight bits of data.

- h) DATA is shifted out the SDA pin until all 8 bits are transmitted.

## FIGURE 8-30: ACKNOWLEDGE FLOWCHART

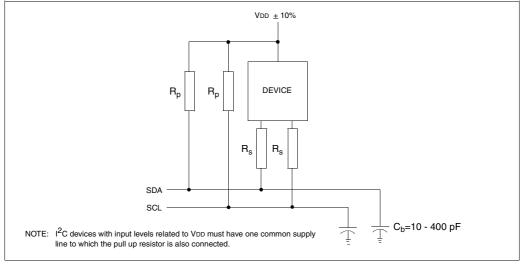

### 8.3 <u>Connection Considerations for I<sup>2</sup>C</u> Bus

For standard-mode  $I^2C$  bus devices, the values of resistors  $\mathbf{R_p} \mathbf{R_s}$  in Figure 8-42 depends on the following parameters

- Supply voltage

- Bus capacitance

- Number of connected devices (input current + leakage current).

The supply voltage limits the minimum value of resistor  $R_p$  due to the specified minimum sink current of 3 mA at VoL max = 0.4V for the specified output stages. For

example, with a supply voltage of VDD =  $5V\pm10\%$  and VoL max = 0.4V at 3 mA, R<sub>p min</sub> = (5.5-0.4)/0.003 = 1.7 k\Omega. VDD as a function of **R**<sub>p</sub> is shown in Figure 8-42. The desired noise margin of 0.1VDD for the low level limits the maximum value of **R**<sub>s</sub>. Series resistors are optional and used to improve ESD susceptibility.

The bus capacitance is the total capacitance of wire, connections, and pins. This capacitance limits the maximum value of  $R_p$  due to the specified rise time (Figure 8-42).

The SMP bit is the slew rate control enabled bit. This bit is in the SSPSTAT register, and controls the slew rate of the I/O pins when in  $I^2C$  mode (master or slave).

## FIGURE 8-42: SAMPLE DEVICE CONFIGURATION FOR I<sup>2</sup>C BUS

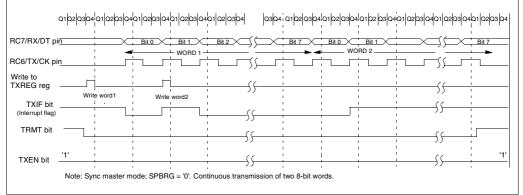

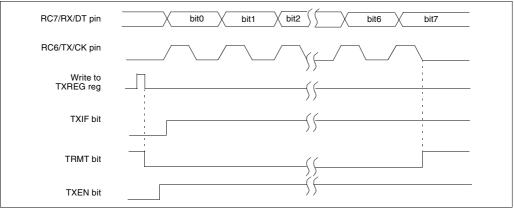

## FIGURE 9-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

| TABLE 12-6 INITIALIZATION CONDITIONS FOR ALL REGISTERS |     |      |                                    |                          |                                 |  |  |  |  |  |

|--------------------------------------------------------|-----|------|------------------------------------|--------------------------|---------------------------------|--|--|--|--|--|

| Register                                               | Dev | ices | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |  |  |  |  |

| W                                                      | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |  |

| INDF                                                   | 773 | 774  | N/A                                | N/A                      | N/A                             |  |  |  |  |  |

| TMR0                                                   | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |  |

| PCL                                                    | 773 | 774  | 0000h                              | 0000h                    | PC + 1 <b>(2)</b>               |  |  |  |  |  |

| STATUS                                                 | 773 | 774  | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |  |  |  |  |  |

| FSR                                                    | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |  |

| PORTA                                                  | 773 | 774  | 0x 0000                            | 0u 0000                  | uu uuuu                         |  |  |  |  |  |

| PORTB                                                  | 773 | 774  | xxxx 11xx                          | uuuu 11uu                | uuuu uuuu                       |  |  |  |  |  |

| PORTC                                                  | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |  |

| PORTD                                                  | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |  |

| PORTE                                                  | 773 | 774  | 000                                | 000                      | uuu                             |  |  |  |  |  |

| PCLATH                                                 | 773 | 774  | 0 0000                             | 0 0000                   | u uuuu                          |  |  |  |  |  |

| INTCON                                                 | 773 | 774  | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |  |  |  |  |  |

| PIR1                                                   | 773 | 774  | r000 0000                          | r000 0000                | ruuu uuuu <b>(1)</b>            |  |  |  |  |  |

|                                                        | 773 | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu <b>(1)</b>            |  |  |  |  |  |

| PIR2                                                   | 773 | 774  | 00                                 | 00                       | u uu <b>(1)</b>                 |  |  |  |  |  |

| TMR1L                                                  | 773 | 774  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |  |

| TMR1H                                                  | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |  |

| T1CON                                                  | 773 | 774  | 00 0000                            | uu uuuu                  | uu uuuu                         |  |  |  |  |  |

| TMR2                                                   | 773 | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |  |  |

| T2CON                                                  | 773 | 774  | -000 0000                          | -000 0000                | -uuu uuuu                       |  |  |  |  |  |

| SSPBUF                                                 | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |  |

| SSPCON                                                 | 773 | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |  |  |

| CCPR1L                                                 | 773 | 774  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |  |

| CCPR1H                                                 | 773 | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |  |

| CCP1CON                                                | 773 | 774  | 00 0000                            | 00 0000                  | uu uuuu                         |  |  |  |  |  |

| RCSTA                                                  | 773 | 774  | 0000 000x                          | 0000 000x                | uuuu uuuu                       |  |  |  |  |  |

| TXREG                                                  | 773 | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |  |  |

| RCREG                                                  | 773 | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |  |  |

| CCPR2L                                                 | 773 | 774  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |  |

| CCPR2H                                                 | 773 | 774  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |  |

| CCP2CON                                                | 773 | 774  | 00 0000                            | 00 0000                  | uu uuuu                         |  |  |  |  |  |

| ADRESH                                                 | 773 | 774  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |  |  |  |

| ADCON0                                                 | 773 | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |  |  |  |

| OPTION_REG                                             | 773 | 774  | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |  |  |  |  |

| TABLE 12-6 | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|------------|---------------------------------------------|

|            |                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-5 for reset value for specific condition.

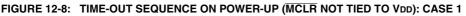

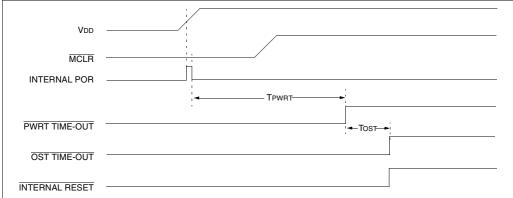

## FIGURE 12-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

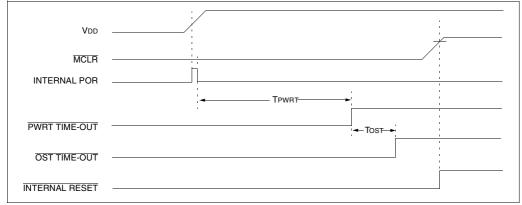

## FIGURE 12-10: SLOW RISE TIME (MCLR TIED TO VDD)

# 14.0 DEVELOPMENT SUPPORT

## 14.1 Development Tools

The PICmicro<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- MPLAB<sup>™</sup> -ICE Real-Time In-Circuit Emulator

- ICEPIC<sup>™</sup> Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- SIMICE

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB<sup>™</sup> SIM Software Simulator

- MPLAB-C17 (C Compiler)

- Fuzzy Logic Development System (*fuzzy*TECH<sup>®</sup>–MP)

- KEELOQ<sup>®</sup> Evaluation Kits and Programmer

### 14.2 <u>MPLAB-ICE: High Performance</u> Universal In-Circuit Emulator with MPLAB IDE

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers (MCUs). MPLAB-ICE is supplied with the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support all new Microchip microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x or Windows 95 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE is available in two versions. MPLAB-ICE 1000 is a basic, low-cost emulator system with simple trace capabilities. It shares processor modules with the MPLAB-ICE 2000. This is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems will operate across the entire operating speed reange of the PICmicro MCU.

## 14.3 ICEPIC: Low-Cost PICmicro In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC12CXXX, PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 386 through Pentium™ based machines under Windows 3.x, Windows 95, or Windows NT environment. ICEPIC features real time, non-intrusive emulation.

### 14.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices. It can also set configuration and code-protect bits in this mode.

## 14.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923, PIC16C924 and PIC17C756 may be supported with an adapter socket. PICSTART Plus is CE compliant.

## 15.4 DC Characteristics: VREF

## TABLE 15-2 ELECTRICAL CHARACTERISTICS: VREF

| DC CHAR      | perating Co<br>mperature | -40°C<br>0°C   | : TA ≥ C<br>≤ TA ≥ | ≤ +85°C<br>≤ +70°C | for industr<br>for comme | ial and             |         |                         |

|--------------|--------------------------|----------------|--------------------|--------------------|--------------------------|---------------------|---------|-------------------------|

| Param<br>No. | Characte                 |                | Symbol             | Min                | Typ†                     | Max                 | Units   | Conditions              |

| D400         | Output Voltage           |                | VRL                | 2.0                | 2.048                    | 2.1                 | V       | VDD ≥ 2.5V              |

|              |                          |                | VRH                | 4.0                | 4.096                    | 4.2                 | V       | VDØ ≥ 4.5V              |

| D401A        | VRL Quiescent S          | upply Current  | $\Delta IVRL$      | —                  | 70                       | TBD                 | μΑ      | No load on VRL.         |

| D401B        | VRH Quiescent S          | Supply Current | $\Delta IVRH$      | _                  | 70                       | TBD                 | µtA     | No load on VRH.         |

| D402         | Ouput Voltage Dr         | ift            | TCVOUT             | —                  | 15*                      | 50*                 | ppm/°C/ | Note 1                  |

| D404         | External Load So         | urce           | IVREFSO            | —                  | —                        | ,5*                 | (mA     |                         |

| D405         | External Load Sir        | ık             | IVREFSI            | —                  | —                        | <- <del>5</del> * \ | ∖mA     |                         |

| D406         | Load Regulation          |                |                    | _                  | $\checkmark$             | †βD/₹ (             |         | Isource = 0 mA to       |

|              |                          |                | $\Delta VOUT/$     |                    | $\langle \rangle$        |                     | mV/mA   | 5 mA                    |

|              |                          |                | ΔΙΟυτ              | ~                  | 71/                      | TBD                 |         | Isink = 0 mA to<br>5 mA |

| D407         | Line Regulation          |                |                    | B                  |                          | 50*                 | μV/V    | 5 111A                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Production tested at TAMB  $= 25^{\circ}$ C. Specifications over temp limits guaranteed by characterization.

# PIC16C77X

NOTES:

# **PIC16C77X**

# INDEX

# A

| A/D                                               |

|---------------------------------------------------|

| A/D Converter Enable (ADIE Bit)                   |

| A/D Converter Flag (ADIF Bit)                     |

| ADCON0 Register                                   |

| ADCON1 Register 117, 118                          |

| ADRES Register                                    |

| Analog Port Pins                                  |

| Block Diagram                                     |

| Configuring Analog Port119                        |

| Conversion time                                   |

| Conversions121                                    |

| converter characteristics 156, 157, 158, 165      |

| Faster Conversion - Lower Resolution Tradeoff 125 |

| Internal Sampling Switch (Rss) Impedence          |

| Operation During Sleep126                         |

| Sampling Requirements 123                         |

| Sampling Time                                     |

| Source Impedance                                  |

| Special Event Trigger (CCP) 49                    |

| A/D Conversion Clock                              |

| ACK                                               |

| Acknowledge Data bit, AKD56                       |

| Acknowledge Pulse64                               |

| Acknowledge Sequence Enable bit, AKE56            |

| Acknowledge Status bit, AKS56                     |

| ADCON0 Register                                   |

| ADCON1 Register 117, 118                          |

| ADRES 117                                         |

| ADRES Register                                    |

| AKD                                               |

| AKE                                               |

| AKS                                               |

| Application Note AN578, "Use of the SSP           |

| Module in the I2C Multi-Master Environment."      |

| Architecture                                      |

| PIC16C63A/PIC16C73B Block Diagram5                |

| PIC16C65B/PIC16C74B Block Diagram6                |

| Assembler                                         |

| MPASM Assembler147                                |

| В                                                 |

| -                                                 |

| Banking, Data Memory 11, 16                       |

| Banking, Data Memory11,                     | 16 |

|---------------------------------------------|----|

| Baud Rate Generator                         | 73 |

| BF54, 64, 79,                               | 82 |

| Block Diagrams                              |    |

| Baud Rate Generator                         | 73 |

| I <sup>2</sup> C Master Mode                | 71 |

| I <sup>2</sup> C Module                     |    |

| SSP (I <sup>2</sup> C Mode)                 | 63 |

| SSP (SPI Mode)                              | 57 |

| BOR. See Brown-out Reset                    |    |

| BRG                                         | 73 |

| Brown-out Reset (BOR) 127, 131, 132, 133, 1 | 34 |

| BOR Status (BOR Bit)                        | 23 |

| Buffer Full bit, BF                         | 64 |

| Buffer Full Status bit, BF                  | 54 |

| Bus Arbitration                             | 90 |

| Bus Collision                               |    |

| Section                                     | 90 |

| Bus Collision During a RESTART Condition    | 93 |

| Bus Collision During a Start Condition      | 91 |

| Bus Collision During a Stop Condition       | 94 |

|                                             |    |

# С

| C                                   |  |  |  |  |

|-------------------------------------|--|--|--|--|

| Capture (CCP Module) 48             |  |  |  |  |

| Block Diagram                       |  |  |  |  |

| CCP Pin Configuration               |  |  |  |  |

| CCPR1H:CCPR1L Registers             |  |  |  |  |

| Changing Between Capture Prescalers |  |  |  |  |

| Software Interrupt                  |  |  |  |  |

| Timer1 Mode Selection               |  |  |  |  |

| Capture/Compare/PWM (CCP) 47        |  |  |  |  |

| CCP1                                |  |  |  |  |

| CCP1CON Register 47                 |  |  |  |  |

| CCPR1H Register                     |  |  |  |  |

| CCPR1L Register 47                  |  |  |  |  |

| Enable (CCP1IE Bit) 19              |  |  |  |  |

| Flag (CCP1IF Bit)                   |  |  |  |  |

| RC2/CCP1 Pin                        |  |  |  |  |

| CCP2                                |  |  |  |  |

| CCP2CON Register                    |  |  |  |  |

| CCPR2H Register                     |  |  |  |  |

| CCPR2L Register                     |  |  |  |  |

| Enable (CCP2IE Bit)                 |  |  |  |  |

| Flag (CCP2IF Bit)                   |  |  |  |  |

| RC1/T10SI/CCP2 Pin                  |  |  |  |  |

| Interaction of Two CCP Modules      |  |  |  |  |

| Timer Resources                     |  |  |  |  |

| CCP1CON                             |  |  |  |  |

| CCP1CON Register                    |  |  |  |  |

| CCP1M3:CCP1M0 Bits                  |  |  |  |  |

| CCP1X:CCP1Y Bits                    |  |  |  |  |

| CCP2CON                             |  |  |  |  |

| CCP2CON Register                    |  |  |  |  |

| CCP200N Register                    |  |  |  |  |

| CCP2XIS.CCP2XID Bits                |  |  |  |  |

|                                     |  |  |  |  |

| CCPR1H Register                     |  |  |  |  |

| CCPR1L Register                     |  |  |  |  |

| CCPR2H Register                     |  |  |  |  |

| CCPR2L Register                     |  |  |  |  |

| CKE                                 |  |  |  |  |

| CKP                                 |  |  |  |  |

| Clock Polarity Select bit, CKP 55   |  |  |  |  |

| Code Examples                       |  |  |  |  |

| Loading the SSPBUF register         |  |  |  |  |

| Code Protection                     |  |  |  |  |

| Compare (CCP Module)                |  |  |  |  |

| Block Diagram                       |  |  |  |  |

| CCP Pin Configuration               |  |  |  |  |

| CCPR1H:CCPR1L Registers             |  |  |  |  |

| Software Interrupt                  |  |  |  |  |

| Special Event Trigger 43, 49        |  |  |  |  |

| Timer1 Mode Selection 49            |  |  |  |  |

| Configuration Bits 127              |  |  |  |  |

| Conversion Considerations 187       |  |  |  |  |

| n                                   |  |  |  |  |

## D

| D/Ā                        | 54     |

|----------------------------|--------|

| Data Memory                | 11     |

| Bank Select (RP1:RP0 Bits) | 11, 16 |

| General Purpose Registers  | 11     |

| Register File Map          | 12     |

| Special Function Registers | 13     |

| Data/Address bit, D/A      |        |

| DC Characteristics         |        |

| PIC16C73                   | 152    |

| PIC16C74                   | 152    |

| Development Support        | 145    |

| Development Tools          | 145    |

| Device Differences         |        |

| Direct Addressing          | 25     |

|                            |        |

# BIT/REGISTER CROSS-REFERENCE LIST

| 10001 10000   |             |

|---------------|-------------|

| ADCS1:ADCS0   |             |

| ADIE          |             |

| ADIF          |             |

| ADON          |             |

| BF            |             |

| BOR           |             |

| BRGH          |             |

| С             |             |

| CCP1IE        |             |

| CCP1IF        |             |

| CCP1M3:CCP1M0 |             |

| CCP1X:CCP1Y   |             |

| CCP2IE        |             |

| CCP2IF        |             |

| CCP2M3:CCP2M0 |             |

| CCP2X:CCP2Y   |             |

| CHS2:CHS0     |             |

| CKE           | SSPSTAT<6>  |

| СКР           | SSPCON<4>   |

| CREN          | RCSTA<4>    |

| CSRC          | TXSTA<7>    |

| D/A           | SSPSTAT<5>  |

| DC            | STATUS<1>   |

| FERR          | RCSTA<2>    |

| GIE           | INTCON<7>   |

| GO/DONE       |             |

| IBF           |             |

| IBOV          |             |

| INTE          |             |

| INTEDG        |             |

| INTF          |             |

| IRP           |             |

| OBF           |             |

| OERB          |             |

| P             |             |

| PCFG2:PCFG0   |             |

| PD            |             |

| PEIE          |             |

|               |             |

| POR           |             |

| PS2:PS0       | _           |

| PSA           |             |

| PSPIE         |             |

| PSPIF         |             |

| PSPMODE       |             |

| R/W           |             |

| RBIE          |             |

| RBIF          |             |

| RBPU          | _           |

| RCIE          |             |

| RCIF          |             |

| RP1:RP0       |             |

| RX9           |             |

| RX9D          |             |

| S             |             |

| SMP           |             |

| SPEN          |             |

| SREN          |             |

| SSPEN         |             |

| SSPIE         |             |

| SSPIF         |             |

| SSPM3:SSPM0   | SSPCON<3:0> |

| SSPOV         |             |

| SYNC          | TXSTA<4>    |

|               |             |

| T0CS            |               |

|-----------------|---------------|

| TOIE            | INTCON<5>     |

| TOIF            | INTCON<2>     |

| T0SE            | OPTION_REG<4> |

| T1CKPS1:T1CKPS0 | T1CON<5:4>    |

| T1OSCEN         | T1CON<3>      |

| T1SYNC          | T1CON<2>      |

| T2CKPS1:T2CKPS0 | T2CON<1:0>    |

| TMR1CS          | T1CON<1>      |

| TMR1IE          | PIE1<0>       |

| TMR1IF          | PIR1<0>       |

| TMR1ON          | T1CON<0>      |

| TMR2IE          | PIE1<1>       |

| TMR2IF          | PIR1<1>       |

| TMR2ON          | T2CON<2>      |

| TO              | STATUS<4>     |

| TOUTPS3:TOUTPS0 | T2CON<6:3>    |

| TRMT            | TXSTA<1>      |

| ТХ9             | TXSTA<6>      |

| TX9D            | TXSTA<0>      |

| TXEN            | TXSTA<5>      |

| TXIE            | PIE1<4>       |

| TXIF            | PIR1<4>       |

| UA              | SSPSTAT<1>    |

| WCOL            | SSPCON<7>     |

| Z               |               |

|                 |               |

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (602) 786-7578.

Please list the following information, and use this outline to provide us with your comments about this Data Sheet.

| To:  | 2: Technical Publications Manager                              | Total Pages Sent                  |

|------|----------------------------------------------------------------|-----------------------------------|

| RE:  | E: Reader Response                                             |                                   |

| From | om: Name                                                       |                                   |

|      | Company                                                        |                                   |

|      | Address                                                        |                                   |

|      | City / State / ZIP / Country                                   |                                   |

|      | Telephone: ()                                                  | FAX: ()                           |

| • •  | oplication (optional):                                         |                                   |

| Wou  | ould you like a reply?YN                                       |                                   |

| Dev  | evice: PIC16C77X Literature Number: DS30                       | 275B                              |

| Que  | uestions:                                                      |                                   |

| 4    | What are the best features of this document?                   |                                   |

| 1.   | what are the best leatures of this document?                   |                                   |

|      |                                                                |                                   |

| 2.   | How does this document meet your hardware and software         | development needs?                |

|      |                                                                |                                   |

|      |                                                                |                                   |

| 3.   | Do you find the organization of this data sheet easy to follow | v? If not, why?                   |

|      |                                                                |                                   |

|      |                                                                |                                   |

| 4.   | What additions to the data sheet do you think would enhance    | ce the structure and subject?     |

|      |                                                                |                                   |

|      |                                                                | <i></i>                           |

| 5.   | What deletions from the data sheet could be made without a     | affecting the overall usefulness? |

|      |                                                                |                                   |

| 6    | Is there any incorrect or misleading information (what and w   | (here)?                           |

| 0.   |                                                                |                                   |

|      |                                                                |                                   |

| 7.   | How would you improve this document?                           |                                   |

|      |                                                                |                                   |

|      |                                                                |                                   |

| 8.   | How would you improve our software, systems, and silicon       | products?                         |

|      |                                                                |                                   |