Welcome to E-XFL.COM

# What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                                |

| Data Converters            | A/D 6x12b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c773-i-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin# | QFP<br>Pin# | I/O/P<br>Type | Buffer<br>Type         | Description                                                                                                                                                                                                       |

|-------------------|-------------|--------------|-------------|---------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN        | 13          | 14           | 30          | Ι             | ST/CMOS <sup>(4)</sup> | Oscillator crystal input/external clock source input.                                                                                                                                                             |

| OSC2/CLKOUT       | 14          | 15           | 31          | 0             | _                      | Oscillator crystal output. Connects to crystal or resonator<br>in crystal oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| MCLR/Vpp          | 1           | 2            | 18          | I/P           | ST                     | Master clear (reset) input or programming voltage input.<br>This pin is an active low reset to the device.                                                                                                        |

|                   |             |              |             |               |                        | PORTA is a bi-directional I/O port.                                                                                                                                                                               |

| RA0/AN0           | 2           | 3            | 19          | I/O           | TTL                    | RA0 can also be analog input0                                                                                                                                                                                     |

| RA1/AN1           | 3           | 4            | 20          | I/O           | TTL                    | RA1 can also be analog input1                                                                                                                                                                                     |

| RA2/AN2/VREF-/VRL | 4           | 5            | 21          | I/O           | TTL                    | RA2 can also be analog input2 or negative analog<br>reference voltage input or internal voltage reference<br>low                                                                                                  |

| RA3/AN3/VREF+/VRH | 5           | 6            | 22          | I/O           | TTL                    | RA3 can also be analog input3 or positive analog<br>reference voltage input or internal voltage reference<br>high                                                                                                 |

| RA4/T0CKI         | 6           | 7            | 23          | I/O           | ST                     | RA4 can also be the clock input to the Timer0 timer/<br>counter. Output is open drain type.                                                                                                                       |

| RA5/AN4           | 7           | 8            | 24          | I/O           | TTL                    | RA5 can also be analog input4                                                                                                                                                                                     |

|                   |             |              |             |               |                        | PORTB is a bi-directional I/O port. PORTB can be soft-<br>ware programmed for internal weak pull-up on all inputs.                                                                                                |

| RB0/INT           | 33          | 36           | 8           | I/O           | TTL/ST <sup>(1)</sup>  | RB0 can also be the external interrupt pin.                                                                                                                                                                       |

| RB1/SS            | 34          | 37           | 9           | I/O           | TTL/ST <sup>(1)</sup>  | RB1 can also be the SSP slave select                                                                                                                                                                              |

| RB2/AN8           | 35          | 38           | 10          | I/O           | TTL                    | RB2 can also be analog input8                                                                                                                                                                                     |

| RB3/AN9/LVDIN     | 36          | 39           | 11          | I/O           | TTL                    | RB3 can also be analog input9 or input reference for<br>low voltage detect                                                                                                                                        |

| RB4               | 37          | 41           | 14          | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                          |

| RB5               | 38          | 42           | 15          | I/O           | TTL                    | Interrupt on change pin.                                                                                                                                                                                          |

| RB6               | 39          | 43           | 16          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming clock.                                                                                                                                                                |

| RB7               | 40          | 44           | 17          | I/O           | TTL/ST <sup>(2)</sup>  | Interrupt on change pin. Serial programming data.                                                                                                                                                                 |

## TABLE 1-2 PIC16C774 PINOUT DESCRIPTION

— = Not used TTL = TTL input ST = Schmitt Trigger input

Note 1: This buffer is a Schmitt Trigger input when configured for the multiplexed function.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

## FIGURE 2-2: REGISTER FILE MAP

|                                |         |                                            | 1          |                                            | 100        |                       |

|--------------------------------|---------|--------------------------------------------|------------|--------------------------------------------|------------|-----------------------|

| Indirect addr.(*)              | 00h     | Indirect addr.(*)                          | 80h        | Indirect addr.(*)                          | 100h       | Indirect addr.(*)     |

| TMR0                           | 01h     | OPTION_REG                                 | 81h        | TMR0                                       | 101h       | OPTION_REG            |

| PCL                            | 02h     | PCL                                        | 82h        | PCL                                        | 102h       | PCL                   |

| STATUS                         | 03h     | STATUS                                     | 83h        | STATUS                                     | 103h       | STATUS                |

| FSR                            | 04h     | FSR                                        | 84h        | FSR                                        | 104h       | FSR                   |

| PORTA                          | 05h     | TRISA                                      | 85h        |                                            | 105h       |                       |

| PORTB                          | 06h     | TRISB                                      | 86h        | PORTB                                      | 106h       | TRISB                 |

| PORTC                          | 07h     | TRISC                                      | 87h        |                                            | 107h       |                       |

| PORTD (1)                      | 08h     | TRISD (1)                                  | 88h        |                                            | 108h       |                       |

| PORTE (1)                      | 09h     | TRISE <sup>(1)</sup>                       | 89h        |                                            | 109h       |                       |

| PCLATH                         | 0Ah     | PCLATH                                     | 8Ah        | PCLATH                                     | 10Ah       | PCLATH                |

| INTCON                         | 0Bh     | INTCON                                     | 8Bh        | INTCON                                     | 10Bh       | INTCON                |

| PIR1                           | 0Ch     | PIE1                                       | 8Ch        |                                            | 10Ch       |                       |

| PIR2                           | 0Dh     | PIE2                                       | 8Dh        |                                            | 10Dh       |                       |

| TMR1L                          | 0Eh     | PCON                                       | 8Eh        |                                            | 10Eh       |                       |

| TMR1H                          | 0Fh     |                                            | 8Fh        |                                            | 10Fh       |                       |

| T1CON                          | 10h     |                                            | 90h        |                                            | 110h       |                       |

| TMR2                           | 11h     | SSPCON2                                    | 91h        |                                            | 111h       |                       |

| T2CON                          | 12h     | PR2                                        | 92h        |                                            | 112h       |                       |

| SSPBUF                         | 13h     | SSPADD                                     | 93h        |                                            | 113h       |                       |

| SSPCON                         | 14h     | SSPSTAT                                    | 94h        |                                            | 114h       |                       |

| CCPR1L                         | 15h     |                                            | 95h        |                                            | 115h       |                       |

| CCPR1H                         | 16h     |                                            | 96h        |                                            | 116h       |                       |

| CCP1CON                        | 17h     |                                            | 97h        |                                            | 117h       |                       |

| RCSTA                          | 18h     | TXSTA                                      | 98h        |                                            | 118h       |                       |

| TXREG                          | 19h     | SPBRG                                      | 99h        |                                            | 119h       |                       |

| RCREG                          | 1Ah     |                                            | 9Ah        |                                            | 11Ah       |                       |

| CCPR2L                         | 1Bh     | REFCON                                     | 9Bh        |                                            | 11Bh       |                       |

| CCPR2H                         | 1Ch     | LVDCON                                     | 9Ch        |                                            | 11Ch       |                       |

| CCP2CON                        | 1Dh     |                                            | 9Dh        |                                            | 11Dh       |                       |

| ADRESH                         | 1Eh     | ADRESL                                     | 9Eh        |                                            | 11Eh       |                       |

| ADCON0                         | 1Fh     | ADCON1                                     | 9Fh        |                                            | 11Fh       |                       |

|                                | 20h     |                                            | A0h        |                                            | 120h       |                       |

| General<br>Purpose<br>Register |         | General<br>Purpose<br>Register<br>80 Bytes |            | General<br>Purpose<br>Register<br>80 Bytes |            |                       |

| 96 Bytes                       |         | accesses<br>70h-7Fh                        | EFh<br>F0h | accesses<br>70h - 7Fh                      | 6Fh<br>70h | accesses<br>70h - 7Fh |

|                                | 7Fh     | 7011-7FN                                   | FFh        | 7011 - 7F11                                | 17Fh       | 7011 - 7F11           |

| Bank 0                         |         | Bank 1                                     |            | Bank 2                                     |            | Bank 3                |

| plemented on PI                | C16C773 | 8.                                         |            |                                            |            |                       |

# **PIC16C77X**

| Address              | Name       | Bit 7                | Bit 6                                               | Bit 5                       | Bit 4           | Bit 3        | Bit 2           | Bit 1          | Bit 0   | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(2) |

|----------------------|------------|----------------------|-----------------------------------------------------|-----------------------------|-----------------|--------------|-----------------|----------------|---------|--------------------------|-------------------------------------|

| Bank 1               |            |                      |                                                     | 1                           | 1               |              | 1               |                | 1       | 1                        |                                     |

| 80h <sup>(4)</sup>   | INDF       | Addressing           | this location                                       | uses content                | s of FSR to ad  | dress data m | emory (not a    | ı physical reç | gister) | 0000 0000                | 0000 0000                           |

| 81h                  | OPTION_REG | RBPU                 | INTEDG                                              | TOCS                        | TOSE            | PSA          | PS2             | PS1            | PS0     | 1111 1111                | 1111 1111                           |

| 82h <sup>(4)</sup>   | PCL        | Program Co           | unter's (PC)                                        | Least Signifi               | cant Byte       | ł            |                 |                |         | 0000 0000                | 0000 0000                           |

| 83h <sup>(4)</sup>   | STATUS     | IRP                  | RP1                                                 | RP0                         | TO              | PD           | Z               | DC             | С       | 0001 1xxx                | 000q quuu                           |

| 84h <sup>(4)</sup>   | FSR        | Indirect data        | a memory ad                                         | Idress pointer              |                 |              |                 |                |         | xxxx xxxx                | uuuu uuuu                           |

| 85h                  | TRISA      | _                    | — bit5 <sup>(5)</sup> PORTA Data Direction Register |                             |                 |              |                 |                |         |                          | 11 1111                             |

| 86h                  | TRISB      | PORTB Dat            | a Direction F                                       | Register                    |                 |              |                 |                |         | 1111 1111                | 1111 1111                           |

| 87h                  | TRISC      | PORTC Dat            | a Direction F                                       | Register                    |                 |              |                 |                |         | 1111 1111                | 1111 1111                           |

| 88h <sup>(5)</sup>   | TRISD      | PORTD Dat            | a Direction F                                       | Register                    |                 |              |                 |                |         | 1111 1111                | 1111 1111                           |

| 89h <b>(5)</b>       | TRISE      | IBF                  | OBF                                                 | IBOV                        | PSPMODE         | —            | PORTE Dat       | a Direction E  | Bits    | 0000 -111                | 0000 -111                           |

| 8Ah <sup>(1,4)</sup> | PCLATH     | _                    | -                                                   | —                           | Write Buffer fo | or the upper | 5 bits of the F | Program Cou    | inter   | 0 0000                   | 0 0000                              |

| 8Bh <sup>(4)</sup>   | INTCON     | GIE                  | PEIE                                                | TOIE                        | INTE            | RBIE         | TOIF            | INTF           | RBIF    | 0000 000x                | 0000 000u                           |

| 8Ch                  | PIE1       | PSPIE <sup>(3)</sup> | ADIE                                                | RCIE                        | TXIE            | SSPIE        | CCP1IE          | TMR2IE         | TMR1IE  | 0000 0000                | 0000 0000                           |

| 8Dh                  | PIE2       | LVDIE                | -                                                   | _                           | _               | BCLIE        | _               | -              | CCP2IE  | 0 00                     | 0 00                                |

| 8Eh                  | PCON       | -                    | -                                                   | —                           | —               | —            | —               | POR            | BOR     | qq                       | uu                                  |

| 8Fh                  | —          | Unimplemer           | nted                                                |                             |                 |              |                 |                |         | —                        | —                                   |

| 90h                  | —          | Unimplemen           | nted                                                |                             |                 |              |                 |                |         | —                        | -                                   |

| 91h                  | SSPCON2    | GCEN                 | AKSTAT                                              | AKDT                        | AKEN            | RCEN         | PEN             | RSEN           | SEN     | 0000 0000                | 0000 0000                           |

| 92h                  | PR2        | Timer2 Peri          | od Register                                         |                             |                 |              |                 |                |         | 1111 1111                | 1111 1111                           |

| 93h                  | SSPADD     | Synchronou           | s Serial Port                                       | t (I <sup>2</sup> C mode) A | Address Regist  | er           |                 |                |         | 0000 0000                | 0000 0000                           |

| 94h                  | SSPSTAT    | SMP                  | CKE                                                 | D/A                         | Р               | S            | R/W             | UA             | BF      | 0000 0000                | 0000 0000                           |

| 95h                  | —          | Unimplemer           | nted                                                |                             |                 |              |                 |                |         | _                        | _                                   |

| 96h                  | _          | Unimpleme            | nted                                                |                             |                 |              |                 |                |         | _                        | _                                   |

| 97h                  | —          | Unimplemer           | nted                                                |                             |                 |              |                 |                |         | _                        | _                                   |

| 98h                  | TXSTA      | CSRC                 | TX9                                                 | TXEN                        | SYNC            | —            | BRGH            | TRMT           | TX9D    | 0000 -010                | 0000 -010                           |

| 99h                  | SPBRG      | Baud Rate (          | Generator Re                                        | egister                     |                 |              |                 |                |         | 0000 0000                | 0000 0000                           |

| 9Ah                  | —          | Unimplemer           | nted                                                |                             |                 |              |                 |                |         | _                        | _                                   |

| 9Bh                  | REFCON     | VRHEN                | VRLEN                                               | VRHOEN                      | VRLOEN          | —            | —               | _              | —       | 0000                     | 0000                                |

| 9Ch                  | LVDCON     | —                    | _                                                   | BGST                        | LVDEN           | LV3          | LV2             | LV1            | LV0     | 00 0101                  | 00 0101                             |

| 9Ah                  | —          | Unimplemer           | nimplemented                                        |                             |                 |              |                 |                |         |                          | _                                   |

| 9Eh                  | ADRESL     | A/D Low By           | Low Byte Result Register                            |                             |                 |              |                 |                |         |                          | uuuu uuuu                           |

| 9Fh                  | ADCON1     | ADFM                 | VCFG2                                               | VCFG1                       | VCFG0           | PCFG3        | PCFG2           | PCFG1          | PCFG0   | 0000 0000                | 0000 0000                           |

#### TABLE 2-1 PIC16C77X SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Legend:

Shaded locations are unimplemented, read as '0'. Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset. 2:

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

4: These registers can be addressed from any bank.

5: These registers/bits are not implemented on the 28-pin devices read as '0'.

#### 5.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers; TMR1H and TMR1L)

- Readable and writable (Both registers)

- · Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- · Reset from CCP module trigger

Timer1 has a control register, shown in Figure 5-1. Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Figure 5-3 is a simplified block diagram of the Timer1 module.

Additional information on timer modules is available in the PICmicro™ Mid-Range Reference Manual, (DS33023).

#### 5.1 **Timer1 Operation**

Timer1 can operate in one of these modes:

- · As a timer

- · As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the clock select bit. TMR1CS (T1CON<1>).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored.

Timer1 also has an internal "reset input". This reset can be generated by the CCP module (Section 7.0).

#### T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h) U-0 U-0 R/W-0 R/W-0 B/W-0 R/W-0 **B/W-0** R/W-0 T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON R = Readable bit W = Writable bit bit7 bit0 = Unimplemented bit, U read as '0' n = Value at POR reset bit 7-6: Unimplemented: Read as '0' bit 5-4: T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits 11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value 00 = 1:1 Prescale value T1OSCEN: Timer1 Oscillator Enable Control bit hit 3 1 = Oscillator is enabled 0 = Oscillator is shut off Note: The oscillator inverter and feedback resistor are turned off to eliminate power drain T1SYNC: Timer1 External Clock Input Synchronization Control bit bit 2: TMR1CS = 11 = Do not synchronize external clock input 0 = Synchronize external clock input TMR1CS = 0This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0. TMR1CS: Timer1 Clock Source Select bit bit 1: 1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge) 0 = Internal clock (Fosc/4)

## FIGURE 5-1:

- 1 = Enables Timer1

- 0 = Stops Timer1

# PIC16C77X

NOTES:

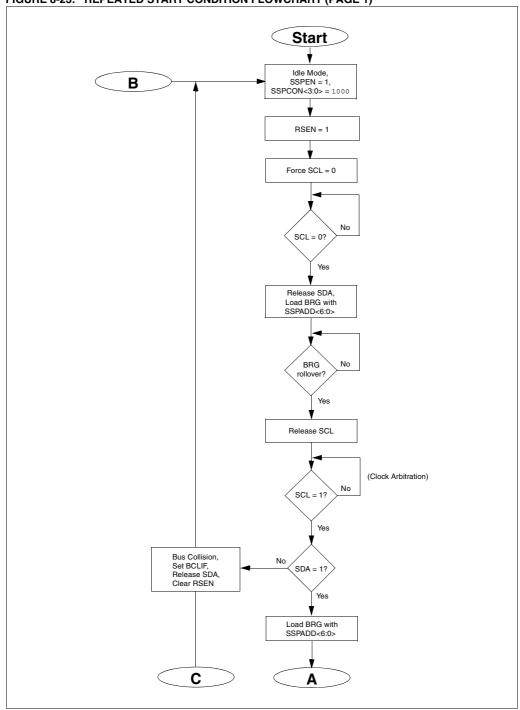

FIGURE 8-23: REPEATED START CONDITION FLOWCHART (PAGE 1)

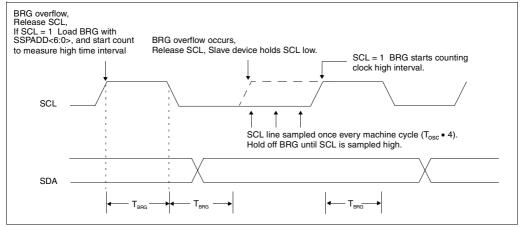

#### 8.2.15 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit, or repeated start/stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the baud rate generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 8-33).

#### 8.2.16 SLEEP OPERATION

While in sleep mode, the I<sup>2</sup>C module can receive addresses or data, and when an address match or complete byte transfer occurs wake the processor from sleep (if the SSP interrupt is enabled).

#### 8.2.17 EFFECTS OF A RESET

A reset disables the SSP module and terminates the current transfer.

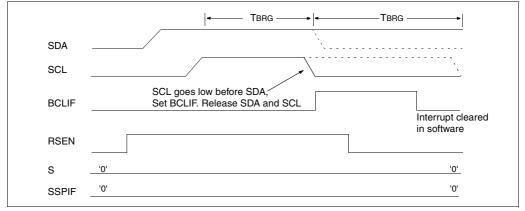

#### FIGURE 8-33: CLOCK ARBITRATION TIMING IN MASTER TRANSMIT MODE

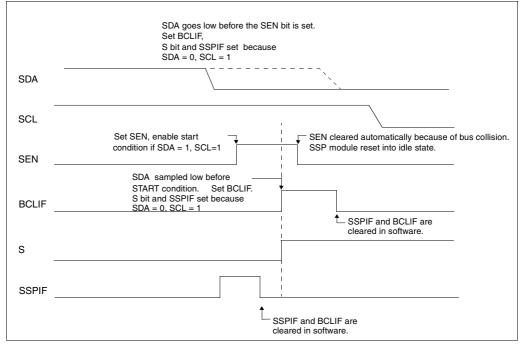

#### 8.2.18.15 BUS COLLISION DURING A START CONDITION

During a START condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the START condition (Figure 8-35).

- b) SCL is sampled low before SDA is asserted low. (Figure 8-36).

During a START condition both the SDA and the SCL pins are monitored.

lf:

the SDA pin is already low or the SCL pin is already low,

then:

the START condition is aborted, and the BCLIF flag is set, and the SSP module is reset to its IDLE state (Figure 8-35).

The START condition begins with the SDA and SCL pins de-asserted. When the SDA pin is sampled high, the baud rate generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low

while SDA is high, a bus collision occurs, because it is assumed that another master is attempting to drive a data '1' during the START condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 8-37). If however a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The baud rate generator is then reloaded and counts down to 0, and during this time, if the SCL pins is sampled as '0', a bus collision does not occur. At the end of the BRG count the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a START condition is that no two bus masters can assert a START condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the START condition, and if the address is the same, arbitration must be allowed to continue into the data portion, REPEATED START, or STOP conditions.

## FIGURE 8-35: BUS COLLISION DURING START CONDITION (SDA ONLY)

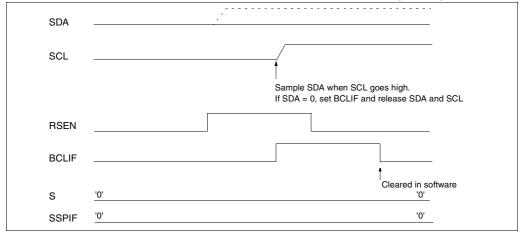

# 8.2.18.16 BUS COLLISION DURING A REPEATED START CONDITION

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user de-asserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0>, and counts down to 0. The SCL pin is then deasserted, and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e. another master is attempting to transmit a data '0'). If however SDA is sampled high then the BRG is reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs, because no two masters can assert SDA at exactly the same time.

If, however, SCL goes from high to low before the BRG times out and SDA has not already been asserted, then a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition.

If at the end of the BRG time out both SCL and SDA are still high, the SDA pin is driven low, the BRG is reloaded, and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete (Figure 8-38).

FIGURE 8-38: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

#### FIGURE 8-39: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

#### 9.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In asynchronous mode bit BRGH (TXSTA<2>) also controls the baud rate. In synchronous mode bit BRGH is ignored. Table 9-1 shows the formula for computation of the baud rate for different USART modes which only apply in master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 9-1. From this, the error in baud rate can be determined.

Example 9-1 shows the calculation of the baud rate error for the following conditions:

Fosc = 16 MHz Desired Baud Rate = 9600 BRGH = 0 SYNC = 0

#### EXAMPLE 9-1: CALCULATING BAUD RATE ERROR

#### Desired Baud rate = Fosc / (64 (X + 1))

9600 = 1600000 / (64 (X + 1))X =  $\lfloor 25.042 \rfloor = 25$

Calculated Baud Rate=16000000 / (64 (25 + 1))

= 9615

Error = (Calculated Baud Rate - Desired Baud Rate) Desired Baud Rate

= (9615 - 9600) / 9600

= 0.16%

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the Fosc/(16(X + 1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

9.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

#### TABLE 9-1BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)     |

|------|-------------------------------------------|---------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate= Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = FOSC/(4(X+1))   | NA                        |

X = value in SPBRG (0 to 255)

## TABLE 9-2 REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name                                   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|----------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 98h     | TXSTA                                  | CSRC  | TX9   | TXEN  | SYNC  | —     | BRGH  | TRMT  | TX9D  | 0000 -010                | 0000 -010                 |

| 18h     | RCSTA                                  | SPEN  | RX9   | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 0000 000x                | 0000 000x                 |

| 99h     | 99h SPBRG Baud Rate Generator Register |       |       |       |       |       |       |       |       | 0000 0000                | 0000 0000                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used by the BRG.

# 12.0 SPECIAL FEATURES OF THE CPU

These PICmicro devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Low-voltage detection

- SLEEP

- Code protection

- · ID locations

- · In-circuit serial programming

These devices have a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up type resets only (POR, BOR), designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

Additional information on special features is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

#### 12.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

Some of the core features provided may not be necessary to each application that a device may be used for. The configuration word bits allow these features to be configured/enabled/disabled as necessary. These features include code protection, brown-out reset and its trippoint, the power-up timer, the watchdog timer and the devices oscillator mode. As can be seen in Figure 12-1, some additional configuration word bits have been provided for brown-out reset trippoint selection.

# 14.0 DEVELOPMENT SUPPORT

# 14.1 Development Tools

The PICmicro<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- MPLAB<sup>™</sup> -ICE Real-Time In-Circuit Emulator

- ICEPIC<sup>™</sup> Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- SIMICE

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB<sup>™</sup> SIM Software Simulator

- MPLAB-C17 (C Compiler)

- Fuzzy Logic Development System (*fuzzy*TECH<sup>®</sup>–MP)

- KEELOQ<sup>®</sup> Evaluation Kits and Programmer

#### 14.2 <u>MPLAB-ICE: High Performance</u> Universal In-Circuit Emulator with MPLAB IDE

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers (MCUs). MPLAB-ICE is supplied with the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support all new Microchip microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x or Windows 95 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE is available in two versions. MPLAB-ICE 1000 is a basic, low-cost emulator system with simple trace capabilities. It shares processor modules with the MPLAB-ICE 2000. This is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems will operate across the entire operating speed reange of the PICmicro MCU.

#### 14.3 ICEPIC: Low-Cost PICmicro In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC12CXXX, PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 386 through Pentium™ based machines under Windows 3.x, Windows 95, or Windows NT environment. ICEPIC features real time, non-intrusive emulation.

#### 14.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices. It can also set configuration and code-protect bits in this mode.

#### 14.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923, PIC16C924 and PIC17C756 may be supported with an adapter socket. PICSTART Plus is CE compliant.

TABLE 14-1 DEVELOPMENT TOOLS FROM MICROCHIP

| TABLE                      | 14-1 DE                 | VELO                                                 | PMENT T                                            | OOL                     | SFROM                                                                 | MICH                               | OCHIP                                           |                                         |                                   |                                      | ,      |            |          |          |                                       | ,                         |

|----------------------------|-------------------------|------------------------------------------------------|----------------------------------------------------|-------------------------|-----------------------------------------------------------------------|------------------------------------|-------------------------------------------------|-----------------------------------------|-----------------------------------|--------------------------------------|--------|------------|----------|----------|---------------------------------------|---------------------------|

| HCS200<br>HCS300<br>HCS301 |                         |                                                      |                                                    |                         |                                                                       |                                    |                                                 | >                                       | ~                                 |                                      |        |            |          |          | >                                     | >                         |

| 24CXX<br>25CXX<br>93CXX    |                         |                                                      |                                                    |                         |                                                                       | >                                  |                                                 | >                                       |                                   | >                                    |        |            |          |          |                                       |                           |

| PIC17C7XX                  | >                       |                                                      | >                                                  | ∕                       |                                                                       |                                    | >                                               | >                                       |                                   |                                      |        |            |          |          |                                       |                           |

| PIC17C4X                   | >                       |                                                      | >                                                  | ~                       | >                                                                     |                                    | >                                               | >                                       |                                   |                                      |        | ``         | >        |          |                                       |                           |

| PIC16C9XX                  | `                       | `                                                    | `                                                  |                         | >                                                                     |                                    | >                                               | >                                       |                                   |                                      |        |            |          | >        |                                       |                           |

| PIC16C8X                   | >                       | >                                                    | >                                                  |                         | >                                                                     |                                    | >                                               | >                                       |                                   |                                      |        | ``         | >        |          |                                       |                           |

| PIC16C7XX                  | ``                      | `                                                    | `                                                  |                         | >                                                                     |                                    | >                                               | >                                       |                                   |                                      |        |            | `        |          |                                       |                           |

| PIC16C6X                   | >                       | >                                                    | >                                                  |                         | >                                                                     |                                    | >                                               | >                                       |                                   |                                      |        |            | `        |          |                                       |                           |

| PIC16CXXX                  | >                       | >                                                    | >                                                  |                         | >                                                                     |                                    | >                                               | >                                       |                                   |                                      |        | `          | ~        |          |                                       |                           |

| PIC16C5X                   | >                       | >                                                    | >                                                  |                         | >                                                                     |                                    | >                                               | >                                       |                                   |                                      | >      | ``         | >        |          |                                       |                           |

| PIC14000                   | >                       |                                                      | >                                                  |                         | >                                                                     |                                    | >                                               | >                                       |                                   |                                      |        | >          |          |          |                                       |                           |

| PIC12C5XX                  | >                       |                                                      | >                                                  |                         | >                                                                     |                                    | >                                               | >                                       |                                   |                                      | >      |            |          |          |                                       |                           |

|                            | MPLAB <sup>™</sup> -ICE | ICEPIC <sup>TM</sup> Low-Cost<br>In-Circuit Emulator | MPLAB™<br>Integrated<br>Development<br>Environment | MPLAB™ C17*<br>Compiler | <i>fuzzy</i> TECH®-MP<br>Explorer/Edition<br>Fuzzy Logic<br>Dev. Tool | Total Endurance™<br>Software Model | PICSTART®Plus<br>Low-Cost<br>Universal Dev. Kit | PRO MATE® II<br>Universal<br>Programmer | KEELOQ <sup>®</sup><br>Programmer | SEEVAL <sup>®</sup><br>Designers Kit | SIMICE | PICDEM-14A | PICDEM-1 | PICDEM-3 | KEELoq <sup>®</sup><br>Evaluation Kit | KεεLoα<br>Transponder Kit |

|                            | tor Products            | Software Tools Emulator Product                      |                                                    |                         |                                                                       |                                    |                                                 | ւօգւթաս                                 | d                                 |                                      |        | spi        | soa      | owe      | Ð                                     |                           |

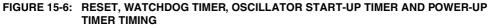

# TABLE 15-7 RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

← 35 →

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions                                    |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|-----------------------------------------------|

| 30*              | TmcL  | MCLR Pulse Width (low)                                 | 100 | —        | —   | ns    | $VDD = 5V$ , $-40^{\circ}C$ to $+85^{\circ}C$ |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +85°C                      |

| 32*              | Tost  | Oscillation Start-up Timer Period                      | -   | 1024Tosc |     | —     | Tosc = OSC1 period                            |

| 33*              | Tpwrt | Power up Timer Period                                  | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +85°C                      |

| 34*              | Tioz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset |     | _        | 100 | ns    |                                               |

| 35*              | TBOR  | Brown-out Reset pulse width                            | 100 | —        | —   | μS    | $VDD \le VBOR (D005)$                         |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# FIGURE 15-8: BANDGAP START-UP TIME

| TABLE 15-8     | BANDGAP START-UP TIME | $\sum$           |

|----------------|-----------------------|------------------|

|                |                       | 2                |

| Bandgap stable | ← TBGAP —►            |                  |

| Enable Bandgap |                       |                  |

| Vbgap          |                       | <br>'BGAP = 1.2V |

#### **TABLE 15-8 BANDGAP START-UP TIME**

| Parameter<br>No. | Sym       | Characteristic                         | Min | Тур | t  | Max  | ί | Inits | $\nearrow$            | Conc            | litions                                                    | >            |

|------------------|-----------|----------------------------------------|-----|-----|----|------|---|-------|-----------------------|-----------------|------------------------------------------------------------|--------------|

| 36*              | Tbgap     | Bandgap start-up time                  |     | 30  | // | THED |   | μs    | the insta<br>is enabl | ed and<br>bandg | e time bet<br>t the ban<br>d the mor<br>gap refere<br>ble. | dgap<br>nent |

| * Tho            | eo naramo | store are characterized but not tested |     |     |    |      |   | ノー    | •                     |                 |                                                            |              |

These parameters are characterized but not tested. Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

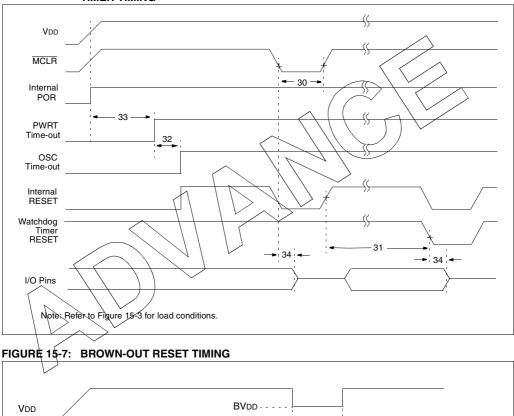

### FIGURE 15-12: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

# TABLE 15-13 CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Parameter<br>No. | Sym      | Characteristic   |                | / /     |                     | Min                   | Тур† | Мах | Units | Conditions                        |

|------------------|----------|------------------|----------------|---------|---------------------|-----------------------|------|-----|-------|-----------------------------------|

| 50*              | Tcç⊾∕    | CCP1 and CCP2    | No Pres        | caler   |                     | 0.5TCY + 20           | _    | _   | ns    |                                   |

|                  |          | input low time   |                |         | PIC16 <b>C</b> 77X  | 10                    | _    | -   | ns    |                                   |

|                  |          | $\land \land )$  | With Pre       | escaler | PIC16 <b>LC</b> 77X | 20                    | —    |     | ns    |                                   |

| 51*              | TCCH     | CCP1 and CCP2    | No Pres        | caler   |                     | 0.5TCY + 20           | —    |     | ns    |                                   |

|                  | > )      | input high time  |                |         | PIC16 <b>C</b> 77X  | 10                    | —    |     | ns    |                                   |

|                  | $\frown$ | $\checkmark$     | With Prescaler |         | PIC16 <b>LC</b> 77X | 20                    | _    | -   | ns    |                                   |

| 52*              | TccP     | CCP1 and CCP2 ir | nput peric     | bd      |                     | <u>3Tcy + 40</u><br>N |      | Ι   | ns    | N = prescale value<br>(1,4 or 16) |

| 53*              | TccR     | CCP1 and CCP2 o  | utput fall     | time    | PIC16 <b>C</b> 77X  | _                     | 10   | 25  | ns    |                                   |

|                  |          |                  |                |         | PIC16 <b>LC</b> 77X | —                     | 25   | 45  | ns    |                                   |

| 54*              | TccF     | CCP1 and CCP2 o  | utput fall     | time    | PIC16 <b>C</b> 77X  | —                     | 10   | 25  | ns    |                                   |

|                  |          |                  |                |         | PIC16 <b>LC</b> 77X | _                     | 25   | 45  | ns    |                                   |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

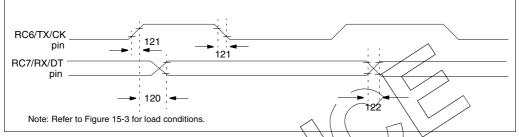

### FIGURE 15-14: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

# TABLE 15-15 USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                    |                         | Min_ | Typt | Max | Units | Conditions |

|--------------|----------|-----------------------------------|-------------------------|------|------|-----|-------|------------|

| 120*         | TckH2dtV | SYNC XMIT (MASTER & SLAVE)        | PIC16C774/773           | _    | _    | 80  | ns    |            |

|              |          | Clock high to data out valid      | PIC16LC774/773          | —    | —    | 100 | ns    |            |

| 121*         | Tckrf    | Clock out rise time and fall time | PIC16C774/773           | _    | —    | 45  | ns    |            |

|              |          | (Master Mode)                     | PIC16LC774/773          | —    | —    | 50  | ns    |            |

| 122*         | Tdtrf    | Data out rise time and fall time  | PIC16 <b>C</b> 774/773  | —    | —    | 45  | ns    |            |

|              |          |                                   | PIC16 <b>LC</b> 774/773 | —    | —    | 50  | ns    |            |

\* These parameters are characterized but not tested.

+: Data in "Typ" column is at \$V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

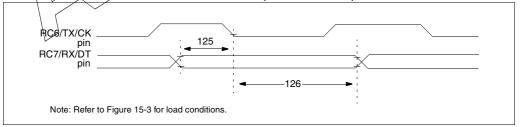

# FIGURE 15-15: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

# TABLE 15-16 USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                 | Min | Тур† | Max | Units    | Conditions |

|------------------|----------|--------------------------------------------------------------------------------|-----|------|-----|----------|------------|

| 125*             | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data setup before $CK \downarrow$ (DT setup time) | 15  |      |     |          |            |

| 126*             | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                 | 15  | =    |     | ns<br>ns |            |

\* These parameters are characterized but not tested.

†: Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

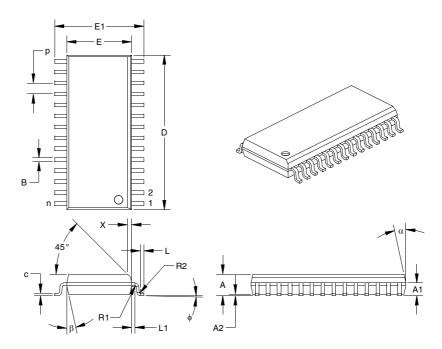

### 17.4 K04-052 28-Lead Plastic Small Outline (SO) – Wide, 300 mil

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                   |                | INCHES* |       |       | MILLIMETERS |       |       |  |

|-------------------------|----------------|---------|-------|-------|-------------|-------|-------|--|

| Dimension Limits        |                | MIN     | NOM   | MAX   | MIN         | NOM   | MAX   |  |

| Pitch                   | р              |         | 0.050 |       |             | 1.27  |       |  |

| Number of Pins          | n              |         | 28    |       |             | 28    |       |  |

| Overall Pack. Height    | A              | 0.093   | 0.099 | 0.104 | 2.36        | 2.50  | 2.64  |  |

| Shoulder Height         | A1             | 0.048   | 0.058 | 0.068 | 1.22        | 1.47  | 1.73  |  |

| Standoff                | A2             | 0.004   | 0.008 | 0.011 | 0.10        | 0.19  | 0.28  |  |

| Molded Package Length   | D <sup>‡</sup> | 0.700   | 0.706 | 0.712 | 17.78       | 17.93 | 18.08 |  |

| Molded Package Width    | E‡             | 0.292   | 0.296 | 0.299 | 7.42        | 7.51  | 7.59  |  |

| Outside Dimension       | E1             | 0.394   | 0.407 | 0.419 | 10.01       | 10.33 | 10.64 |  |

| Chamfer Distance        | х              | 0.010   | 0.020 | 0.029 | 0.25        | 0.50  | 0.74  |  |

| Shoulder Radius         | R1             | 0.005   | 0.005 | 0.010 | 0.13        | 0.13  | 0.25  |  |

| Gull Wing Radius        | R2             | 0.005   | 0.005 | 0.010 | 0.13        | 0.13  | 0.25  |  |

| Foot Length             | L              | 0.011   | 0.016 | 0.021 | 0.28        | 0.41  | 0.53  |  |

| Foot Angle              | φ              | 0       | 4     | 8     | 0           | 4     | 8     |  |

| Radius Centerline       | L1             | 0.010   | 0.015 | 0.020 | 0.25        | 0.38  | 0.51  |  |

| Lead Thickness          | с              | 0.009   | 0.011 | 0.012 | 0.23        | 0.27  | 0.30  |  |

| Lower Lead Width        | B <sup>†</sup> | 0.014   | 0.017 | 0.019 | 0.36        | 0.42  | 0.48  |  |

| Mold Draft Angle Top    | α              | 0       | 12    | 15    | 0           | 12    | 15    |  |

| Mold Draft Angle Bottom | β              | 0       | 12    | 15    | 0           | 12    | 15    |  |

\* Controlling Parameter.

<sup>†</sup> Dimension "B" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B."

<sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."

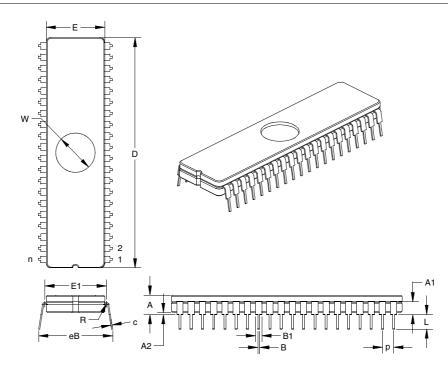

## 17.7 K04-014 40-Lead Ceramic Dual In-line with Window (JW) – 600 mil

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                        |    | INCHES* |       |       | MILLIMETERS |       |       |  |

|------------------------------|----|---------|-------|-------|-------------|-------|-------|--|

| Dimension Limits             |    | MIN     | NOM   | MAX   | MIN         | NOM   | MAX   |  |

| PCB Row Spacing              |    |         | 0.600 |       |             | 15.24 |       |  |

| Number of Pins               | n  |         | 40    |       |             | 40    |       |  |

| Pitch                        | р  | 0.098   | 0.100 | 0.102 | 2.49        | 2.54  | 2.59  |  |

| Lower Lead Width             | В  | 0.016   | 0.020 | 0.023 | 0.41        | 0.50  | 0.58  |  |

| Upper Lead Width             | B1 | 0.050   | 0.053 | 0.055 | 1.27        | 1.33  | 1.40  |  |

| Shoulder Radius              | R  | 0.000   | 0.005 | 0.010 | 0.00        | 0.13  | 0.25  |  |

| Lead Thickness               | с  | 0.008   | 0.011 | 0.014 | 0.20        | 0.28  | 0.36  |  |

| Top to Seating Plane         | А  | 0.190   | 0.205 | 0.220 | 4.83        | 5.21  | 5.59  |  |

| Top of Lead to Seating Plane | A1 | 0.117   | 0.135 | 0.153 | 2.97        | 3.43  | 3.89  |  |

| Base to Seating Plane        | A2 | 0.030   | 0.045 | 0.060 | 0.00        | 1.14  | 1.52  |  |

| Tip to Seating Plane         | L  | 0.135   | 0.140 | 0.145 | 3.43        | 3.56  | 3.68  |  |

| Package Length               | D  | 2.040   | 2.050 | 2.060 | 51.82       | 52.07 | 52.32 |  |

| Package Width                | E  | 0.514   | 0.520 | 0.526 | 13.06       | 13.21 | 13.36 |  |

| Radius to Radius Width       | E1 | 0.560   | 0.580 | 0.600 | 14.22       | 14.73 | 15.24 |  |

| Overall Row Spacing          | eB | 0.610   | 0.660 | 0.710 | 15.49       | 16.76 | 18.03 |  |

| Window Diameter              | W  | 0.340   | 0.350 | 0.360 | 8.64        | 8.89  | 9.14  |  |

\* Controlling Parameter.

# PIC16C77X

NOTES: