Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | PIC                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 22                                                                     |

| Program Memory Size        | 7KB (4K x 14)                                                          |

| Program Memory Type        | ОТР                                                                    |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                              |

| Data Converters            | A/D 6x12b                                                              |

| Oscillator Type            | External                                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                        |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | 28-SPDIP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c773-sp |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

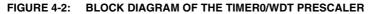

#### 4.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

Note: To avoid an unintended device RESET, a specific instruction sequence (shown in the PICmicro™ Mid-Range Reference Manual, DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

#### 4.3 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut off during SLEEP.

#### TABLE 4-1 REGISTERS ASSOCIATED WITH TIMER0

| Address               | Name       | Bit 7  | Bit 6      | Bit 5                         | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------------------|------------|--------|------------|-------------------------------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 01h,101h              | TMR0       | Timer0 | module's r | egister                       |       |       |       |       |       | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE    | PEIE       | TOIE                          | INTE  | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x                | 0000 000u                 |

| 81h,181h              | OPTION_REG | RBPU   | INTEDG     | TOCS                          | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

| 85h                   | TRISA      | _      | _          | PORTA Data Direction Register |       |       |       |       |       | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

#### 8.0 MASTER SYNCHRONOUS SERIAL PORT (MSSP) MODULE

The Master Synchronous Serial Port (MSSP) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D converters, etc. The MSSP module can operate in one of two modes:

- Serial Peripheral Interface (SPI)

- Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)

determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 8-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

#### EXAMPLE 8-1: LOADING THE SSPBUF (SSPSR) REGISTER

|      | BSF   | STATUS, | RP0  | ;Specify Bank 1   |

|------|-------|---------|------|-------------------|

| LOOP | BTFSS | SSPSTAT | , BF | ;Has data been    |

|      |       |         |      | ;received         |

|      |       |         |      | ;(transmit        |

|      |       |         |      | ;complete)?       |

|      | GOTO  | LOOP    |      | ;No               |

|      | BCF   | STATUS, | RP0  | ;Specify Bank 0   |

|      | MOVF  | SSPBUF, | W    | ;W reg = contents |

|      |       |         |      | ;of SSPBUF        |

|      | MOVWF | RXDATA  |      | ;Save in user RAM |

|      | MOVF  | TXDATA, | W    | ;W reg = contents |

|      |       |         |      | ; of TXDATA       |

|      | MOVWF | SSPBUF  |      | ;New data to xmit |

The SSPSR is not directly readable or writable, and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP status register (SSPSTAT) indicates the various status conditions.

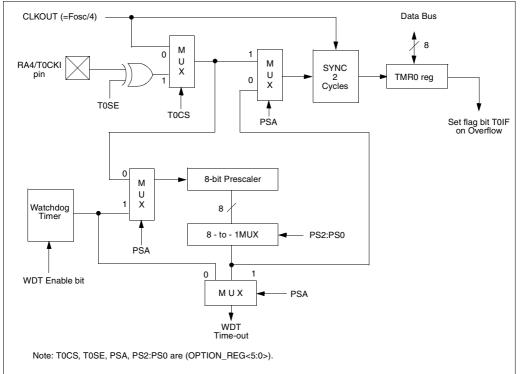

#### 8.1.2 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON registers, and then set bit SSPEN. This configures the

FIGURE 8-5: SPI MASTER/SLAVE CONNECTION

SDI, SDO, SCK, and  $\overline{SS}$  pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- · SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

#### 8.1.3 TYPICAL CONNECTION

Figure 8-5 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

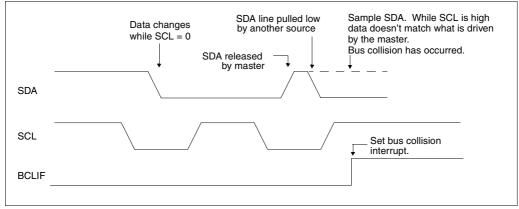

## 8.2.18 MULTI -MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the I<sup>2</sup>C port to its IDLE state. (Figure 8-34).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are de-asserted, and the SSPBUF can be written to. When the user services the bus collision interrupt service routine, and if the  $l^2C$  bus is free, the user can resume communication by asserting a START condition.

If a START, Repeated Start, STOP, or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision interrupt service routine, and if the  $l^2$ C bus is free, the user can resume communication by asserting a START condition.

The Master will continue to monitor the SDA and SCL pins, and if a STOP condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when bus collision occurred.

In multi-master mode, the interrupt generation on the detection of start and stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is idle and the S and P bits are cleared.

FIGURE 8-34: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

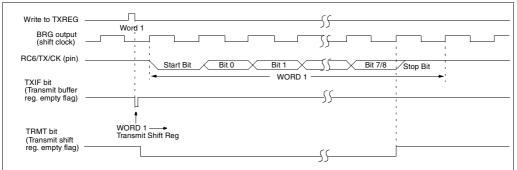

#### FIGURE 9-4: ASYNCHRONOUS TRANSMISSION

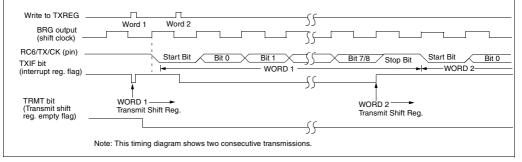

#### FIGURE 9-5: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

#### TABLE 9-6 REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address | Name                                   | Bit 7                | Bit 6    | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|----------------------------------------|----------------------|----------|----------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Ch     | PIR1                                   | PSPIF <sup>(1)</sup> | ADIF     | RCIF     | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h     | RCSTA                                  | SPEN                 | RX9      | SREN     | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 19h     | TXREG                                  | USART Tra            | ansmit F | Register |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1                                   | PSPIE <sup>(1)</sup> | ADIE     | RCIE     | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h     | TXSTA                                  | CSRC                 | TX9      | TXEN     | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h     | 99h SPBRG Baud Rate Generator Register |                      |          |          |       |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

#### 9.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 9-6. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at FOSC.

The USART module has a special provision for multiprocessor communication. When the RX9 bit is set in the RCSTA register, 9-bits are received and the ninth bit is placed in the RX9D status bit of the RSTA register. The port can be programmed such that when the stop bit is received, the serial port interrupt will only be activated if the RX9D bit = 1. This feature is enabled by setting the ADDEN bit RCSTA<3> in the RCSTA register. This feature can be used in a multi-processor system as follows:

A master processor intends to transmit a block of data to one of many slaves. It must first send out an address byte that identifies the target slave. An address byte is identified by the RX9D bit being a '1' (instead of a '0' for a data byte). If the ADDEN bit is set in the slave's RCSTA register, all data bytes will be ignored. However, if the ninth received bit is equal to a '1', indicating that the received byte is an address, the slave will be interrupted and the contents of the RSR register will be transferred into the receive buffer. This allows the slave can examine the received byte to see if it is addressed. The addressed slave will then clear its ADDEN bit and prepare to receive data bytes from the master.

When ADDEN is set, all data bytes are ignored. Following the STOP bit, the data will not be loaded into the receive buffer, and no interrupt will occur. If another byte is shifted into the RSR register, the previous data byte will be lost.

The ADDEN bit will only take effect when the receiver is configured in 9-bit mode.

The receiver block diagram is shown in Figure 9-6.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

## 9.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

Steps to follow when setting up an Asynchronous Reception with Address Detect Enabled:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- · If interrupts are desired, then set enable bit RCIE.

- Set bit RX9 to enable 9-bit reception.

- · Set ADDEN to enable address detect.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register, to determine if the device is being addressed.

- If any error occurred, clear the error by clearing enable bit CREN.

- If the device has been addressed, clear the ADDEN bit to allow data bytes and address bytes to be read into the receive buffer, and interrupt the CPU.

#### 9.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner i.e. transmission and reception do not occur at the same time. When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 9.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 9-3. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcycle), the TXREG is empty and interrupt bit, TXIF (PIR1<4>) is set. The interrupt can be

enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 9.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

| Address | Name                               | Bit 7                | Bit 6  | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|------------------------------------|----------------------|--------|----------|-------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1                               | PSPIF <sup>(1)</sup> | ADIF   | RCIF     | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA                              | SPEN                 | RX9    | SREN     | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                 |

| 19h     | TXREG                              | USART Tr             | ansmit | Register |       |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1                               | PSPIE <sup>(1)</sup> | ADIE   | RCIE     | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA                              | CSRC                 | TX9    | TXEN     | SYNC  |       | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG Baud Rate Generator Register |                      |        |          |       |       |        |        |        |                          | 0000 0000                 |

#### TABLE 9-8 REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for Synchronous Master Transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

#### 9.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>) or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set then CREN takes precedence.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. (Section 9.1)

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- 8. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREG register.

- 10. If any error occurred, clear the error by clearing bit CREN.

| Address | Name                                   | Bit 7                | Bit 6    | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|----------------------------------------|----------------------|----------|----------|-------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1                                   | PSPIF <sup>(1)</sup> | ADIF     | RCIF     | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA                                  | SPEN                 | RX9      | SREN     | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                 |

| 1Ah     | RCREG                                  | USART R              | eceive I | Register |       |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1                                   | PSPIE <sup>(1)</sup> | ADIE     | RCIE     | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA                                  | CSRC                 | TX9      | TXEN     | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | 99h SPBRG Baud Rate Generator Register |                      |          |          |       |       |        |        |        |                          | 0000 0000                 |

#### TABLE 9-9 REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

#### FIGURE 9-11: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

| C7/RX/DT pin            | bit0        | , bit1      | bit2        | ,bit3            | bit4      | , bit5           | bit6        | bit7             | 1                |

|-------------------------|-------------|-------------|-------------|------------------|-----------|------------------|-------------|------------------|------------------|

| C6/TX/CK pin            |             |             |             |                  |           |                  |             |                  | 1<br>1<br>1      |

| Write to                |             | 1<br>1<br>1 | 1<br>1<br>1 | 1<br>T<br>L<br>T | <br> <br> | 1<br>1<br>1<br>1 | 1<br>T<br>T | 1<br>1<br>1<br>1 | 1<br>1<br>1<br>1 |

| SREN bit                | 1           | 1<br>1<br>1 | 1<br>1<br>1 | 1<br>1<br>1      |           | 1                | t<br>t<br>t |                  | 1                |

| CREN bit                | 1           | 1<br>1<br>1 | 1<br>1      | t<br>t           |           | ,<br>,           | t           | 1<br>1           |                  |

| RCIF bit<br>(interrupt) | 1<br>1<br>1 | 1<br>1<br>1 | 1<br>1<br>1 | 1<br>1<br>1      |           | 1                | 1<br>1<br>1 | ſ                |                  |

| Read<br>RXREG           | 1           | 1<br>1<br>1 |             | 1<br>1           |           | ,<br>,<br>,      | 1<br>1<br>1 |                  |                  |

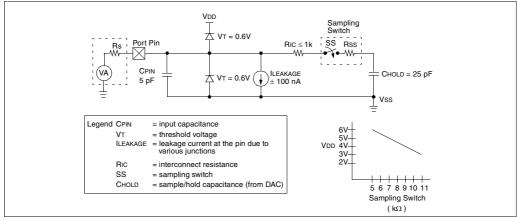

#### FIGURE 11-7: CALCULATING THE MINIMUM REQUIRED SAMPLE TIME

| TACQ =  | + Holding Capacitor Charging Time<br>+Temperature Coefficient † |

|---------|-----------------------------------------------------------------|

| TACQ =  | 1                                                               |

|         | + Tc                                                            |

|         | + [(Temp - 25°C)(0.05 μs/°C)] †                                 |

| Tc= +   | Holding Capacitor Charging Time                                 |

| Tc = (C | HOLD) (RIC + RSS + RS) In (1/16384)                             |

| Tc = -2 | 5 pF (1 kΩ +10 kΩ + 2.5 kΩ) ln (1/16384)                        |

| Tc = -2 | 5 pF (13.5 kΩ) In (1/16384)                                     |

| Tc = -0 | .338 (-9.704)μs                                                 |

| Tc = 3. | 3μs                                                             |

| TACQ =  | 5 μs                                                            |

|         | + 3.3 μs                                                        |

|         | + [(50°C - 25°C)(0.05 μs / °C)]                                 |

| TACQ =  | 8.3 μs + 1.25 μs                                                |

| TACQ =  | 9.55 μs                                                         |

† The temperature coefficient is only required for temperatures > 25°C.

#### FIGURE 11-8: ANALOG INPUT MODEL

#### FIGURE 12-1: CONFIGURATION WORD

| CP1     | CP0    | BORV1                | BORV0    | CP1    | CP0      | -                   | BODEN            | CP1              | CP0 | PWRTE | WDTE | FOSC1 | FOSC0       | Register:<br>Address | CONFIG<br>2007h |

|---------|--------|----------------------|----------|--------|----------|---------------------|------------------|------------------|-----|-------|------|-------|-------------|----------------------|-----------------|

| bit13   | 12     | 11                   | 10       | 9      | 8        | 7                   | 6                | 5                | 4   | 3     | 2    | 1     | bit0        | Address              | 2007h           |

| oit 13  | -12: ( | CP1:CP               | 0: Code  | Prote  | ction b  | oits <sup>(2)</sup> |                  |                  |     |       |      |       |             | 1                    |                 |

| bit 9-8 | 3: ·   | 11 = Pro             | gram m   | emory  | code p   | rotecti             | on off           |                  |     |       |      |       |             |                      |                 |

| oit 5-4 |        | 10 = 080             |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 01 = 040             |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 00 = 000             |          |        | •        |                     |                  | (3)              |     |       |      |       |             |                      |                 |

| bit 11  |        |                      |          |        | n-out F  | eset V              | oltage bit       | s <sup>(3)</sup> |     |       |      |       |             |                      |                 |

|         |        | 11 = Vвс<br>10 = Vвс |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 0 = VBC              |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         | (      | 00 = Vвс             | R set to | 4.5V   |          |                     |                  |                  |     |       |      |       |             |                      |                 |

| bit 7:  | I      | Unimple              | mented   | I, Rea | d as '1' |                     |                  |                  |     |       |      |       |             |                      |                 |

| bit 6:  |        | BODEN:               | Brown-   | out Re | eset En  | able bi             | <sub>†</sub> (1) |                  |     |       |      |       |             |                      |                 |

|         |        | 1 = Brow             |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         | (      | ) = Brow             | n-out R  | eset d | isabled  |                     |                  |                  |     |       |      |       |             |                      |                 |

| bit 3:  | ī      | WRTE:                | Power-   | up Tin | ner Ena  | ble bit             | (1)              |                  |     |       |      |       |             |                      |                 |

|         |        | 1 = PWF              |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         | (      | D = PWF              | RT enabl | ed     |          |                     |                  |                  |     |       |      |       |             |                      |                 |

| bit 2:  |        | WDTE: \              |          | 0      | er Enał  | ole bit             |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 1 = WDT              |          | -      |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | D = WDT              |          | -      |          |                     |                  |                  |     |       |      |       |             |                      |                 |

| bit 1-0 |        | FOSC1:               |          |        | ator Se  | lectior             | bits             |                  |     |       |      |       |             |                      |                 |

|         |        | 11 = RC<br>10 = HS   |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 0 = HS<br>01 = XT (  |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 00 = LP              |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        |                      |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

| Note    |        |                      |          |        |          |                     |                  |                  |     |       |      |       | dless of th | ne value of b        | it PWRTE.       |

|         |        |                      |          |        |          |                     | ed anytim        |                  |     |       |      |       | tion scher  | na listad            |                 |

|         |        |                      |          |        |          |                     |                  |                  |     |       |      |       |             | election of a        | n unused        |

|         |        |                      |          |        |          |                     | nterrupt.        | , 000            |     |       |      |       |             |                      |                 |

#### 12.2 Oscillator Configurations

#### 12.2.1 OSCILLATOR TYPES

The PIC16C77X can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

# 12.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 12-2). The PIC16C77X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications.

A difference from the other mid-range devices may be noted in that the device can be driven from an external clock only when configured in HS mode (Figure 12-3).

| TABLE 12-6 | INITIA | LIZA | TION CONDITIONS FO                 | OR ALL REGISTER          | 5                               |

|------------|--------|------|------------------------------------|--------------------------|---------------------------------|

| Register   | Dev    | ices | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

| W          | 773    | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| INDF       | 773    | 774  | N/A                                | N/A                      | N/A                             |

| TMR0       | 773    | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| PCL        | 773    | 774  | 0000h                              | 0000h                    | PC + 1 <b>(2)</b>               |

| STATUS     | 773    | 774  | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |

| FSR        | 773    | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| PORTA      | 773    | 774  | 0x 0000                            | 0u 0000                  | uu uuuu                         |

| PORTB      | 773    | 774  | xxxx 11xx                          | uuuu 11uu                | uuuu uuuu                       |

| PORTC      | 773    | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| PORTD      | 773    | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| PORTE      | 773    | 774  | 000                                | 000                      | uuu                             |

| PCLATH     | 773    | 774  | 0 0000                             | 0 0000                   | u uuuu                          |

| INTCON     | 773    | 774  | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |

| PIR1       | 773    | 774  | r000 0000                          | r000 0000                | ruuu uuuu <b>(1)</b>            |

|            | 773    | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu <b>(1)</b>            |

| PIR2       | 773    | 774  | 00                                 | 00                       | u uu <b>(1)</b>                 |

| TMR1L      | 773    | 774  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| TMR1H      | 773    | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| T1CON      | 773    | 774  | 00 0000                            | uu uuuu                  | uu uuuu                         |

| TMR2       | 773    | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| T2CON      | 773    | 774  | -000 0000                          | -000 0000                | -uuu uuuu                       |

| SSPBUF     | 773    | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| SSPCON     | 773    | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| CCPR1L     | 773    | 774  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR1H     | 773    | 774  | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |

| CCP1CON    | 773    | 774  | 00 0000                            | 00 0000                  | uu uuuu                         |

| RCSTA      | 773    | 774  | 0000 000x                          | 0000 000x                | uuuu uuuu                       |

| TXREG      | 773    | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| RCREG      | 773    | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| CCPR2L     | 773    | 774  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCPR2H     | 773    | 774  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| CCP2CON    | 773    | 774  | 00 0000                            | 00 0000                  | uu uuuu                         |

| ADRESH     | 773    | 774  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON0     | 773    | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| OPTION_REG | 773    | 774  | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TABLE 12-6 | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|------------|---------------------------------------------|

|            |                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-5 for reset value for specific condition.

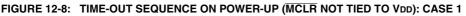

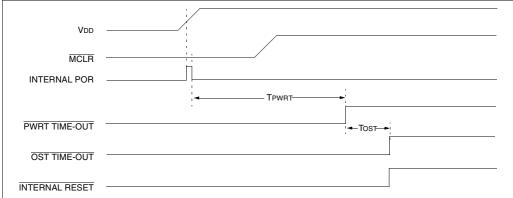

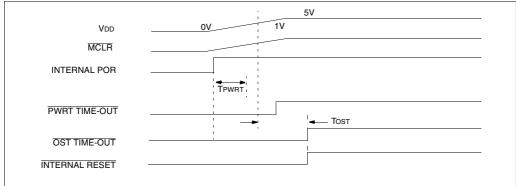

#### FIGURE 12-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

#### FIGURE 12-10: SLOW RISE TIME (MCLR TIED TO VDD)

# PIC16C77X

NOTES:

|        |                                          | Standa  | rd Opera     | ting Co             | onditions                 | (unles          | s otherwise stated)                                      |

|--------|------------------------------------------|---------|--------------|---------------------|---------------------------|-----------------|----------------------------------------------------------|

|        |                                          | Operati | ng tempe     | rature              | -40°C                     | ≤ TA            | $\leq$ +85°C for industrial and                          |

| DC CHA | RACTERISTICS                             |         |              |                     | 0°C                       | ≤ TA            | $\leq$ +70°C for commercial                              |

|        |                                          | Operati | ng voltage   | e VDD r             | ange as d                 | escribe         | ed in DC spec Section 15.1 and                           |

|        |                                          | Section | 15.2.        |                     |                           |                 | ~                                                        |

| Param  | Characteristic                           | Sym     | Min          | Typ†                | Max                       | Units           | Conditions                                               |

| No.    |                                          |         |              |                     |                           |                 |                                                          |

|        | Output High Voltage                      |         |              |                     |                           |                 |                                                          |

| D090   | I/O ports (Note 3)                       | Voн     | VDD - 0.7    | _                   | —                         | V               | $10_{H} = -3.0 \text{ mA}, \text{ VDD} = 4.5 \text{ V},$ |

|        |                                          |         |              |                     |                           | $\int$          | -40°C to +85°C                                           |

| D092   | OSC2/CLKOUT (RC osc config)              |         | VDD - 0.7    |                     | $\sim$                    | ( v             | IOH = -1.3  mA, VDP = 4.5V,                              |

|        |                                          |         |              |                     | $\langle \rangle \rangle$ | $\backslash$    | -40°C to +85°C                                           |

| D150*  | Open-Drain High Voltage                  | VOD     | —            | $\sim$              | 8.5                       | X               | RA4 pin                                                  |

|        | Capacitive Loading Specs on              |         | <            |                     | 1</td <td></td> <td></td> |                 |                                                          |

|        | Output Pins                              |         | ~            | 11                  |                           | $\setminus$ $-$ |                                                          |

| D100   | OSC2 pin                                 | Cos¢2   | $\sim$       | $  \neq $           | 15                        | ۶F              | In XT, HS and LP modes when                              |

|        |                                          |         | $\backslash$ |                     | $\left  \right\rangle$    | ſ               | external clock is used to drive                          |

|        |                                          | 1 /     | $ \rangle$   | $\nearrow$ '        | $\searrow$                |                 | OSC1.                                                    |

| D101   | All I/O pins and OSC2 (in RC \           | Cio     |              | $\land \rightarrow$ | <b>5</b> 0                | pF              |                                                          |

| D102   | mode) SCL, SDA in <del>/</del> 2Ĉ mode ∖ | ∖Св     |              | $\geq$              | 400                       | pF              |                                                          |

| *      | These parameters are characterized       | zed but | not tested   |                     | •                         |                 | ·                                                        |

I nese parameters are characterized but not tested.

Data in "Typ" column is at SV, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels

represent normal operating conditions. Higher leakage current may be measured at different input voltages. 3) Negative current is defined as current sourced by the pin.

The game current is defined as current sourced by the pin.

#### 15.4 DC Characteristics: VREF

#### TABLE 15-2 ELECTRICAL CHARACTERISTICS: VREF

| DC CHAR      | ACTERISTICS                  | Standard Op<br>Operating ter | mperature      | -40°C<br>0°C | C` ≤ TA :<br>≤ TA : | ≤ +85°C<br>≤ +70°C  | for industr<br>for comme | ial and                 |

|--------------|------------------------------|------------------------------|----------------|--------------|---------------------|---------------------|--------------------------|-------------------------|

| Param<br>No. | Characte                     |                              | Symbol         | Min          | Typ†                | Max                 | Units                    | Conditions              |

| D400         | Output Voltage               |                              | VRL            | 2.0          | 2.048               | 2.1                 | V                        | VDD ≥ 2.5V              |

|              |                              |                              | VRH            | 4.0          | 4.096               | 4.2                 | V                        | VDØ ≥ 4.5V              |

| D401A        | VRL Quiescent S              | upply Current                | $\Delta IVRL$  | —            | 70                  | TBD                 | μΑ                       | No load on VRL.         |

| D401B        | VRH Quiescent Supply Current |                              | $\Delta IVRH$  | _            | 70                  | TBD                 | µtA                      | No load on VRH.         |

| D402         | Ouput Voltage Drift          |                              | TCVOUT         | —            | 15*                 | 50*                 | ppm/°C/                  | Note 1                  |

| D404         | External Load So             | urce                         | IVREFSO        | —            | —                   | ,5*                 | (mA                      |                         |

| D405         | External Load Sir            | ık                           | IVREFSI        | —            | —                   | <- <del>5</del> * \ | ∖mA                      |                         |

| D406         | Load Regulation              |                              |                | _            | $\checkmark$        | †βD/₹ (             |                          | Isource = 0 mA to       |

|              |                              |                              | $\Delta VOUT/$ |              | $\langle \rangle$   |                     | mV/mA                    | 5 mA                    |

|              |                              |                              | ∆IOUT          | ~            | 71                  | TBD*                |                          | Isink = 0 mA to<br>5 mA |

| D407         | Line Regulation              |                              | AVOUT/<br>AVDD | A            | _/                  | 50*                 | μV/V                     |                         |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Production tested at TAMB  $= 25^{\circ}$ C. Specifications over temp limits guaranteed by characterization.

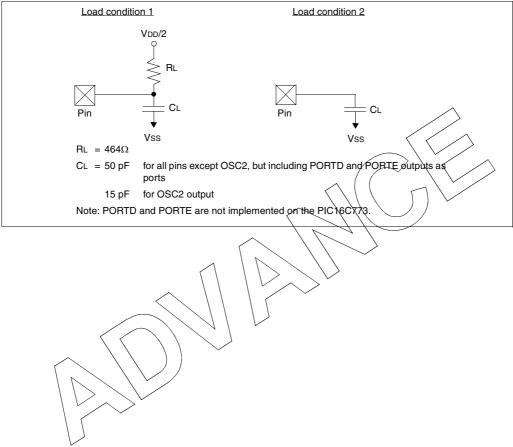

#### FIGURE 15-3: LOAD CONDITIONS

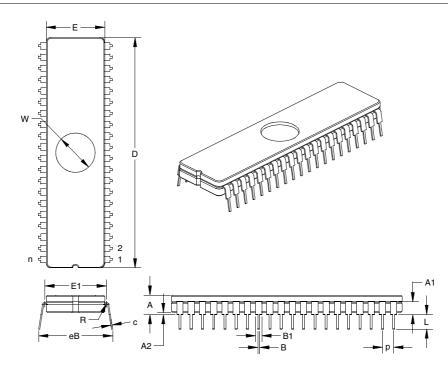

#### 17.7 K04-014 40-Lead Ceramic Dual In-line with Window (JW) – 600 mil

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                        |    |       | INCHES* |       | MILLIMETERS |       |       |

|------------------------------|----|-------|---------|-------|-------------|-------|-------|

| Dimension Limits             |    | MIN   | NOM     | MAX   | MIN         | NOM   | MAX   |

| PCB Row Spacing              |    |       | 0.600   |       |             | 15.24 |       |

| Number of Pins               | n  |       | 40      |       |             | 40    |       |

| Pitch                        | р  | 0.098 | 0.100   | 0.102 | 2.49        | 2.54  | 2.59  |

| Lower Lead Width             | В  | 0.016 | 0.020   | 0.023 | 0.41        | 0.50  | 0.58  |

| Upper Lead Width             | B1 | 0.050 | 0.053   | 0.055 | 1.27        | 1.33  | 1.40  |

| Shoulder Radius              | R  | 0.000 | 0.005   | 0.010 | 0.00        | 0.13  | 0.25  |

| Lead Thickness               | с  | 0.008 | 0.011   | 0.014 | 0.20        | 0.28  | 0.36  |

| Top to Seating Plane         | А  | 0.190 | 0.205   | 0.220 | 4.83        | 5.21  | 5.59  |

| Top of Lead to Seating Plane | A1 | 0.117 | 0.135   | 0.153 | 2.97        | 3.43  | 3.89  |

| Base to Seating Plane        | A2 | 0.030 | 0.045   | 0.060 | 0.00        | 1.14  | 1.52  |

| Tip to Seating Plane         | L  | 0.135 | 0.140   | 0.145 | 3.43        | 3.56  | 3.68  |

| Package Length               | D  | 2.040 | 2.050   | 2.060 | 51.82       | 52.07 | 52.32 |

| Package Width                | E  | 0.514 | 0.520   | 0.526 | 13.06       | 13.21 | 13.36 |

| Radius to Radius Width       | E1 | 0.560 | 0.580   | 0.600 | 14.22       | 14.73 | 15.24 |

| Overall Row Spacing          | eB | 0.610 | 0.660   | 0.710 | 15.49       | 16.76 | 18.03 |

| Window Diameter              | W  | 0.340 | 0.350   | 0.360 | 8.64        | 8.89  | 9.14  |

\* Controlling Parameter.

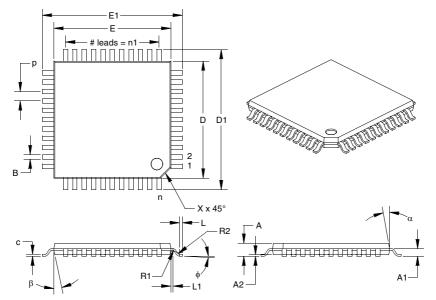

#### 17.8 K04-076 44-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 1.0/0.1 mm Lead Form

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                   |    |       | INCHES |       | MILLIMETERS* |       | *     |

|-------------------------|----|-------|--------|-------|--------------|-------|-------|

| Dimension Limits        |    | MIN   | NOM    | MAX   | MIN          | NOM   | MAX   |

| Pitch                   | р  |       | 0.031  |       |              | 0.80  |       |

| Number of Pins          | n  |       | 44     |       |              | 44    |       |

| Pins along Width        | n1 |       | 11     |       |              | 11    |       |

| Overall Pack. Height    | А  | 0.039 | 0.043  | 0.047 | 1.00         | 1.10  | 1.20  |

| Shoulder Height         | A1 | 0.015 | 0.025  | 0.035 | 0.38         | 0.64  | 0.89  |

| Standoff                | A2 | 0.002 | 0.004  | 0.006 | 0.05         | 0.10  | 0.15  |

| Shoulder Radius         | R1 | 0.003 | 0.003  | 0.010 | 0.08         | 0.08  | 0.25  |

| Gull Wing Radius        | R2 | 0.003 | 0.006  | 0.008 | 0.08         | 0.14  | 0.20  |

| Foot Length             | L  | 0.005 | 0.010  | 0.015 | 0.13         | 0.25  | 0.38  |

| Foot Angle              | φ  | 0     | 3.5    | 7     | 0            | 3.5   | 7     |

| Radius Centerline       | L1 | 0.003 | 0.008  | 0.013 | 0.08         | 0.20  | 0.33  |

| Lead Thickness          | с  | 0.004 | 0.006  | 0.008 | 0.09         | 0.15  | 0.20  |

| Lower Lead Width        | Вţ | 0.012 | 0.015  | 0.018 | 0.30         | 0.38  | 0.45  |

| Outside Tip Length      | D1 | 0.463 | 0.472  | 0.482 | 11.75        | 12.00 | 12.25 |

| Outside Tip Width       | E1 | 0.463 | 0.472  | 0.482 | 11.75        | 12.00 | 12.25 |

| Molded Pack. Length     | D‡ | 0.390 | 0.394  | 0.398 | 9.90         | 10.00 | 10.10 |

| Molded Pack. Width      | E‡ | 0.390 | 0.394  | 0.398 | 9.90         | 10.00 | 10.10 |

| Pin 1 Corner Chamfer    | х  | 0.025 | 0.035  | 0.045 | 0.64         | 0.89  | 1.14  |

| Mold Draft Angle Top    | α  | 5     | 10     | 15    | 5            | 10    | 15    |

| Mold Draft Angle Bottom | β  | 5     | 12     | 15    | 5            | 12    | 15    |

Controlling Parameter.

<sup>†</sup> Dimension "B" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B."

<sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E." JEDEC equivalent:MS-026 ACB

# PIC16C77X

### Е

| Errata                                  | 4          |

|-----------------------------------------|------------|

| External Power-on Reset Circuit         | 132        |

| F                                       |            |

| Firmware Instructions                   | 143        |

| Flowcharts                              |            |

| Acknowledge                             |            |

| Master Receiver                         |            |

| Master Transmit                         | 80         |

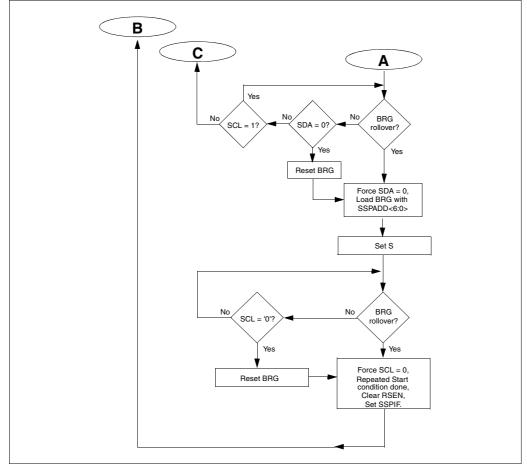

| Restart Condition                       | 77         |

| Start Condition                         | 75         |

| Stop Condition                          |            |

| FSR Register                            | 13, 14, 15 |

| Fuzzy Logic Dev. System (fuzzyTECH®-MP) | 147        |

## G

| GCE                           | . 56 |

|-------------------------------|------|

| General Call Address Sequence | . 69 |

| General Call Address Support  | . 69 |

| General Call Enable bit, GCE  | . 56 |

### I

| I/O Ports                                         |  |

|---------------------------------------------------|--|

| I <sup>2</sup> C63                                |  |

| I <sup>2</sup> C Master Mode Receiver Flowchart83 |  |

| I <sup>2</sup> C Master Mode Reception82          |  |

| I <sup>2</sup> C Master Mode Restart Condition76  |  |

| I <sup>2</sup> C Mode Selection63                 |  |

| I <sup>2</sup> C Module                           |  |

| Acknowledge Flowchart86                           |  |

| Acknowledge Sequence timing85                     |  |

| Addressing64                                      |  |

| Baud Rate Generator73                             |  |

| Block Diagram71                                   |  |

| BRG Block Diagram73                               |  |

| BRG Reset due to SDA Collision92                  |  |

| BRG Timing73                                      |  |

| Bus Arbitration90                                 |  |

| Bus Collision90                                   |  |

| Acknowledge90                                     |  |

| Restart Condition93                               |  |

| Restart Condition Timing (Case1)93                |  |

| Restart Condition Timing (Case2)                  |  |

| Start Condition91                                 |  |

| Start Condition Timing91, 92                      |  |

| Stop Condition94                                  |  |

| Stop Condition Timing (Case1)94                   |  |

| Stop Condition Timing (Case2)                     |  |

| Transmit Timing90                                 |  |

| Bus Collision timing                              |  |

| Clock Arbitration                                 |  |

| Clock Arbitration Timing (Master Transmit)89      |  |

| Conditions to not give ACK Pulse                  |  |

| General Call Address Support69                    |  |

| Master Mode71                                     |  |

| Master Mode 7-bit Reception timing84              |  |

| Master Mode Operation72                           |  |

| Master Mode Start Condition74                     |  |

| Master Mode Transmission79                        |  |

| Master Mode Transmit Sequence72                   |  |

| Master Transmit Flowchart                         |  |

| Multi-Master Communication90                      |  |

| Multi-master Mode72                               |  |

| Operation63                                       |  |

| Repeat Start Condition timing76                   |  |

| Restart Condition Flowchart                                           |             |

|-----------------------------------------------------------------------|-------------|

| Slave Mode                                                            |             |

| Slave Reception                                                       |             |

| Slave Transmission                                                    |             |

| SSPBUF                                                                |             |

| Start Condition Flowchart                                             |             |

| Stop Condition Flowchart<br>Stop Condition Receive or Transmit timing |             |

| Stop Condition timing                                                 | 0/<br>07    |

| Waveforms for 7-bit Reception                                         |             |

| Waveforms for 7-bit Transmission                                      |             |

| I <sup>2</sup> C Module Address Register, SSPADD                      |             |

| I <sup>2</sup> C Slave Mode                                           |             |

| ICEPIC Low-Cost PIC16CXXX In-Circuit Emulator                         |             |

| ID Locations                                                          |             |

| In-Circuit Serial Programming (ICSP)                                  |             |

| INDF                                                                  |             |

| INDF Register                                                         |             |

| Indirect Addressing                                                   |             |

| FSR Register                                                          |             |

| Instruction Format                                                    | 143         |

| Instruction Set                                                       | 143         |

| Summary Table                                                         |             |

| INTCON                                                                |             |

| INTCON Register                                                       |             |

| GIE Bit                                                               |             |

| INTE Bit                                                              |             |

| INTF Bit                                                              |             |

| PEIE Bit                                                              |             |

| RBIE Bit                                                              |             |

| RBIF Bit                                                              |             |

| TOIE Bit                                                              |             |

| T0IF Bit                                                              |             |

| Inter-Integrated Circuit (I <sup>2</sup> C)                           | 53          |

| internal sampling switch (Rss) impedence                              | 123         |

| Interrupt Sources                                                     | . 127, 137  |

| Block Diagram                                                         | 137         |

| Capture Complete (CCP)                                                | 48          |

| Compare Complete (CCP)                                                |             |

| Interrupt on Change (RB7:RB4)                                         |             |

| RB0/INT Pin, External                                                 | . 7, 8, 138 |

| TMR0 Overflow                                                         |             |

| TMR1 Overflow                                                         | 41, 43      |

| TMR2 to PR2 Match                                                     |             |

| TMR2 to PR2 Match (PWM)                                               | 45, 50      |

| USART Receive/Transmit Complete                                       |             |

| Interrupts, Context Saving During                                     | 138         |

| Interrupts, Enable Bits                                               |             |

| A/D Converter Enable (ADIE Bit)                                       |             |

| CCP1 Enable (CCP1IE Bit)                                              | 19, 48      |

| CCP2 Enable (CCP2IE Bit)                                              |             |

| Global Interrupt Enable (GIE Bit)                                     | 18, 137     |

| Interrupt on Change (RB7:RB4) Enable                                  |             |

| (RBIE Bit)                                                            |             |

| Peripheral Interrupt Enable (PEIE Bit)                                |             |

| PSP Read/Write Enable (PSPIE Bit)                                     | 19          |

| RB0/INT Enable (INTE Bit)                                             |             |

| SSP Enable (SSPIE Bit)                                                |             |

| TMR0 Overflow Enable (T0IE Bit)                                       |             |

| TMR1 Overflow Enable (TMR1IE Bit)                                     | 19          |

| TMR2 to PR2 Match Enable (TMR2IE Bit)                                 |             |

| UNADT Dessive Enchle (DOIE Bit)                                       |             |

| USART Receive Enable (RCIE Bit)<br>USART Transmit Enable (TXIE Bit)   |             |