#### Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 6x12b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                          |

| Supplier Device Package    | 28-SSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c773t-ss |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## FIGURE 2-5: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0  | R/W-0                                          | R/W-0       | R/W-0       | R/W-0        | R/W-0                           | R/W-0       | R/W-x        |                                                                                                                        |

|--------|------------------------------------------------|-------------|-------------|--------------|---------------------------------|-------------|--------------|------------------------------------------------------------------------------------------------------------------------|

| GIE    | PEIE                                           | TOIE        | INTE        | RBIE         | T0IF                            | INTF        | RBIF         | R = Readable bit                                                                                                       |

| bit7   |                                                |             |             |              |                                 |             | bitO         | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>- n = Value at POR reset</li> </ul> |

| bit 7: | <b>GIE:</b> Glob<br>1 = Enable<br>0 = Disable  | es all un-r | nasked in   |              |                                 |             |              |                                                                                                                        |

| bit 6: | <b>PEIE</b> : Per<br>1 = Enable<br>0 = Disable | es all un-r | nasked pe   | eripheral in | iterrupts                       |             |              |                                                                                                                        |

| bit 5: | <b>TOIE</b> : TMF<br>1 = Enable<br>0 = Disable | es the TM   | R0 interru  | ıpt          | oit                             |             |              |                                                                                                                        |

| bit 4: | IINTE: RE<br>1 = Enable<br>0 = Disable         | es the RB   | 0/INT exte  | ernal interr | upt                             |             |              |                                                                                                                        |

| bit 3: | <b>RBIE</b> : RB<br>1 = Enable<br>0 = Disable  | es the RB   | port char   | ige interru  | pt                              |             |              |                                                                                                                        |

| bit 2: | <b>TOIF</b> : TMF<br>1 = TMR0<br>0 = TMR0      | register h  | nas overflo | wed (mus     | t be cleare                     | d in softwa | re)          |                                                                                                                        |

| bit 1: | INTF: RB(<br>1 = The R<br>0 = The R            | B0/INT ex   | ternal inte | errupt occi  | urred (must                     | be cleared  | d in softwa  | re)                                                                                                                    |

| bit 0: |                                                | st one of t | he RB7:R    | B4 pins ch   | t<br>nanged stat<br>anged state |             | e cleared in | software)                                                                                                              |

## 2.2.2.7 PIR2 REGISTER

Γ

This register contains the CCP2, SSP Bus Collision, and Low-voltage detect interrupt flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## FIGURE 2-9: PIR2 REGISTER (ADDRESS 0Dh)

| R/W-0         | U-0                                                                                                                                                                                                                       | U-0         | U-0        | R/W-0                    | U-0         | U-0        | R/W-0          |                                                                                                                |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|--------------------------|-------------|------------|----------------|----------------------------------------------------------------------------------------------------------------|

| LVDIF<br>bit7 | _                                                                                                                                                                                                                         | _           | _          | BCLIF                    |             | _          | CCP2IF<br>bit0 | <ul> <li>R = Readable bit</li> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> </ul> |

| bit 7:        | 1 = The si                                                                                                                                                                                                                | upply volta | age has fa |                          |             |            |                | - n = Value at POR reset                                                                                       |

| bit 6-4:      | Unimplen                                                                                                                                                                                                                  | nented: R   | ead as '0  | 1                        |             |            |                |                                                                                                                |

| bit 3:        | BCLIF: Bus Collision Interrupt Flag bit<br>1 = A bus collision has occurred while the SSP module configured in I <sup>2</sup> C Master was transmitting<br>(must be cleared in software)<br>0 = No bus collision occurred |             |            |                          |             |            |                |                                                                                                                |

| bit 2-1:      | Unimplen                                                                                                                                                                                                                  | nented: R   | ead as '0  | i                        |             |            |                |                                                                                                                |

| bit 0:        | CCP2IF: (                                                                                                                                                                                                                 | CCP2 Inte   | rrupt Flag | bit                      |             |            |                |                                                                                                                |

|               | <u>Capture M</u><br>1 = A TMF<br>0 = No TM                                                                                                                                                                                | R1 registe  |            |                          | nust be cle | ared in sc | ftware)        |                                                                                                                |

|               |                                                                                                                                                                                                                           | R1 registe  | •          | e match oc<br>re match o | •           | st be clea | red in softw   | are)                                                                                                           |

|               | <u>PWM Moo</u><br>Unused                                                                                                                                                                                                  | <u>de</u>   |            |                          |             |            |                |                                                                                                                |

## 2.3 PCL and PCLATH

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly readable or writable. All updates to the PCH register go through the PCLATH register.

## 2.3.1 STACK

The stack allows a combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Midrange devices have an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

## 2.4 Program Memory Paging

PIC16C77X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

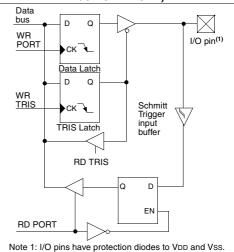

## 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output, i.e., put the contents of the output latch on the selected pin.

## EXAMPLE 3-1: INITIALIZING PORTB

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| CLRF  | PORTB   |     | ; | Initialize PORTB by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISB   |     | ; | Set RB<3:0> as inputs |

|       |         |     | ; | RB<5:4> as outputs    |

|       |         |     | ; | RB<7:6> as inputs     |

|       |         |     |   |                       |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overrightarrow{\text{RBPU}}$  (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

The RB0 pin is multiplexed with the external interrupt (RB0/INT).

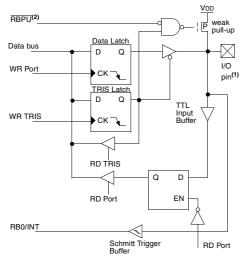

## FIGURE 3-4: BLOCK DIAGRAM OF RB0 PIN

Note 1: I/O pins have diode protection to VDD and VSS. 2: To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (OPTION\_REG<7>).

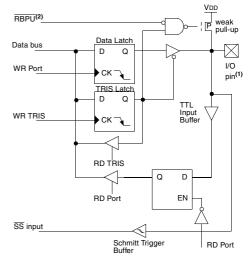

The RB1 pin is multiplexed with the SSP module slave select (RB1/SS).

## FIGURE 3-5: BLOCK DIAGRAM OF RB1/SS PIN

Note 1: I/O pins have diode protection to VDD and Vss. 2: To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (OPTION\_REG<7>).

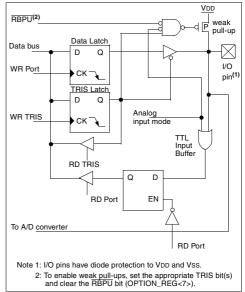

The RB2 pin is multiplexed with analog channel 8 (RB2/AN8).

## FIGURE 3-6: BLOCK DIAGRAM OF RB2/AN8 PIN

## 3.5 PORTE and TRISE Register

This section is applicable to the 40/44-pin devices only.

PORTE has three pins RE0/RD/AN5, RE1/ $\overline{WR}$ /AN6 and RE2/ $\overline{CS}$ /AN7, which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

I/O PORTE becomes control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs). Ensure ADCON1 is configured for digital I/O. In this mode the input buffers are TTL.

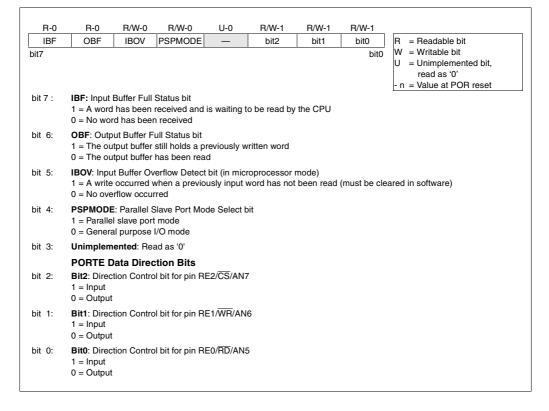

Figure 3-12 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected as an analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

Note: On a Power-on Reset these pins are configured as analog inputs.

## FIGURE 3-12: TRISE REGISTER (ADDRESS 89h)

#### 5.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers; TMR1H and TMR1L)

- Readable and writable (Both registers)

- · Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- · Reset from CCP module trigger

Timer1 has a control register, shown in Figure 5-1. Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Figure 5-3 is a simplified block diagram of the Timer1 module.

Additional information on timer modules is available in the PICmicro™ Mid-Range Reference Manual, (DS33023).

#### 5.1 **Timer1 Operation**

Timer1 can operate in one of these modes:

- · As a timer

- · As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the clock select bit. TMR1CS (T1CON<1>).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored.

Timer1 also has an internal "reset input". This reset can be generated by the CCP module (Section 7.0).

#### T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h) U-0 U-0 R/W-0 R/W-0 B/W-0 R/W-0 **B/W-0** R/W-0 T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON R = Readable bit W = Writable bit bit7 bit0 = Unimplemented bit, U read as '0' n = Value at POR reset bit 7-6: Unimplemented: Read as '0' bit 5-4: T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits 11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value 00 = 1:1 Prescale value T1OSCEN: Timer1 Oscillator Enable Control bit hit 3 1 = Oscillator is enabled 0 = Oscillator is shut off Note: The oscillator inverter and feedback resistor are turned off to eliminate power drain T1SYNC: Timer1 External Clock Input Synchronization Control bit bit 2: TMR1CS = 11 = Do not synchronize external clock input 0 = Synchronize external clock input TMR1CS = 0This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0. TMR1CS: Timer1 Clock Source Select bit bit 1: 1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge) 0 = Internal clock (Fosc/4)

## FIGURE 5-1:

- 1 = Enables Timer1

- 0 = Stops Timer1

### 7.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

## TABLE 7-4 EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

## TABLE 7-5 REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address               | Name    | Bit 7                | Bit 6          | Bit 5          | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>PC<br>BC | ,    | all o | e on<br>other<br>sets |

|-----------------------|---------|----------------------|----------------|----------------|---------|---------|--------|---------|---------|-------------------|------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE           | TOIE           | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000              | 000x | 0000  | 000u                  |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup> | ADIF           | RCIF           | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000              | 0000 | 0000  | 0000                  |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup> | ADIE           | RCIE           | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000              | 0000 | 0000  | 0000                  |

| 87h                   | TRISC   | PORTC Da             | ata Directio   | n Register     |         |         |        |         |         | 1111              | 1111 | 1111  | 1111                  |

| 11h                   | TMR2    | Timer2 mo            | dule's registe | er             |         |         |        |         |         | 0000              | 0000 | 0000  | 0000                  |

| 92h                   | PR2     | Timer2 mo            | dule's period  | l register     |         |         |        |         |         | 1111              | 1111 | 1111  | 1111                  |

| 12h                   | T2CON   | —                    | TOUTPS3        | TOUTPS2        | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000              | 0000 | -000  | 0000                  |

| 15h                   | CCPR1L  | Capture/Co           | mpare/PWN      | /I register1 ( | (LSB)   |         |        |         |         | xxxx              | xxxx | uuuu  | uuuu                  |

| 16h                   | CCPR1H  | Capture/Co           | mpare/PWN      | /I register1 ( | (MSB)   |         |        |         |         | xxxx              | xxxx | uuuu  | uuuu                  |

| 17h                   | CCP1CON | —                    | _              | CCP1X          | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00                | 0000 | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin, always maintain these bits clear.

determine when the transmission/reception has completed. The SSPBUF must be read and/or written. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur. Example 8-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

## EXAMPLE 8-1: LOADING THE SSPBUF (SSPSR) REGISTER

|      | BSF   | STATUS, | RP0  | ;Specify Bank 1   |

|------|-------|---------|------|-------------------|

| LOOP | BTFSS | SSPSTAT | , BF | ;Has data been    |

|      |       |         |      | ;received         |

|      |       |         |      | ;(transmit        |

|      |       |         |      | ;complete)?       |

|      | GOTO  | LOOP    |      | ;No               |

|      | BCF   | STATUS, | RP0  | ;Specify Bank 0   |

|      | MOVF  | SSPBUF, | W    | ;W reg = contents |

|      |       |         |      | ;of SSPBUF        |

|      | MOVWF | RXDATA  |      | ;Save in user RAM |

|      | MOVF  | TXDATA, | W    | ;W reg = contents |

|      |       |         |      | ; of TXDATA       |

|      | MOVWF | SSPBUF  |      | ;New data to xmit |

The SSPSR is not directly readable or writable, and can only be accessed by addressing the SSPBUF register. Additionally, the MSSP status register (SSPSTAT) indicates the various status conditions.

#### 8.1.2 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON<5>) must be set. To reset or reconfigure SPI mode, clear bit SSPEN, re-initialize the SSPCON registers, and then set bit SSPEN. This configures the

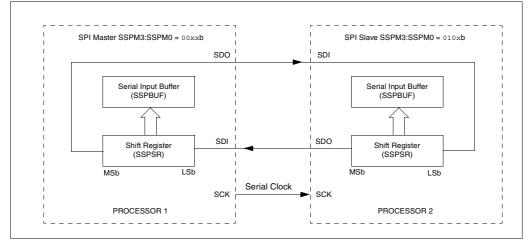

FIGURE 8-5: SPI MASTER/SLAVE CONNECTION

SDI, SDO, SCK, and  $\overline{SS}$  pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- · SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> cleared

- SCK (Master mode) must have TRISC<3> cleared

- SCK (Slave mode) must have TRISC<3> set

- SS must have TRISA<5> set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

## 8.1.3 TYPICAL CONNECTION

Figure 8-5 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

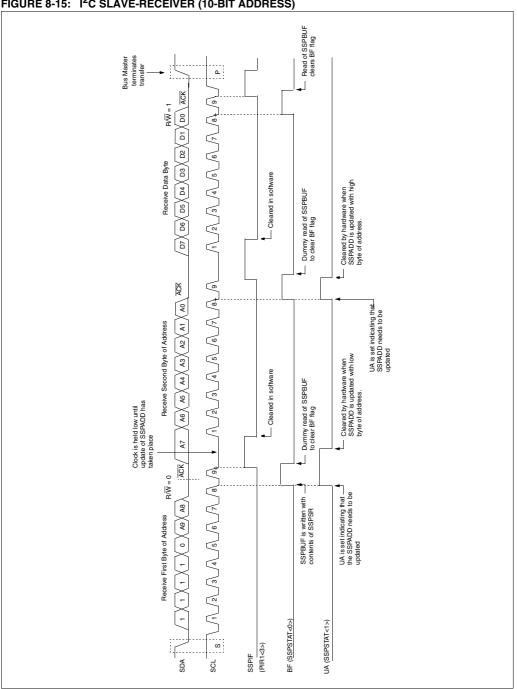

## FIGURE 8-15: I<sup>2</sup>C SLAVE-RECEIVER (10-BIT ADDRESS)

## 8.2.12 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the receive enable bit, RCEN (SSPCON2<3>).

| Note: | The SSP Module must be in an IDLE        |

|-------|------------------------------------------|

|       | STATE before the RCEN bit is set, or the |

|       | RCEN bit will be disregarded.            |

The baud rate generator begins counting, and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag is set, the SSPIF is set, and the baud rate generator is suspended from counting, holding SCL low. The SSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag is automatically cleared. The user can then send an acknowledge bit at the end of reception, by setting the acknowledge sequence enable bit, AKEN (SSPCON2<4>).

### 8.2.12.10 BF STATUS FLAG

In receive operation, BF is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when SSPBUF is read.

### 8.2.12.11 SSPOV STATUS FLAG

In receive operation, SSPOV is set when 8 bits are received into the SSPSR, and the BF flag is already set from a previous reception.

## 8.2.12.12 WCOL STATUS FLAG

If the user writes the SSPBUF when a receive is already in progress (i.e. SSPSR is still shifting in a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

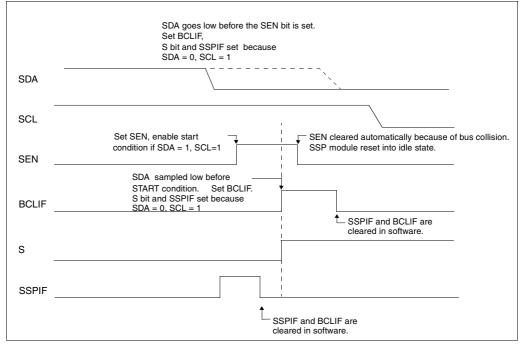

## 8.2.18.15 BUS COLLISION DURING A START CONDITION

During a START condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the START condition (Figure 8-35).

- b) SCL is sampled low before SDA is asserted low. (Figure 8-36).

During a START condition both the SDA and the SCL pins are monitored.

lf:

the SDA pin is already low or the SCL pin is already low,

then:

the START condition is aborted, and the BCLIF flag is set, and the SSP module is reset to its IDLE state (Figure 8-35).

The START condition begins with the SDA and SCL pins de-asserted. When the SDA pin is sampled high, the baud rate generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low

while SDA is high, a bus collision occurs, because it is assumed that another master is attempting to drive a data '1' during the START condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 8-37). If however a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The baud rate generator is then reloaded and counts down to 0, and during this time, if the SCL pins is sampled as '0', a bus collision does not occur. At the end of the BRG count the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a START condition is that no two bus masters can assert a START condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the START condition, and if the address is the same, arbitration must be allowed to continue into the data portion, REPEATED START, or STOP conditions.

## FIGURE 8-35: BUS COLLISION DURING START CONDITION (SDA ONLY)

NOTES:

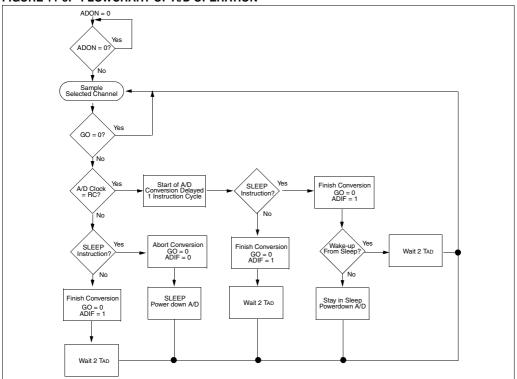

## 11.6 A/D Sample Requirements

## 11.6.1 RECOMMENDED SOURCE IMPEDANCE

The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . This value is calculated based on the maximum leakage current of the input pin. The leakage current is 100 nA max., and the analog input voltage cannot be vary by more than 1/4 LSb or 250 mV due to leakage. This places a requirement on the input impedance of 250  $\mu$ V/100 nA = 2.5 k $\Omega$ .

### 11.6.2 SAMPLING TIME CALCULATION

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 11-8. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 11-8. The maximum recommended impedance for analog sources is 2.5 k $\Omega$ . After the analog input channel is selected (changed) this sampling must be done before the conversion can be started.

To calculate the minimum sampling time, Equation 11-6 may be used. This equation assumes that 1/4 LSb error is used (16384 steps for the A/D). The 1/4 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

The CHOLD is assumed to be 25 pF for the 12-bit A/D.

## FIGURE 11-6: A/D SAMPLING TIME EQUATION

VHOLD =(VREF - VREF/16384) = (VREF) • (1 -e (-Tc/C (Ric +Rss + Rs)) VREF(1 - 1/16384) = VREF • (1 -e (-Tc/C (Ric +Rss + Rs)))

$T_c = -CHOLD (1k\Omega + RSS + RS) ln (1/16384)$

Figure 11-7 shows the calculation of the minimum time required to charge CHOLD. This calculation is based on the following system assumptions:

## CHOLD = 25 pF

$Rs = 2.5 \text{ k}\Omega$

1/4 LSb error

$VDD = 5V \rightarrow RSS = 10 \text{ k}\Omega \text{ (worst case)}$

Temp (system Max.) = 50°C

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:**The maximum recommended impedance for analog sources is 2.5 kΩ. This is required to meet the pin leakage specification.

- 4: After a conversion has completed, 2 TAD time must be waited before sampling can begin again. During this time the holding capacitor is not connected to the selected A/D input channel.

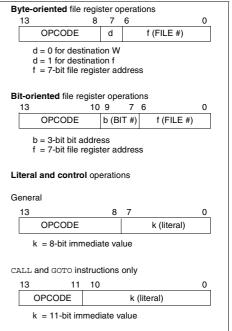

## 13.0 INSTRUCTION SET SUMMARY

Each PIC16CXXX instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CXX instruction set summary in Table 13-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 13-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

## TABLE 13-1 OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                        |

| W     | Working register (accumulator)                                                                                                                                              |

| b     | Bit address within an 8-bit file register                                                                                                                                   |

| k     | Literal field, constant data or label                                                                                                                                       |

| x     | Don't care location (= 0 or 1)<br>The assembler will generate code with x = 0. It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                |

| PC    | Program Counter                                                                                                                                                             |

| TO    | Time-out bit                                                                                                                                                                |

| PD    | Power-down bit                                                                                                                                                              |

The instruction set is highly orthogonal and is grouped into three basic categories:

- · Byte-oriented operations

- Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Table 13-2 lists the instructions recognized by the MPASM assembler.

Figure 13-1 shows the general formats that the instructions can have.

| Note: | To maintain upward compatibility with |

|-------|---------------------------------------|

|       | future PIC16CXXX products, do not use |

|       | the OPTION and TRIS instructions.     |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

## FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

A description of each instruction is available in the PICmicro™ Mid-Range Reference Manual, (DS33023).

## 15.1 DC Characteristics: PIC16C77X (Commercial, Industrial)

| DC CHA        | RACTERISTICS                                                     |                   | <b>Standa</b><br>Operati |            |            |                  | tions (unless otherwise stated) $0^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and $C \leq TA \leq +70^{\circ}C$ for commercial |

|---------------|------------------------------------------------------------------|-------------------|--------------------------|------------|------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.  | Characteristic                                                   | Sym               | Min                      | Тур†       | Max        | Units            | Conditions                                                                                                                             |

| D001<br>D001A | Supply Voltage                                                   | VDD               | 4.0<br>4.5               | _          | 5.5<br>5.5 | V<br>V           | XT, RC and LP osc configuration<br>HS osc configuration                                                                                |

| D002*         | RAM Data Retention<br>Voltage (Note 1)                           | VDR               | —                        | 1.5        | —          | V                |                                                                                                                                        |

| D003          | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR              | _                        | Vss        | _          | V                | See section on Power on Reset for details                                                                                              |

| D004*         | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD              | 0.05                     | _          | -          | V/ms             | See section on Power-on Reset for details.<br>PWRT enabled                                                                             |

| D010          | Supply Current (Note 2)                                          | IDD               | —                        | 2.7        | 5          | mA               | XT RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                           |

| D013          |                                                                  | ٢                 | $\sqrt{-}$               | 1315       | 30         | mA               | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                      |

| D020<br>D020A | Power-down Current<br>(Note 3) <                                 | IPD               | (                        | 1.5<br>1.5 | 16<br>19   | μ <b>A</b><br>μA | VDD = 4.0V, -0°C to +70°C<br>VDD = 4.0V, -40°C to +85°C                                                                                |

|               | Module Differential Cur-<br>rent (Note 5)                        |                   | 7/                       |            |            |                  |                                                                                                                                        |

| D021          | Watchdog Timer                                                   |                   | $\checkmark$             | 6.0        | 20         | μA               | VDD = 4.0V                                                                                                                             |

| D023*         | Brown-out Reset Current<br>(Note 5)                              |                   | TBD                      | 200        | —          | μA               | BOR enabled, VDD = 5.0V                                                                                                                |

| D023B*        | Bahdgap voltage<br>generator                                     | ∆lbG <sup>6</sup> | —                        | 40μΑ       | TBD        | μA               |                                                                                                                                        |

| D025*         | Timer1 oscillator                                                | ∆IT1osc           | _                        | 5          | 9          | μA               | VDD = 4.0V                                                                                                                             |

| D026*         | A/D Converter                                                    | $\Delta$ IAD      | —                        | 300        | —          | μA               | VDD = 5.5V, A/D on, not converting                                                                                                     |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD MCLR = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: The ∆ current is the additional current consumed when the peripheral is enabled. This current should be added to the base (IPD or IDD) current.

- 6: The bandgap voltate reference provides 1.22V to the VRL, VRH, LVD and BOR circuits. When calculating current consumption use the following formula:  $\Delta$ IVRL +  $\Delta$ IVRH +  $\Delta$ ILVD +  $\Delta$ IBOR +  $\Delta$ IBG. Any of the  $\Delta$ IVRL,  $\Delta$ IVRH,  $\Delta$ ILVD or  $\Delta$ IBOR can be 0.

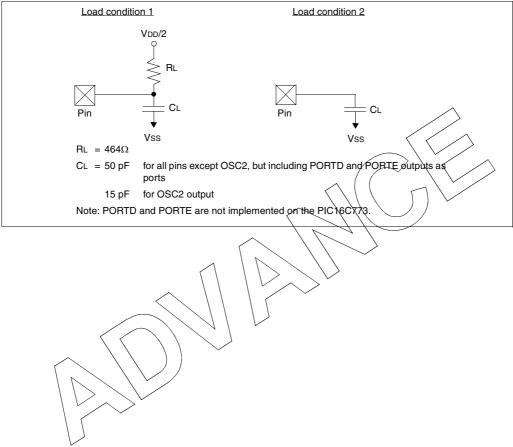

## FIGURE 15-3: LOAD CONDITIONS

| S                                         |       |

|-------------------------------------------|-------|

| SAE                                       |       |

| SCK                                       |       |

| SCL                                       |       |

| SDA                                       |       |

| SDA                                       |       |

| SDO                                       |       |

| SEEVAL® Evaluation and Programming System |       |

| Serial Clock, SCK                         |       |

| Serial Clock, SCK                         |       |

|                                           |       |

| Serial Data Address, SDA                  |       |

| Serial Data In, SDI                       |       |

| Serial Data Out, SDO                      |       |

| Slave Select Synchronization              |       |

| Slave Select, SS                          |       |

| SLEEP                                     |       |

| SMP                                       |       |

| Software Simulator (MPLAB-SIM)            |       |

| SPBRG Register                            |       |

| SPE                                       |       |

| Special Features of the CPU               | 1     |

| Special Function Registers                |       |

| PIC16C73                                  |       |

| PIC16C73A                                 |       |

| PIC16C74                                  |       |

| PIC16C74A                                 |       |

| PIC16C76                                  |       |

| PIC16C77                                  |       |

| Speed, Operating                          |       |

| SPI                                       |       |

| Master Mode                               |       |

| Serial Clock                              |       |

| Serial Data In                            |       |

| Serial Data Out                           |       |

| Serial Peripheral Interface (SPI)         |       |

| Slave Select                              |       |

| SPI clock                                 |       |

| SPI Mode                                  |       |

| SPI Clock Edge Select, CKE                |       |

| SPI Data Input Sample Phase Select, SMP   |       |

|                                           |       |

| SPI Master/Slave Connection               | ••••• |

| SPI Module                                |       |

| Master/Slave Connection                   |       |

| Slave Mode                                |       |

| Slave Select Synchronization              |       |

| Slave Synch Timnig                        |       |

| <u>SS</u>                                 |       |

| SSP                                       |       |

| Block Diagram (SPI Mode)                  |       |

| Enable (SSPIE Bit)                        |       |

| Flag (SSPIF Bit)                          |       |

| RA5/SS/AN4 Pin                            |       |

| RC3/SCK/SCL Pin                           |       |

| RC4/SDI/SDA Pin                           |       |

| RC5/SDO Pin                               |       |

| SPI Mode                                  |       |

| SPI Mode                                  |       |

|                                           |       |

| SSPBUF                                    |       |

| SSPCON1                                   |       |

| SSPCON2                                   |       |

| SSPSR                                     |       |

|                                           |       |

| SSPSTAT                                   |       |

| SSPSTAT<br>TMR2 Output for Clock Shift    |       |

| SSPSTAT                                   | 45,   |

| SSP Module                                   |

|----------------------------------------------|

| SPI Master Mode 59                           |

| SPI Master./Slave Connection 58              |

| SPI Slave Mode 60                            |

| SSPCON1 Register 63                          |

| SSP Overflow Detect bit, SSPOV 64            |

| SSPADD Register 14                           |

| SSPBUF 15, 64                                |

| SSPBUF Register 13                           |

| SSPCON Register 13                           |

| SSPCON1                                      |

| SSPCON2                                      |

| SSPEN                                        |

| SSPIF                                        |

| SSPM3:SSPM0                                  |

| SSPOV 55, 64, 82                             |

| SSPSTAT                                      |

| SSPSTAT Register 14                          |

| Stack                                        |

| Start bit (S)                                |

| Start Condition Enabled bit, SAE 56          |

| STATUS Register 16, 138                      |

| C Bit                                        |

| DC Bit 16                                    |

| IRP Bit                                      |

| PD Bit                                       |

| <u>RP</u> 1:RP0 Bits 16                      |

| TO Bit                                       |

| Z Bit                                        |

| Stop bit (P)                                 |

| Stop Condition Enable bit                    |

| Synchronous Serial Port 53                   |

| Synchronous Serial Port Enable bit, SSPEN 55 |

| Synchronous Serial Port Mode Select bits,    |

| SSPM3:SSPM0                                  |

|                                              |

## т

| T1CON                                  | 15      |

|----------------------------------------|---------|

| T1CON Register                         | 15, 41  |

| T1CKPS1:T1CKPS0 Bits                   | 41      |

| T1OSCEN Bit                            | 41      |

| T1SYNC Bit                             | 41      |

| TMR1CS Bit                             | 41      |

| TMR1ON Bit                             | 41      |

| T2CON Register                         | 15, 45  |

| T2CKPS1:T2CKPS0 Bits                   | 45      |

| TMR2ON Bit                             | 45      |

| TOUTPS3:TOUTPS0 Bits                   | 45      |

| Timer0                                 | 39      |

| Block Diagram                          | 39      |

| Clock Source Edge Select (T0SE Bit)    | 17, 39  |

| Clock Source Select (T0CS Bit)         | 17, 39  |

| Overflow Enable (T0IE Bit)             | 18      |

| Overflow Flag (T0IF Bit)               | 18, 138 |

| Overflow Interrupt                     | 40, 138 |

| RA4/T0CKI Pin, External Clock          |         |

| Timer1                                 | 41      |

| Block Diagram                          | 42      |

| Capacitor Selection                    | 43      |

| Clock Source Select (TMR1CS Bit)       | 41      |

| External Clock Input Sync (T1SYNC Bit) | 41      |

| Module On/Off (TMR1ON Bit)             |         |

| Oscillator                             | 41, 43  |

| Oscillator Enable (T1OSCEN Bit)        | 41      |

| Overflow Enable (TMR1IE Bit)           | 19      |

| Overflow Flag (TMR1IF Bit)             |         |

| ,                                      |         |

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (602) 786-7578.

Please list the following information, and use this outline to provide us with your comments about this Data Sheet.

| To:                                           | 2: Technical Publications Manager                                                         | Total Pages Sent                  |  |  |  |  |

|-----------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|

| RE:                                           | E: Reader Response                                                                        |                                   |  |  |  |  |

| From                                          | om: Name                                                                                  |                                   |  |  |  |  |

|                                               | Company                                                                                   |                                   |  |  |  |  |

|                                               | Address                                                                                   |                                   |  |  |  |  |

|                                               | City / State / ZIP / Country                                                              |                                   |  |  |  |  |

|                                               | Telephone: ()                                                                             | FAX: ()                           |  |  |  |  |

| Application (optional):                       |                                                                                           |                                   |  |  |  |  |

| Would you like a reply? Y N                   |                                                                                           |                                   |  |  |  |  |

| Device: PIC16C77X Literature Number: DS30275B |                                                                                           |                                   |  |  |  |  |

| Questions:                                    |                                                                                           |                                   |  |  |  |  |

| 4                                             |                                                                                           |                                   |  |  |  |  |

| 1.                                            | What are the best features of this document?                                              |                                   |  |  |  |  |

|                                               |                                                                                           |                                   |  |  |  |  |

| 2.                                            | 2. How does this document meet your hardware and software development needs?              |                                   |  |  |  |  |

|                                               |                                                                                           |                                   |  |  |  |  |

|                                               |                                                                                           |                                   |  |  |  |  |

| 3.                                            | 3. Do you find the organization of this data sheet easy to follow? If not, why?           |                                   |  |  |  |  |

|                                               |                                                                                           |                                   |  |  |  |  |

|                                               |                                                                                           |                                   |  |  |  |  |

| 4.                                            | 4. What additions to the data sheet do you think would enhance the structure and subject? |                                   |  |  |  |  |

|                                               |                                                                                           |                                   |  |  |  |  |

|                                               |                                                                                           | <i></i>                           |  |  |  |  |

| 5.                                            | What deletions from the data sheet could be made without a                                | affecting the overall usefulness? |  |  |  |  |

|                                               |                                                                                           |                                   |  |  |  |  |

| 6                                             | Is there any incorrect or misleading information (what and w                              | where)?                           |  |  |  |  |

| 0.                                            |                                                                                           |                                   |  |  |  |  |

|                                               |                                                                                           |                                   |  |  |  |  |

| 7.                                            | How would you improve this document?                                                      |                                   |  |  |  |  |

|                                               |                                                                                           |                                   |  |  |  |  |

|                                               |                                                                                           |                                   |  |  |  |  |

| 8.                                            | How would you improve our software, systems, and silicon p                                | products?                         |  |  |  |  |

|                                               |                                                                                           |                                   |  |  |  |  |

## PIC16C77X PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br>Device F | -XX X /XX XXX<br>requency Temperature Package Pattern<br>Range Range                                                                                                                                                                    | Examples:<br>g) PIC16C774 -04/P 301 = Commercial temp.,<br>PDIP package, 4 MHz, normal VDD limits, QTP<br>pattern #301.                                                                              |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device               | PIC16C77X <sup>(1)</sup> , PIC16C77XT <sup>(2)</sup> ;VDD range 4.0V to 5.5V<br>PIC16LC77X <sup>(1)</sup> , PIC16LC77XT <sup>(2)</sup> ;VDD range 2.5V to 5.5V                                                                          | <ul> <li>h) PIC16LC773 - 04I/SO = Industrial temp., SOIC package, 200 kHz, Extended VDD limits.</li> <li>i) PIC16C774 - 20I/P = Industrial temp., PDIP package, 20MHz, normal VDD limits.</li> </ul> |

| Frequency Range      | 04 = 4 MHz<br>20 = 20 MHz                                                                                                                                                                                                               | Note 1: C = CMOS                                                                                                                                                                                     |

| Temperature Range    | $b^{(3)} = 0^{\circ}C$ to 70°C (Commercial)<br>I = -40°C to +85°C (Industrial)                                                                                                                                                          | LC = Low Power CMOS<br>T = in tape and reel - SOIC, SSOP,<br>PLCC,<br>MQFP, TQFP packages only.<br>2: b = blank                                                                                      |

| Package              | $\begin{array}{rcl} JW & = & Windowed CERDIP/Ceramic \\ PQ & = & MQFP (Metric PQFP) \\ PT & = & TQFP (Thin Quad Flatpack) \\ SO & = & SOIC \\ SP & = & Skinny plastic dip \\ P & = & PDIP \\ L & = & PLCC \\ SS & = & SSOP \end{array}$ |                                                                                                                                                                                                      |

| Pattern              | QTP, SQTP, Code or Special Requirements<br>(blank otherwise)                                                                                                                                                                            |                                                                                                                                                                                                      |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type (including LC devices).

## Sales and Support

#### **Data Sheets**

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- 1. Your local Microchip sales office

- 2. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.