Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                               |

| Data Converters            | A/D 10x12b                                                              |

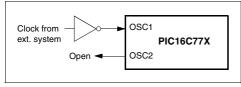

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

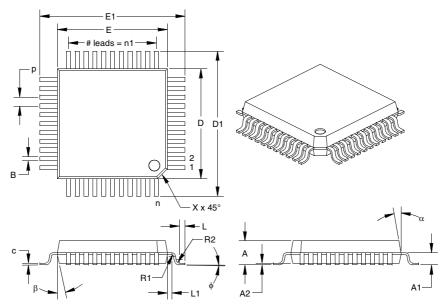

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c774-i-l |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Key Features<br>PICmicro™ Mid-Range Reference Manual<br>(DS33023) | PIC16C773                          | PIC16C774                          |

|-------------------------------------------------------------------|------------------------------------|------------------------------------|

| Operating Frequency                                               | DC - 20 MHz                        | DC - 20 MHz                        |

| Resets (and Delays)                                               | POR, BOR, MCLR, WDT<br>(PWRT, OST) | POR, BOR, MCLR, WDT<br>(PWRT, OST) |

| Program Memory (14-bit words)                                     | 4K                                 | 4K                                 |

| Data Memory (bytes)                                               | 256                                | 256                                |

| Interrupts                                                        | 13                                 | 14                                 |

| I/O Ports                                                         | Ports A,B,C                        | Ports A,B,C,D,E                    |

| Timers                                                            | 3                                  | 3                                  |

| Capture/Compare/PWM modules                                       | 2                                  | 2                                  |

| Serial Communications                                             | MSSP, USART                        | MSSP, USART                        |

| Parallel Communications                                           | —                                  | PSP                                |

| 12-bit Analog-to-Digital Module                                   | 6 input channels                   | 10 input channels                  |

| Instruction Set                                                   | 35 Instructions                    | 35 Instructions                    |

#### **Table of Contents**

| 1.0 Device Overview                                                             | 5   |

|---------------------------------------------------------------------------------|-----|

| 2.0 Memory Organization                                                         | 11  |

| 3.0 I/O Ports                                                                   |     |

| 4.0 Timer0 Module                                                               |     |

| 5.0 Timer1 Module                                                               | 41  |

| 6.0 Timer2 Module                                                               | 45  |

| 7.0 Capture/Compare/PWM (CCP) Module(s)                                         |     |

| 8.0 Master Synchronous Serial Port (MSSP) Module                                | 53  |

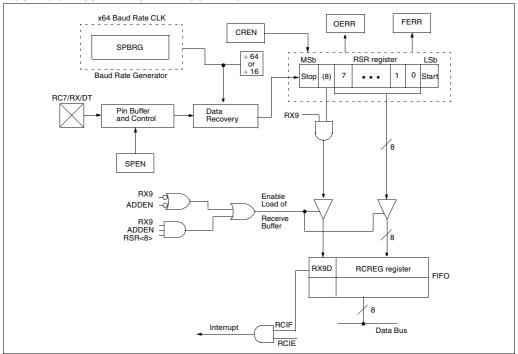

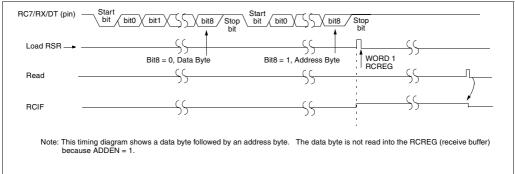

| 9.0 Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) |     |

| 10.0 Voltage Reference Module and Low-voltage Detect                            | 113 |

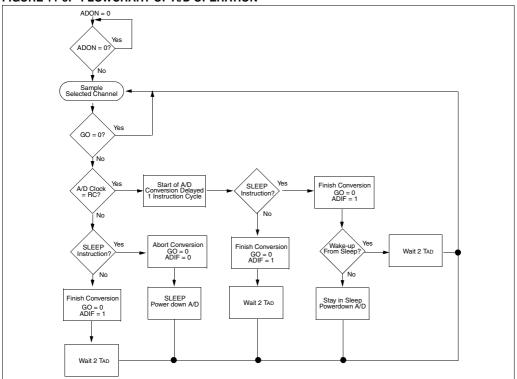

| 11.0 Analog-to-Digital Converter (A/D) Module                                   | 117 |

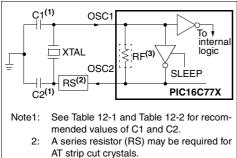

| 12.0 Special Features of the CPU                                                | 127 |

| 13.0 Instruction Set Summary                                                    | 143 |

| 14.0 Development Support                                                        | 145 |

| 15.0 Electrical Characteristics                                                 | 151 |

| 16.0 DC and AC Characteristics Graphs and Tables                                | 173 |

| 17.0 Packaging Information                                                      | 175 |

| Appendix A: Revision History                                                    | 187 |

| Appendix B: Device Differences                                                  | 187 |

| Appendix C: Conversion Considerations                                           | 187 |

| Index                                                                           | 189 |

| Bit/Register Cross-Reference List                                               | 196 |

| On-Line Support                                                                 | 197 |

| Reader Response                                                                 | 198 |

| PIC16C77X Product Identification System                                         | 199 |

## To Our Valued Customers

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please check our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (602) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

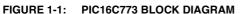

# 1.0 DEVICE OVERVIEW

This document contains device-specific information. Additional information may be found in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

There a two devices (PIC16C773 and PIC16C774) covered by this datasheet. The PIC16C773 devices come in 28-pin packages and the PIC16C774 devices come in 40-pin packages. The 28-pin devices do not have a Parallel Slave Port implemented.

The following two figures are device block diagrams sorted by pin number; 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-1 and Table 1-2, respectively.

#### 2.2.2.5 PIR1 REGISTER

This register contains the individual flag bits for the peripheral interrupts.

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# FIGURE 2-7: PIR1 REGISTER (ADDRESS 0Ch)

| R/W-0                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R-0          | R-0        | R/W-0         | R/W-0                        | R/W-0        | R/W-0          |                                                                   |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|---------------|------------------------------|--------------|----------------|-------------------------------------------------------------------|--|

| PSPIF <sup>(1)</sup><br>bit7 | ADIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RCIF         | TXIF       | SSPIF         | CCP1IF                       | TMR2IF       | TMR1IF<br>bit0 | R = Readable bit<br>W = Writable bit                              |  |

| 2                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |            |               |                              |              | 5110           | U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |

| bit 7:                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | d or a write | e operatio | n has take    | e Interrupt I<br>en place (m |              | red in soft    | ware)                                                             |  |

| bit 6:                       | <b>ADIF</b> : A/E<br>1 = An A/I<br>0 = The A                                                                                                                                                                                                                                                                                                                                                                                                                           | D convers    | ion compl  | eted (mus     | t be cleared                 | d in softwa  | re)            |                                                                   |  |

| bit 5:                       | <b>RCIF</b> : US<br>1 = The U<br>0 = The U                                                                                                                                                                                                                                                                                                                                                                                                                             | ISART rec    | eive buffe | r is full (cl | eared by re                  | ading RCF    | REG)           |                                                                   |  |

| bit 4:                       | <b>TXIF</b> : USART Transmit Interrupt Flag bit<br>1 = The USART transmit buffer is empty (cleared by writing to TXREG)<br>0 = The USART transmit buffer is full                                                                                                                                                                                                                                                                                                       |              |            |               |                              |              |                |                                                                   |  |

| bit 3:                       | <b>SSPIF</b> : Synchronous Serial Port Interrupt Flag bit<br>1 = The transmission/reception is complete (must be cleared in software)<br>0 = Waiting to transmit/receive                                                                                                                                                                                                                                                                                               |              |            |               |                              |              |                |                                                                   |  |

| bit 2:                       | CCPTIF: CCP1 Interrupt Flag bit         Capture Mode         1 = A TMR1 register capture occurred (must be cleared in software)         0 = No TMR1 register capture occurred         Compare Mode         1 = A TMR1 register compare match occurred (must be cleared in software)         0 = No TMR1 register compare match occurred (must be cleared in software)         0 = No TMR1 register compare match occurred         PWM Mode         Unused in this mode |              |            |               |                              |              |                |                                                                   |  |

| bit 1:                       | <ul> <li>TMR2IF: TMR2 to PR2 Match Interrupt Flag bit</li> <li>1 = TMR2 to PR2 match occurred (must be cleared in software)</li> <li>0 = No TMR2 to PR2 match occurred</li> </ul>                                                                                                                                                                                                                                                                                      |              |            |               |                              |              |                |                                                                   |  |

| bit 0:                       | <b>TMR1IF</b> : 1<br>1 = TMR1<br>0 = TMR1                                                                                                                                                                                                                                                                                                                                                                                                                              | register o   | overflowed | l (must be    | bit<br>cleared in s          | software)    |                |                                                                   |  |

| Note 1:                      | PSPIF is                                                                                                                                                                                                                                                                                                                                                                                                                                                               | reserved o   | on the 28- | pin device    | s, always m                  | naintain thi | s bit clear.   |                                                                   |  |

# FIGURE 8-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS: 94h)

| R/W-0  | R/W-0                                                         | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R-0                                                                        | R-0                                       | R-0                                          | R-0          | R-0                                            |                                                                                    |

|--------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------|--------------|------------------------------------------------|------------------------------------------------------------------------------------|

| SMP    | CKE                                                           | D/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Р                                                                          | S                                         | R/W                                          | UA           | BF                                             | R =Readable bit                                                                    |

| bit7   |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |                                           |                                              |              | bit0                                           | W =Writable bit<br>U =Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |

| oit 7: | <u>SPI Ma</u>                                                 | ample bi<br>ster Mod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <u>e</u>                                                                   | end of data                               | a output time                                |              |                                                |                                                                                    |

|        | 0 = Inpi<br><u>SPI Sla</u>                                    | ut data sa<br><u>ve Mode</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | impled at i                                                                | middle of c                               | lata output ti<br>ed in slave r              | me           |                                                |                                                                                    |

|        | 1= Slev                                                       | rate cor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            | ed for star                               | dard speed                                   | •            | <hz 1="" and="" i<="" td=""><td>MHz)</td></hz> | MHz)                                                                               |

| oit 6: | CKP =                                                         | <u>0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                                                          | ect (Figure                               | 8-6, Figure 8                                | 3-8, and Fig | ure 8-9)                                       |                                                                                    |

|        | 0 = Dat<br><u>CKP =</u><br>1 = Dat                            | a transmi<br><u>1</u><br>a transmi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | tted on fal<br>tted on fal                                                 | ling edge o<br>ling edge o<br>ling edge o | of SCK<br>of SCK                             |              |                                                |                                                                                    |

| oit 5: | 1 = Indi                                                      | cates tha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t the last b                                                               |                                           | /)<br>ed or transm<br>ed or transm           |              |                                                |                                                                                    |

| oit 4: | 1 = Indi                                                      | de only.<br>cates tha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                            | t has been                                | en the MSS<br>detected las                   |              |                                                | SSPEN is cleared)<br>ET)                                                           |

| oit 3: | 1 = Indi                                                      | de only.<br>cates tha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                            | it has beer                               | en the MSS                                   |              |                                                | SSPEN is cleared)<br>EET)                                                          |

| oit 2: | This bit<br>address                                           | holds the match te holds the holds the holds the holds are holds and holds the holds are holds and holds the holds are holds a | e R/W bit<br>the next                                                      | informatio                                | mode only)<br>on following<br>top bit, or no |              | lress matc                                     | h. This bit is only valid from th                                                  |

|        | 0 = Wri<br><u>In I<sup>2</sup>C n</u><br>1 = Trai<br>0 = Trai | te<br><u>naster mo</u><br>nsmit is ir<br>nsmit is n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n progress<br>ot in progr                                                  | ess.                                      |                                              | KEN will in  | diagta if th                                   | e MSSP is in IDLE mode                                                             |

| oit 1: | <b>UA</b> : Up<br>1 = Indi                                    | date Add<br>cates tha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ress (10-b<br>t the user                                                   | it I <sup>2</sup> C mod                   | e only)<br>Ipdate the ac                     |              |                                                |                                                                                    |

| oit O: | <u>Receive</u><br>1 = Rec<br>0 = Rec<br><u>Transm</u>         | eive com<br>eive not<br>it (l <sup>2</sup> C mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>d I<sup>2</sup>C mod</u><br>plete, SSI<br>complete,<br><u>ode only)</u> | PBUF is fu<br>SSPBUF i                    |                                              |              |                                                |                                                                                    |

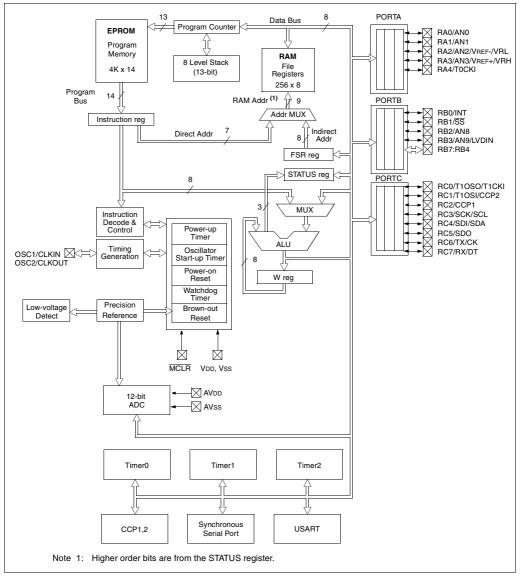

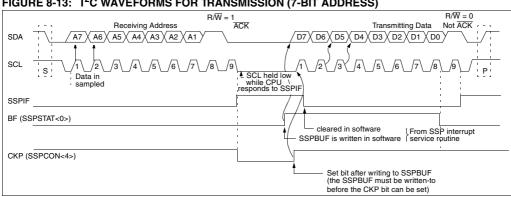

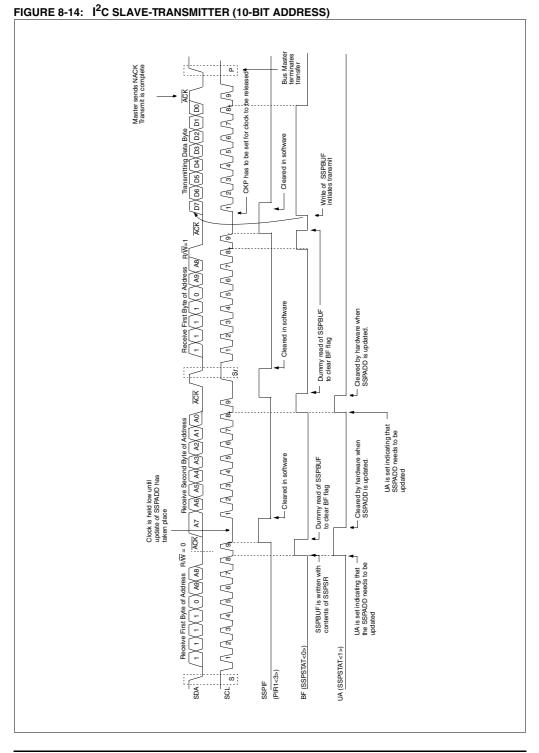

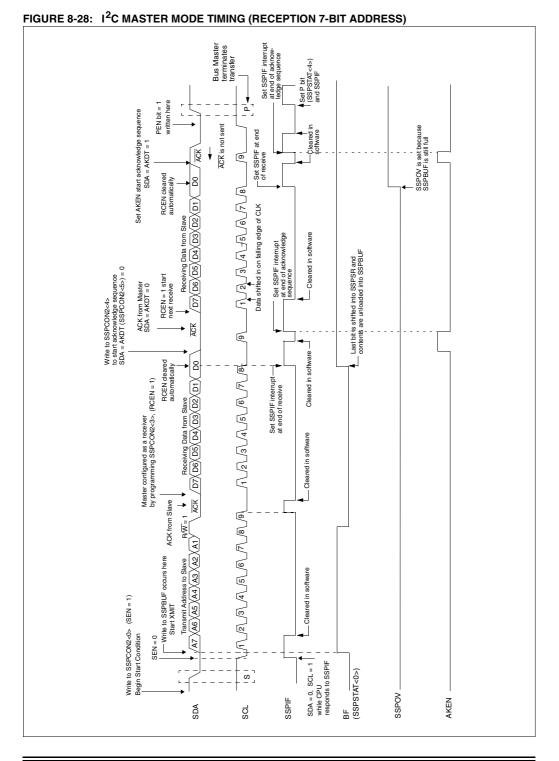

# 8.2 MSSP I<sup>2</sup>C Operation

The MSSP module in I<sup>2</sup>C mode fully implements all master and slave functions (including general call support) and provides interrupts on start and stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing.

Refer to Application Note AN578, "Use of the SSP Module in the I<sup>2</sup>C Multi-Master Environment."

A "glitch" filter is on the SCL and SDA pins when the pin is an input. This filter operates in both the 100 kHz and 400 kHz modes. In the 100 kHz mode, when these pins are an output, there is a slew rate control of the pin that is independent of device frequency.

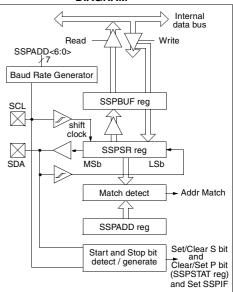

#### FIGURE 8-11: I<sup>2</sup>C MASTER MODE BLOCK DIAGRAM

Two pins are used for data transfer. These are the SCL pin, which is the clock, and the SDA pin, which is the data. The SDA and SCL pins that are automatically configured when the  $l^2C$  mode is enabled. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSPCON<5>).

The MSSP module has six registers for  ${\rm I}^2 C$  operation. They are the:

- SSP Control Register (SSPCON)

- SSP Control Register2 (SSPCON2)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

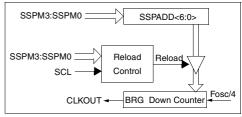

The SSPCON register allows control of the I<sup>2</sup>C operation. Four mode selection bits (SSPCON<3:0>) allow one of the following I<sup>2</sup>C modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Master mode, clock = OSC/4 (SSPADD +1)

Before selecting any  $I^2C$  mode, the SCL and SDA pins must be programmed to inputs by setting the appropriate TRIS bits. Selecting an  $I^2C$  mode, by setting the SSPEN bit, enables the SCL and SDA pins to be used as the clock and data lines in  $I^2C$  mode.

#### SLEEP OPERATION 8.2.3

While in sleep mode, the I<sup>2</sup>C module can receive addresses or data, and when an address match or complete byte transfer occurs wake the processor from sleep (if the SSP interrupt is enabled).

#### EFFECTS OF A RESET 8.2.4

A reset diables the SSP module and terminates the current transfer.

| Name    | Bit 7                                                                 | Bit 6                                                                                                                                                | Bit 5                                                                                                                                                                                       | Bit 4                                                                                                                                                   | Bit 3                                                                                                                                                                                  | Bit 2                                                                                                                                                                                                                             | Bit 1                                                                                                                                                                                                                                                             | Bit 0                                                                                                                                                                                                                                                                                          | POR, BOR                                                                                                                                                                                                                                                                                                | MCLR, WDT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTCON  | GIE                                                                   | PEIE                                                                                                                                                 | TOIE                                                                                                                                                                                        | INTE                                                                                                                                                    | RBIE                                                                                                                                                                                   | TOIF                                                                                                                                                                                                                              | INTF                                                                                                                                                                                                                                                              | RBIF                                                                                                                                                                                                                                                                                           | 0000 000x                                                                                                                                                                                                                                                                                               | 0000 000u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PIR1    | PSPIF <sup>(1)</sup>                                                  | ADIF                                                                                                                                                 | RCIF                                                                                                                                                                                        | TXIF                                                                                                                                                    | SSPIF                                                                                                                                                                                  | CCP1IF                                                                                                                                                                                                                            | TMR2IF                                                                                                                                                                                                                                                            | TMR1IF                                                                                                                                                                                                                                                                                         | 0000 0000                                                                                                                                                                                                                                                                                               | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PIE1    | PSPIE <sup>(1)</sup>                                                  | ADIE                                                                                                                                                 | RCIE                                                                                                                                                                                        | TXIE                                                                                                                                                    | SSPIE                                                                                                                                                                                  | CCP1IE                                                                                                                                                                                                                            | TMR2IE                                                                                                                                                                                                                                                            | TMR1IE                                                                                                                                                                                                                                                                                         | 0000 0000                                                                                                                                                                                                                                                                                               | 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PIR2    | LVDIF                                                                 | —                                                                                                                                                    |                                                                                                                                                                                             | -                                                                                                                                                       | BCLIF                                                                                                                                                                                  | —                                                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                                 | CCP2IF                                                                                                                                                                                                                                                                                         | 00                                                                                                                                                                                                                                                                                                      | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PIE2    | LVDIE                                                                 | _                                                                                                                                                    | _                                                                                                                                                                                           | _                                                                                                                                                       | BCLIE                                                                                                                                                                                  | _                                                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                                 | CCP2IE                                                                                                                                                                                                                                                                                         | 00                                                                                                                                                                                                                                                                                                      | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |