Welcome to E-XFL.COM

# What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | PIC                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 20MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 33                                                                    |

| Program Memory Size        | 7KB (4K x 14)                                                         |

| Program Memory Type        | OTP                                                                   |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 256 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                             |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LCC (J-Lead)                                                       |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c774-l |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

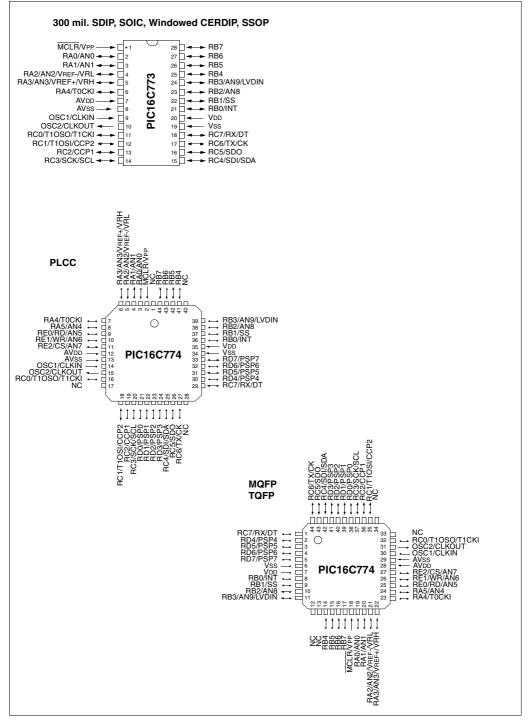

### **Pin Diagrams**

#### **Table of Contents**

| 1.0 Device Overview                                                             | 5   |

|---------------------------------------------------------------------------------|-----|

| 2.0 Memory Organization                                                         | 11  |

| 3.0 I/O Ports                                                                   |     |

| 4.0 Timer0 Module                                                               |     |

| 5.0 Timer1 Module                                                               | 41  |

| 6.0 Timer2 Module                                                               | 45  |

| 7.0 Capture/Compare/PWM (CCP) Module(s)                                         |     |

| 8.0 Master Synchronous Serial Port (MSSP) Module                                | 53  |

| 9.0 Addressable Universal Synchronous Asynchronous Receiver Transmitter (USART) |     |

| 10.0 Voltage Reference Module and Low-voltage Detect                            | 113 |

| 11.0 Analog-to-Digital Converter (A/D) Module                                   | 117 |

| 12.0 Special Features of the CPU                                                | 127 |

| 13.0 Instruction Set Summary                                                    | 143 |

| 14.0 Development Support                                                        | 145 |

| 15.0 Electrical Characteristics                                                 | 151 |

| 16.0 DC and AC Characteristics Graphs and Tables                                | 173 |

| 17.0 Packaging Information                                                      | 175 |

| Appendix A: Revision History                                                    | 187 |

| Appendix B: Device Differences                                                  | 187 |

| Appendix C: Conversion Considerations                                           | 187 |

| Index                                                                           | 189 |

| Bit/Register Cross-Reference List                                               | 196 |

| On-Line Support                                                                 | 197 |

| Reader Response                                                                 | 198 |

| PIC16C77X Product Identification System                                         | 199 |

# To Our Valued Customers

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please check our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (602) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

| TABLE 1-2 P | PIC16C774 PINOUT DESCRIPTION | (Cont.'d) |

|-------------|------------------------------|-----------|

|-------------|------------------------------|-----------|

| Pin Name             | DIP<br>Pin# | PLCC<br>Pin#   | QFP<br>Pin#     | I/O/P<br>Type | Buffer<br>Type                                 | Description                                                                                            |

|----------------------|-------------|----------------|-----------------|---------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------|

|                      |             |                |                 |               |                                                | PORTC is a bi-directional I/O port.                                                                    |

| RC0/T1OSO/T1CKI      | 15          | 16             | 32              | I/O           | ST                                             | RC0 can also be the Timer1 oscillator output or a<br>Timer1 clock input.                               |

| RC1/T1OSI/CCP2       | 16          | 18             | 35              | I/O           | ST                                             | RC1 can also be the Timer1 oscillator input or<br>Capture2 input/Compare2 output/PWM2 output.          |

| RC2/CCP1             | 17          | 19             | 36              | I/O           | ST                                             | RC2 can also be the Capture1 input/Compare1<br>output/PWM1 output.                                     |

| RC3/SCK/SCL          | 18          | 20             | 37              | I/O           | ST                                             | RC3 can also be the synchronous serial clock input/<br>output for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA          | 23          | 25             | 42              | I/O           | ST                                             | RC4 can also be the SPI Data In (SPI mode) or data $I/O$ ( $I^{2}C$ mode).                             |

| RC5/SDO              | 24          | 26             | 43              | I/O           | ST                                             | RC5 can also be the SPI Data Out (SPI mode).                                                           |

| RC6/TX/CK            | 25          | 27             | 44              | I/O           | ST                                             | RC6 can also be the USART Asynchronous<br>Transmit or Synchronous Clock.                               |

| RC7/RX/DT            | 26          | 29             | 1               | I/O           | ST                                             | RC7 can also be the USART Asynchronous Receive<br>or Synchronous Data.                                 |

|                      |             |                |                 |               |                                                | PORTD is a bi-directional I/O port or parallel slave port                                              |

|                      |             |                |                 |               |                                                | when interfacing to a microprocessor bus.                                                              |

| RD0/PSP0             | 19          | 21             | 38              | I/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD1/PSP1             | 20          | 22             | 39              | I/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD2/PSP2             | 21          | 23             | 40              | I/O           | ST/TTL <sup>(3)</sup><br>ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD3/PSP3<br>RD4/PSP4 | 22<br>27    | 24<br>30       | 41<br>2         | 1/O<br>1/O    | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD5/PSP5             | 27          | 30             | 2               | 1/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD6/PSP6             | 20<br>29    | 32             | 4               | 1/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD7/PSP7             | 29<br>30    | 32             | 4<br>5          | 1/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

|                      | 30          |                | 5               | 1/0           | 31/112                                         | PORTE is a bi-directional I/O port.                                                                    |

| RE0/RD/AN5           | 8           | 9              | 25              | I/O           | ST/TTL <sup>(3)</sup>                          | RE0 can also be read control for the parallel slave<br>port, or analog input5.                         |

| RE1/WR/AN6           | 9           | 10             | 26              | I/O           | ST/TTL <sup>(3)</sup>                          | RE1 can also be write control for the parallel slave<br>port, or analog input6.                        |

| RE2/CS/AN7           | 10          | 11             | 27              | I/O           | ST/TTL <sup>(3)</sup>                          | RE2 can also be select control for the parallel slave<br>port, or analog input7.                       |

| AVss                 | 12          | 13             | 29              | Р             |                                                | Ground reference for A/D converter                                                                     |

| AVDD                 | 11          | 12             | 28              | Р             |                                                | Positive supply for A/D converter                                                                      |

| Vss                  | 31          | 34             | 6               | Р             | _                                              | Ground reference for logic and I/O pins.                                                               |

| VDD                  | 32          | 35             | 7               | P             | _                                              | Positive supply for logic and I/O pins.                                                                |

| NC                   | -           | 1,17,28,<br>40 | 12,13,<br>33,34 |               | -                                              | These pins are not internally connected. These pins should be left unconnected.                        |

| Legend: I = input    | O = outp    | ut             | I/C             | ) = input     | /output                                        | P = power                                                                                              |

|                      | — = Not     | used           | TT              | L = TTL       | . input                                        | ST = Schmitt Trigger input                                                                             |

Note 1: This buffer is a Schmitt Trigger input when configured for the multiplexed function.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

# PIC16C77X

#### 2.2.2.5 PIR1 REGISTER

This register contains the individual flag bits for the peripheral interrupts.

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# FIGURE 2-7: PIR1 REGISTER (ADDRESS 0Ch)

| R/W-0                        | R/W-0                                        | R-0                                                                                             | R-0                                              | R/W-0                                  | R/W-0                        | R/W-0        | R/W-0          |                                                                   |

|------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------|------------------------------|--------------|----------------|-------------------------------------------------------------------|

| PSPIF <sup>(1)</sup><br>bit7 | ADIF                                         | RCIF                                                                                            | TXIF                                             | SSPIF                                  | CCP1IF                       | TMR2IF       | TMR1IF<br>bit0 | R = Readable bit<br>W = Writable bit                              |

| 2                            |                                              |                                                                                                 |                                                  |                                        |                              |              | 5110           | U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:                       |                                              | d or a write                                                                                    | e operatio                                       | n has take                             | e Interrupt I<br>en place (m |              | red in softw   | ware)                                                             |

| bit 6:                       | <b>ADIF</b> : A/E<br>1 = An A/I<br>0 = The A | D convers                                                                                       | ion compl                                        | eted (mus                              | t be cleared                 | d in softwa  | re)            |                                                                   |

| bit 5:                       | <b>RCIF</b> : US<br>1 = The U<br>0 = The U   | ISART rec                                                                                       | eive buffe                                       | r is full (cl                          | eared by re                  | ading RCF    | REG)           |                                                                   |

| bit 4:                       | <b>TXIF</b> : US/<br>1 = The U<br>0 = The U  | ISART trai                                                                                      | nsmit buffe                                      | er is empty                            | t<br>y (cleared              | by writing t | o TXREG)       |                                                                   |

| bit 3:                       |                                              | ,<br>ansmissio                                                                                  | n/receptic                                       | on is comp                             | pt Flag bit<br>lete (must l  | be cleared   | in software    | 9)                                                                |

| bit 2:                       | 0 = No TM<br>Compare                         | <u>Aode</u><br>R1 registe<br>MR1 regist<br><u>Mode</u><br>R1 registe<br>MR1 regist<br><u>de</u> | r capture<br>er capture<br>r compare<br>er compa | occurred (<br>e occurred<br>e match oc | curred (mu                   |              |                | rare)                                                             |

| bit 1:                       | TMR2IF:<br>1 = TMR2<br>0 = No TM             | to PR2 m                                                                                        | natch occu                                       | irred (mus                             | Flag bit<br>t be cleared     | d in softwa  | re)            |                                                                   |

| bit 0:                       | <b>TMR1IF</b> : 1<br>1 = TMR1<br>0 = TMR1    | register o                                                                                      | overflowed                                       | l (must be                             | bit<br>cleared in s          | software)    |                |                                                                   |

| Note 1:                      | PSPIF is                                     | reserved o                                                                                      | on the 28-                                       | pin device                             | s, always m                  | naintain thi | s bit clear.   |                                                                   |

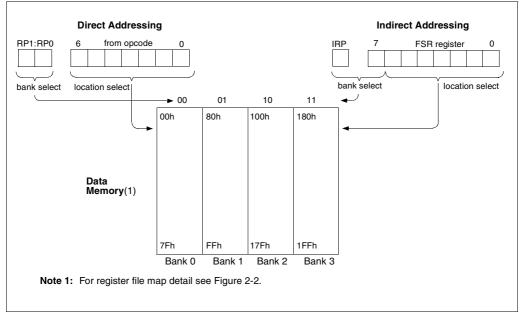

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

#### EXAMPLE 2-1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT     | incf<br>btfss | FSR<br>INDF<br>FSR<br>FSR,4 | ; to RAM<br>;clear INDF register<br>;inc pointer<br>;all done? |

|----------|---------------|-----------------------------|----------------------------------------------------------------|

|          | goto          | NEX.L.                      | ;NO, clear next                                                |

| CONTINUE |               |                             |                                                                |

|          | :             |                             | ;YES, continue                                                 |

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-11.

# FIGURE 2-11: DIRECT/INDIRECT ADDRESSING

# 3.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PICmicro™ Mid-Range Reference Manual, (DS33023).

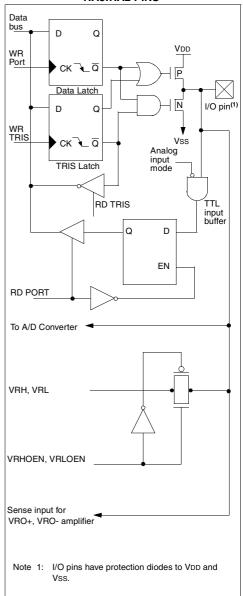

# 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide bi-directional port for the 40/44 pin devices and is 5-bits wide for the 28-pin devices. PORTA<5> is not on the 28-pin devices. The corresponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, i.e., put the corresponding PORTA pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, i.e., put the contents of the output latch on the selected pin.

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and analog VREF inputs and precision on-board references (VRL/VRH). The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

Note: On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

# EXAMPLE 3-1: INITIALIZING PORTA

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| CLRF  | PORTA   |     | ; | Initialize PORTA by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISA   |     | ; | Set RA<3:0> as inputs |

|       |         |     | ; | RA<5:4> as outputs    |

|       |         |     | ; | TRISA<7:6> are always |

|       |         |     | ; | read as '0'.          |

|       |         |     |   |                       |

#### FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA2 PINS

#### 5.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers; TMR1H and TMR1L)

- Readable and writable (Both registers)

- · Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- · Reset from CCP module trigger

Timer1 has a control register, shown in Figure 5-1. Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Figure 5-3 is a simplified block diagram of the Timer1 module.

Additional information on timer modules is available in the PICmicro™ Mid-Range Reference Manual, (DS33023).

#### 5.1 **Timer1 Operation**

Timer1 can operate in one of these modes:

- · As a timer

- · As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the clock select bit. TMR1CS (T1CON<1>).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored.

Timer1 also has an internal "reset input". This reset can be generated by the CCP module (Section 7.0).

#### T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h) U-0 U-0 R/W-0 R/W-0 B/W-0 R/W-0 **B/W-0** R/W-0 T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON R = Readable bit W = Writable bit bit7 bit0 = Unimplemented bit, U read as '0' n = Value at POR reset bit 7-6: Unimplemented: Read as '0' bit 5-4: T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits 11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value 00 = 1:1 Prescale value T1OSCEN: Timer1 Oscillator Enable Control bit hit 3 1 = Oscillator is enabled 0 = Oscillator is shut off Note: The oscillator inverter and feedback resistor are turned off to eliminate power drain T1SYNC: Timer1 External Clock Input Synchronization Control bit bit 2: TMR1CS = 11 = Do not synchronize external clock input 0 = Synchronize external clock input TMR1CS = 0This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0. TMR1CS: Timer1 Clock Source Select bit bit 1: 1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge) 0 = Internal clock (Fosc/4)

# FIGURE 5-1:

- 1 = Enables Timer1

- 0 = Stops Timer1

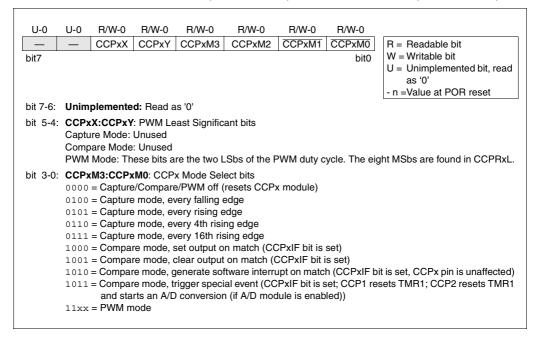

# 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE(S)

Each CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Table 7-1 shows the timer resources of the CCP module modes.

The operation of CCP1 is identical to that of CCP2, with the exception of the special trigger. Therefore, operation of a CCP module in the following sections is described with respect to CCP1.

Table 7-2 shows the interaction of the CCP modules.

#### CCP1 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

# CCP2 Module

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. All are readable and writable.

Additional information on the CCP module is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

## TABLE 7-1 CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

| CCPx Mode | CCPy Mode | Interaction                                                                           |

|-----------|-----------|---------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base.                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM       | The PWMs will have the same frequency, and update rate (TMR2 interrupt).              |

| PWM       | Capture   | None                                                                                  |

| PWM       | Compare   | None                                                                                  |

# TABLE 7-2 INTERACTION OF TWO CCP MODULES

# FIGURE 7-1: CCP1CON REGISTER (ADDRESS 17h) / CCP2CON REGISTER (ADDRESS 1Dh)

| 1) |

|----|

| 1  |

| BAUD<br>RATE<br>(K)                                        | Fosc = 2<br>KBAUD                                     | 0 MHz<br>%<br>ERROR                                 | SPBRG<br>value<br>(decimal)                            | 16 MHz<br>KBAUD                                        | %<br>ERROF                       | SPBRG<br>value<br>decimal                               |                                                                    | %                                                       | b Va                                          | PBRG<br>alue<br>cimal)                           | 7.16 MHz<br>KBAUD E                                                                       | %                                             | SPBRG<br>value<br>decimal)                  |                                               |                                                  |

|------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|----------------------------------|---------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------|-----------------------------------------------|--------------------------------------------------|

| 9.6                                                        | 9.615                                                 | +0.16                                               | 129                                                    | 9.615                                                  | +0.16                            | 103                                                     | 9.615                                                              | 5 +0.                                                   | 16                                            | 64                                               | 9.520                                                                                     | -0.83                                         | 46                                          |                                               |                                                  |

| 19.2                                                       | 19.230                                                | +0.16                                               | 64                                                     | 19.230                                                 | +0.16                            | 51                                                      | 18.93                                                              | 9 -1.3                                                  | 36                                            | 32                                               | 19.454                                                                                    | +1.32                                         | 22                                          |                                               |                                                  |

| 38.4                                                       | 37.878                                                | -1.36                                               | 32                                                     | 38.461                                                 | +0.16                            | 25                                                      | 39.06                                                              | 2 +1                                                    | .7                                            | 15                                               | 37.286                                                                                    | -2.90                                         | 11                                          |                                               |                                                  |

| 57.6                                                       | 56.818                                                | -1.36                                               | 21                                                     | 58.823                                                 | +2.12                            | 16                                                      | 56.81                                                              | 8 -1.3                                                  | 36                                            | 10                                               | 55.930                                                                                    | -2.90                                         | 7                                           |                                               |                                                  |

| 115.2                                                      | 113.636                                               | -1.36                                               | 10                                                     | 111.111                                                | -3.55                            | 8                                                       | 125                                                                | +8.                                                     | 51                                            | 4                                                | 111.860                                                                                   | -2.90                                         | 3                                           |                                               |                                                  |

| 250                                                        | 250                                                   | 0                                                   | 4                                                      | 250                                                    | 0                                | 3                                                       | NA                                                                 | -                                                       |                                               | -                                                | NA                                                                                        | -                                             | -                                           |                                               |                                                  |

| 625                                                        | 625                                                   | 0                                                   | 1                                                      | NA                                                     | -                                | -                                                       | 625                                                                | 0                                                       |                                               | 0                                                | NA                                                                                        | -                                             | -                                           |                                               |                                                  |

| 1250                                                       | 1250                                                  | 0                                                   | 0                                                      | NA                                                     | -                                | -                                                       | NA                                                                 | -                                                       |                                               | -                                                | NA                                                                                        | -                                             | -                                           |                                               |                                                  |

| DALID                                                      | Fosc = 5                                              | 000 1411-                                           |                                                        |                                                        |                                  |                                                         |                                                                    |                                                         |                                               |                                                  |                                                                                           |                                               |                                             |                                               |                                                  |

| BAUD<br>RATE                                               |                                                       | %                                                   | SPBRG<br>value                                         | 4 MHz                                                  | %                                | SPBRG<br>value                                          | 8.579 MH                                                           | %                                                       | SPBRG<br>value                                |                                                  | %                                                                                         | SPBRG<br>value                                |                                             | %                                             | SPBRG<br>value                                   |

|                                                            | KBAUD                                                 | %                                                   | SPBRG<br>value                                         |                                                        |                                  | SPBRG                                                   |                                                                    | %                                                       | value                                         |                                                  | %                                                                                         |                                               |                                             |                                               | value                                            |

| RATE                                                       |                                                       | %                                                   | SPBRG<br>value                                         |                                                        |                                  | SPBRG<br>value<br>(decimal) ł                           |                                                                    | %                                                       | value                                         |                                                  | %<br>UD ERROF                                                                             | value                                         |                                             | %                                             | value                                            |

| RATE<br>(K)                                                | KBAUD                                                 | %<br>ERROR                                          | SPBRG<br>value<br>(decimal)                            | KBAUD                                                  |                                  | SPBRG<br>value<br>(decimal) ł                           | KBAUD                                                              | %<br>ERROR                                              | value<br>(decimal                             | ) KBA                                            | %<br>UD ERROF<br>28 -6.99                                                                 | value<br>(decimal)                            | ) KBAUD                                     | %                                             | value                                            |

| RATE<br>(K)<br>9.6                                         | KBAUD<br>9.6                                          | %<br>ERROR<br>0                                     | SPBRG<br>value<br>(decimal)<br>32                      | KBAUD<br>NA                                            | ERROR<br>-                       | SPBRG<br>value<br>(decimal) F<br>207                    | KBAUD<br>9.727                                                     | %<br>ERROR<br>+1.32                                     | value<br>(decimal<br>22                       | ) KBA                                            | %<br>UD ERROF<br>28 -6.99<br>33 +8.51                                                     | value<br>(decimal)<br>6                       | ) KBAUD                                     | %                                             | value                                            |

| RATE<br>(K)<br>9.6<br>19.2                                 | KBAUD<br>9.6<br>18.645                                | %<br>ERROR<br>0<br>-2.94                            | SPBRG<br>value<br>(decimal)<br>32<br>16                | KBAUD<br>NA<br>1.202                                   | ERROR<br>-<br>+0.17              | SPBRG<br>value<br>(decimal) F<br>-<br>207<br>103        | KBAUD<br>9.727<br>18.643                                           | %<br>ERROR<br>+1.32<br>-2.90                            | value<br>(decimal<br>22<br>11                 | ) KBA<br>8.92<br>20.8                            | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61                                        | value<br>(decimal)<br>6<br>2                  | ) KBAUD<br>NA<br>NA                         | ERROR<br>-<br>-                               | value<br>(decimal)<br>-<br>-                     |

| RATE<br>(K)<br>9.6<br>19.2<br>38.4<br>57.6<br>115.2        | KBAUD<br>9.6<br>18.645<br>39.6<br>52.8<br>105.6       | %<br>ERROR<br>0<br>-2.94<br>+3.12                   | SPBRG<br>value<br>(decimal)<br>32<br>16<br>7           | KBAUD<br>NA<br>1.202<br>2.403<br>9.615<br>19.231       | -<br>+0.17<br>+0.13              | SPBRG<br>value<br>(decimal) H<br>207<br>103<br>25<br>12 | KBAUD<br>9.727<br>18.643<br>37.286<br>55.930<br>111.860            | %<br>ERROR<br>+1.32<br>-2.90<br>-2.90<br>-2.90<br>-2.90 | value<br>(decimal<br>22<br>11<br>5            | ) KBA<br>8.92<br>20.8<br>31.2<br>62.<br>NA       | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61<br>5 +8.51<br>A -                      | value<br>(decimal)<br>6<br>2<br>1             | ) KBAUD<br>NA<br>NA<br>NA<br>NA<br>NA       | * ERROR<br>-<br>-<br>-                        | value<br>(decimal)<br>-<br>-                     |

| RATE<br>(K)<br>9.6<br>19.2<br>38.4<br>57.6<br>115.2<br>250 | KBAUD<br>9.6<br>18.645<br>39.6<br>52.8<br>105.6<br>NA | %<br>ERROR<br>0<br>-2.94<br>+3.12<br>-8.33          | SPBRG<br>value<br>(decimal)<br>32<br>16<br>7<br>5      | KBAUD<br>NA<br>1.202<br>2.403<br>9.615<br>19.231<br>NA | +0.17<br>+0.13<br>+0.16          | SPBRG<br>value<br>(decimal) H<br>207<br>103<br>25<br>12 | KBAUD<br>9.727<br>18.643<br>37.286<br>55.930<br>111.860<br>223.721 | %<br>ERROR<br>+1.32<br>-2.90<br>-2.90<br>-2.90          | value<br>(decimal<br>22<br>11<br>5<br>3       | ) KBA<br>8.92<br>20.8<br>31.2<br>62.<br>NA<br>NA | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61<br>5 +8.51<br>A -<br>A -               | value<br>(decimal)<br>6<br>2<br>1<br>0        | ) KBAUD<br>NA<br>NA<br>NA<br>NA<br>NA<br>NA | * ERROR<br>-<br>-<br>-<br>-                   | value<br>(decimal)<br>-<br>-<br>-<br>-           |

| RATE<br>(K)<br>9.6<br>19.2<br>38.4<br>57.6<br>115.2        | KBAUD<br>9.6<br>18.645<br>39.6<br>52.8<br>105.6       | %<br>ERROR<br>0<br>-2.94<br>+3.12<br>-8.33<br>-8.33 | SPBRG<br>value<br>(decimal)<br>32<br>16<br>7<br>5<br>2 | KBAUD<br>NA<br>1.202<br>2.403<br>9.615<br>19.231       | +0.17<br>+0.13<br>+0.16<br>+0.16 | SPBRG<br>value<br>(decimal) H<br>207<br>103<br>25<br>12 | KBAUD<br>9.727<br>18.643<br>37.286<br>55.930<br>111.860            | %<br>ERROR<br>+1.32<br>-2.90<br>-2.90<br>-2.90<br>-2.90 | value<br>(decimal)<br>22<br>11<br>5<br>3<br>1 | ) KBA<br>8.92<br>20.8<br>31.2<br>62.<br>NA       | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61<br>5 +8.51<br>A -<br>A -<br>A -<br>A - | value<br>R (decimal)<br>6<br>2<br>1<br>0<br>- | ) KBAUD<br>NA<br>NA<br>NA<br>NA<br>NA       | %<br>ERROR<br>-<br>-<br>-<br>-<br>-<br>-<br>- | value<br>(decimal)<br>-<br>-<br>-<br>-<br>-<br>- |

# PIC16C77X

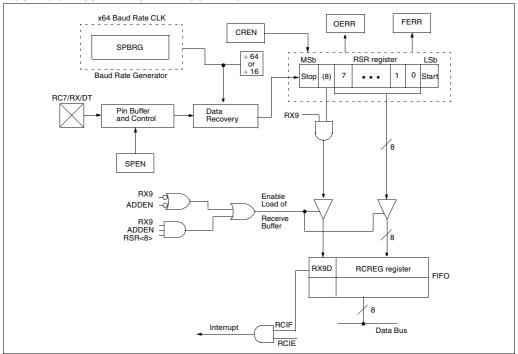

#### FIGURE 9-6: USART RECEIVE BLOCK DIAGRAM

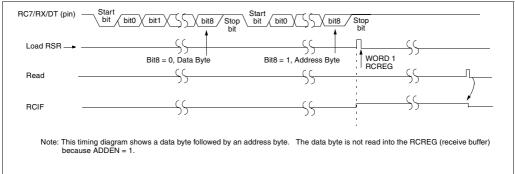

# FIGURE 9-7: ASYNCHRONOUS RECEPTION WITH ADDRESS DETECT

### 11.7 Use of the CCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP module. This requires that the CCPnM<3:0> bits be programmed as 1011b and that the A/D module is enabled (ADON is set). When the trigger occurs, the GO/DONE bit will be set on Q2 to start the A/D conversion and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D conversion cycle, with minimal software overhead (moving the ADRESH and ADRESL to the desired location). The appropriate analog input channel must be selected before the "special event trigger" sets the GO/DONE bit (starts a conversion cycle).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

### 11.8 Effects of a RESET

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted. The value that is in the ADRESH and ADRESL registers are not modified. The ADRESH and ADRESL registers will contain unknown data after a Power-on Reset.

### 11.9 <u>Faster Conversion - Lower</u> <u>Resolution Trade-off</u>

Not all applications require a result with 12-bits of resolution, but may instead require a faster conversion time. The A/D module allows users to make the trade-off of conversion speed to resolution. Regardless of the resolution required, the acquisition time is the same. To speed up the conversion, the A/D module may be halted by clearing the GO/DONE bit after the desired number of bits in the result have been converted. Once the GO/DONE bit has been cleared, all of the remaining A/D result bits are '0'. The equation to determine the time before the GO/DONE bit can be switched is as follows:

Conversion time =  $N \bullet TAD + 1TAD$

Where: N = number of bits of resolution required, and 1TAD is the amplifier settling time.

Since TAD is based from the device oscillator, the user must use some method (a timer, software loop, etc.) to determine when the A/D  $GO/\overline{DONE}$  bit may be cleared. Table 11-2 shows a comparison of time required for a conversion with 4-bits of resolution, versus the normal 12-bit resolution conversion. The example is for devices operating at 20 MHz. The A/D clock is programmed for 32 Tosc.

#### TABLE 11-2 4-BIT vs. 12-BIT CONVERSION TIMES

|               | Freq. | Resol  | ution   |

|---------------|-------|--------|---------|

|               | (MHz) | 4-bit  | 12-bit  |

| Tosc          | 20    | 50 ns  | 50 ns   |

| TAD = 32 Tosc | 20    | 1.6 μs | 1.6 μs  |

| 1Tad+N•Tad    | 20    | 8 µs   | 20.8 μs |

#### 12.2.3 RC OSCILLATOR

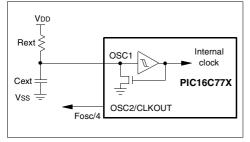

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. These factors and the variation due to tolerances of external R and C components used need to be taken into account for each application. Figure 12-4 shows how the R/C combination is connected to the PIC16C77X.

| Standard Operating Conditions (unless otherwise stated) |                                          |                                                                    |              |                     |                           |                |                                                          |  |  |  |  |

|---------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------|--------------|---------------------|---------------------------|----------------|----------------------------------------------------------|--|--|--|--|

|                                                         |                                          | Operating temperature                                              |              |                     | -40°C ≤ TA                |                | $\leq$ +85°C for industrial and                          |  |  |  |  |

| DC CHARACTERISTICS                                      |                                          |                                                                    |              |                     | 0°C ≤ TA                  |                | $\Delta \leq +70^{\circ}C$ for commercial                |  |  |  |  |

|                                                         |                                          | Operating voltage VDD range as described in DC spec Section 15.1 a |              |                     |                           |                |                                                          |  |  |  |  |

| Section 15.2.                                           |                                          |                                                                    |              |                     |                           |                |                                                          |  |  |  |  |

| Param                                                   | Characteristic                           | Sym                                                                | Min          | Typ†                | Max                       | Units          | Conditions                                               |  |  |  |  |

| No.                                                     |                                          |                                                                    |              |                     |                           |                |                                                          |  |  |  |  |

|                                                         | Output High Voltage                      |                                                                    |              |                     |                           |                |                                                          |  |  |  |  |

| D090                                                    | I/O ports (Note 3)                       | Voн                                                                | VDD - 0.7    | · —                 | —                         | V              | $10_{H} = -3.0 \text{ mA}, \text{ VDD} = 4.5 \text{ V},$ |  |  |  |  |

|                                                         |                                          |                                                                    |              |                     |                           | $\int$         | -40°C to +85°C                                           |  |  |  |  |

| D092                                                    | OSC2/CLKOUT (RC osc config)              |                                                                    | VDD - 0.7    | · _                 | $\sim$                    | ( v            | IOH = -1.3  mA, VDP = 4.5V,                              |  |  |  |  |

|                                                         |                                          |                                                                    |              |                     | $\langle \rangle \rangle$ | $\backslash$   | -40°C to +85°C                                           |  |  |  |  |

| D150*                                                   | Open-Drain High Voltage                  | Vod                                                                | —            | $\sim$              | 8.5                       | X              | RA4 pin                                                  |  |  |  |  |

|                                                         | Capacitive Loading Specs on              |                                                                    | <            |                     | 1</td <td></td> <td></td> |                |                                                          |  |  |  |  |

|                                                         | Output Pins                              |                                                                    | ~            | 1 /                 |                           | $\backslash -$ |                                                          |  |  |  |  |

| D100                                                    | OSC2 pin                                 | Cos¢2                                                              | $\sim$       | Ξź,                 | 15                        | рF             | In XT, HS and LP modes when                              |  |  |  |  |

|                                                         |                                          |                                                                    | $\backslash$ |                     | $\left  \right\rangle$    | ſ              | external clock is used to drive                          |  |  |  |  |

|                                                         |                                          | $\langle \rangle$                                                  | $ \rangle$   | $\nearrow$ '        | $\langle \rangle$         |                | OSC1.                                                    |  |  |  |  |

| D101                                                    | All I/O pins and OSC2 (in RC \           | Cio \                                                              |              | $\land \rightarrow$ | <b>5</b> 0                | pF             |                                                          |  |  |  |  |

| D102                                                    | mode) SCL, SDA in <del>/</del> 2Ĉ mode ∖ | ∖Св                                                                |              | $\leq$              | 400                       | pF             |                                                          |  |  |  |  |

| * These parameters are characterized but not tested.    |                                          |                                                                    |              |                     |                           |                |                                                          |  |  |  |  |

I nese parameters are characterized but not tested.

Data in "Typ" column is at SV, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels

represent normal operating conditions. Higher leakage current may be measured at different input voltages. 3) Negative current is defined as current sourced by the pin.

The game current is defined as current sourced by the pin.

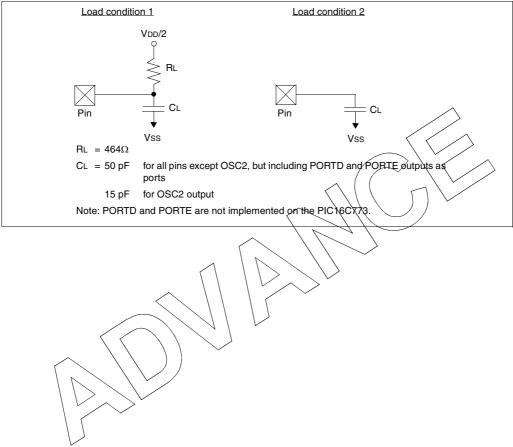

# FIGURE 15-3: LOAD CONDITIONS

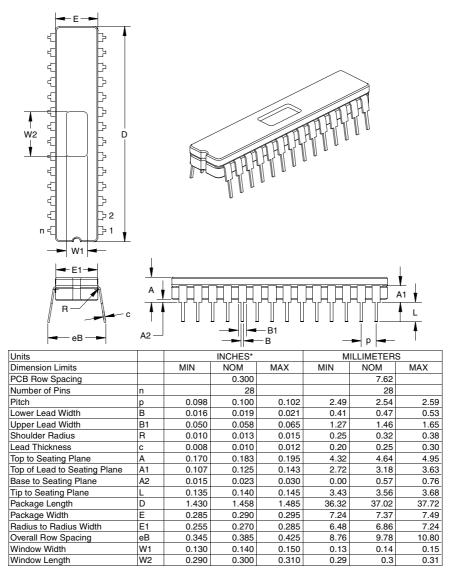

### 17.3 K04-080 28-Lead Ceramic Dual In-line with Window (JW) – 300 mil

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

\* Controlling Parameter.

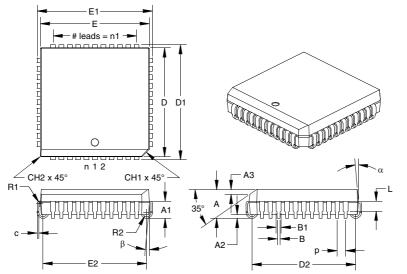

# 17.10 K04-048 44-Lead Plastic Leaded Chip Carrier (L) – Square

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                   |                 |       | INCHES* |       | MILLIMETERS |       |       |

|-------------------------|-----------------|-------|---------|-------|-------------|-------|-------|

| Dimension Limits        |                 | MIN   | NOM     | MAX   | MIN         | NOM   | MAX   |

| Number of Pins          | n               |       | 44      |       |             | 44    |       |

| Pitch                   | р               |       | 0.050   |       |             | 1.27  |       |

| Overall Pack. Height    | А               | 0.165 | 0.173   | 0.180 | 4.19        | 4.38  | 4.57  |

| Shoulder Height         | A1              | 0.095 | 0.103   | 0.110 | 2.41        | 2.60  | 2.79  |

| Standoff                | A2              | 0.015 | 0.023   | 0.030 | 0.38        | 0.57  | 0.76  |

| Side 1 Chamfer Dim.     | A3              | 0.024 | 0.029   | 0.034 | 0.61        | 0.74  | 0.86  |

| Corner Chamfer (1)      | CH1             | 0.040 | 0.045   | 0.050 | 1.02        | 1.14  | 1.27  |

| Corner Chamfer (other)  | CH2             | 0.000 | 0.005   | 0.010 | 0.00        | 0.13  | 0.25  |

| Overall Pack. Width     | E1              | 0.685 | 0.690   | 0.695 | 17.40       | 17.53 | 17.65 |

| Overall Pack. Length    | D1              | 0.685 | 0.690   | 0.695 | 17.40       | 17.53 | 17.65 |

| Molded Pack. Width      | E‡              | 0.650 | 0.653   | 0.656 | 16.51       | 16.59 | 16.66 |

| Molded Pack. Length     | D‡              | 0.650 | 0.653   | 0.656 | 16.51       | 16.59 | 16.66 |

| Footprint Width         | E2              | 0.610 | 0.620   | 0.630 | 15.49       | 15.75 | 16.00 |

| Footprint Length        | D2              | 0.610 | 0.620   | 0.630 | 15.49       | 15.75 | 16.00 |

| Pins along Width        | n1              |       | 11      |       |             | 11    |       |

| Lead Thickness          | с               | 0.008 | 0.010   | 0.012 | 0.20        | 0.25  | 0.30  |

| Upper Lead Width        | B1 <sup>†</sup> | 0.026 | 0.029   | 0.032 | 0.66        | 0.74  | 0.81  |

| Lower Lead Width        | В               | 0.015 | 0.018   | 0.021 | 0.38        | 0.46  | 0.53  |

| Upper Lead Length       | L               | 0.050 | 0.058   | 0.065 | 1.27        | 1.46  | 1.65  |

| Shoulder Inside Radius  | R1              | 0.003 | 0.005   | 0.010 | 0.08        | 0.13  | 0.25  |

| J-Bend Inside Radius    | R2              | 0.015 | 0.025   | 0.035 | 0.38        | 0.64  | 0.89  |

| Mold Draft Angle Top    | α               | 0     | 5       | 10    | 0           | 5     | 10    |

| Mold Draft Angle Bottom | β               | 0     | 5       | 10    | 0           | 5     | 10    |

Controlling Parameter.

<sup>†</sup> Dimension "B1" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B1."

<sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E." JEDEC equivalent:MO-047 AC

# PIC16C77X

NOTES: