Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | PIC                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 20MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                 |

| Number of I/O              | 33                                                                    |

| Program Memory Size        | 7KB (4K x 14)                                                         |

| Program Memory Type        | OTP                                                                   |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 256 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                             |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | External                                                              |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                       |

| Mounting Type              | Through Hole                                                          |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                              |

| Supplier Device Package    | 40-PDIP                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16c774-p |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16C77X

NOTES:

# FIGURE 8-1: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS: 94h)

| R/W-0  | R/W-0                                                         | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R-0                                                                        | R-0                                       | R-0                                          | R-0          | R-0                                            |                                                                                    |

|--------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------|--------------|------------------------------------------------|------------------------------------------------------------------------------------|

| SMP    | CKE                                                           | D/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Р                                                                          | S                                         | R/W                                          | UA           | BF                                             | R =Readable bit                                                                    |

| bit7   |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |                                           |                                              |              | bit0                                           | W =Writable bit<br>U =Unimplemented bit, read<br>as '0'<br>- n =Value at POR reset |

| oit 7: | <u>SPI Ma</u>                                                 | ample bi<br>ster Mod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <u>e</u>                                                                   | end of data                               | a output time                                |              |                                                |                                                                                    |

|        | 0 = Inpi<br><u>SPI Sla</u>                                    | ut data sa<br><u>ve Mode</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | impled at i                                                                | middle of c                               | lata output ti<br>ed in slave r              | me           |                                                |                                                                                    |

|        | 1= Slev                                                       | rate cor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                            | ed for star                               | dard speed                                   | •            | <hz 1="" and="" i<="" td=""><td>MHz)</td></hz> | MHz)                                                                               |

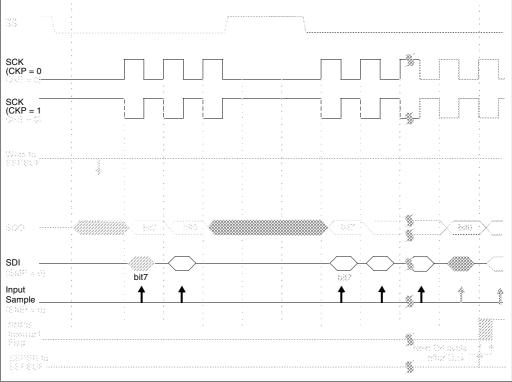

| oit 6: | CKP =                                                         | <u>0</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -                                                                          | ect (Figure                               | 8-6, Figure 8                                | 3-8, and Fig | ure 8-9)                                       |                                                                                    |

|        | 0 = Dat<br><u>CKP =</u><br>1 = Dat                            | a transmi<br><u>1</u><br>a transmi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | tted on fal<br>tted on fal                                                 | ling edge o<br>ling edge o<br>ling edge o | of SCK<br>of SCK                             |              |                                                |                                                                                    |

| oit 5: | 1 = Indi                                                      | cates tha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | t the last b                                                               |                                           | /)<br>ed or transm<br>ed or transm           |              |                                                |                                                                                    |

| oit 4: | 1 = Indi                                                      | de only.<br>cates tha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                            | t has been                                | en the MSS<br>detected las                   |              |                                                | SSPEN is cleared)<br>ET)                                                           |

| oit 3: | 1 = Indi                                                      | de only.<br>cates tha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                            | it has beer                               | en the MSS                                   |              |                                                | SSPEN is cleared)<br>EET)                                                          |

| oit 2: | This bit<br>address                                           | holds the match te holds the holds t | e R/W bit<br>the next                                                      | informatio                                | mode only)<br>on following<br>top bit, or no |              | lress matc                                     | h. This bit is only valid from th                                                  |

|        | 0 = Wri<br><u>In I<sup>2</sup>C n</u><br>1 = Trai<br>0 = Trai | te<br><u>naster mo</u><br>nsmit is ir<br>nsmit is n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n progress<br>ot in progr                                                  | ess.                                      |                                              | KEN will in  | diagta if th                                   | e MSSP is in IDLE mode                                                             |

| oit 1: | <b>UA</b> : Up<br>1 = Indi                                    | date Add<br>cates tha                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ress (10-b<br>t the user                                                   | it I <sup>2</sup> C mod                   | e only)<br>Ipdate the ac                     |              |                                                |                                                                                    |

| oit O: | <u>Receive</u><br>1 = Rec<br>0 = Rec<br><u>Transm</u>         | eive com<br>eive not<br>it (l <sup>2</sup> C mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>d I<sup>2</sup>C mod</u><br>plete, SSI<br>complete,<br><u>ode only)</u> | PBUF is fu<br>SSPBUF i                    |                                              |              |                                                |                                                                                    |

#### 8.1.5 SLAVE MODE

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched the interrupt flag bit SSPIF (PIR1<3>) is set.

While in slave mode the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in sleep mode, the slave can transmit/receive data. When a byte is received the device will wake-up from sleep.

#### 8.1.6 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 0100). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. TRISA<5> must be set. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the

SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. External pull-up/ pull-down resistors may be desirable, depending on the application.

| Note: | When the SPI module is in Slave Mode<br>with $\overline{SS}$ pin control enabled, (SSP-<br>CON<3:0> = 0100) the SPI module will<br>reset if the $\overline{SS}$ pin is set to VDD. |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | If the SPI is used in Slave Mode with $CKE = '1'$ , then $\overline{SS}$ pin control must be enabled.                                                                              |

When the SPI module resets, the bit counter is forced to 0. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

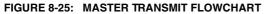

#### 8.2.12 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the receive enable bit, RCEN (SSPCON2<3>).

| Note: | The SSP Module must be in an IDLE        |

|-------|------------------------------------------|

|       | STATE before the RCEN bit is set, or the |

|       | RCEN bit will be disregarded.            |

The baud rate generator begins counting, and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag is set, the SSPIF is set, and the baud rate generator is suspended from counting, holding SCL low. The SSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag is automatically cleared. The user can then send an acknowledge bit at the end of reception, by setting the acknowledge sequence enable bit, AKEN (SSPCON2<4>).

#### 8.2.12.10 BF STATUS FLAG

In receive operation, BF is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when SSPBUF is read.

#### 8.2.12.11 SSPOV STATUS FLAG

In receive operation, SSPOV is set when 8 bits are received into the SSPSR, and the BF flag is already set from a previous reception.

#### 8.2.12.12 WCOL STATUS FLAG

If the user writes the SSPBUF when a receive is already in progress (i.e. SSPSR is still shifting in a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

# 9.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI). The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc. The USART can be configured in the following modes:

- · Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>), and bits TRISC<7:6>, have to be set in order to configure pins RC6/TX/CK and RC7/ RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

## FIGURE 9-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

| R/W-0<br>CSRC | R/W-0<br>TX9                                                | R/W-0<br>TXEN             | R/W-0<br>SYNC | U-0      | R/W-0<br>BRGH | R-1<br>TRMT | R/W-0<br>TX9D | R = Readable bit                                                                      |

|---------------|-------------------------------------------------------------|---------------------------|---------------|----------|---------------|-------------|---------------|---------------------------------------------------------------------------------------|

| bit7          | 173                                                         | TALN                      | 31110         |          | DROIT         |             | bitO          | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| oit 7:        | CSRC: Clo                                                   | ck Source                 | Select bit    |          |               |             |               |                                                                                       |

|               | Asynchrone<br>Don't care                                    | ous mode                  |               |          |               |             |               |                                                                                       |

|               | Synchrono<br>1 = Master<br>0 = Slave n                      | mode (Clo                 | •             |          |               | IG)         |               |                                                                                       |

| oit 6:        | <b>TX9</b> : 9-bit 1<br>1 = Selects<br>0 = Selects          | 9-bit trans               | smission      |          |               |             |               |                                                                                       |

| oit 5:        | <b>TXEN</b> : Tran<br>1 = Transm<br>0 = Transm<br>Note: SRE | it enabled<br>it disabled |               | EN in SY | NC mode.      |             |               |                                                                                       |

| oit 4:        | SYNC: USA<br>1 = Synchro<br>0 = Asynchro                    | onous mod                 | le            |          |               |             |               |                                                                                       |

| oit 3:        | Unimplem                                                    | ented: Rea                | ad as '0'     |          |               |             |               |                                                                                       |

| oit 2:        | BRGH: Hig                                                   | h Baud Ra                 | ate Select b  | it       |               |             |               |                                                                                       |

|               | Asynchrono<br>1 = High sp                                   | beed                      |               |          |               |             |               |                                                                                       |

|               | 0 = Low sp                                                  |                           |               |          |               |             |               |                                                                                       |

|               | Synchrono<br>Unused in t                                    |                           |               |          |               |             |               |                                                                                       |

| oit 1:        | <b>TRMT</b> : Tran<br>1 = TSR er<br>0 = TSR fu              | npty                      | Register St   | atus bit |               |             |               |                                                                                       |

| oit 0:        | <b>TX9D</b> : 9th                                           |                           |               |          |               |             |               |                                                                                       |

| 1) |

|----|

| 1  |

| BAUD<br>RATE<br>(K)                                        | Fosc = 2<br>KBAUD                                     | 0 MHz<br>%<br>ERROR                                 | SPBRG<br>value<br>(decimal)                            | 16 MHz<br>KBAUD                                        | %<br>ERROF                       | SPBRG<br>value<br>decimal                               |                                                                    | %                                                       | b Va                                          | PBRG<br>alue<br>cimal)                           | 7.16 MHz<br>KBAUD E                                                                       | %                                             | SPBRG<br>value<br>decimal)                  |                                               |                                                  |

|------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|----------------------------------|---------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------|-----------------------------------------------|--------------------------------------------------|

| 9.6                                                        | 9.615                                                 | +0.16                                               | 129                                                    | 9.615                                                  | +0.16                            | 103                                                     | 9.615                                                              | 5 +0.                                                   | 16                                            | 64                                               | 9.520                                                                                     | -0.83                                         | 46                                          |                                               |                                                  |

| 19.2                                                       | 19.230                                                | +0.16                                               | 64                                                     | 19.230                                                 | +0.16                            | 51                                                      | 18.93                                                              | 9 -1.3                                                  | 36                                            | 32                                               | 19.454                                                                                    | +1.32                                         | 22                                          |                                               |                                                  |

| 38.4                                                       | 37.878                                                | -1.36                                               | 32                                                     | 38.461                                                 | +0.16                            | 25                                                      | 39.06                                                              | 2 +1                                                    | .7                                            | 15                                               | 37.286                                                                                    | -2.90                                         | 11                                          |                                               |                                                  |

| 57.6                                                       | 56.818                                                | -1.36                                               | 21                                                     | 58.823                                                 | +2.12                            | 16                                                      | 56.81                                                              | 8 -1.3                                                  | 36                                            | 10                                               | 55.930                                                                                    | -2.90                                         | 7                                           |                                               |                                                  |

| 115.2                                                      | 113.636                                               | -1.36                                               | 10                                                     | 111.111                                                | -3.55                            | 8                                                       | 125                                                                | +8.                                                     | 51                                            | 4                                                | 111.860                                                                                   | -2.90                                         | 3                                           |                                               |                                                  |

| 250                                                        | 250                                                   | 0                                                   | 4                                                      | 250                                                    | 0                                | 3                                                       | NA                                                                 | -                                                       |                                               | -                                                | NA                                                                                        | -                                             | -                                           |                                               |                                                  |

| 625                                                        | 625                                                   | 0                                                   | 1                                                      | NA                                                     | -                                | -                                                       | 625                                                                | 0                                                       |                                               | 0                                                | NA                                                                                        | -                                             | -                                           |                                               |                                                  |

| 1250                                                       | 1250                                                  | 0                                                   | 0                                                      | NA                                                     | -                                | -                                                       | NA                                                                 | -                                                       |                                               | -                                                | NA                                                                                        | -                                             | -                                           |                                               |                                                  |

| DALID                                                      | Fosc = 5                                              | 000 1411-                                           |                                                        |                                                        |                                  |                                                         |                                                                    |                                                         |                                               |                                                  |                                                                                           |                                               |                                             |                                               |                                                  |

| BAUD<br>RATE                                               |                                                       | %                                                   | SPBRG<br>value                                         | 4 MHz                                                  | %                                | SPBRG<br>value                                          | 8.579 MH                                                           | %                                                       | SPBRG<br>value                                |                                                  | %                                                                                         | SPBRG<br>value                                |                                             | %                                             | SPBRG<br>value                                   |

|                                                            | KBAUD                                                 | %                                                   | SPBRG<br>value                                         |                                                        |                                  | SPBRG                                                   |                                                                    | %                                                       | value                                         |                                                  | %                                                                                         |                                               |                                             |                                               | value                                            |

| RATE                                                       |                                                       | %                                                   | SPBRG<br>value                                         |                                                        |                                  | SPBRG<br>value<br>(decimal) ł                           |                                                                    | %                                                       | value                                         |                                                  | %<br>UD ERROF                                                                             | value                                         |                                             | %                                             | value                                            |

| RATE<br>(K)                                                | KBAUD                                                 | %<br>ERROR                                          | SPBRG<br>value<br>(decimal)                            | KBAUD                                                  |                                  | SPBRG<br>value<br>(decimal) ł                           | KBAUD                                                              | %<br>ERROR                                              | value<br>(decimal                             | ) KBA                                            | %<br>UD ERROF<br>28 -6.99                                                                 | value<br>(decimal)                            | ) KBAUD                                     | %                                             | value                                            |

| RATE<br>(K)<br>9.6                                         | KBAUD<br>9.6                                          | %<br>ERROR<br>0                                     | SPBRG<br>value<br>(decimal)<br>32                      | KBAUD<br>NA                                            | ERROR<br>-                       | SPBRG<br>value<br>(decimal) F<br>207                    | KBAUD<br>9.727                                                     | %<br>ERROR<br>+1.32                                     | value<br>(decimal<br>22                       | ) KBA                                            | %<br>UD ERROF<br>28 -6.99<br>33 +8.51                                                     | value<br>(decimal)<br>6                       | ) KBAUD                                     | %                                             | value                                            |

| RATE<br>(K)<br>9.6<br>19.2                                 | KBAUD<br>9.6<br>18.645                                | %<br>ERROR<br>0<br>-2.94                            | SPBRG<br>value<br>(decimal)<br>32<br>16                | KBAUD<br>NA<br>1.202                                   | ERROR<br>-<br>+0.17              | SPBRG<br>value<br>(decimal) F<br>-<br>207<br>103        | KBAUD<br>9.727<br>18.643                                           | %<br>ERROR<br>+1.32<br>-2.90                            | value<br>(decimal<br>22<br>11                 | ) KBA<br>8.92<br>20.8                            | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61                                        | value<br>(decimal)<br>6<br>2                  | ) KBAUD<br>NA<br>NA                         | ERROR<br>-<br>-                               | value<br>(decimal)<br>-<br>-                     |

| RATE<br>(K)<br>9.6<br>19.2<br>38.4<br>57.6<br>115.2        | KBAUD<br>9.6<br>18.645<br>39.6<br>52.8<br>105.6       | %<br>ERROR<br>0<br>-2.94<br>+3.12                   | SPBRG<br>value<br>(decimal)<br>32<br>16<br>7           | KBAUD<br>NA<br>1.202<br>2.403<br>9.615<br>19.231       | -<br>+0.17<br>+0.13              | SPBRG<br>value<br>(decimal) H<br>207<br>103<br>25<br>12 | KBAUD<br>9.727<br>18.643<br>37.286<br>55.930<br>111.860            | %<br>ERROR<br>+1.32<br>-2.90<br>-2.90<br>-2.90<br>-2.90 | value<br>(decimal<br>22<br>11<br>5            | ) KBA<br>8.92<br>20.8<br>31.2<br>62.<br>NA       | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61<br>5 +8.51<br>A -                      | value<br>(decimal)<br>6<br>2<br>1             | ) KBAUD<br>NA<br>NA<br>NA<br>NA<br>NA       | * ERROR<br>-<br>-<br>-                        | value<br>(decimal)<br>-<br>-                     |

| RATE<br>(K)<br>9.6<br>19.2<br>38.4<br>57.6<br>115.2<br>250 | KBAUD<br>9.6<br>18.645<br>39.6<br>52.8<br>105.6<br>NA | %<br>ERROR<br>0<br>-2.94<br>+3.12<br>-8.33          | SPBRG<br>value<br>(decimal)<br>32<br>16<br>7<br>5      | KBAUD<br>NA<br>1.202<br>2.403<br>9.615<br>19.231<br>NA | +0.17<br>+0.13<br>+0.16          | SPBRG<br>value<br>(decimal) H<br>207<br>103<br>25<br>12 | KBAUD<br>9.727<br>18.643<br>37.286<br>55.930<br>111.860<br>223.721 | %<br>ERROR<br>+1.32<br>-2.90<br>-2.90<br>-2.90          | value<br>(decimal<br>22<br>11<br>5<br>3       | ) KBA<br>8.92<br>20.8<br>31.2<br>62.<br>NA<br>NA | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61<br>5 +8.51<br>A -<br>A -               | value<br>(decimal)<br>6<br>2<br>1<br>0        | ) KBAUD<br>NA<br>NA<br>NA<br>NA<br>NA<br>NA | * ERROR<br>-<br>-<br>-<br>-                   | value<br>(decimal)<br>-<br>-<br>-<br>-           |

| RATE<br>(K)<br>9.6<br>19.2<br>38.4<br>57.6<br>115.2        | KBAUD<br>9.6<br>18.645<br>39.6<br>52.8<br>105.6       | %<br>ERROR<br>0<br>-2.94<br>+3.12<br>-8.33<br>-8.33 | SPBRG<br>value<br>(decimal)<br>32<br>16<br>7<br>5<br>2 | KBAUD<br>NA<br>1.202<br>2.403<br>9.615<br>19.231       | +0.17<br>+0.13<br>+0.16<br>+0.16 | SPBRG<br>value<br>(decimal) H<br>207<br>103<br>25<br>12 | KBAUD<br>9.727<br>18.643<br>37.286<br>55.930<br>111.860            | %<br>ERROR<br>+1.32<br>-2.90<br>-2.90<br>-2.90<br>-2.90 | value<br>(decimal)<br>22<br>11<br>5<br>3<br>1 | ) KBA<br>8.92<br>20.8<br>31.2<br>62.<br>NA       | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61<br>5 +8.51<br>A -<br>A -<br>A -<br>A - | value<br>R (decimal)<br>6<br>2<br>1<br>0<br>- | ) KBAUD<br>NA<br>NA<br>NA<br>NA<br>NA       | %<br>ERROR<br>-<br>-<br>-<br>-<br>-<br>-<br>- | value<br>(decimal)<br>-<br>-<br>-<br>-<br>-<br>- |

### 9.2 USART Asynchronous Mode

In this mode, the USART uses standard nonreturn-tozero (NRZ) format (one start bit, eight or nine data bits and one stop bit). The most common data format is 8-bits. An on-chip dedicated 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART transmits and receives the LSb first. The USART's transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock either x16 or x64 of the bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

Asynchronous mode is selected by clearing bit SYNC (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- · Asynchronous Transmitter

- Asynchronous Receiver

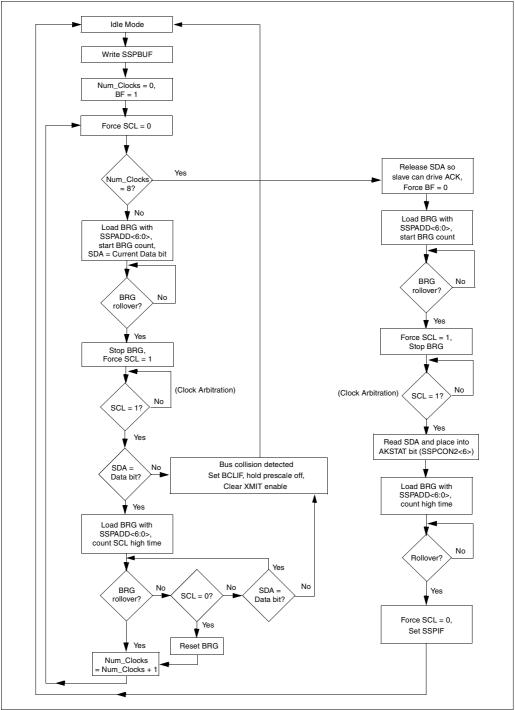

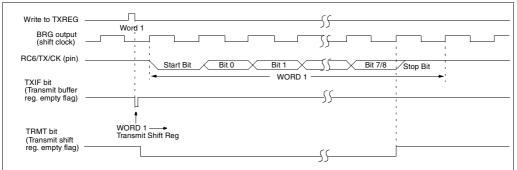

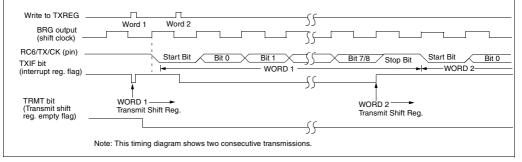

#### 9.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 9-3. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer, TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the STOP bit has been transmitted from the previous load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the TXREG register (if available). Once the TXREG register transfers the data to the TSR register

(occurs in one TcY), the TXREG register is empty and flag bit TXIF (PIR1<4>) is set. This interrupt can be enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicated the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read only bit which is set when the TSR register is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty.

- Note 1: The TSR register is not mapped in data memory so it is not available to the user.

- Note 2: Flag bit TXIF is set when enable bit TXEN is set.

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH. (Section 9.1)

- 2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set transmit bit TX9.

- 5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Load data to the TXREG register (starts transmission).

#### FIGURE 9-4: ASYNCHRONOUS TRANSMISSION

#### FIGURE 9-5: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

#### TABLE 9-6 REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address | Name  | Bit 7                | Bit 6    | Bit 5    | Bit 4 | Bit 3     | Bit 2     | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------------------|----------|----------|-------|-----------|-----------|--------|--------|--------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF     | RCIF     | TXIF  | SSPIF     | CCP1IF    | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h     | RCSTA | SPEN                 | RX9      | SREN     | CREN  | ADDEN     | FERR      | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 19h     | TXREG | USART Tra            | ansmit F | Register |       |           |           |        |        | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE     | RCIE     | TXIE  | SSPIE     | CCP1IE    | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h     | TXSTA | CSRC                 | TX9      | TXEN     | SYNC  | _         | BRGH      | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h     | SPBRG | Baud Rate            | Genera   | tor Regi |       | 0000 0000 | 0000 0000 |        |        |                          |                                 |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

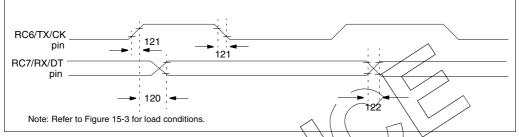

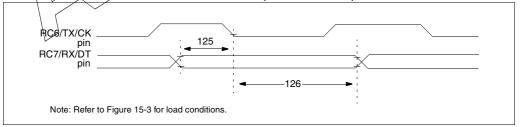

#### 9.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner i.e. transmission and reception do not occur at the same time. When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

#### 9.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 9-3. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcycle), the TXREG is empty and interrupt bit, TXIF (PIR1<4>) is set. The interrupt can be

enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 9.1).

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

| Address | Name  | Bit 7                | Bit 6   | Bit 5    | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|---------|----------|--------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF    | RCIF     | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9     | SREN     | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                 |

| 19h     | TXREG | USART Tr             | ansmit  | Register |        |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE    | RCIE     | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9     | TXEN     | SYNC   |       | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate            | e Gener | ator Reg | jister |       |        |        |        | 0000 0000                | 0000 0000                 |

#### TABLE 9-8 REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for Synchronous Master Transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

#### TABLE 9-10 REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address | Name  | Bit 7                | Bit 6  | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|--------|----------|-------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF   | RCIF     | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9    | SREN     | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                 |

| 19h     | TXREG | USART Tr             | ansmit | Register |       |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE   | RCIE     | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9    | TXEN     | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate            | Gener  | ator Reg | ister |       |        |        |        | 0000 0000                | 0000 0000                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Transmission. Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

#### TABLE 9-11 REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address | Name  | Bit 7                | Bit 6    | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|----------|----------|-------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF     | RCIF     | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9      | SREN     | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                 |

| 1Ah     | RCREG | USART R              | eceive I | Register |       |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE     | RCIE     | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9      | TXEN     | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |