# Microchip Technology - PIC16LC773-I/SO Datasheet

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Dectano                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 22                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | A/D 6x12b                                                                 |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc773-i-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

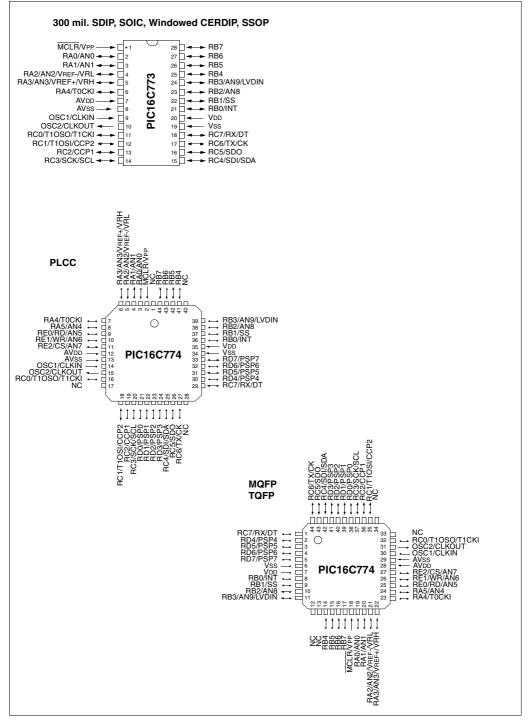

### **Pin Diagrams**

| TABLE 1-2 P | IC16C774 PINOUT DESCRIPTION | (Cont.'d) |

|-------------|-----------------------------|-----------|

|-------------|-----------------------------|-----------|

| Pin Name          | DIP<br>Pin# | PLCC<br>Pin#   | QFP<br>Pin#     | I/O/P<br>Type | Buffer<br>Type                                 | Description                                                                                            |

|-------------------|-------------|----------------|-----------------|---------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------|

|                   |             |                |                 |               |                                                | PORTC is a bi-directional I/O port.                                                                    |

| RC0/T1OSO/T1CKI   | 15          | 16             | 32              | I/O           | ST                                             | RC0 can also be the Timer1 oscillator output or a<br>Timer1 clock input.                               |

| RC1/T1OSI/CCP2    | 16          | 18             | 35              | I/O           | ST                                             | RC1 can also be the Timer1 oscillator input or<br>Capture2 input/Compare2 output/PWM2 output.          |

| RC2/CCP1          | 17          | 19             | 36              | I/O           | ST                                             | RC2 can also be the Capture1 input/Compare1<br>output/PWM1 output.                                     |

| RC3/SCK/SCL       | 18          | 20             | 37              | I/O           | ST                                             | RC3 can also be the synchronous serial clock input/<br>output for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA       | 23          | 25             | 42              | I/O           | ST                                             | RC4 can also be the SPI Data In (SPI mode) or data $I/O$ ( $I^{2}C$ mode).                             |

| RC5/SDO           | 24          | 26             | 43              | I/O           | ST                                             | RC5 can also be the SPI Data Out (SPI mode).                                                           |

| RC6/TX/CK         | 25          | 27             | 44              | I/O           | ST                                             | RC6 can also be the USART Asynchronous<br>Transmit or Synchronous Clock.                               |

| RC7/RX/DT         | 26          | 29             | 1               | I/O           | ST                                             | RC7 can also be the USART Asynchronous Receive<br>or Synchronous Data.                                 |

|                   |             |                |                 |               |                                                | PORTD is a bi-directional I/O port or parallel slave port                                              |

|                   |             |                |                 |               | (2)                                            | when interfacing to a microprocessor bus.                                                              |

| RD0/PSP0          | 19          | 21             | 38              | I/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD1/PSP1          | 20          | 22             | 39              | I/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD2/PSP2          | 21          | 23             | 40              | I/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD3/PSP3          | 22          | 24             | 41              | I/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD4/PSP4          | 27          | 30             | 2               | I/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD5/PSP5          | 28          | 31             | 3               | I/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD6/PSP6          | 29          | 32             | 4               | I/O           | ST/TTL <sup>(3)</sup><br>ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD7/PSP7          | 30          | 33             | 5               | I/O           | SI/IIL®                                        |                                                                                                        |

|                   |             |                |                 |               |                                                | PORTE is a bi-directional I/O port.                                                                    |

| RE0/RD/AN5        | 8           | 9              | 25              | I/O           | ST/TTL <sup>(3)</sup>                          | RE0 can also be read control for the parallel slave port, or analog input5.                            |

| RE1/WR/AN6        | 9           | 10             | 26              | I/O           | ST/TTL <sup>(3)</sup>                          | RE1 can also be write control for the parallel slave port, or analog input6.                           |

| RE2/CS/AN7        | 10          | 11             | 27              | I/O           | ST/TTL <sup>(3)</sup>                          | RE2 can also be select control for the parallel slave<br>port, or analog input7.                       |

| AVss              | 12          | 13             | 29              | Р             |                                                | Ground reference for A/D converter                                                                     |

| AVDD              | 11          | 12             | 28              | Р             |                                                | Positive supply for A/D converter                                                                      |

| Vss               | 31          | 34             | 6               | P             | _                                              | Ground reference for logic and I/O pins.                                                               |

| VDD               | 32          | 35             | 7               | P             | _                                              | Positive supply for logic and I/O pins.                                                                |

| NC                | -           | 1,17,28,<br>40 | 12,13,<br>33,34 |               | -                                              | These pins are not internally connected. These pins should be left unconnected.                        |

| Legend: I = input | O = outp    | ut             | I/C             | ) = input     | /output                                        | P = power                                                                                              |

| 0                 | — = Not     |                |                 | L = TTL       |                                                | ST = Schmitt Trigger input                                                                             |

Note 1: This buffer is a Schmitt Trigger input when configured for the multiplexed function.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

#### 2.2.2.6 PIE2 REGISTER

This register contains the individual enable bits for the CCP2, SSP bus collision, and low voltage detect interrupts.

| FIGURE 2-8: | PIE2 REGISTER | (ADDRESS 8Dh) |

|-------------|---------------|---------------|

|-------------|---------------|---------------|

| R/W-0    | U-0                                           | U-0          | U-0         | R/W-0      | U-0      | U-0 | R/W-0  |                                                                                                                      |

|----------|-----------------------------------------------|--------------|-------------|------------|----------|-----|--------|----------------------------------------------------------------------------------------------------------------------|

| LVDIE    | —                                             | —            |             | BCLIE      | —        |     | CCP2IE | R = Readable bit                                                                                                     |

| bit7     |                                               |              |             |            |          |     | bit0   | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |

| bit 7    | <b>LVDIE</b> : Lo<br>1 = LVD Ir<br>0 = LVD Ir | nterrupt is  | enabled     | terrupt En | able bit |     |        |                                                                                                                      |

| bit 6-4: | Unimplen                                      | nented: R    | lead as '0' |            |          |     |        |                                                                                                                      |

| bit 3:   | <b>BCLIE</b> : Bu<br>1 = Bus C<br>0 = Bus C   | ollision int | errupt is e | enabled    | bit      |     |        |                                                                                                                      |

| bit 2-1: | Unimplen                                      | nented: R    | lead as '0' |            |          |     |        |                                                                                                                      |

| bit 0:   | <b>CCP2IE</b> : 0<br>1 = Enable<br>0 = Disabl | es the CC    | P2 interru  | pt         |          |     |        |                                                                                                                      |

# 2.3 PCL and PCLATH

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly readable or writable. All updates to the PCH register go through the PCLATH register.

#### 2.3.1 STACK

The stack allows a combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Midrange devices have an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

## 2.4 Program Memory Paging

PIC16C77X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

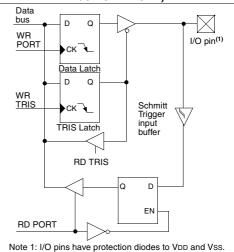

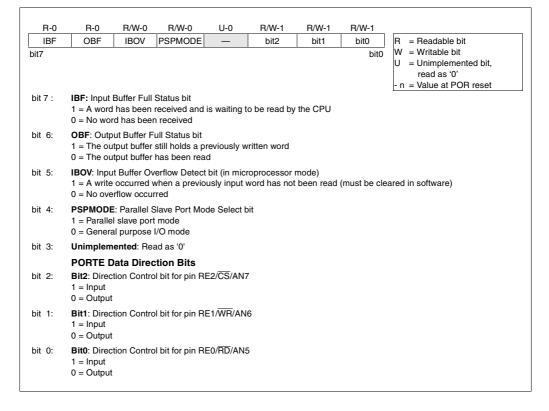

## 3.5 PORTE and TRISE Register

This section is applicable to the 40/44-pin devices only.

PORTE has three pins RE0/RD/AN5, RE1/ $\overline{WR}$ /AN6 and RE2/ $\overline{CS}$ /AN7, which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

I/O PORTE becomes control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs). Ensure ADCON1 is configured for digital I/O. In this mode the input buffers are TTL.

Figure 3-12 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected as an analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

Note: On a Power-on Reset these pins are configured as analog inputs.

#### FIGURE 3-12: TRISE REGISTER (ADDRESS 89h)

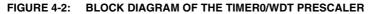

#### 4.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

Note: To avoid an unintended device RESET, a specific instruction sequence (shown in the PICmicro™ Mid-Range Reference Manual, DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

### 4.3 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut off during SLEEP.

# TABLE 4-1 REGISTERS ASSOCIATED WITH TIMER0

| Address               | Name       | Bit 7  | Bit 6      | Bit 5   | Bit 4                         | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------------------|------------|--------|------------|---------|-------------------------------|-------|-------|-------|-------|--------------------------|---------------------------|

| 01h,101h              | TMR0       | Timer0 | module's r | egister |                               |       |       |       |       | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE    | PEIE       | TOIE    | INTE                          | RBIE  | TOIF  | INTF  | RBIF  | 0000 000x                | 0000 000u                 |

| 81h,181h              | OPTION_REG | RBPU   | INTEDG     | TOCS    | TOSE                          | PSA   | PS2   | PS1   | PS0   | 1111 1111                | 1111 1111                 |

| 85h                   | TRISA      | _      | _          | PORTA   | PORTA Data Direction Register |       |       |       |       | 11 1111                  | 11 1111                   |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

#### 5.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers; TMR1H and TMR1L)

- Readable and writable (Both registers)

- · Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- · Reset from CCP module trigger

Timer1 has a control register, shown in Figure 5-1. Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Figure 5-3 is a simplified block diagram of the Timer1 module.

Additional information on timer modules is available in the PICmicro™ Mid-Range Reference Manual, (DS33023).

#### 5.1 **Timer1 Operation**

Timer1 can operate in one of these modes:

- · As a timer

- · As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the clock select bit. TMR1CS (T1CON<1>).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored.

Timer1 also has an internal "reset input". This reset can be generated by the CCP module (Section 7.0).

#### T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h) U-0 U-0 R/W-0 R/W-0 B/W-0 R/W-0 **B/W-0** R/W-0 T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON R = Readable bit W = Writable bit bit7 bit0 = Unimplemented bit, U read as '0' n = Value at POR reset bit 7-6: Unimplemented: Read as '0' bit 5-4: T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits 11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value 00 = 1:1 Prescale value T1OSCEN: Timer1 Oscillator Enable Control bit hit 3 1 = Oscillator is enabled 0 = Oscillator is shut off Note: The oscillator inverter and feedback resistor are turned off to eliminate power drain T1SYNC: Timer1 External Clock Input Synchronization Control bit bit 2: TMR1CS = 11 = Do not synchronize external clock input 0 = Synchronize external clock input TMR1CS = 0This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0. TMR1CS: Timer1 Clock Source Select bit bit 1: 1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge) 0 = Internal clock (Fosc/4)

# FIGURE 5-1:

- 1 = Enables Timer1

- 0 = Stops Timer1

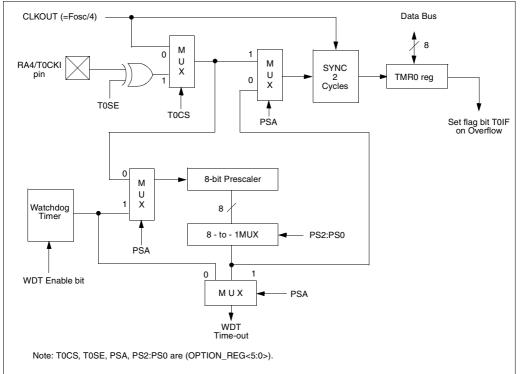

#### 8.2.2 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the START condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all 0's with R/W = 0

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> is set). Following a start-bit detect, 8-bits are shifted into SSPSR and the address is compared against SSPADD, and is also compared to the general call address, fixed in hardware. If the general call address matches, the SSPSR is transfered to the SSPBUF, the BF flag is set (eighth bit), and on the falling edge of the ninth bit ( $\overline{ACK}$  bit) the SSPIF flag is set.

When the interrupt is serviced. The source for the interrupt can be checked by reading the contents of the SSPBUF to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match, and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when GCEN is set while the slave is configured in 10-bit address mode, then the second half of the address is not necessary, the UA bit will not be set, and the slave will begin receiving data after the acknowledge (Figure 8-16).

FIGURE 8-16: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE (7 OR 10-BIT MODE)

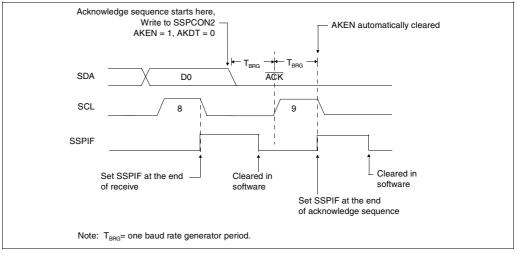

#### 8.2.13 ACKNOWLEDGE SEQUENCE TIMING

An acknowledge sequence is enabled by setting the acknowledge sequence enable bit, AKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the acknowledge data bit is presented on the SDA pin. If the user wishes to generate an acknowledge, then the AKDT bit should be cleared. If not, the user should set the AKDT bit before starting an acknowledge sequence. The baud rate generator then counts for one rollover period ( $T_{BRG}$ ), and the SCL pin is de-asserted (pulled high). When the SCL pin is sampled high (clock arbitration), the baud

rate generator counts for  $T_{BRG}$ . The SCL pin is then pulled low. Following this, the AKEN bit is automatically cleared, the baud rate generator is turned off, and the SSP module then goes into IDLE mode. (Figure 8-29)

#### 8.2.13.13 WCOL STATUS FLAG

If the user writes the SSPBUF when an acknowledege sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 8-29: ACKNOWLEDGE SEQUENCE WAVEFORM

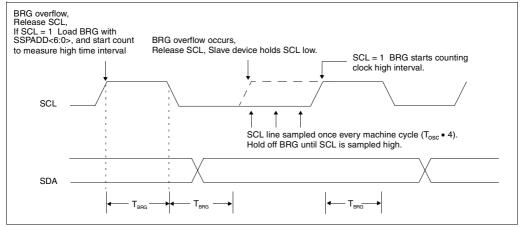

#### 8.2.15 CLOCK ARBITRATION

Clock arbitration occurs when the master, during any receive, transmit, or repeated start/stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the baud rate generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 8-33).

#### 8.2.16 SLEEP OPERATION

While in sleep mode, the I<sup>2</sup>C module can receive addresses or data, and when an address match or complete byte transfer occurs wake the processor from sleep (if the SSP interrupt is enabled).

#### 8.2.17 EFFECTS OF A RESET

A reset disables the SSP module and terminates the current transfer.

#### FIGURE 8-33: CLOCK ARBITRATION TIMING IN MASTER TRANSMIT MODE

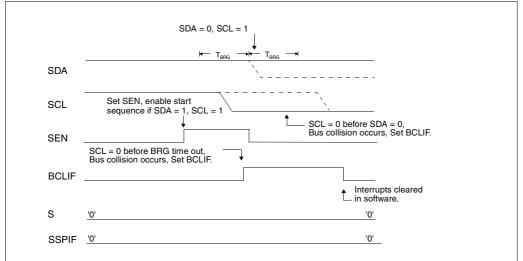

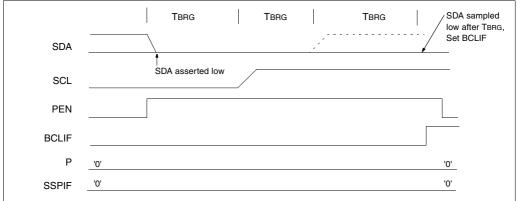

# FIGURE 8-37: BRG RESET DUE TO SDA COLLISION DURING START CONDITION

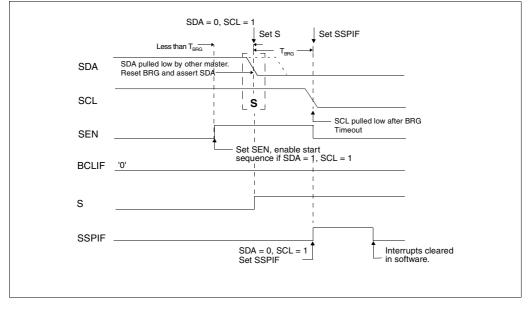

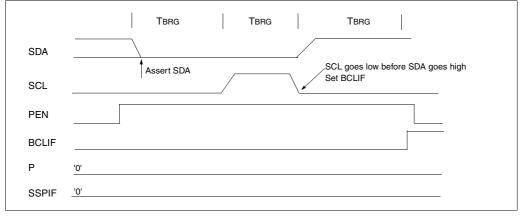

#### 8.2.18.17 BUS COLLISION DURING A STOP CONDITION

Bus collision occurs during a STOP condition if:

- After the SDA pin has been de-asserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is de-asserted, SCL is sampled low before SDA goes high.

The STOP condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allow to float. When the pin is sampled high (clock arbitration), the baud rate generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0'. If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 8-40).

# FIGURE 8-40: BUS COLLISION DURING A STOP CONDITION (CASE 1)

# FIGURE 8-41: BUS COLLISION DURING A STOP CONDITION (CASE 2)

The value that is in the ADRESH and ADRESL registers are not modified for a Power-on Reset. The ADRESH and ADRESL registers will contain unknown data after a Power-on Reset.

After the A/D module has been configured as desired, the selected channel must be acquired before the conversion is started. The analog input channels must have their corresponding TRIS bits selected as an input. To determine acquisition time, see Section 11.6. After this acquisition time has elapsed the A/D conversion can be started. The following steps should be followed for doing an A/D conversion:

# 11.2 Configuring the A/D Module

### 11.3 Configuring Analog Port Pins

The ADCON1 and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The A/D operation is independent of the state of the CHS3:CHS0 bits and the TRIS bits.

- Note 1: When reading the PORTA or PORTE register, all pins configured as analog input channels will read as cleared (a low level). When reading the PORTB register, all pins configured as analog input channels will read as set (a high level). Pins configured as digital inputs, will convert an analog input. Analog levels on a digitally configured input will not affect the conversion accuracy.

- Note 2: Analog levels on any pin that is defined as a digital input (including the ANx pins), may cause the input buffer to consume current that is out of the devices specification.

# 11.3.1 CONFIGURING THE REFERENCE VOLTAGES

The VCFG bits in the ADCON1 register configure the A/D module reference inputs. The reference high input can come from an internal reference (VRH) or (VRL), an external reference (VREF+), or AVDD. The low reference input can come from an internal reference (VRL), an external reference (VREF-), or AVSS. If an external reference is chosen for the reference high or reference low inputs, the port pin that multiplexes the incoming external references is configured as an analog input, regardless of the values contained in the A/D port configuration bits (PCFG3:PCFG0).

After the A/D module has been configured as desired. and the analog input channels have their corresponding TRIS bits selected for port inputs, the selected channel must be acquired before conversion is started. The A/D conversion cycle can be initiated by setting the GO/DONE bit. The A/D conversion begins, and lasts for 13TAD. The following steps should be followed for performing an A/D conversion:

- 1. Configure the A/D module

- Configure analog pins / voltage reference / and digital I/O (ADCON1)

- Select A/D input channel (ADCON0)

- Select A/D conversion clock (ADCON0)

- Turn on A/D module (ADCON0)

- 2. Configure A/D interrupt (if required)

- Clear ADIF bit

- Set ADIE bit

- Set PEIE bit

- · Set GIE bit

- 3. Wait the required acquisition time (3TAD)

- 4. Start conversion

- Set GO/DONE bit (ADCON0)

- 5. Wait 13TAD until A/D conversion is complete, by either:

- Polling for the GO/DONE bit to be cleared OR

- Waiting for the A/D interrupt

- 6. Read A/D Result registers (ADRESH and ADRESL), clear ADIF if required.

- 7. For next conversion, go to step 1, step 2 or step 3 as required.

Clearing the GO/DONE bit during a conversion will abort the current conversion. The ADRESH and ADRESL registers **WILL** be updated with the partially completed A/D conversion value. That is, the ADRESH and ADRESL registers **WILL** contain the value of the current incomplete conversion.

Note: Do not set the ADON bit and the GO/DONE bit in the same instruction. Doing so will cause the GO/DONE bit to be automatically cleared.

# 15.5 AC Characteristics: PIC16C77X (Commercial, Industrial)

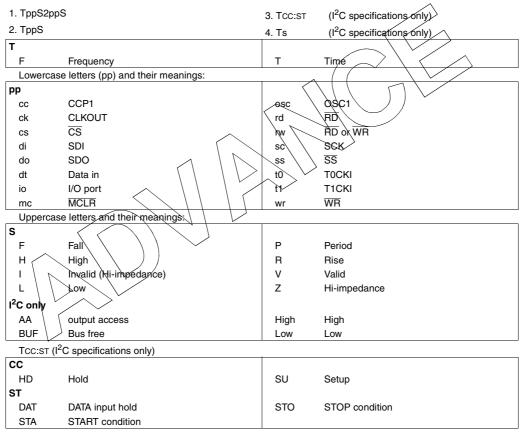

# 15.5.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

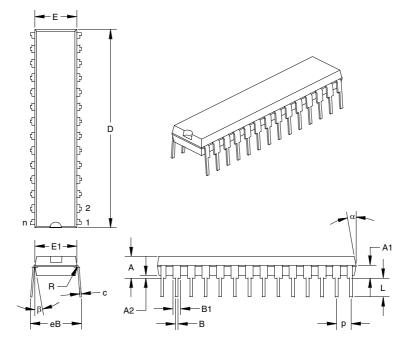

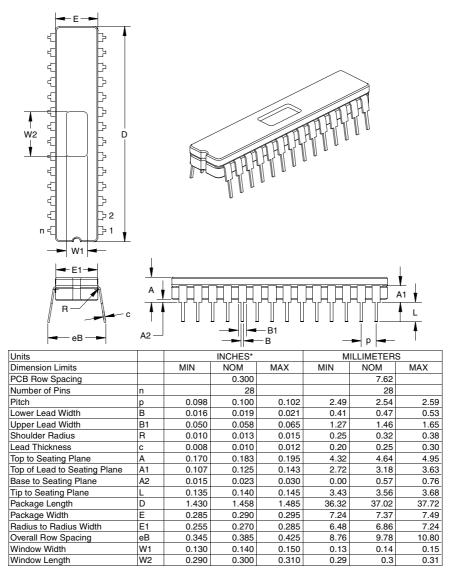

### 17.2 K04-070 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                        |                 |       | INCHES* |       | М     | ILLIMETER | S     |

|------------------------------|-----------------|-------|---------|-------|-------|-----------|-------|

| Dimension Limits             |                 | MIN   | NOM     | MAX   | MIN   | NOM       | MAX   |

| PCB Row Spacing              |                 |       | 0.300   |       |       | 7.62      |       |

| Number of Pins               | n               |       | 28      |       |       | 28        |       |

| Pitch                        | р               |       | 0.100   |       |       | 2.54      |       |

| Lower Lead Width             | В               | 0.016 | 0.019   | 0.022 | 0.41  | 0.48      | 0.56  |

| Upper Lead Width             | B1 <sup>†</sup> | 0.040 | 0.053   | 0.065 | 1.02  | 1.33      | 1.65  |

| Shoulder Radius              | R               | 0.000 | 0.005   | 0.010 | 0.00  | 0.13      | 0.25  |

| Lead Thickness               | с               | 0.008 | 0.010   | 0.012 | 0.20  | 0.25      | 0.30  |

| Top to Seating Plane         | A               | 0.140 | 0.150   | 0.160 | 3.56  | 3.81      | 4.06  |

| Top of Lead to Seating Plane | A1              | 0.070 | 0.090   | 0.110 | 1.78  | 2.29      | 2.79  |

| Base to Seating Plane        | A2              | 0.015 | 0.020   | 0.025 | 0.38  | 0.51      | 0.64  |

| Tip to Seating Plane         | L               | 0.125 | 0.130   | 0.135 | 3.18  | 3.30      | 3.43  |

| Package Length               | D‡              | 1.345 | 1.365   | 1.385 | 34.16 | 34.67     | 35.18 |

| Molded Package Width         | E‡              | 0.280 | 0.288   | 0.295 | 7.11  | 7.30      | 7.49  |

| Radius to Radius Width       | E1              | 0.270 | 0.283   | 0.295 | 6.86  | 7.18      | 7.49  |

| Overall Row Spacing          | eB              | 0.320 | 0.350   | 0.380 | 8.13  | 8.89      | 9.65  |

| Mold Draft Angle Top         | α               | 5     | 10      | 15    | 5     | 10        | 15    |

| Mold Draft Angle Bottom      | β               | 5     | 10      | 15    | 5     | 10        | 15    |

\* Controlling Parameter.

<sup>†</sup> Dimension "B1" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B1."

<sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."

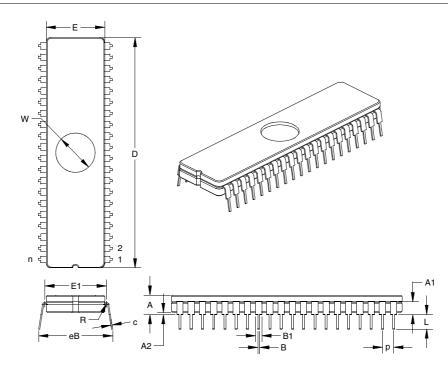

### 17.3 K04-080 28-Lead Ceramic Dual In-line with Window (JW) – 300 mil

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

\* Controlling Parameter.

# 17.7 K04-014 40-Lead Ceramic Dual In-line with Window (JW) – 600 mil

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                        |    |       | INCHES* |       | N     | <b>IILLIMETER</b> | S     |

|------------------------------|----|-------|---------|-------|-------|-------------------|-------|

| Dimension Limits             |    | MIN   | NOM     | MAX   | MIN   | NOM               | MAX   |

| PCB Row Spacing              |    |       | 0.600   |       |       | 15.24             |       |

| Number of Pins               | n  |       | 40      |       |       | 40                |       |

| Pitch                        | р  | 0.098 | 0.100   | 0.102 | 2.49  | 2.54              | 2.59  |

| Lower Lead Width             | В  | 0.016 | 0.020   | 0.023 | 0.41  | 0.50              | 0.58  |

| Upper Lead Width             | B1 | 0.050 | 0.053   | 0.055 | 1.27  | 1.33              | 1.40  |

| Shoulder Radius              | R  | 0.000 | 0.005   | 0.010 | 0.00  | 0.13              | 0.25  |

| Lead Thickness               | с  | 0.008 | 0.011   | 0.014 | 0.20  | 0.28              | 0.36  |

| Top to Seating Plane         | А  | 0.190 | 0.205   | 0.220 | 4.83  | 5.21              | 5.59  |

| Top of Lead to Seating Plane | A1 | 0.117 | 0.135   | 0.153 | 2.97  | 3.43              | 3.89  |

| Base to Seating Plane        | A2 | 0.030 | 0.045   | 0.060 | 0.00  | 1.14              | 1.52  |

| Tip to Seating Plane         | L  | 0.135 | 0.140   | 0.145 | 3.43  | 3.56              | 3.68  |

| Package Length               | D  | 2.040 | 2.050   | 2.060 | 51.82 | 52.07             | 52.32 |

| Package Width                | E  | 0.514 | 0.520   | 0.526 | 13.06 | 13.21             | 13.36 |

| Radius to Radius Width       | E1 | 0.560 | 0.580   | 0.600 | 14.22 | 14.73             | 15.24 |

| Overall Row Spacing          | eB | 0.610 | 0.660   | 0.710 | 15.49 | 16.76             | 18.03 |

| Window Diameter              | W  | 0.340 | 0.350   | 0.360 | 8.64  | 8.89              | 9.14  |

\* Controlling Parameter.

# **PIC16C77X**

| S                                                |     |

|--------------------------------------------------|-----|

| SAE                                              |     |

| SCK                                              |     |

| SCL                                              |     |

| SDA                                              |     |

| SDA                                              |     |

| SDO                                              |     |

| SEEVAL® Evaluation and Programming System        |     |

| Serial Clock, SCK                                |     |

| Serial Clock, SCL                                |     |

| Serial Data Address, SDA                         |     |

| Serial Data Address, SDA                         |     |

| Serial Data III, SDI                             |     |

|                                                  |     |

| Slave Select Synchronization<br>Slave Select. SS |     |

|                                                  |     |

| SLEEP                                            |     |

| SMP                                              |     |

| Software Simulator (MPLAB-SIM)                   |     |

| SPBRG Register                                   |     |

| SPE                                              |     |

| Special Features of the CPU                      |     |

| Special Function Registers                       |     |

| PIC16C73                                         |     |

| PIC16C73A                                        |     |

| PIC16C74                                         |     |

| PIC16C74A                                        |     |

| PIC16C76                                         |     |

| PIC16C77                                         |     |

| Speed, Operating<br>SPI                          |     |

| Master Mode                                      |     |

| Serial Clock                                     |     |

| Serial Data In                                   |     |

| Serial Data Out                                  |     |

| Serial Peripheral Interface (SPI)                |     |

| Slave Select                                     |     |

| SPI clock                                        |     |

| SPI Mode                                         |     |

| SPI Clock Edge Select, CKE                       |     |

| SPI Data Input Sample Phase Select, SMP          |     |

| SPI Master/Slave Connection                      |     |

| Master/Slave Connection                          |     |

| Slave Mode                                       |     |

| Slave Select Synchronization                     |     |

| Slave Synch Timnig                               |     |

| SS                                               |     |

| SSP                                              |     |

| Block Diagram (SPI Mode)                         |     |

| Enable (SSPIE Bit)                               |     |

| Flag (SSPIE Bit)                                 |     |

| RA5/SS/AN4 Pin                                   |     |

|                                                  |     |

| RC3/SCK/SCL Pin                                  |     |

| RC4/SDI/SDA Pin                                  |     |

| RC5/SDO Pin                                      |     |

| SPI Mode                                         |     |

| SSPADD                                           |     |

| SSPBUF                                           |     |

| SSPCON1                                          |     |

| SSPCON2                                          |     |

| SSPSR                                            |     |

| SSPSTAT                                          |     |

| TMR2 Output for Clock Shift                      | 45, |

| SSP I <sup>2</sup> C                             |     |

| SSP I <sup>2</sup> C Operation                   |     |

|                                                  |     |

| SSP Module                                   |

|----------------------------------------------|

| SPI Master Mode 59                           |

| SPI Master./Slave Connection 58              |

| SPI Slave Mode 60                            |

| SSPCON1 Register 63                          |

| SSP Overflow Detect bit, SSPOV 64            |

| SSPADD Register 14                           |

| SSPBUF 15, 64                                |

| SSPBUF Register 13                           |

| SSPCON Register 13                           |

| SSPCON1                                      |

| SSPCON2                                      |

| SSPEN                                        |

| SSPIF                                        |

| SSPM3:SSPM0                                  |

| SSPOV 55, 64, 82                             |

| SSPSTAT                                      |

| SSPSTAT Register 14                          |

| Stack                                        |

| Start bit (S)                                |

| Start Condition Enabled bit, SAE 56          |

| STATUS Register 16, 138                      |

| C Bit                                        |

| DC Bit                                       |

| IRP Bit                                      |

| PD Bit                                       |

| <u>RP</u> 1:RP0 Bits 16                      |

| TO Bit                                       |

| Z Bit                                        |

| Stop bit (P)                                 |

| Stop Condition Enable bit                    |

| Synchronous Serial Port 53                   |

| Synchronous Serial Port Enable bit, SSPEN 55 |

| Synchronous Serial Port Mode Select bits,    |

| SSPM3:SSPM0                                  |

|                                              |

# т

| T1CON                                  | 15      |

|----------------------------------------|---------|

| T1CON Register                         | 15, 41  |

| T1CKPS1:T1CKPS0 Bits                   | 41      |

| T1OSCEN Bit                            | 41      |

| T1SYNC Bit                             | 41      |

| TMR1CS Bit                             | 41      |

| TMR1ON Bit                             | 41      |

| T2CON Register                         | 15, 45  |

| T2CKPS1:T2CKPS0 Bits                   | 45      |

| TMR2ON Bit                             | 45      |

| TOUTPS3:TOUTPS0 Bits                   | 45      |

| Timer0                                 | 39      |

| Block Diagram                          | 39      |

| Clock Source Edge Select (T0SE Bit)    | 17, 39  |

| Clock Source Select (T0CS Bit)         | 17, 39  |

| Overflow Enable (T0IE Bit)             | 18      |

| Overflow Flag (T0IF Bit)               | 18, 138 |

| Overflow Interrupt                     | 40, 138 |

| RA4/T0CKI Pin, External Clock          |         |

| Timer1                                 | 41      |

| Block Diagram                          | 42      |

| Capacitor Selection                    | 43      |

| Clock Source Select (TMR1CS Bit)       | 41      |

| External Clock Input Sync (T1SYNC Bit) | 41      |

| Module On/Off (TMR1ON Bit)             |         |

| Oscillator                             | 41, 43  |

| Oscillator Enable (T1OSCEN Bit)        | 41      |

| Overflow Enable (TMR1IE Bit)           | 19      |

| Overflow Flag (TMR1IF Bit)             |         |

| ,                                      |         |

# **ON-LINE SUPPORT**

Microchip provides on-line support on the Microchip World Wide Web (WWW) site.

The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

#### Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

#### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

#### ftp://ftp.microchip.com

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- Latest Microchip Press Releases

- Technical Support Section with Frequently Asked

Questions

- Design Tips

- Device Errata

- Job Postings

- Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

- Conferences for products, Development Systems, technical information and more

- · Listing of seminars and events