Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                             |

| Data Converters            | A/D 6x12b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | 28-SOIC                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc773-so |

NOTES:

#### 8.2.6 MULTI-MASTER OPERATION

In multi-master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the MSSP module is disabled. Control of the  $\rm I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored, for abitration, to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- · A Start Condition

- A Repeated Start Condition

- · An Acknowledge Condition

#### 8.2.7 I<sup>2</sup>C MASTER OPERATION SUPPORT

Master Mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON and by setting the SSPEN bit. Once master mode is enabled, the user has six options.

- Assert a start condition on SDA and SCL.

- Assert a Repeated Start condition on SDA and SCL.

- Write to the SSPBUF register initiating transmission of data/address.

- Generate a stop condition on SDA and SCL.

- Configure the I2C port to receive data.

- Generate an Acknowledge condition at the end of a received byte of data.

Note: The MSSP Module, when configured in I<sup>2</sup>C Master Mode, does not allow queueing of events. For instance: The user is not allowed to initiate a start condition, and immediately write the SSPBUF register to initiate transmission before the START condition is complete. In this case the SSPBUF will not be written to, and the WCOL bit will be set, indicating that a write

to the SSPBUF did not occur.

#### 8.2.7.4 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write ( $R\overline{W}$ ) bit. In this case, the  $R\overline{W}$  bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

In Master receive mode the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case the  $R/\overline{W}$  bit will be logic '1'. Thus the first byte transmitted is a 7-bit slave address followed by a '1' to indicate receive bit. Serial data is received via SDA while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions indicate the beginning and end of transmission.

The baud rate generator used for SPI mode operation is now used to set the SCL clock frequency for either 100 kHz, 400 kHz, or 1 MHz I<sup>2</sup>C operation. The baud rate generator reload value is contained in the lower 7 bits of the SSPADD register. The baud rate generator will automatically begin counting on a write to the SSPBUF. Once the given operation is complete (i.e. transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state

A typical transmit sequence would go as follows:

- The user generates a Start Condition by setting the START enable bit (SEN) in SSPCON2.

- SSPIF is set. The module will wait the required start time before any other operation takes place.

- The user loads the SSPBUF with address to transmit.

- Address is shifted out the SDA pin until all 8 bits are transmitted.

- The MSSP Module shifts in the ACK bit from the slave device, and writes its value into the SSPCON2 register (SSPCON2<6>).

- f) The module generates an interrupt at the end of the ninth clock cycle by setting SSPIF.

- The user loads the SSPBUF with eight bits of data.

- DATA is shifted out the SDA pin until all 8 bits are transmitted.

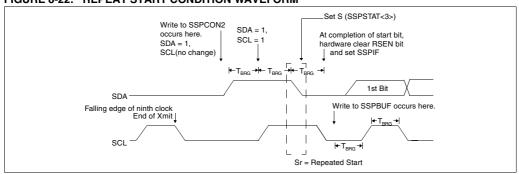

## 8.2.10 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPCON2<1>) is programmed high and the I<sup>2</sup>C module is in the idle state. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the baud rate generator is loaded with the contents of SSPADD<6:0>, and begins counting. The SDA pin is released (brought high) for one baud rate generator count (T<sub>BRG</sub>). When the baud rate generator times out, if SDA is sampled high, the SCL pin will be de-asserted (brought high). When SCL is sampled high the baud rate generator is re-loaded with the contents of SSPADD<6:0> and begins counting. SDA and SCL must be sampled high for one T<sub>BRG</sub>. This action is then followed by assertion of the SDA pin (SDA is low) for one TBRG while SCL is high. Following this, the RSEN bit in the SSPCON2 register will be automatically cleared, and the baud rate generator is not reloaded, leaving the SDA pin held low. As soon as a start condition is detected on the SDA and SCL pins, the S bit (SSPSTAT<3>) will be set. The SSPIF bit will not be set until the baud rate generator has timed-out.

Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

**Note 2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low to high.

- SCL goes low before SDA is asserted low. This

may indicate that another master is attempting

to transmit a data "1".

Immediately following the SSPIF bit getting set, the user may write the SSPBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional eight bits of address (10-bit mode) or eight bits of data (7-bit mode).

#### 8.2.10.6 WCOL STATUS FLAG

If the user writes the SSPBUF when a Repeated Start sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing of the lower 5 bits of SSPCON2 is disabled until the Repeated Start condition is complete.

#### FIGURE 8-22: REPEAT START CONDITION WAVEFORM

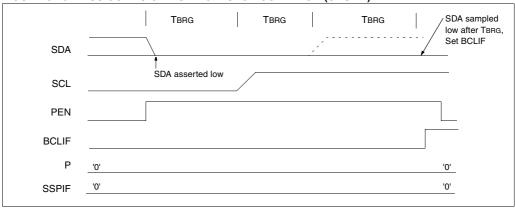

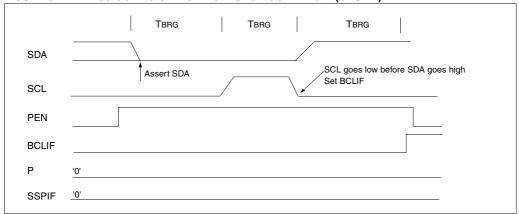

## 8.2.18.17 BUS COLLISION DURING A STOP CONDITION

Bus collision occurs during a STOP condition if:

- After the SDA pin has been de-asserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is de-asserted, SCL is sampled low before SDA goes high.

The STOP condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allow to float. When the pin is sampled high (clock arbitration), the baud rate generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0'. If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 8-40).

FIGURE 8-40: BUS COLLISION DURING A STOP CONDITION (CASE 1)

FIGURE 8-41: BUS COLLISION DURING A STOP CONDITION (CASE 2)

# 9.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI). The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc.

The USART can be configured in the following modes:

- · Asynchronous (full duplex)

- · Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>), and bits TRISC<7:6>, have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

#### FIGURE 9-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

| R/W-0        | R/W-0                                   | R/W-0        | R/W-0        | U-0        | R/W-0               | R-1  | R/W-0        |                                                          |

|--------------|-----------------------------------------|--------------|--------------|------------|---------------------|------|--------------|----------------------------------------------------------|

| CSRC<br>bit7 | TX9                                     | TXEN         | SYNC         |            | BRGH                | TRMT | TX9D<br>bit0 | R = Readable bit W = Writable bit U = Unimplemented bit, |

|              |                                         |              |              |            |                     |      |              | read as '0'                                              |

| bit 7:       | CSRC: Clo                               | ok Couron    | Coloot bit   |            |                     |      |              | - n =Value at POR reset                                  |

| DIL 7.       |                                         |              | Select bit   |            |                     |      |              |                                                          |

|              | Asynchron<br>Don't care                 |              |              |            |                     |      |              |                                                          |

|              | Synchrono                               |              |              |            |                     |      |              |                                                          |

|              | 1 = Master<br>0 = Slave r               |              |              |            | illy from BR<br>ce) | (G)  |              |                                                          |

| bit 6:       | <b>TX9</b> : 9-bit                      |              |              |            |                     |      |              |                                                          |

|              | 1 = Selects<br>0 = Selects              |              |              |            |                     |      |              |                                                          |

| bit 5:       | TXEN: Trai                              |              | ole bit      |            |                     |      |              |                                                          |

|              | 1 = Transm<br>0 = Transm                |              |              |            |                     |      |              |                                                          |

|              | Note: SRE                               |              |              | (EN in SY  | NC mode.            |      |              |                                                          |

| bit 4:       | SYNC: US                                |              |              |            |                     |      |              |                                                          |

|              | 1 = Synchr<br>0 = Asynch                |              |              |            |                     |      |              |                                                          |

| bit 3:       | Unimplem                                |              |              |            |                     |      |              |                                                          |

| bit 0:       | BRGH: Hig                               |              |              | nit        |                     |      |              |                                                          |

| Dit L.       | Asynchron                               | •            | 210 001001 2 |            |                     |      |              |                                                          |

|              | 1 = High sp                             |              |              |            |                     |      |              |                                                          |

|              | 0 = Low sp                              | eed          |              |            |                     |      |              |                                                          |

|              | Synchrono<br>Unused in                  |              |              |            |                     |      |              |                                                          |

| bit 1:       | TRMT: Train<br>1 = TSR er<br>0 = TSR fu | mpty         | Register S   | tatus bit  |                     |      |              |                                                          |

| bit 0:       | <b>TX9D</b> : 9th                       | bit of trans | mit data. C  | an be pari | ity bit.            |      |              |                                                          |

|              |                                         |              |              |            |                     |      |              |                                                          |

#### TABLE 9-3 BAUD RATES FOR SYNCHRONOUS MODE

| BAUD        | Fosc = 2 | 20 MHz     | SPBRG              | 16 MHz |            | SPBRG              | 10 MHz |            | SPBRG              | 7.15909 I | MHz        | SPBRG              |

|-------------|----------|------------|--------------------|--------|------------|--------------------|--------|------------|--------------------|-----------|------------|--------------------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD  | %<br>ERROR | value<br>(decimal) | KBAUD     | %<br>ERROR | value<br>(decimal) |

| 0.3         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 1.2         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 2.4         | NA       | -          | -                  | NA     | -          | -                  | NA     | -          | -                  | NA        | -          | -                  |

| 9.6         | NA       | -          | -                  | NA     | -          | -                  | 9.766  | +1.73      | 255                | 9.622     | +0.23      | 185                |

| 19.2        | 19.53    | +1.73      | 255                | 19.23  | +0.16      | 207                | 19.23  | +0.16      | 129                | 19.24     | +0.23      | 92                 |

| 76.8        | 76.92    | +0.16      | 64                 | 76.92  | +0.16      | 51                 | 75.76  | -1.36      | 32                 | 77.82     | +1.32      | 22                 |

| 96          | 96.15    | +0.16      | 51                 | 95.24  | -0.79      | 41                 | 96.15  | +0.16      | 25                 | 94.20     | -1.88      | 18                 |

| 300         | 294.1    | -1.96      | 16                 | 307.69 | +2.56      | 12                 | 312.5  | +4.17      | 7                  | 298.3     | -0.57      | 5                  |

| 500         | 500      | 0          | 9                  | 500    | 0          | 7                  | 500    | 0          | 4                  | NA        | -          | -                  |

| HIGH        | 5000     | -          | 0                  | 4000   | -          | 0                  | 2500   | -          | 0                  | 1789.8    | -          | 0                  |

| LOW         | 19.53    | -          | 255                | 15.625 | -          | 255                | 9.766  | -          | 255                | 6.991     | -          | 255                |

|                     | Fosc = 8 | 5.0688 MI  | Нz                          | 4 MHz  |            |                             | 3.579545 | MHz        |                             | 1 MHz  |            |                             | 32.768 k | Hz         |                             |

|---------------------|----------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | NA       | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | 0.303    | +1.14      | 26                          |

| 1.2                 | NA       | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 1.202  | +0.16      | 207                         | 1.170    | -2.48      | 6                           |

| 2.4                 | NA       | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | 2.404  | +0.16      | 103                         | NA       | -          | -                           |

| 9.6                 | 9.6      | 0          | 131                         | 9.615  | +0.16      | 103                         | 9.622    | +0.23      | 92                          | 9.615  | +0.16      | 25                          | NA       | -          | -                           |

| 19.2                | 19.2     | 0          | 65                          | 19.231 | +0.16      | 51                          | 19.04    | -0.83      | 46                          | 19.24  | +0.16      | 12                          | NA       | -          | -                           |

| 76.8                | 79.2     | +3.13      | 15                          | 76.923 | +0.16      | 12                          | 74.57    | -2.90      | 11                          | 83.34  | +8.51      | 2                           | NA       | -          | -                           |

| 96                  | 97.48    | +1.54      | 12                          | 1000   | +4.17      | 9                           | 99.43    | +3.57      | 8                           | NA     | -          | -                           | NA       | -          | -                           |

| 300                 | 316.8    | +5.60      | 3                           | NA     | -          | -                           | 298.3    | -0.57      | 2                           | NA     | -          | -                           | NA       | -          | -                           |

| 500                 | NA       | -          | -                           | NA     | -          | -                           | NA       | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| HIGH                | 1267     | -          | 0                           | 100    | -          | 0                           | 894.9    | -          | 0                           | 250    | -          | 0                           | 8.192    | -          | 0                           |

| LOW                 | 4.950    | -          | 255                         | 3.906  | -          | 255                         | 3.496    | -          | 255                         | 0.9766 | -          | 255                         | 0.032    | -          | 255                         |

## TABLE 9-4 BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD | Fosc = 2 | 20 MHz | SPBRG     | 16 MHz |       | SPBRG     | 10 MHz |       | SPBRG     | 7.15909 I | MHz   | SPBRG     |

|------|----------|--------|-----------|--------|-------|-----------|--------|-------|-----------|-----------|-------|-----------|

| RATE |          | %      | value     |        | %     | value     |        | %     | value     |           | %     | value     |

| (K)  | KBAUD    | ERROR  | (decimal) | KBAUD  | ERROR | (decimal) | KBAUD  | ERROR | (decimal) | KBAUD     | ERROR | (decimal) |

| 0.3  | NA       | -      | -         | NA     | -     | -         | NA     | -     | -         | NA        | -     | -         |

| 1.2  | 1.221    | +1.73  | 255       | 1.202  | +0.16 | 207       | 1.202  | +0.16 | 129       | 1.203     | +0.23 | 92        |

| 2.4  | 2.404    | +0.16  | 129       | 2.404  | +0.16 | 103       | 2.404  | +0.16 | 64        | 2.380     | -0.83 | 46        |

| 9.6  | 9.469    | -1.36  | 32        | 9.615  | +0.16 | 25        | 9.766  | +1.73 | 15        | 9.322     | -2.90 | 11        |

| 19.2 | 19.53    | +1.73  | 15        | 19.23  | +0.16 | 12        | 19.53  | +1.73 | 7         | 18.64     | -2.90 | 5         |

| 76.8 | 78.13    | +1.73  | 3         | 83.33  | +8.51 | 2         | 78.13  | +1.73 | 1         | NA        | -     | -         |

| 96   | 104.2    | +8.51  | 2         | NA     | -     | -         | NA     | -     | -         | NA        | -     | -         |

| 300  | 312.5    | +4.17  | 0         | NA     | -     | -         | NA     | -     | -         | NA        | -     | -         |

| 500  | NA       | -      | -         | NA     | -     | -         | NA     | -     | -         | NA        | -     | -         |

| HIGH | 312.5    | -      | 0         | 250    | -     | 0         | 156.3  | -     | 0         | 111.9     | -     | 0         |

| LOW  | 1.221    | -      | 255       | 0.977  | -     | 255       | 0.6104 | -     | 255       | 0.437     | -     | 255       |

|                     | Fosc = 8 | 5.0688 MI  | Hz                          | 4 MHz  |            |                             | 3.57954 | 5 MHz      |                             | 1 MHz  |            |                             | 32.768 k | Hz         |                             |

|---------------------|----------|------------|-----------------------------|--------|------------|-----------------------------|---------|------------|-----------------------------|--------|------------|-----------------------------|----------|------------|-----------------------------|

| BAUD<br>RATE<br>(K) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD   | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD  | %<br>ERROR | SPBRG<br>value<br>(decimal) | KBAUD    | %<br>ERROR | SPBRG<br>value<br>(decimal) |

| 0.3                 | 0.31     | +3.13      | 255                         | 0.3005 | -0.17      | 207                         | 0.301   | +0.23      | 185                         | 0.300  | +0.16      | 51                          | 0.256    | -14.67     | 1                           |

| 1.2                 | 1.2      | 0          | 65                          | 1.202  | +1.67      | 51                          | 1.190   | -0.83      | 46                          | 1.202  | +0.16      | 12                          | NA       | -          | -                           |

| 2.4                 | 2.4      | 0          | 32                          | 2.404  | +1.67      | 25                          | 2.432   | +1.32      | 22                          | 2.232  | -6.99      | 6                           | NA       | -          | -                           |

| 9.6                 | 9.9      | +3.13      | 7                           | NA     | -          | -                           | 9.322   | -2.90      | 5                           | NA     | -          | -                           | NA       | -          | -                           |

| 19.2                | 19.8     | +3.13      | 3                           | NA     | -          | -                           | 18.64   | -2.90      | 2                           | NA     | -          | -                           | NA       | -          | -                           |

| 76.8                | 79.2     | +3.13      | 0                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 96                  | NA       | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 300                 | NA       | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| 500                 | NA       | -          | -                           | NA     | -          | -                           | NA      | -          | -                           | NA     | -          | -                           | NA       | -          | -                           |

| HIGH                | 79.2     | -          | 0                           | 62.500 | -          | 0                           | 55.93   | -          | 0                           | 15.63  | -          | 0                           | 0.512    | -          | 0                           |

| LOW                 | 0.3094   | -          | 255                         | 3.906  | -          | 255                         | 0.2185  | -          | 255                         | 0.0610 | -          | 255                         | 0.0020   | -          | 255                         |

#### 9.3 USART Synchronous Master Mode

In Synchronous Master mode, the data is transmitted in a half-duplex manner i.e. transmission and reception do not occur at the same time. When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit SYNC (TXSTA<4>). In addition enable bit SPEN (RCSTA<7>) is set in order to configure the RC6/TX/CK and RC7/RX/DT I/O pins to CK (clock) and DT (data) lines respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting bit CSRC (TXSTA<7>).

## 9.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 9-3. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer register TXREG. The TXREG register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once the TXREG register transfers the data to the TSR register (occurs in one Tcycle), the TXREG is empty and interrupt bit, TXIF (PIR1<4>) is set. The interrupt can be

enabled/disabled by setting/clearing enable bit TXIE (PIE1<4>). Flag bit TXIF will be set regardless of the state of enable bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into the TXREG register. While flag bit TXIF indicates the status of the TXREG register, another bit TRMT (TXSTA<1>) shows the status of the TSR register. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (Section 9.1).

- Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting bit TXEN.

- If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- Start transmission by loading data to the TXREG register.

TABLE 9-8 REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address | Name                               | Bit 7                | Bit 6  | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|------------------------------------|----------------------|--------|----------|-------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1                               | PSPIF <sup>(1)</sup> | ADIF   | RCIF     | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA                              | SPEN                 | RX9    | SREN     | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                 |

| 19h     | TXREG                              | USART Tr             | ansmit | Register | ,     |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1                               | PSPIE <sup>(1)</sup> | ADIE   | RCIE     | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA                              | CSRC                 | TX9    | TXEN     | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG Baud Rate Generator Register |                      |        |          |       |       |        |        |        | 0000 0000                | 0000 0000                 |

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for Synchronous Master Transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

NOTES:

NOTES:

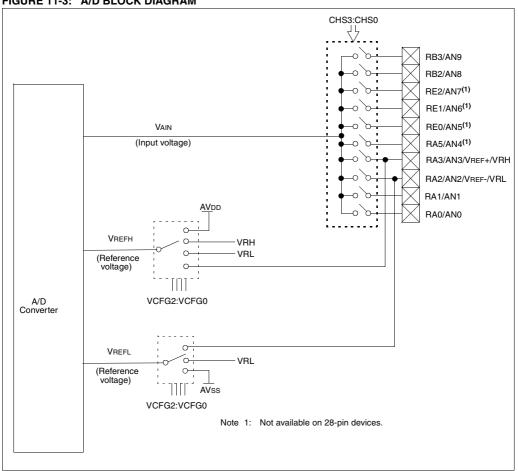

#### FIGURE 11-2: ADCON1 REGISTER (ADDRESS 9Fh)

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

ADFM

VCFG2

VCFG1

VCFG0

PCFG3

PCFG2

PCFG1

PCFG0

bit7

bit 0

R = Readable bit W = Writable bit

U = Unimplemented bit, read as '0'

- n = Value at POR reset

bit 7: ADFM: A/D Result Format Select bit

1 = Right justified 0 = Left justified

bit 6:4 VCFG2:VCFG0: Voltage reference configuration bits

|     | A/D VREFH      | A/D VREFL      |

|-----|----------------|----------------|

| 000 | AVDD           | Avss           |

| 001 | External VREF+ | External VREF- |

| 010 | Internal VRH   | Internal VRL   |

| 011 | External VREF+ | Avss           |

| 100 | Internal VRH   | Avss           |

| 101 | AVDD           | External VREF- |

| 110 | AVDD           | Internal VRL   |

| 111 | Internal VRL   | Avss           |

#### bit 3:0 PCFG3:PCFG0: A/D Port Configuration bits<sup>(1)</sup>

|      | AN9 | AN8 | AN7 | AN6 | AN5 | AN4 | AN3 | AN2 | AN1 | AN0 |

|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0000 | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0001 | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0010 | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0011 | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0100 | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0101 | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0110 | D   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0111 | D   | D   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   |

| 1000 | D   | D   | D   | Α   | Α   | Α   | Α   | Α   | Α   | Α   |

| 1001 | D   | D   | D   | D   | Α   | Α   | Α   | Α   | Α   | Α   |

| 1010 | D   | D   | D   | D   | D   | Α   | Α   | Α   | Α   | Α   |

| 1011 | D   | D   | D   | D   | D   | D   | Α   | Α   | Α   | Α   |

| 1100 | D   | D   | D   | D   | D   | D   | D   | Α   | Α   | Α   |

| 1101 | D   | D   | D   | D   | D   | D   | D   | D   | Α   | Α   |

| 1110 | D   | D   | D   | D   | D   | D   | D   | D   | D   | Α   |

| 1111 | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   |

A = Analog input D= Digital I/O

Note 1: Selection of an unimplemented channel produces a result of 0xFFFFFF.

FIGURE 11-3: A/D BLOCK DIAGRAM

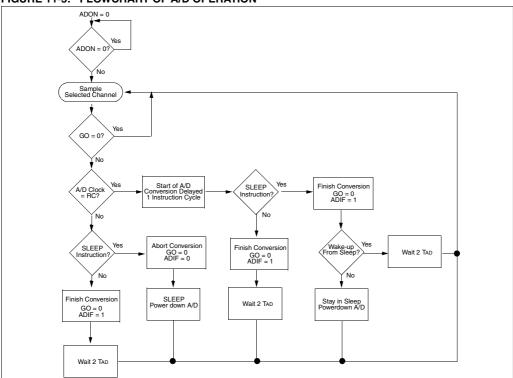

#### FIGURE 11-5: FLOWCHART OF A/D OPERATION

# 12.0 SPECIAL FEATURES OF THE CPU

These PICmicro devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- · Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- · Low-voltage detection

- SLEEP

- · Code protection

- · ID locations

- · In-circuit serial programming

These devices have a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up type resets only (POR, BOR), designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

Additional information on special features is available in the PICmicro™ Mid-Range Reference Manual, (DS33023).

#### 12.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

Some of the core features provided may not be necessary to each application that a device may be used for. The configuration word bits allow these features to be configured/enabled/disabled as necessary. These features include code protection, brown-out reset and its trippoint, the power-up timer, the watchdog timer and the devices oscillator mode. As can be seen in Figure 12-1, some additional configuration word bits have been provided for brown-out reset trippoint selection.

#### 12.10 Interrupts

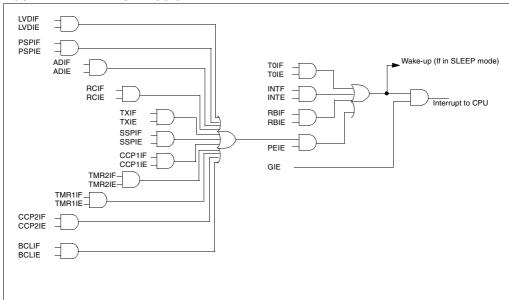

The PIC16C77X family has up to 14 sources of interrupt. The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

Note: Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. When bit GIE is enabled, and an interrupt's flag bit and mask bit are set, the interrupt will vector immediately. Individual interrupts can be disabled through their corresponding enable bits in various registers. Individual interrupt bits are set regardless of the status of the GIE bit. The GIE bit is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit, which re-enables interrupts.

The RB0/INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flags are contained in the special function registers PIR1 and PIR2. The corresponding interrupt enable bits are contained in special function registers PIE1 and PIE2, and the peripheral interrupt enable bit is contained in special function register INTCON.

When an interrupt is responded to, the GIE bit is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for one or two cycle instructions. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit

#### FIGURE 12-11: INTERRUPT LOGIC

The following table shows which devices have which interrupts.

| PIC16C773         Yes         Y | Device    | T0IF | INTF | RBIF | PSPIF | ADIF | RCIF | TXIF | SSPIF | CCP1IF | TMR2IF | TMR1IF | LVDIF | BCLIF | CCP2IF |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|------|------|-------|------|------|------|-------|--------|--------|--------|-------|-------|--------|

| PIC16C774 Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PIC16C773 | Yes  | Yes  | Yes  |       | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes   | Yes   | Yes    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PIC16C774 | Yes  | Yes  | Yes  | Yes   | Yes  | Yes  | Yes  | Yes   | Yes    | Yes    | Yes    | Yes   | Yes   | Yes    |

#### 15.3 DC Characteristics: PIC16C77X (Commercial, Industrial)

| DC CHA | RACTERISTICS                     | Operati               | ng tempe | rature        | -40°C<br>0°C      |              |                                                 |  |  |

|--------|----------------------------------|-----------------------|----------|---------------|-------------------|--------------|-------------------------------------------------|--|--|

| Param  | Characteristic                   | Sym                   | Min      | Typ†          | Max               | Units        | Conditions                                      |  |  |

| No.    |                                  |                       |          |               |                   |              |                                                 |  |  |

|        | Input Low Voltage                |                       |          |               |                   |              | ~                                               |  |  |

|        | I/O ports                        | VIL                   |          |               |                   |              |                                                 |  |  |

| D030   | with TTL buffer                  |                       | Vss      | _             | 0.15VDD           | V            | For entire VDD range                            |  |  |

| D030A  |                                  |                       | Vss      | _             | 0.8V              | V            | 4.5V ≤ VDD ≤ 5.5V                               |  |  |

| D031   | with Schmitt Trigger buffer      |                       |          |               |                   |              |                                                 |  |  |

|        | RC3 and RC4                      |                       | Vss      | _             | 0.3VDD            | ٧/           | I <sup>2</sup> C compliant                      |  |  |

|        | All others                       |                       | Vss      | _             | 0.2VDD            |              | For entire VDD range                            |  |  |

| D032   | MCLR, OSC1 (in RC mode)          |                       | Vss      | _             | 0.2VD             | //           |                                                 |  |  |

| D033   | OSC1 (in XT, HS and LP)          |                       | Vss      | _ /           | 0.3VDD            | / <b>X</b> / | Note1                                           |  |  |

|        | Input High Voltage               |                       |          |               |                   | 1            |                                                 |  |  |

|        | I/O ports                        | VIH                   |          | _             | 1                 | 1            |                                                 |  |  |

|        | with TTL buffer                  |                       |          |               |                   |              |                                                 |  |  |

| D040   |                                  | 1                     | 2 0      |               | V DD /            | V            | $4.5V \le VDD \le 5.5V$                         |  |  |

| D040A  |                                  |                       | 0.25VDD  | $\rightarrow$ | VDD               | \ \          | For entire VDD range                            |  |  |

|        |                                  | \ \                   | + 0.8V \ |               | $\langle \rangle$ |              |                                                 |  |  |

|        | with Schmitt Trigger buffer      | \                     | <u> </u> |               | Ť                 |              |                                                 |  |  |

| D041   | RC3 and RC4                      | $\setminus \setminus$ | \0.7VDD  | ] —           | VDD               | V            | I <sup>2</sup> C compliant                      |  |  |

|        | All others                       | 1                     | Ø.8VDb   | r –           | VDD               | V            | For entire VDD range                            |  |  |

| D042   | MCLR \\                          |                       | 0.8VDD   | _             | VDD               | V            |                                                 |  |  |

| D042A  | OSC1 (XT, HS and LP)             | _                     | 0.7Vdd   | _             | VDD               | V            | Note1                                           |  |  |

| D043   | OSC1 (in RC mode)                |                       | 0.9VDD   | _             | VDD               | V            |                                                 |  |  |

| D070   | PORTB weak pull-up current       | IPURB                 | 50       | 250           | 400               | μΑ           | VDD = 5V, VPIN = VSS                            |  |  |

|        | Input Leakage Current            |                       |          |               |                   |              |                                                 |  |  |

|        | (Notes 2, 3)                     |                       |          |               |                   |              |                                                 |  |  |

| D060   | I/O ports (digital)              | lıL                   | _        | _             | ±1                | μΑ           | Vss ≤ VPIN ≤ VDD, Pin at hi-                    |  |  |

|        |                                  |                       |          |               |                   |              | impedance                                       |  |  |

| D060A  | I/O potts (RA0-RA3, RA5, RB2,    | II∟                   | _        | _             | ±100              | nA           | Vss ≤ VPIN ≤ VDD, Pin at hi-                    |  |  |

|        | RB3 analog)                      |                       |          |               |                   |              | impedance                                       |  |  |

| D061   | MCLR, RA4/T0CKI                  |                       | _        | _             | ±5                | μΑ           | $Vss \le VPIN \le VDD$                          |  |  |

| D063   | OSC1                             |                       | _        | _             | ±5                | μΑ           | $Vss \leq VPIN \leq VDD, \ XT, \ HS \ and \ LP$ |  |  |

|        |                                  |                       |          |               |                   |              | osc configuration                               |  |  |

|        | Output Low Voltage               |                       |          |               |                   |              |                                                 |  |  |

| D080   | I/O ports                        | Vol                   | _        | _             | 0.6               | V            | IOL = 8.5  mA, VDD = 4.5V,                      |  |  |

|        |                                  |                       |          |               |                   |              | -40°C to +85°C                                  |  |  |

| D083   | OSC2/CLKOUT (RC osc config)      |                       | _        | _             | 0.6               | V            | IOL = 1.6  mA, VDD = 4.5V,                      |  |  |

| *      | Those peremeters are characteri- |                       |          |               |                   |              | -40°C to +85°C                                  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C77X be driven with external clock in RC mode.

<sup>2:</sup> The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as current sourced by the pin.

#### **DC Characteristics: VREF** 15.4

#### **TABLE 15-2 ELECTRICAL CHARACTERISTICS: VREF**

| DC CHAR      | Standard O Operating te Operating vo | mperature       | -40°C | C ` ≤ TA :<br>≤ TA : | ≤ +85°C 1<br>≤ +70°C 1 | for industr<br>for comme | ial and           |

|--------------|--------------------------------------|-----------------|-------|----------------------|------------------------|--------------------------|-------------------|

| Param<br>No. | Characteristic                       | Symbol          | Min   | Тур†                 | Max                    | Units                    | Conditions        |

| D400         | Output Voltage                       | VRL             | 2.0   | 2.048                | 2.1                    | V                        | VDD ≥ 2.5V)       |

|              |                                      | VRH             | 4.0   | 4.096                | 4.2                    | V                        | VDØ ≥ 4.5V        |

| D401A        | VRL Quiescent Supply Current         | ΔIVRL           | _     | 70                   | TBD                    | μΑ                       | No load on VRL.   |

| D401B        | VRH Quiescent Supply Current         | ΔIVRH           | _     | 70                   | TBD                    | μA                       | No load on VRH.   |

| D402         | Ouput Voltage Drift                  | TCVout          | _     | 15*                  | 50*                    | ppm/°C/                  | Note 1            |

| D404         | External Load Source                 | IVREFSO         | _     | _                    | 5*                     | /mA                      |                   |

| D405         | External Load Sink                   | Ivrefsi         | _     | _                    | -5*                    | \mA                      |                   |

| D406         | Load Regulation                      |                 | _     | 1                    | J/BD/                  |                          | Isource = 0 mA to |

|              |                                      | $\Delta V$ OUT/ |       |                      |                        | mV/mA                    | 5 mA              |

|              |                                      | $\Delta$ lout   | . —   | 11 /                 | TBD∕₹                  | ALLACTIVA                | Isink = 0 mA to   |

|              |                                      |                 |       | \ \                  |                        |                          | 5 mA              |

| D407         | Line Regulation                      | ∆Vout/<br>∆Vdd  | P     | _/                   | \$0*                   | μ <b>V/V</b>             |                   |

Note 1: Production tested at TAMB = 25 °C. Specifications over temp limits guaranteed by characterization.

<sup>\*</sup> These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

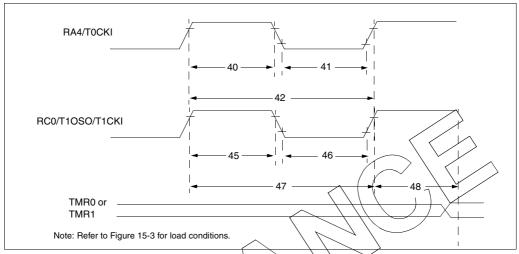

FIGURE 15-11: TIMERO AND TIMER1 EXTERNAL CLOCK TIMINGS

TABLE 15-12 TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                        |                             |                    |              | Min                                | Тур† | Max   | Units | Conditions                         |  |

|--------------|-------|---------------------------------------|-----------------------------|--------------------|--------------|------------------------------------|------|-------|-------|------------------------------------|--|

| 40*          | Tt0H  | T0CKI High Pulse Width                |                             | No Pres            | caler        | 0.5Tcy + 20                        | _    | _     | ns    | Must also meet                     |  |

|              |       |                                       | ////                        | With Pre           | scaler       | 10                                 | _    | _     | ns    | parameter 42                       |  |

| 41*          | TtOL  |                                       |                             | No Pres            |              | 0.5TCY + 20                        | _    | _     | ns    | Must also meet                     |  |

|              |       |                                       |                             | With Pre           |              | 10                                 | _    | _     | ns    | parameter 42                       |  |

| 42*          | Tt0P  | TOCK Period                           | 1 1                         | No Pre             |              | Tcy + 40                           | _    | _     | ns    |                                    |  |

|              |       |                                       | ) )                         | With Pr            | escaler      | Greater of:                        | _    | _     | ns    | N = prescale value                 |  |

|              |       |                                       | / /                         |                    |              | 20 or TCY + 40                     |      |       |       | (2, 4,, 256)                       |  |

|              | 1     |                                       | /                           |                    |              | N                                  |      |       |       |                                    |  |

| 45*          | Tt1H\ | TO CKI High Time                      | Synchronous, P              |                    |              | 0.5Tcy + 20                        | _    | _     | ns    | Must also meet                     |  |

|              | \ \ \ |                                       | Synchronous,<br>Prescaler = | PIC16C             |              | 15                                 | _    | _     | ns    | parameter 47                       |  |

|              | \ [   |                                       | 2,4,8                       | PIC16L             |              | 25                                 |      | _     | ns    |                                    |  |

|              |       | )                                     | Asynchronous                | PIC16 <b>C</b> 77X |              | 30                                 | _    | _     | ns    |                                    |  |

|              |       |                                       |                             | PIC16L             | <b>C</b> 77X | 50                                 | _    | _     | ns    |                                    |  |

| 46*          | Tt1L  | T1CKI Low Time                        | Synchronous, P              | rescaler = 1       |              | 0.5TCY + 20                        | _    | _     | ns    | Must also meet                     |  |

|              |       |                                       | Synchronous,                | PIC16C             |              | 15                                 | _    | _     | ns    | parameter 47                       |  |

|              |       |                                       | Prescaler = 2,4,8           | PIC16L             | <b>C</b> 77X | 25                                 | _    | _     | ns    |                                    |  |

|              |       |                                       | Asynchronous                | PIC16C             |              | 30                                 | _    | _     | ns    |                                    |  |

|              |       |                                       |                             | PIC16L             | <b>C</b> 77X | 50                                 | _    | _     | ns    |                                    |  |

| 47*          | Tt1P  | T1CKI input period                    | Synchronous                 | PIC16C             |              | Greater of:<br>30 OR TCY + 40<br>N | _    |       | ns    | N = prescale value<br>(1, 2, 4, 8) |  |

|              |       |                                       |                             | PIC16L             |              | Greater of:<br>50 OR TCY + 40<br>N | _    | _     | ns    | N = prescale value<br>(1, 2, 4, 8) |  |

|              |       |                                       | Asynchronous                | PIC16 <b>C</b>     |              | 60                                 | _    | _     | ns    |                                    |  |

|              |       |                                       |                             | PIC16L             | <b>C</b> 77X | 100                                | _    | _     | ns    |                                    |  |

|              | Ft1   | Timer1 oscillator input frequency ran |                             | nge                |              | DC                                 | _    | 50    | kHz   |                                    |  |

|              |       | (oscillator enabled b                 |                             |                    |              |                                    |      |       |       |                                    |  |

| 48<br>* T    |       | Delay from external                   |                             |                    | ment         | 2Tosc                              | _    | 7Tosc |       |                                    |  |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

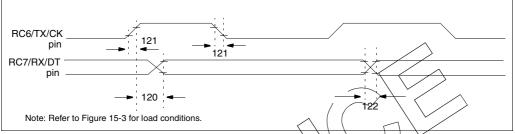

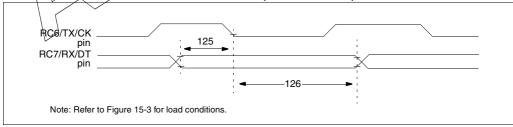

#### FIGURE 15-14: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

## TABLE 15-15 USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                    |                         | Min | Typt | Max | Units | Conditions |

|--------------|----------|-----------------------------------|-------------------------|-----|------|-----|-------|------------|

| 120*         | TckH2dtV | SYNC XMIT (MASTER & SLAVE)        | PIC16 <b>C</b> 7774/773 | _   | _    | 80  | ns    |            |

|              |          | Clock high to data out valid      | PIC16LC774/773          | _   | _    | 100 | ns    |            |

| 121*         | Tckrf    | Clock out rise time and fall time | PIC16 <b>C</b> 774/773  | _   | _    | 45  | ns    |            |

|              |          | (Master Mode)                     | PIC16 <b>LC</b> 774/773 | _   | _    | 50  | ns    |            |

| 122*         | Tdtrf    | Data out rise time and fall time  | PIC16 <b>C</b> 774/773  | _   | _    | 45  | ns    |            |

|              |          |                                   | PIC16 <b>LC</b> 774/773 | _   | _    | 50  | ns    |            |

<sup>\*</sup> These parameters are characterized but not tested.

#### FIGURE 15-15: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### TABLE 15-16 USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter No. | Sym      | Characteristic                                                   | Min | Typ† | Max | Units | Conditions |

|---------------|----------|------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125*          | TdtV2ckL | SYNC RCV (MASTER & SLAVE) Data setup before CK ↓ (DT setup time) | 15  | 1    | 1   | ns    |            |

| 126*          | TckL2dtl | Data hold after CK ↓ (DT hold time)                              | 15  |      | _   | ns    |            |

These parameters are characterized but not tested.

<sup>†:</sup> Data in "Typ" column is at \$V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>†:</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

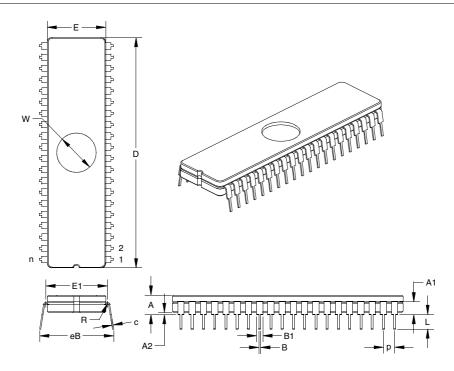

#### 17.7 K04-014 40-Lead Ceramic Dual In-line with Window (JW) - 600 mil

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                        |    | INCHES* |       |       | MILLIMETERS |       |       |  |

|------------------------------|----|---------|-------|-------|-------------|-------|-------|--|

| Dimension Limits             |    | MIN     | NOM   | MAX   | MIN         | NOM   | MAX   |  |

| PCB Row Spacing              |    |         | 0.600 |       |             | 15.24 |       |  |

| Number of Pins               | n  |         | 40    |       |             | 40    |       |  |

| Pitch                        | р  | 0.098   | 0.100 | 0.102 | 2.49        | 2.54  | 2.59  |  |

| Lower Lead Width             | В  | 0.016   | 0.020 | 0.023 | 0.41        | 0.50  | 0.58  |  |

| Upper Lead Width             | B1 | 0.050   | 0.053 | 0.055 | 1.27        | 1.33  | 1.40  |  |

| Shoulder Radius              | R  | 0.000   | 0.005 | 0.010 | 0.00        | 0.13  | 0.25  |  |

| Lead Thickness               | С  | 0.008   | 0.011 | 0.014 | 0.20        | 0.28  | 0.36  |  |

| Top to Seating Plane         | Α  | 0.190   | 0.205 | 0.220 | 4.83        | 5.21  | 5.59  |  |

| Top of Lead to Seating Plane | A1 | 0.117   | 0.135 | 0.153 | 2.97        | 3.43  | 3.89  |  |

| Base to Seating Plane        | A2 | 0.030   | 0.045 | 0.060 | 0.00        | 1.14  | 1.52  |  |

| Tip to Seating Plane         | L  | 0.135   | 0.140 | 0.145 | 3.43        | 3.56  | 3.68  |  |

| Package Length               | D  | 2.040   | 2.050 | 2.060 | 51.82       | 52.07 | 52.32 |  |

| Package Width                | E  | 0.514   | 0.520 | 0.526 | 13.06       | 13.21 | 13.36 |  |

| Radius to Radius Width       | E1 | 0.560   | 0.580 | 0.600 | 14.22       | 14.73 | 15.24 |  |

| Overall Row Spacing          | eВ | 0.610   | 0.660 | 0.710 | 15.49       | 16.76 | 18.03 |  |

| Window Diameter              | W  | 0.340   | 0.350 | 0.360 | 8.64        | 8.89  | 9.14  |  |

Controlling Parameter.

#### PIC16C77X PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO. Device F | -XX X<br>                                                                                                                                                                                                                                                                                                                    | /XX<br>                                                  | XXX<br>Pattern                  | g)       | PDIP packag<br>pattern #301. |                                                                                                                   |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------|----------|------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Device            | PIC16C77X <sup>(1)</sup> , PIC16C77XT<br>PIC16LC77X <sup>(1)</sup> , PIC16LC77X                                                                                                                                                                                                                                              | <sup>(2)</sup> ;VDD range<br>(T <sup>(2)</sup> ;VDD rang | 4.0V to 5.5V<br>ge 2.5V to 5.5V | h)<br>i) | package, 200<br>PIC16C774 -  | - 04I/SO = Industrial temp., SOIC kHz, Extended VDD limits 20I/P = Industrial temp., PDIP MHz, normal VDD limits. |

| Frequency Range   | 04 = 4 MHz<br>20 = 20 MHz                                                                                                                                                                                                                                                                                                    |                                                          |                                 | Note     |                              | CMOS<br>Low Power CMOS                                                                                            |

| Temperature Range | $b^{(3)} = 0^{\circ}C \text{ to } 70^{\circ}C$<br>$I = -40^{\circ}C \text{ to } +85^{\circ}C$                                                                                                                                                                                                                                | (Commerci<br>(Industrial)                                |                                 |          | T = PLCC,                    | in tape and reel - SOIC, SSOP,  QFP, TQFP packages only.  blank                                                   |

| Package           | JW         =         Windowed CER           PQ         =         MQFP (Metric P           PT         =         TOFP (Thin Que           SO         =         SOIC           SP         =         Skinny plastic dl           P         =         PDIP           L         =         PLCC           SS         =         SSOP | QFP)<br>ad Flatpack)                                     |                                 |          |                              |                                                                                                                   |

| Pattern           | QTP, SQTP, Code or Special (blank otherwise)                                                                                                                                                                                                                                                                                 | Requirement                                              | s                               |          |                              |                                                                                                                   |

<sup>\*</sup> JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type (including LC devices).

#### **Sales and Support**

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- Your local Microchip sales office

- 2. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.