Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                             |

| Data Converters            | A/D 6x12b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 28-SPDIP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc773-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

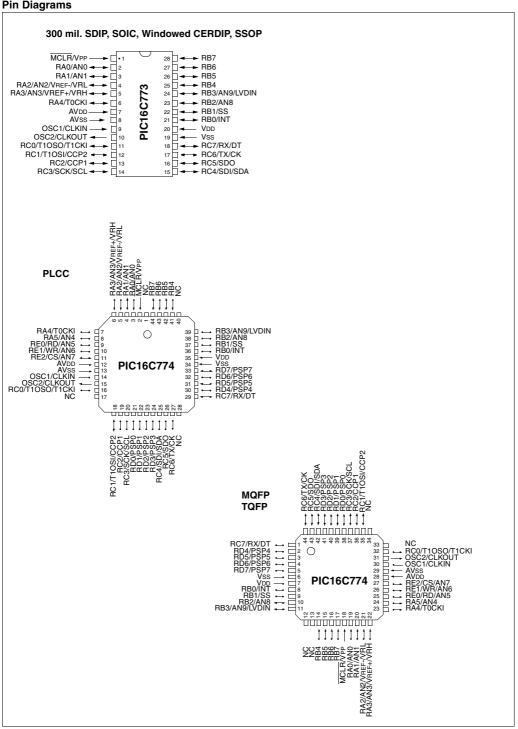

#### Pin Diagrams

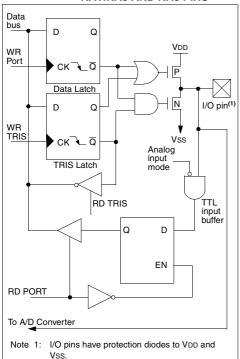

# FIGURE 3-2: BLOCK DIAGRAM OF RA1:RA0 AND RA5 PINS

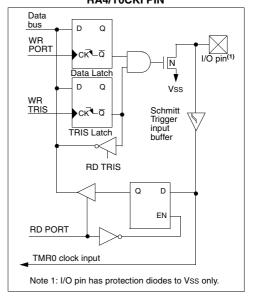

FIGURE 3-3: BLOCK DIAGRAM OF RA4/T0CKI PIN

TABLE 3-1 PORTA FUNCTIONS

| Name                   | Bit# | Buffer | Function                                                                                 |

|------------------------|------|--------|------------------------------------------------------------------------------------------|

| RA0/AN0                | bit0 | TTL    | Input/output or analog input0                                                            |

| RA1/AN1                | bit1 | TTL    | Input/output or analog input1                                                            |

| RA2/AN2/VREF-/VRL      | bit2 | TTL    | Input/output or analog input2 or VREF- input or internal reference voltage low           |

| RA3/AN3/VREF+/VRH      | bit3 | TTL    | Input/output or analog input or VREF+ input or output of internal reference voltage high |

| RA4/T0CKI              | bit4 | ST     | Input/output or external clock input for Timer0 Output is open drain type                |

| RA5/AN4 <sup>(1)</sup> | bit5 | TTL    | Input/output or analog input                                                             |

Legend: TTL = TTL input, ST = Schmitt Trigger input

Note 1: RA5 is reserved on the 28-pin devices, maintain this bit clear.

#### TABLE 3-2 SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

| Address | Name                 | Bit 7 | Bit 6 | Bit 5   | Bit 4                                | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|----------------------|-------|-------|---------|--------------------------------------|-------|-------|-------|-------|--------------------------|---------------------------|

| 05h     | PORTA <sup>(1)</sup> | _     | _     | RA5     | RA4                                  | RA3   | RA2   | RA1   | RA0   | 0x 0000                  | 0u 0000                   |

| 85h     | TRISA <sup>(1)</sup> | _     | _     | PORTA [ | PORTA Data Direction Register11 1111 |       |       |       |       |                          | 11 1111                   |

| 9Fh     | ADCON1               | ADFM  | VCFG2 | VCFG1   | VCFG0                                | PCFG3 | PCFG2 | PCFG1 | PCFG0 | 0000 0000                | 0000 0000                 |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

Note 1: PORTA<5>, TRISA<5> are reserved on the 28-pin devices, maintain these bits clear.

#### 3.3 PORTC and the TRISC Register

PORTC is an 8-bit wide bi-directional port. The corresponding data direction register is TRISC. Setting a TRISC bit (=1) will make the corresponding PORTC pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISC bit (=0) will make the corresponding PORTC pin an output, i.e., put the contents of the output latch on the selected pin.

PORTC is multiplexed with several peripheral functions (Table 3-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in effect while the peripheral is enabled, read-modify-write instructions (BSF, BCF, XORWF) with TRISC as destination should be avoided. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

#### **EXAMPLE 3-1: INITIALIZING PORTC**

```

BCF

STATUS, RPO ; Select Bank 0

CLRF

; Initialize PORTC by

; clearing output

; data latches

; Select Bank 1

BSF

STATUS, RP0

; Value used to

MOVIW

0xCF

; initialize data

; direction

; Set RC<3:0> as inputs

MOVWE TRISC

; RC<5:4> as outputs

; RC<7:6> as inputs

```

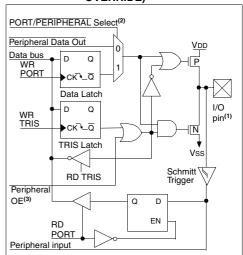

# FIGURE 3-9: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

- Note 1: I/O pins have diode protection to VDD and Vss.

- 2: Port/Peripheral select signal selects between port data and peripheral output.

- 3: Peripheral OE (output enable) is only activated if peripheral select is active.

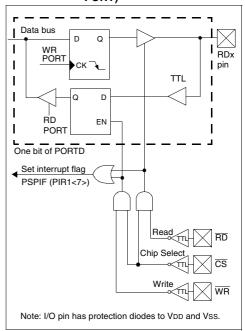

#### 3.6 Parallel Slave Port

The Parallel Slave Port is implemented on the 40/44-pin devices only.

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{\text{RD}}$  control input pin RE0/ $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  control input pin RE1/ $\overline{\text{WR}}$ .

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/ $\overline{RD}$  to be the  $\overline{RD}$  input, RE1/ $\overline{WR}$  to be the  $\overline{WR}$  input and RE2/ $\overline{CS}$  to be the  $\overline{CS}$  (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The configuration bits, PCFG3:PCFG0 (ADCON1<3:0>) must be configured to make pins RE2:RE0 as digital I/O.

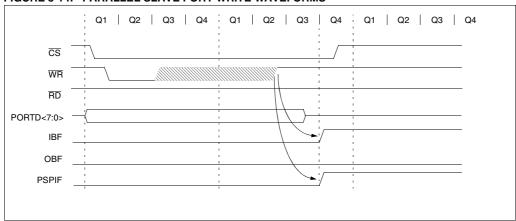

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low.

FIGURE 3-13: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

FIGURE 3-14: PARALLEL SLAVE PORT WRITE WAVEFORMS

#### FIGURE 8-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0 |                          |

|-------|-------|-------|-------|-------|-------|-------|-------|--------------------------|

| WCOL  | SSPOV | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 | R = Readable bit         |

| bit7  |       |       |       |       |       |       | bit0  | W = Writable bit         |

|       |       |       |       |       |       |       |       | - n = Value at POR reset |

bit 7: WCOL: Write Collision Detect bit

Master Mode:

1 = A write to the SSPBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started

0 = No collision Slave Mode:

1 = The SSPBUF register is written while it is still transmitting the previous word

(must be cleared in software)

0 = No collision

bit 6: SSPOV: Receive Overflow Indicator bit

In SPI mode

1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in slave mode. In slave mode, the user must read the SSPBUF, even if only transmitting data, to avoid setting overflow. In master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register. (Must be cleared in software).

0 = No overflow

In I<sup>2</sup>C mode

1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in transmit mode. (Must be cleared in software).

0 = No overflow

bit 5: SSPEN: Synchronous Serial Port Enable bit

In both modes, when enabled, these pins must be properly configured as input or output.

- 1 = Enables serial port and configures SCK, SDO, SDI, and  $\overline{SS}$  as the source of the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins In  $I^2$ C mode

- 1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

- bit 4: CKP: Clock Polarity Select bit

In SPI mode

1 = Idle state for clock is a high level

0 = Idle state for clock is a low level

In I<sup>2</sup>C slave mode

SCK release control

1 = Enable clock

0 = Holds clock low (clock stretch) (Used to ensure data setup time)

In I<sup>2</sup>C master mode

Unused in this mode

bit 3-0: SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

0000 = SPI master mode, clock = Fosc/4

0001 = SPI master mode, clock = Fosc/16

0010 = SPI master mode, clock = Fosc/64

0011 = SPI master mode, clock = TMR2 output/2

0100 = SPI slave mode, clock = SCK pin. SS pin control enabled.

0101 = SPI slave mode, clock = SCK pin. SS pin control disabled. SS can be used as I/O pin

$0110 = I^2C$  slave mode, 7-bit address

$0111 = I^2C$  slave mode, 10-bit address

$1000 = I^2C$  master mode, clock = Fosc / (4 \* (SSPADD+1))

1xx1 = Reserved

1x1x = Reserved

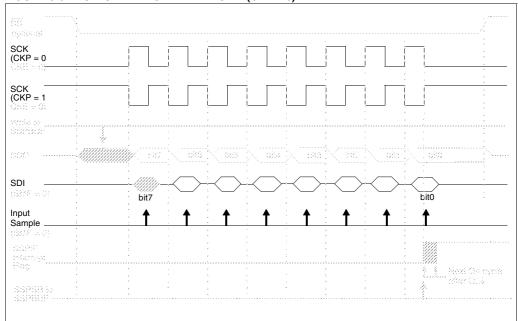

FIGURE 8-8: SPI SLAVE MODE WAVEFORM (CKE = 0)

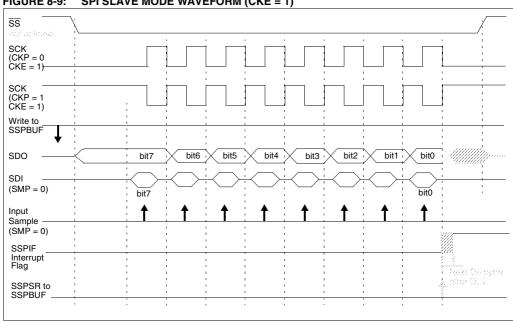

FIGURE 8-9: SPI SLAVE MODE WAVEFORM (CKE = 1)

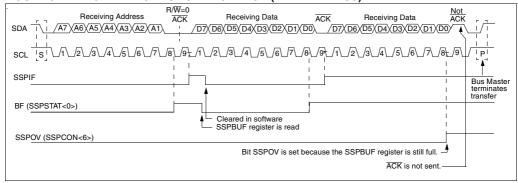

#### 8.2.1.2 SLAVE RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register.

When the address byte overflow condition exists, then no acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON<6>) is set.

An SSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the received byte.

Note:

The SSPBUF will be loaded if the SSPOV bit is set and the BF flag is cleared. If a read of the SSPBUF was performed, but the user did not clear the state of the SSPOV bit before the next receive occured. The ACK is not sent and the SSPBUF is updated.

TABLE 8-2 DATA TRANSFER RECEIVED BYTE ACTIONS

|    | its as Data<br>is Received |                    | Generate ACK | Set bit SSPIF                     |  |

|----|----------------------------|--------------------|--------------|-----------------------------------|--|

| BF | SSPOV                      | $SSPSR \to SSPBUF$ | Pulse        | (SSP Interrupt occurs if enabled) |  |

| 0  | 0                          | Yes                | Yes          | Yes                               |  |

| 1  | 0                          | No                 | No           | Yes                               |  |

| 1  | 1                          | No                 | No           | Yes                               |  |

| 0  | 1                          | Yes                | No           | Yes                               |  |

Note 1: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

#### 8.2.1.3 SLAVE TRANSMISSION

When the R\overline{W} bit of the incoming address byte is set and an address match occurs, the R\overline{W} bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The \overline{ACK} pulse will be sent on the ninth bit, and the SCL pin is held low. The transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then the SCL pin should be enabled by setting bit CKP (SSP-CON<4>). The master must monitor the SCL pin prior to asserting another clock pulse. The slave devices may be holding off the master by stretching the clock. The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 8-13).

An SSP interrupt is generated for each data transfer byte. The SSPIF flag bit must be cleared in software, and the SSPSTAT register is used to determine the status of the byte transfer. The SSPIF flag bit is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. When the not  $\overline{ACK}$  is latched by the slave, the slave logic is reset and the slave then monitors for another occurrence of the START bit. If the SDA line was low  $(\overline{ACK})$ , the transmit data must be loaded into the SSPBUF register, which also loads the SSPSR register. Then the SCL pin should be enabled by setting the CKP bit.

### PIC16C77X

#### SLEEP OPERATION 8.2.3

While in sleep mode, the I<sup>2</sup>C module can receive addresses or data, and when an address match or complete byte transfer occurs wake the processor from sleep (if the SSP interrupt is enabled).

#### EFFECTS OF A RESET 8.2.4

A reset diables the SSP module and terminates the current transfer.

#### REGISTERS ASSOCIATED WITH I2C OPERATION **TABLE 8-3**

| Address                | Name    | Bit 7                | Bit 6        | Bit 5      | Bit 4      | Bit 3      | Bit 2  | Bit 1  | Bit 0  | POR, BOR  | MCLR, WDT |

|------------------------|---------|----------------------|--------------|------------|------------|------------|--------|--------|--------|-----------|-----------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE         | TOIE       | INTE       | RBIE       | TOIF   | INTF   | RBIF   | 0000 000x | 0000 000u |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF         | RCIF       | TXIF       | SSPIF      | CCP1IF | TMR2IF | TMR1IF | 0000 0000 | 0000 0000 |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE         | RCIE       | TXIE       | SSPIE      | CCP1IE | TMR2IE | TMR1IE | 0000 0000 | 0000 0000 |

| 0Dh                    | PIR2    | LVDIF                | _            | _          | _          | BCLIF      | _      | _      | CCP2IF | 0 00      | 0 00      |

| 8Dh                    | PIE2    | LVDIE                | _            | _          | _          | BCLIE      | _      | _      | CCP2IE | 0 00      | 0 00      |

| 13h                    | SSPBUF  | Synchronou           | ıs Serial Po | rt Receive | Buffer/Tra | ansmit Reg | ister  |        |        | xxxx xxxx | uuuu uuuu |

| 14h                    | SSPCON  | WCOL                 | SSPOV        | SSPEN      | CKP        | SSPM3      | SSPM2  | SSPM1  | SSPM0  | 0000 0000 | 0000 0000 |

| 91h                    | SSPCON2 | GCEN                 | AKSTAT       | AKDT       | AKEN       | RCEN       | PEN    | RSEN   | SEN    | 0000 0000 | 0000 0000 |

| 94h                    | SSPSTAT | SMP                  | CKE          | D/A        | Р          | S          | R/W    | UA     | BF     | 0000 0000 | 0000 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in I2C mode.

These bits are reserved on the 28-pin devices, always maintain these bits clear. These bits are reserved on these devices, always maintain these bits clear. Note 1:

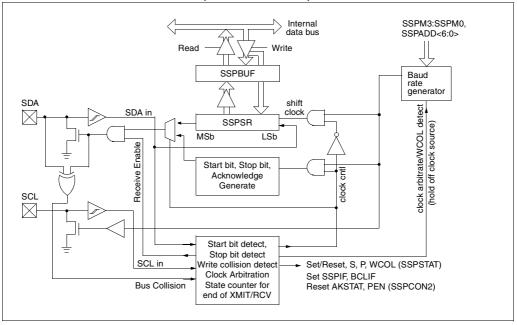

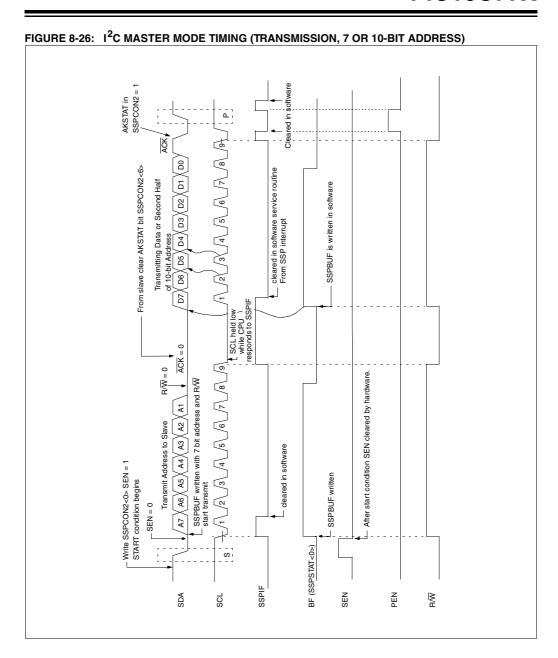

#### 8.2.5 MASTER MODE

Master mode of operation is supported by interrupt generation on the detection of the START and STOP conditions. The STOP (P) and START (S) bits are cleared from a reset or when the MSSP module is disabled. Control of the  $\rm I^2C$  bus may be taken when the P bit is set, or the bus is idle with both the S and P bits clear.

In master mode, the SCL and SDA lines are manipulated by the MSSP hardware.

The following events will cause SSP Interrupt Flag bit, SSPIF, to be set (SSP Interrupt if enabled):

- START condition

- STOP condition

- · Data transfer byte transmitted/received

- · Acknowledge transmit

- · Repeated Start

FIGURE 8-17: SSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

#### FIGURE 8-30: ACKNOWLEDGE FLOWCHART Idle mode Set AKEN Force SCL = 0 BRG Yes rollover? No SCL = 0? Force SCL = 0, Clear AKEN, Set SSPIF SCL = 0? Reset BRG Yes Drive AKDT bit No (SSPCON2<5>) onto SDA pin, Load BRG with SSPADD<6:0>, start count. No AKDT = 1? Yes No BRG Yes SDA = 1? Force SCL = 1 Bus collision detected, Set BCLIF, Release SCL, Clear AKEN SCL = 1? (Clock Arbitration) Load BRG with SSPADD <6:0>, start count.

# 9.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI). The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc.

The USART can be configured in the following modes:

- · Asynchronous (full duplex)

- · Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>), and bits TRISC<7:6>, have to be set in order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

#### FIGURE 9-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

| R/W-0        | R/W-0                                                                                             | R/W-0     | R/W-0        | U-0       | R/W-0    | R-1  | R/W-0        |                                                          |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------|-----------|--------------|-----------|----------|------|--------------|----------------------------------------------------------|--|--|--|

| CSRC<br>bit7 | TX9                                                                                               | TXEN      | SYNC         |           | BRGH     | TRMT | TX9D<br>bit0 | R = Readable bit W = Writable bit U = Unimplemented bit, |  |  |  |

|              |                                                                                                   |           |              |           |          |      |              | read as '0'                                              |  |  |  |

| bit 7:       | CCBC: Cla                                                                                         | ok Couron | Coloot bit   |           |          |      |              | - n =Value at POR reset                                  |  |  |  |

| DIL 7.       | CSRC: Clock Source Select bit                                                                     |           |              |           |          |      |              |                                                          |  |  |  |

|              | Asynchronous mode Don't care                                                                      |           |              |           |          |      |              |                                                          |  |  |  |

|              | Synchrono                                                                                         |           |              |           |          |      |              |                                                          |  |  |  |

|              | 1 = Master mode (Clock generated internally from BRG) 0 = Slave mode (Clock from external source) |           |              |           |          |      |              |                                                          |  |  |  |

| bit 6:       | <b>TX9</b> : 9-bit                                                                                |           |              |           |          |      |              |                                                          |  |  |  |

|              | 1 = Selects 9-bit transmission 0 = Selects 8-bit transmission                                     |           |              |           |          |      |              |                                                          |  |  |  |

| bit 5:       | TXEN: Transmit Enable bit                                                                         |           |              |           |          |      |              |                                                          |  |  |  |

|              | 1 = Transm<br>0 = Transm                                                                          |           |              |           |          |      |              |                                                          |  |  |  |

|              | Note: SRE                                                                                         |           |              | (EN in SY | NC mode. |      |              |                                                          |  |  |  |

| bit 4:       | SYNC: US                                                                                          |           |              |           |          |      |              |                                                          |  |  |  |

|              | 1 = Synchr<br>0 = Asynch                                                                          |           |              |           |          |      |              |                                                          |  |  |  |

| bit 3:       | Unimplem                                                                                          |           |              |           |          |      |              |                                                          |  |  |  |

| bit 0:       | BRGH: Hig                                                                                         |           |              | nit       |          |      |              |                                                          |  |  |  |

| Dit L.       | Asynchron                                                                                         | •         | 210 001001 2 |           |          |      |              |                                                          |  |  |  |

|              | 1 = High sp                                                                                       |           |              |           |          |      |              |                                                          |  |  |  |

|              | 0 = Low sp                                                                                        | eed       |              |           |          |      |              |                                                          |  |  |  |

|              | Synchronous mode Unused in this mode                                                              |           |              |           |          |      |              |                                                          |  |  |  |

| bit 1:       | TRMT: Transmit Shift Register Status bit  1 = TSR empty  0 = TSR full                             |           |              |           |          |      |              |                                                          |  |  |  |

| bit 0:       | TX9D: 9th bit of transmit data. Can be parity bit.                                                |           |              |           |          |      |              |                                                          |  |  |  |

|              |                                                                                                   |           |              |           |          |      |              |                                                          |  |  |  |

#### 9.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. In asynchronous mode bit BRGH (TXSTA<2>) also controls the baud rate. In synchronous mode bit BRGH is ignored. Table 9-1 shows the formula for computation of the baud rate for different USART modes which only apply in master mode (internal clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRG register can be calculated using the formula in Table 9-1. From this, the error in baud rate can be determined.

Example 9-1 shows the calculation of the baud rate error for the following conditions:

Fosc = 16 MHz Desired Baud Rate = 9600 BRGH = 0 SYNC = 0

## EXAMPLE 9-1: CALCULATING BAUD RATE ERROR

Desired Baud rate = Fosc / (64 (X + 1))9600 = 16000000 / (64 (X + 1))

$X = \lfloor 25.042 \rfloor = 25$

Calculated Baud Rate=16000000 / (64 (25 + 1))

= 9615

Error = (Calculated Baud Rate - Desired Baud Rate)

Desired Baud Rate

= (9615 - 9600) / 9600

= 0.16%

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. This is because the Fosc/(16(X+1)) equation can reduce the baud rate error in some cases.

Writing a new value to the SPBRG register causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

#### 9.1.1 SAMPLING

The data on the RC7/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RX pin.

#### TABLE 9-1 BAUD RATE FORMULA

| SYNC | BRGH = 0 (Low Speed)                      | BRGH = 1 (High Speed)     |

|------|-------------------------------------------|---------------------------|

| 0    | (Asynchronous) Baud Rate = Fosc/(64(X+1)) | Baud Rate= Fosc/(16(X+1)) |

| 1    | (Synchronous) Baud Rate = Fosc/(4(X+1))   | NA                        |

X = value in SPBRG (0 to 255)

#### TABLE 9-2 REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address | Name  | Bit 7  | Bit 6                       | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|--------|-----------------------------|-------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 98h     | TXSTA | CSRC   | TX9                         | TXEN  | SYNC  | _     | BRGH  | TRMT  | TX9D  | 0000 -010                | 0000 -010                 |

| 18h     | RCSTA | SPEN   | RX9                         | SREN  | CREN  | ADDEN | FERR  | OERR  | RX9D  | 0000 000x                | 0000 000x                 |

| 99h     | SPBRG | Baud R | aud Rate Generator Register |       |       |       |       |       |       |                          | 0000 0000                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used by the BRG.

#### FIGURE 10-2: REFCON: VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0                                                                                                                                                                                   | R/W-0                                                                                                                                                                                       | R/W-0       | R/W-0        | U-0     | U-0 | U-0 | U-0       |                  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|---------|-----|-----|-----------|------------------|--|--|

| VRHEN                                                                                                                                                                                   | VRLEN                                                                                                                                                                                       | VRHOEN      | VRLOEN       | _       | _   | _   | _         | R = Readable bit |  |  |

| bit7                                                                                                                                                                                    | bit0  W = Writable bit U = Unimplemented bit, read as '0' - n = Value at POR reset                                                                                                          |             |              |         |     |     |           |                  |  |  |

| bit 7: VRHEN: Voltage Reference High Enable bit (VRH = 4.096V)  1 = Enabled, powers up reference generator  0 = Disabled, powers down reference generator if unused by LVD, BOR, or VRL |                                                                                                                                                                                             |             |              |         |     |     |           |                  |  |  |

| bit 6:                                                                                                                                                                                  | VRLEN: Volt<br>1 = Enabled,<br>0 = Disabled                                                                                                                                                 | , powers up | reference ge | nerator |     | ,   | BOR, or ' | VRH              |  |  |

| bit 5:                                                                                                                                                                                  | bit 5: VRHOEN: High Voltage Reference Output Enable bit 1 = Enabled, VRH analog reference is presented on RA3 if enabled (VRHEN = 1) 0 = Disabled, analog reference is used internally only |             |              |         |     |     |           |                  |  |  |

| bit 4:                                                                                                                                                                                  | VRLOEN: Low Voltage Reference Output Enable bit  1 = Enabled, VRL analog reference is presented on RA2 if enabled (VRLEN = 1)  0 = Disabled, analog reference is used internally only       |             |              |         |     |     |           |                  |  |  |

#### 10.1 Bandgap Voltage Reference

bit 3-0: Unimplemented: Read as '0'

The bandgap module generates a stable voltage reference of 1.22V over a range of temperatures and device supply voltages. This module is enabled anytime any of the following are enabled:

- · Brown-out Reset

- Low-voltage Detect

- Either of the internal analog references (VRH, VRL)

Whenever the above are all disabled, the bandgap module is disabled and draws no current.

#### 10.2 Internal VREF for A/D Converter

The bandgap output voltage is used to generate two stable references for the A/D converter module. These references are enabled in software to provide the user with the means to turn them on and off in order to minimize current consumption. Each reference can be individually enabled.

The 4.096V reference (VRH) is enabled with control bit VRHEN (REFCON<7>). When this bit is set, the gain amplifier is enabled. After a specified start-up time a stable reference of 4.096V is generated and can be used by the A/D converter as the VRH input.

The 2.048V reference (VRL) is enabled by setting control bit VRLEN (REFCON<6>). When this bit is set, the gain amplifier is enabled. After a specified start up time a stable reference of 2.048V is generated and can be used by the A/D converter as the VRL input.

Each voltage reference can source/sink up to 5 mA of current.

Each reference, if enabled, can be presented on an external pin by setting the VRHOEN (high reference output enable) or VRLOEN (low reference output enable) control bit. If the reference is not enabled, the VRHOEN and VRLOEN bits will have no effect on the corresponding pin. The device specific pin can then be used as general purpose I/O.

Note: If VRH or VRL is enabled and the other reference (VRL or VRH), the BOR, and the LVD modules are not enabled, the bandgap will require a start-up time of no more than 50 μs before the bandgap reference is stable. Before using the internal VRH or VRL reference, ensure that the bandgap reference voltage is stable by monitoring the BGST bit in the LVDCON register. The voltage references will not be reliable until the bandgap is stable as shown by BGST being set.

# PIC16C77X

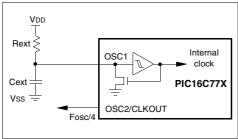

#### 12.2.3 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. These factors and the variation due to tolerances of external R and C components used need to be taken into account for each application. Figure 12-4 shows how the R/C combination is connected to the PIC16C77X.

#### FIGURE 12-4: RC OSCILLATOR MODE

TABLE 12-6 INITIALIZATION CONDITIONS FOR ALL REGISTERS (Cont.'d)

| Register | Dev | ices | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |

|----------|-----|------|------------------------------------|--------------------------|---------------------------------|

| TRISA    | 773 | 774  | 1 1111                             | 1 1111                   | u uuuu                          |

| IIIIOA   | 773 | 774  | 11 1111                            | 11 1111                  | uu uuuu                         |

| TRISB    | 773 | 774  | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISC    | 773 | 774  | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISD    | 773 | 774  | 1111 1111                          | 1111 1111                | uuuu uuuu                       |

| TRISE    | 773 | 774  | 0000 -111                          | 0000 -111                | uuuu -uuu                       |

| PIE1     | 773 | 774  | r000 0000                          | r000 0000                | ruuu uuuu                       |

|          | 773 | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| PIE2     | 773 | 774  | 0 00                               | 0 00                     | u uu                            |

| PCON     | 773 | 774  | qq                                 | uu                       | uu                              |

| PR2      | 773 | 774  | 1111 1111                          | 1111 1111                | 1111 1111                       |

| SSPADD   | 773 | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| SSPSTAT  | 773 | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| TXSTA    | 773 | 774  | 0000 -010                          | 0000 -010                | uuuu -uuu                       |

| SPBRG    | 773 | 774  | 0000 0000                          | 0000 0000                | uuuu uuuu                       |

| REFCON   | 773 | 774  | 0000                               | 0000                     | uuuu                            |

| LVDCON   | 773 | 774  | 00 0101                            | 00 0101                  | uu uuuu                         |

| ADRESL   | 773 | 774  | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |

| ADCON1   | 773 | 774  | 0000 000                           | 0000 0000                | uuuu uuuu                       |

Legend: u= unchanged, x= unknown, -= unimplemented bit, read as '0', q= value depends on condition

- Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 3: See Table 12-5 for reset value for specific condition.

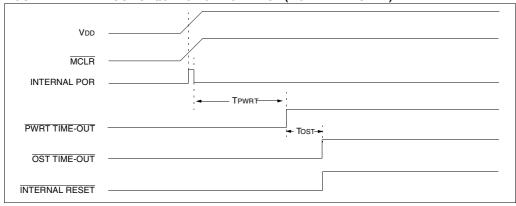

FIGURE 12-7: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

#### 14.0 DEVELOPMENT SUPPORT

#### 14.1 Development Tools

The PICmicro® microcontrollers are supported with a full range of hardware and software development tools:

- MPLAB™ -ICE Real-Time In-Circuit Emulator

- ICEPIC™ Low-Cost PIC16C5X and PIC16CXXX In-Circuit Emulator

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART® Plus Entry-Level Prototype Programmer

- SIMICE

- PICDEM-1 Low-Cost Demonstration Board

- PICDEM-2 Low-Cost Demonstration Board

- PICDEM-3 Low-Cost Demonstration Board

- MPASM Assembler

- MPLAB™ SIM Software Simulator

- MPLAB-C17 (C Compiler)

- Fuzzy Logic Development System (fuzzyTECH<sup>®</sup>-MP)

- KEELOQ<sup>®</sup> Evaluation Kits and Programmer

# 14.2 MPLAB-ICE: High Performance Universal In-Circuit Emulator with MPLAB IDE

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PICmicro microcontrollers (MCUs). MPLAB-ICE is supplied with the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support all new Microchip microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC compatible 386 (and higher) machine platform and Microsoft Windows<sup>®</sup> 3.x or Windows 95 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE is available in two versions. MPLAB-ICE 1000 is a basic, low-cost emulator system with simple trace capabilities. It shares processor modules with the MPLAB-ICE 2000. This is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems will operate across the entire operating speed reange of the PICmicro MCU.

#### 14.3 <u>ICEPIC: Low-Cost PICmicro</u> In-Circuit Emulator

ICEPIC is a low-cost in-circuit emulator solution for the Microchip PIC12CXXX, PIC16C5X and PIC16CXXX families of 8-bit OTP microcontrollers.

ICEPIC is designed to operate on PC-compatible machines ranging from 386 through Pentium™ based machines under Windows 3.x, Windows 95, or Windows NT environment. ICEPIC features real time, non-intrusive emulation.

#### 14.4 PRO MATE II: Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for displaying error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In standalone mode the PRO MATE II can read, verify or program PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices. It can also set configuration and code-protect bits in this mode.

#### 14.5 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, low-cost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient. PICSTART Plus is not recommended for production programming.

PICSTART Plus supports all PIC12CXXX, PIC14C000, PIC16C5X, PIC16CXXX and PIC17CXX devices with up to 40 pins. Larger pin count devices such as the PIC16C923, PIC16C924 and PIC17C756 may be supported with an adapter socket. PICSTART Plus is CE compliant.

#### 15.5 AC Characteristics: PIC16C77X (Commercial, Industrial)

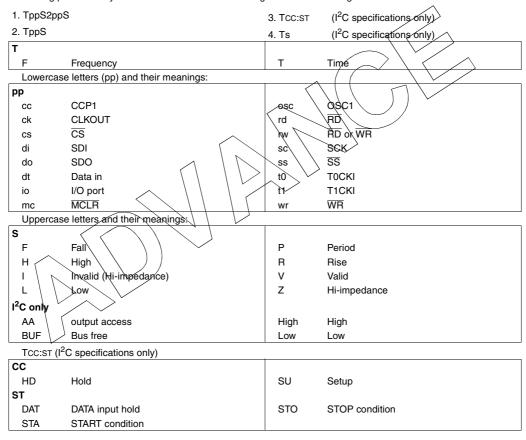

#### 15.5.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

# **PIC16C77X**

| S                                            | SSP Module                                  |

|----------------------------------------------|---------------------------------------------|

| SAE56                                        | SPI Master Mode5                            |

| SCK                                          | SPI Master./Slave Connection                |

| SCL                                          | SPI Slave Mode6                             |

| SDA                                          | SSPCON1 Register                            |

| SDI57                                        | SSP Overflow Detect bit, SSPOV              |

| SDO57                                        | SSPADD Register 1                           |

| SEEVAL® Evaluation and Programming System147 | SSPBUF 15, 6                                |

| Serial Clock, SCK57                          | SSPBUF Register                             |

| Serial Clock, SCL64                          | SSPCON Register 1                           |

| Serial Data Address, SDA64                   | SSPCON1 55, 6                               |

| Serial Data In, SDI57                        | SSPCON2                                     |

| Serial Data Out, SDO57                       |                                             |

| Slave Select Synchronization                 | SSPIF                                       |

| Slave Select, SS57                           | SSPOV                                       |

| SLEEP                                        | SSPSTAT                                     |

| SMP                                          | SSPSTAT Register                            |

| Software Simulator (MPLAB-SIM)147            | Stack                                       |

| SPBRG Register                               | Start bit (S)                               |

| SPE                                          | Start Condition Enabled bit, SAE            |

| Special Features of the CPU                  | STATUS Register                             |

| Special Function Registers                   | C Bit                                       |

| PIC16C73                                     | DC Bit1                                     |

| PIC16C73A                                    | IRP Bit1                                    |

|                                              | PD Bit1                                     |

| PIC16C74A                                    | RP1:RP0 Bits1                               |

|                                              | TO Bit1                                     |

| PIC16C77                                     | Z Bit1                                      |

| SPI                                          | Stop bit (P)5                               |

| Master Mode59                                | Stop Condition Enable bit5                  |

| Serial Clock                                 | Synchronous Serial Port5                    |

| Serial Data In                               | Synchronous Serial Port Enable bit, SSPEN 5 |

| Serial Data Out                              | Synchronous Serial Port Mode Select bits,   |

| Serial Peripheral Interface (SPI)53          | SSPM3:SSPM05                                |

| Slave Select                                 | Т                                           |

| SPI clock                                    | -                                           |

| SPI Mode                                     | T1CON                                       |

| SPI Clock Edge Select, CKE54                 | T1CON Register                              |

| SPI Data Input Sample Phase Select, SMP54    | T1CKPS1:T1CKPS0 Bits                        |

| SPI Master/Slave Connection                  | T1OSCEN Bit                                 |

| SPI Module                                   | T1SYNC Bit                                  |

| Master/Slave Connection 58                   | TMR1CS Bit                                  |

| Slave Mode60                                 | TMR1ON Bit                                  |

| Slave Select Synchronization60               | T2CON Register                              |

| Slave Synch Timnig60                         | T2CKPS1:T2CKPS0 Bits                        |

| <u>SS</u> 57                                 | TOUTPS3:TOUTPS0 Bits                        |

| SSP53                                        | Timer0                                      |

| Block Diagram (SPI Mode)57                   | Block Diagram                               |

| Enable (SSPIE Bit)19                         | Clock Source Edge Select (T0SE Bit)         |

| Flag (SSPIF Bit)20                           | Clock Source Select (TOCS Bit)              |

| RA5/SS/AN4 Pin 8                             | Overflow Enable (T0IE Bit)                  |

| RC3/SCK/SCL Pin                              | Overflow Flag (TOIF Bit)                    |

| RC4/SDI/SDA Pin                              | Overflow Interrupt                          |

| RC5/SDO Pin                                  | RA4/T0CKI Pin, External Clock               |

| SPI Mode57                                   | Timer1 4                                    |

| SSPADD                                       | Block Diagram4                              |

| SSPBUF                                       | Capacitor Selection4                        |

| SSPCON155                                    | Clock Source Select (TMR1CS Bit)4           |

| SSPCON2                                      | External Clock Input Sync (T1SYNC Bit) 4    |

| SSPSR                                        | Module On/Off (TMR1ON Bit)4                 |

| SSPSTAT                                      | Oscillator 41, 4                            |

| SSP I <sup>2</sup> C                         | Oscillator Enable (T1OSCEN Bit) 4           |

| SSP I <sup>2</sup> C Operation               | Overflow Enable (TMR1IE Bit)1               |

| 001 1 0 Operation03                          | Overflow Flag (TMR1IF Bit)2                 |

#### **ON-LINE SUPPORT**

Microchip provides on-line support on the Microchip World Wide Web (WWW) site.

The web site is used by Microchip as a means to make files and information easily available to customers. To view the site, the user must have access to the Internet and a web browser, such as Netscape or Microsoft Explorer. Files are also available for FTP download from our FTP site.

#### Connecting to the Microchip Internet Web Site

The Microchip web site is available by using your favorite Internet browser to attach to:

#### www.microchip.com

The file transfer site is available by using an FTP service to connect to:

#### ftp://ftp.microchip.com

The web site and file transfer site provide a variety of services. Users may download files for the latest Development Tools, Data Sheets, Application Notes, User's Guides, Articles and Sample Programs. A variety of Microchip specific business information is also available, including listings of Microchip sales offices, distributors and factory representatives. Other data available for consideration is:

- · Latest Microchip Press Releases

- Technical Support Section with Frequently Asked Questions

- · Design Tips

- Device Errata

- Job Postings

- · Microchip Consultant Program Member Listing

- Links to other useful web sites related to Microchip Products

- Conferences for products, Development Systems, technical information and more

- · Listing of seminars and events