Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 22                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                             |

| Data Converters            | A/D 6x12b                                                               |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                          |

| Supplier Device Package    | 28-SSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc773-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output, i.e., put the contents of the output latch on the selected pin.

#### **EXAMPLE 3-1: INITIALIZING PORTB**

```

BCF

STATUS, RPO

CLRF

PORTB

Initialize PORTB by

; clearing output

; data latches

BSF

STATUS. RPO

; Select Bank 1

MOVLW

0xCF

Value used to

; initialize data

: direction

MOVWF

TRISB

; Set RB<3:0> as inputs

; RB<5:4> as outputs

; RB<7:6> as inputs

```

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

The RB0 pin is multiplexed with the external interrupt (RB0/INT).

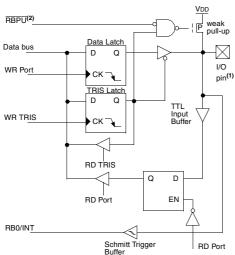

## FIGURE 3-4: BLOCK DIAGRAM OF RB0 PIN

Note 1: I/O pins have diode protection to VDD and Vss.

2: To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (OPTION\_REG<7>).

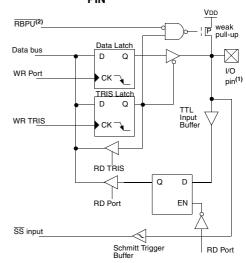

The RB1 pin is multiplexed with the SSP module slave select (RB1/SS).

## FIGURE 3-5: BLOCK DIAGRAM OF RB1/SS

Note 1: I/O pins have diode protection to VDD and VSS.

2: To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (OPTION\_REG<7>).

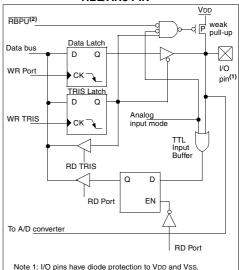

The RB2 pin is multiplexed with analog channel 8 (RB2/AN8).

# FIGURE 3-6: BLOCK DIAGRAM OF RB2/AN8 PIN

2: To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (OPTION\_REG<7>).

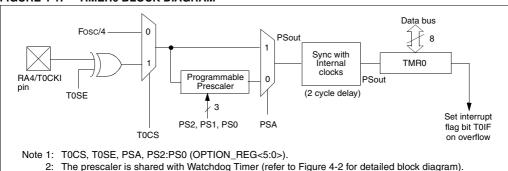

## 4.0 TIMERO MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- · Readable and writable

- · Internal or external clock select

- · Edge select for external clock

- · 8-bit software programmable prescaler

- Interrupt on overflow from FFh to 00h

Figure 4-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PICmicro™ Mid-Range Reference Manual, (DS33023).

### 4.1 Timer0 Operation

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit TOCS (OPTION\_REG<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit TOCS (OPTION\_REG<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/TOCKI. The incrementing edge is determined by the Timer0 Source Edge Select bit TOSE (OPTION\_REG<4>). Clearing bit TOSE selects the rising edge. Restrictions on the external clock input are discussed in below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

#### 4.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 4-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

#### FIGURE 4-1: TIMERO BLOCK DIAGRAM

## FIGURE 8-2: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0 |                          |

|-------|-------|-------|-------|-------|-------|-------|-------|--------------------------|

| WCOL  | SSPOV | SSPEN | CKP   | SSPM3 | SSPM2 | SSPM1 | SSPM0 | R = Readable bit         |

| bit7  |       |       |       |       |       |       | bit0  | W = Writable bit         |

|       |       |       |       |       |       |       |       | - n = Value at POR reset |

bit 7: WCOL: Write Collision Detect bit

Master Mode:

1 = A write to the SSPBUF register was attempted while the I<sup>2</sup>C conditions were not valid for a transmission to be started

0 = No collision Slave Mode:

1 = The SSPBUF register is written while it is still transmitting the previous word

(must be cleared in software)

0 = No collision

bit 6: SSPOV: Receive Overflow Indicator bit

In SPI mode

1 = A new byte is received while the SSPBUF register is still holding the previous data. In case of overflow, the data in SSPSR is lost. Overflow can only occur in slave mode. In slave mode, the user must read the SSPBUF, even if only transmitting data, to avoid setting overflow. In master mode, the overflow bit is not set since each new reception (and transmission) is initiated by writing to the SSPBUF register. (Must be cleared in software).

0 = No overflow

In I<sup>2</sup>C mode

1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don't care" in transmit mode. (Must be cleared in software).

0 = No overflow

bit 5: SSPEN: Synchronous Serial Port Enable bit

In both modes, when enabled, these pins must be properly configured as input or output.

- 1 = Enables serial port and configures SCK, SDO, SDI, and  $\overline{SS}$  as the source of the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins In  $I^2$ C mode

- 1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins

- 0 = Disables serial port and configures these pins as I/O port pins

- bit 4: CKP: Clock Polarity Select bit

In SPI mode

1 = Idle state for clock is a high level

0 = Idle state for clock is a low level

In I<sup>2</sup>C slave mode

SCK release control

1 = Enable clock

0 = Holds clock low (clock stretch) (Used to ensure data setup time)

In I<sup>2</sup>C master mode

Unused in this mode

bit 3-0: SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

0000 = SPI master mode, clock = Fosc/4

0001 = SPI master mode, clock = Fosc/16

0010 = SPI master mode, clock = Fosc/64

0011 = SPI master mode, clock = TMR2 output/2

0100 = SPI slave mode, clock = SCK pin. SS pin control enabled.

0101 = SPI slave mode, clock = SCK pin. SS pin control disabled. SS can be used as I/O pin

$0110 = I^2C$  slave mode, 7-bit address

$0111 = I^2C$  slave mode, 10-bit address

$1000 = I^2C$  master mode, clock = Fosc / (4 \* (SSPADD+1))

1xx1 = Reserved

1x1x = Reserved

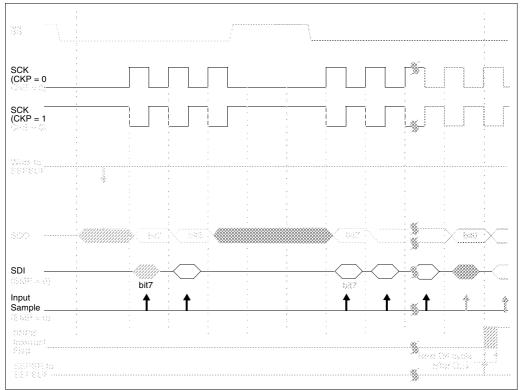

#### 8.1.5 SLAVE MODE

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched the interrupt flag bit SSPIF (PIR1<3>) is set

While in slave mode the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in sleep mode, the slave can transmit/receive data. When a byte is received the device will wake-up from sleep.

#### 8.1.6 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 0100). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. TRISA<5> must be set. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the

SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. External pull-up/pull-down resistors may be desirable, depending on the application.

Note: When the SPI module is in Slave Mode with  $\overline{SS}$  pin control enabled, (SSP-CON<3:0> = 0100) the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

**Note:** If the SPI is used in Slave Mode with CKE = '1', then  $\overline{SS}$  pin control must be enabled.

When the SPI module resets, the bit counter is forced to 0. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

FIGURE 8-7: SLAVE SYNCHRONIZATION WAVEFORM

- The MSSP Module shifts in the ACK bit from the slave device, and writes its value into the SSPCON2 register (SSPCON2<6>).

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- k) The user generates a STOP condition by setting the STOP enable bit PEN in SSPCON2.

- Interrupt is generated once the STOP condition is complete.

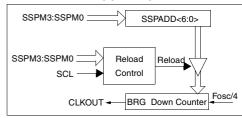

#### 8.2.8 BAUD RATE GENERATOR

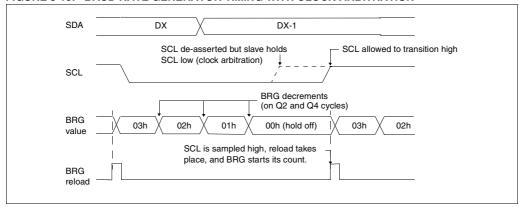

In I<sup>2</sup>C master mode, the reload value for the BRG is located in the lower 7 bits of the SSPADD register (Figure 8-18). When the BRG is loaded with this value, the BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (TCY) on the Q2 and Q4 clock.

In I<sup>2</sup>C master mode, the BRG is reloaded automatically. If Clock Arbitration is taking place for instance, the BRG will be reloaded when the SCL pin is sampled high (Figure 8-19).

# FIGURE 8-18: BAUD RATE GENERATOR BLOCK DIAGRAM

FIGURE 8-19: BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

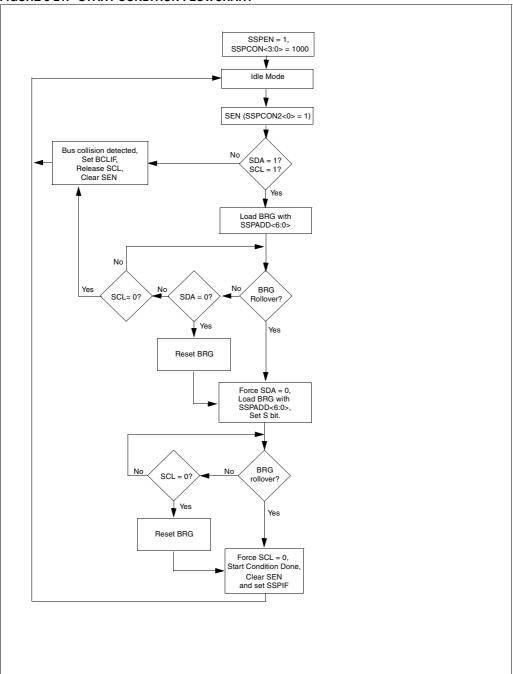

FIGURE 8-21: START CONDITION FLOWCHART

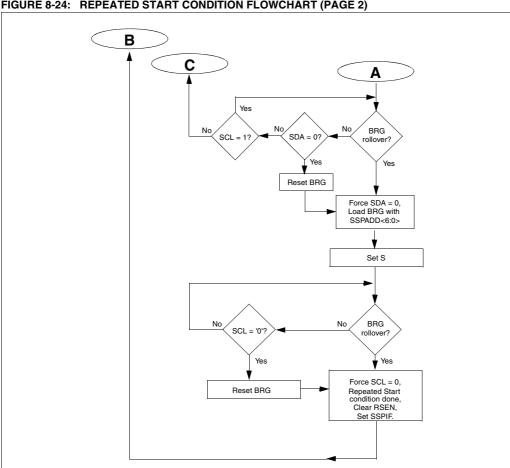

FIGURE 8-24: REPEATED START CONDITION FLOWCHART (PAGE 2)

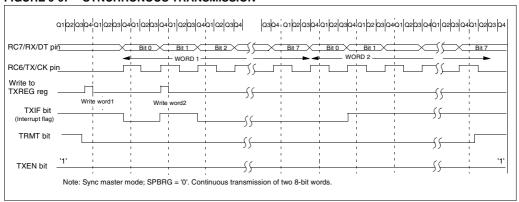

## FIGURE 9-9: SYNCHRONOUS TRANSMISSION

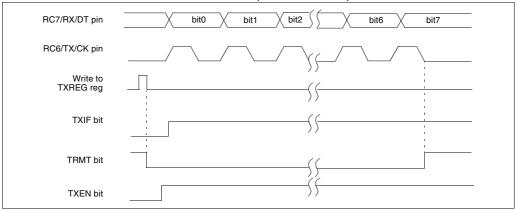

## FIGURE 9-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

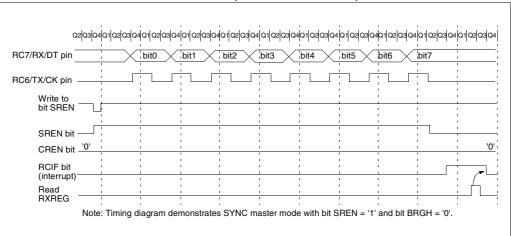

## 9.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either enable bit SREN (RCSTA<5>) or enable bit CREN (RCSTA<4>). Data is sampled on the RC7/RX/DT pin on the falling edge of the clock. If enable bit SREN is set, then only a single word is received. If enable bit CREN is set, the reception is continuous until CREN is cleared. If both bits are set then CREN takes precedence.

Steps to follow when setting up a Synchronous Master Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate. (Section 9.1)

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- If interrupts are desired, then set enable bit RCIE.

- 5. If 9-bit reception is desired, then set bit RX9.

- 6. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- Interrupt flag bit RCIF will be set when reception is complete and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register.

- If any error occurred, clear the error by clearing bit CREN.

TABLE 9-9 REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

| Address | Name  | Bit 7                | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|------------------------------|-------|-------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF                         | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9                          | SREN  | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                 |

| 1Ah     | RCREG | USART R              | USART Receive Register       |       |       |       |        |        |        |                          | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE                         | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9                          | TXEN  | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate            | Baud Rate Generator Register |       |       |       |        |        |        |                          | 0000 0000                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Master Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

FIGURE 9-11: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

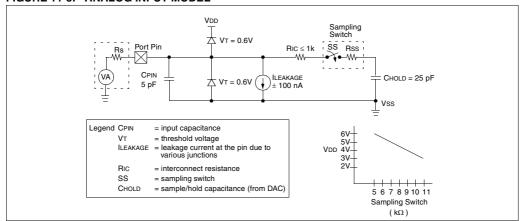

#### FIGURE 11-7: CALCULATING THE MINIMUM REQUIRED SAMPLE TIME

```

TACQ =

Amplifier Settling Time

+ Holding Capacitor Charging Time

+Temperature Coefficient †

TACQ =

+ Tc

+ [(Temp - 25°C)(0.05 μs/°C)] †

Tc = + Holding Capacitor Charging Time

Tc = (CHOLD) (Ric + Rss + Rs) In (1/16384)

-25 pF (1 kΩ +10 kΩ + 2.5 kΩ) In (1/16384)

-25 pF (13.5 kΩ) In (1/16384)

-0.338 (-9.704)μs

Tc=

3.3<sub>us</sub>

TACQ =

5 μs

+ 3.3 \mu s

+ [(50°C - 25°C)(0.05 μs / °C)]

TACQ =

8.3 \mu s + 1.25 \mu s

TACQ =

9.55 μs

```

† The temperature coefficient is only required for temperatures > 25°C.

#### FIGURE 11-8: ANALOG INPUT MODEL

### 11.7 Use of the CCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP module. This requires that the CCPnM<3:0> bits be programmed as 1011b and that the A/D module is enabled (ADON is set). When the trigger occurs, the GO/DONE bit will be set on Q2 to start the A/D conversion and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D conversion cycle, with minimal software overhead (moving the ADRESH and ADRESL to the desired location). The appropriate analog input channel must be selected before the "special event trigger" sets the GO/DONE bit (starts a conversion cycle).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

#### 11.8 Effects of a RESET

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted. The value that is in the ADRESH and ADRESL registers are not modified. The ADRESH and ADRESL registers will contain unknown data after a Power-on Reset.

## 11.9 <u>Faster Conversion - Lower</u> <u>Resolution Trade-off</u>

Not all applications require a result with 12-bits of resolution, but may instead require a faster conversion time. The A/D module allows users to make the trade-off of conversion speed to resolution. Regardless of the resolution required, the acquisition time is the same. To speed up the conversion, the A/D module may be halted by clearing the GO/DONE bit after the desired number of bits in the result have been converted. Once the GO/DONE bit has been cleared, all of the remaining A/D result bits are '0'. The equation to determine the time before the GO/DONE bit can be switched is as follows:

Conversion time = N•TAD + 1TAD

Where: N = number of bits of resolution required, and 1TAD is the amplifier settling time.

Since TAD is based from the device oscillator, the user must use some method (a timer, software loop, etc.) to determine when the A/D GO/DONE bit may be cleared. Table 11-2 shows a comparison of time required for a conversion with 4-bits of resolution, versus the normal 12-bit resolution conversion. The example is for devices operating at 20 MHz. The A/D clock is programmed for 32 Tosc.

TABLE 11-2 4-BIT vs. 12-BIT CONVERSION TIMES

|               | Freq. | Resolution |         |  |

|---------------|-------|------------|---------|--|

|               | (MHz) | 4-bit      | 12-bit  |  |

| Tosc          | 20    | 50 ns      | 50 ns   |  |

| TAD = 32 Tosc | 20    | 1.6 μs     | 1.6 μs  |  |

| 1TAD+N•TAD    | 20    | 8 μs       | 20.8 μs |  |

TABLE 12-6 INITIALIZATION CONDITIONS FOR ALL REGISTERS

| Register   | Devices           |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |

|------------|-------------------|-----|------------------------------------|--------------------------|---------------------------------|--|

| W          | 773               | 774 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| INDF       | 773               | 774 | N/A                                | N/A                      | N/A                             |  |

| TMR0       | 773               | 774 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PCL        | 773               | 774 | 0000h                              | 0000h                    | PC + 1(2)                       |  |

| STATUS     | 773               | 774 | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu(3)                    |  |

| FSR        | 773 774 xxxx xxxx |     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTA      | 773               | 774 | 0x 0000                            | 0u 0000                  | uu uuuu                         |  |

| PORTB      | 773               | 774 | xxxx 11xx                          | uuuu 11uu                | uuuu uuuu                       |  |

| PORTC      | 773 774           |     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTD      | 773 774           |     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| PORTE      | 773 774           |     | 000                                | 000                      | uuu                             |  |

| PCLATH     | 773               | 774 | 0 0000                             | 0 0000                   | u uuuu                          |  |

| INTCON     | 773               | 774 | 0000 000x                          | 0000 000u                | uuuu uuuu(1)                    |  |

| PIR1       | 773               | 774 | r000 0000                          | r000 0000                | ruuu uuuu(1)                    |  |

|            | 773               | 774 | 0000 0000                          | 0000 0000                | uuuu uuuu(1)                    |  |

| PIR2       | 773               | 774 | 0 00                               | 0 00                     | u uu <sup>(1)</sup>             |  |

| TMR1L      | 773               | 774 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| TMR1H      | 773               | 774 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| T1CON      | 773 77400 0000    |     | uu uuuu                            | uu uuuu                  |                                 |  |

| TMR2       | 773               | 774 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

| T2CON      | N 773 774         |     | -000 0000                          | -000 0000                | -uuu uuuu                       |  |

| SSPBUF     | PBUF 773          |     | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| SSPCON     | 773               | 774 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

| CCPR1L     | 773               | 774 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| CCPR1H     | 773               | 774 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| CCP1CON    | 773               | 774 | 00 0000                            | 00 0000                  | uu uuuu                         |  |

| RCSTA      | 773               | 774 | 0000 000x                          | 0000 000x                | uuuu uuuu                       |  |

| TXREG      | 773               | 774 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

| RCREG      | 773               | 774 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

| CCPR2L     | 773               | 774 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| CCPR2H     | 773               | 774 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| CCP2CON    | 773               | 774 | 00 0000                            | 00 0000                  | uu uuuu                         |  |

| ADRESH     | 773               | 774 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |

| ADCON0     | 773               | 774 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |

| OPTION_REG | 773               | 774 | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |

Legend: u= unchanged, x= unknown, -= unimplemented bit, read as '0', q= value depends on condition

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

<sup>2:</sup> When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

<sup>3:</sup> See Table 12-5 for reset value for specific condition.

#### 12.10.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 12.13 for details on SLEEP mode.

#### 12.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 4.0)

#### 12.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 3.2)

### 12.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, i.e., W register and STATUS register. This will have to be implemented in software.

Example 12-1 stores and restores the W and STATUS registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Stores the PCLATH register.

- d) Executes the interrupt service routine code (User-generated).

- e) Restores the STATUS register (and bank select hit)

- f) Restores the W and PCLATH registers.

#### **EXAMPLE 12-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM**

```

W TEMP

;Copy W to TEMP register, could be bank one or zero

MOVWE

SWAPF

STATUS, W

;Swap status to be saved into W

;bank 0, regardless of current bank, Clears IRP,RP1,RP0

STATUS

;Save status to bank zero STATUS_TEMP register

MOVWF

STATUS TEMP

PCLATH, W

;Only required if using pages 1, 2 and/or 3

MOVF

PCLATH TEMP

;Save PCLATH into W

MOVWF

CLRF

PCLATH

;Page zero, regardless of current page

STATUS, IRP

;Return to Bank 0

BCF

MOVF

FSR, W

;Copy FSR to W

MOVWF

FSR TEMP

;Copy FSR from W to FSR TEMP

: (ISR)

MOVE

PCLATH TEMP, W

;Restore PCLATH

;Move W into PCLATH

MOVWF

PCT.ATH

SWAPF

STATUS TEMP, W

;Swap STATUS TEMP register into W

; (sets bank to original state)

MOVWE

STATUS

; Move W into STATUS register

W TEMP, F

;Swap W_TEMP

SWAPF

W TEMP, W

;Swap W_TEMP into W

SWAPE

```

## 14.10 MPLAB Integrated Development Environment Software

The MPLAB IDE Software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a windows based application which contains:

- · A full featured editor

- · Three operating modes

- editor

- emulator

- simulator

- · A project manager

- · Customizable tool bar and key mapping

- · A status bar with project information

- · Extensive on-line help

#### MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PICmicro tools (automatically updates all project information)

- · Debug using:

- source files

- absolute listing file

The ability to use MPLAB with Microchip's simulator allows a consistent platform and the ability to easily switch from the low cost simulator to the full featured emulator with minimal retraining due to development tools.

#### 14.11 Assembler (MPASM)

The MPASM Universal Macro Assembler is a PC-hosted symbolic assembler. It supports all microcontroller series including the PIC12C5XX, PIC14000, PIC16C5X, PIC16CXXX, and PIC17CXX families.

MPASM offers full featured Macro capabilities, conditional assembly, and several source and listing formats. It generates various object code formats to support Microchip's development tools as well as third party programmers.

MPASM allows full symbolic debugging from MPLAB-ICE, Microchip's Universal Emulator System.

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- · Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PICmicro. Directives are helpful in making the development of your assemble source code shorter and more maintainable

#### 14.12 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PICmicro series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C17 and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

### 14.13 MPLAB-C17 Compiler

The MPLAB-C17 Code Development System is a complete ANSI 'C' compiler and integrated development environment for Microchip's PIC17CXXX family of microcontrollers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display.

# 14.14 Fuzzy Logic Development System (fuzzyTECH-MP)

fuzzyTECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, fuzzyTECH-MP, Edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB™ demonstration board for hands-on experience with fuzzy logic systems implementation.

# 14.15 <u>SEEVAL® Evaluation and</u> Programming System

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials™ and secure serials. The Total Endurance™ Disk is included to aid in trade-off analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

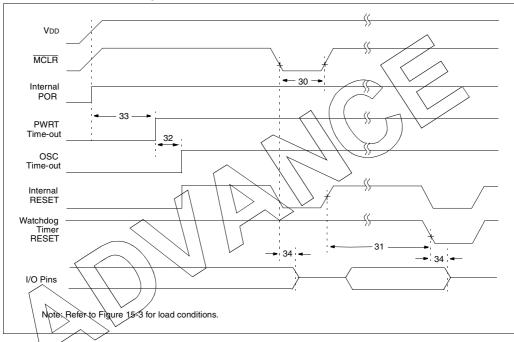

FIGURE 15-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

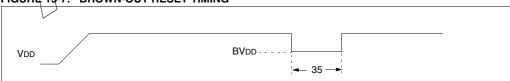

FIGURE 15-7: BROWN-OUT RESET TIMING

TABLE 15-7 RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

| Parameter No. | Sym   | Characteristic                                         | Min | Typ†     | Max | Units | Conditions                                        |

|---------------|-------|--------------------------------------------------------|-----|----------|-----|-------|---------------------------------------------------|

| 30*           | TmcL  | MCLR Pulse Width (low)                                 | 100 | _        | -   | ns    | VDD = 5V, -40°C to +85°C                          |

| 31*           | Twdt  | Watchdog Timer Time-out Period (No Prescaler)          | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +85°C                          |

| 32*           | Tost  | Oscillation Start-up Timer Period                      | _   | 1024Tosc | _   | _     | Tosc = OSC1 period                                |

| 33*           | Tpwrt | Power up Timer Period                                  | 28  | 72       | 132 | ms    | $VDD = 5V, -40^{\circ}C \text{ to } +85^{\circ}C$ |

| 34*           | Tıoz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset | _   | _        | 100 | ns    |                                                   |

| 35*           | TBOR  | Brown-out Reset pulse width                            | 100 | _        | _   | μS    | VDD ≤ VBOR (D005)                                 |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are guaranteed to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. 'Typical' represents the mean of the distribution at  $25^{\circ}$ C. 'Max' or 'min' represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation, over the whole temperature range.

Graphs and Tables not available at this time.

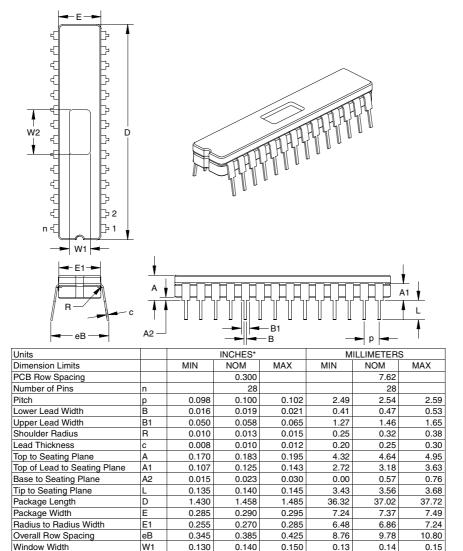

## 17.3 K04-080 28-Lead Ceramic Dual In-line with Window (JW) - 300 mil

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

<sup>\*</sup> Controlling Parameter.

W2

0.290

Window Length

0.300

0.310

0.29

0.3

0.31

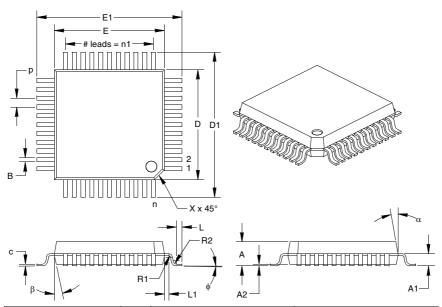

## 17.9 K04-071 44-Lead Plastic Quad Flatpack (PQ) 10x10x2 mm Body, 1.6/0.15 mm Lead Form

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                   |                |       | INCHES |       | MI    | LLIMETERS | *     |

|-------------------------|----------------|-------|--------|-------|-------|-----------|-------|

| Dimension Limits        |                | MIN   | NOM    | MAX   | MIN   | NOM       | MAX   |

| Pitch                   | р              |       | 0.031  |       |       | 0.80      |       |

| Number of Pins          | n              |       | 44     |       |       | 44        |       |

| Pins along Width        | n1             |       | 11     |       |       | 11        |       |

| Overall Pack. Height    | Α              | 0.079 | 0.086  | 0.093 | 2.00  | 2.18      | 2.35  |

| Shoulder Height         | A1             | 0.032 | 0.044  | 0.056 | 0.81  | 1.11      | 1.41  |

| Standoff                | A2             | 0.002 | 0.006  | 0.010 | 0.05  | 0.15      | 0.25  |

| Shoulder Radius         | R1             | 0.005 | 0.005  | 0.010 | 0.13  | 0.13      | 0.25  |

| Gull Wing Radius        | R2             | 0.005 | 0.012  | 0.015 | 0.13  | 0.30      | 0.38  |

| Foot Length             | L              | 0.015 | 0.020  | 0.025 | 0.38  | 0.51      | 0.64  |

| Foot Angle              | ф              | 0     | 3.5    | 7     | 0     | 3.5       | 7     |

| Radius Centerline       | L1             | 0.011 | 0.016  | 0.021 | 0.28  | 0.41      | 0.53  |

| Lead Thickness          | С              | 0.005 | 0.007  | 0.009 | 0.13  | 0.18      | 0.23  |

| Lower Lead Width        | В†             | 0.012 | 0.015  | 0.018 | 0.30  | 0.37      | 0.45  |

| Outside Tip Length      | D1             | 0.510 | 0.520  | 0.530 | 12.95 | 13.20     | 13.45 |

| Outside Tip Width       | E1             | 0.510 | 0.520  | 0.530 | 12.95 | 13.20     | 13.45 |

| Molded Pack. Length     | D <sup>‡</sup> | 0.390 | 0.394  | 0.398 | 9.90  | 10.00     | 10.10 |

| Molded Pack. Width      | E <sup>‡</sup> | 0.390 | 0.394  | 0.398 | 9.90  | 10.00     | 10.10 |

| Pin 1 Corner Chamfer    | Χ              | 0.025 | 0.035  | 0.045 | 0.635 | 0.89      | 1.143 |

| Mold Draft Angle Top    | α              | 5     | 10     | 15    | 5     | 10        | 15    |

| Mold Draft Angle Bottom | β              | 5     | 12     | 15    | 5     | 12        | 15    |

Controlling Parameter.

<sup>&</sup>lt;sup>†</sup> Dimension "B" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B."

<sup>&</sup>lt;sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E." JEDEC equivalent:MS-022 AB

| Interrupts, Flag Bits                                  | PCON Register 23, 133                              |

|--------------------------------------------------------|----------------------------------------------------|

| A/D Converter Flag (ADIF Bit)20                        | BOR Bit                                            |

| CCP1 Flag (CCP1IF Bit)20, 48, 49                       | POR Bit                                            |

| CCP2 Flag (CCP2IF Bit)22                               | PICDEM-1 Low-Cost PICmicro Demo Board              |

| Interrupt on Change (RB7:RB4) Flag                     | PICDEM-2 Low-Cost PIC16CXX Demo Board 146          |

| (RBIF Bit)                                             | PICDEM-3 Low-Cost PIC16CXXX Demo Board             |

| PSP Read/Write Flag (PSPIF Bit)20                      | PICSTART® Plus Entry Level Development System 145  |

| RB0/INT Flag (INTF Bit)18                              | PIE1 Register                                      |

| SSP Flag (SSPIF Bit)20                                 | ADIE Bit                                           |

|                                                        | CCP1IE Bit                                         |

| TMR0 Overflow Flag (T0IF Bit)                          |                                                    |

| TMR1 Overflow Flag (TMR1IF Bit)                        | PSPIE Bit                                          |

| TMR2 to PR2 Match Flag (TMR2IF Bit)                    | RCIE Bit                                           |

| USART Receive Flag (RCIF Bit)20                        | SSPIE Bit                                          |

| USART Transmit Flag (TXIE Bit)20                       | TMR1IE Bit19                                       |

| K                                                      | TMR2IE Bit19                                       |

|                                                        | TXIE Bit19                                         |

| KeeLoq® Evaluation and Programming Tools148            | PIE2 Register21                                    |

| M                                                      | CCP2IE Bit21                                       |

| M                                                      | Pinout Descriptions                                |

| Master Clear (MCLR)7, 8                                | PIC16C63A/PIC16C73B                                |

| MCLR Reset, Normal Operation131, 133, 134              | PIC16C65B/PIC16C74B8                               |

| MCLR Reset, SLEEP131, 133, 134                         | PIR1 Register                                      |

| Memory Organization                                    | ADIF Bit                                           |

| Data Memory11                                          | CCP1IF Bit                                         |

| Program Memory11                                       | PSPIF Bit                                          |

| MPLAB Integrated Development Environment Software .147 | RCIF Bit                                           |

| Multi-Master Communication90                           |                                                    |

| Multi-Master Mode                                      | SSPIF Bit                                          |

| Walti-Waster Wode72                                    | TMR1IF Bit                                         |

| 0                                                      | TMR2IF Bit                                         |

| ODCODE Field Descriptions 143                          | TXIF Bit                                           |

| OPCODE Field Descriptions                              | PIR2 Register                                      |

| OPTION_REG Register                                    | CCP2IF Bit22                                       |

| INTEDG Bit17                                           | Pointer, FSR                                       |

| PS2:PS0 Bits                                           | POR. See Power-on Reset                            |

| <u>PSA B</u> it 17, 39                                 | PORTA 7, 8, 15                                     |

| RBPU Bit17                                             | Analog Port Pins                                   |

| T0CS Bit17, 39                                         | Initialization                                     |

| T0SE Bit17, 39                                         | PORTA Register27                                   |

| OSC1/CLKIN Pin                                         | RA3:RA0 and RA5 Port Pins                          |

| OSC2/CLKOUT Pin                                        | RA4/T0CKI Pin                                      |

| Oscillator Configuration128                            | RA5/SS/AN4 Pin                                     |

| HS128, 133                                             | TRISA Register                                     |

| LP 128, 133                                            | PORTA Register                                     |

| RC128, 130, 133                                        | PORTB                                              |

| XT128, 133                                             | · ·                                                |

| Oscillator, Timer1                                     | Initialization                                     |

| Oscillator, WDT                                        | PORTB Register                                     |

| Oscillator, WD1                                        | Pull-up Enable (RBPU Bit)                          |

| P                                                      | RB0/INT Edge Select (INTEDG Bit)17                 |

| P54                                                    | RB0/INT Pin, External                              |

| Packaging                                              | RB3:RB0 Port Pins                                  |

|                                                        | RB7:RB4 Interrupt on Change                        |

| Paging, Program Memory                                 | RB7:RB4 Interrupt on Change Enable (RBIE Bit) 18,  |

| Parallel Slave Port (PSP)                              | 138                                                |

| Block Diagram                                          | RB7:RB4 Interrupt on Change Flag (RBIF Bit) 18,30, |

| RE0/ <u>RD/</u> AN5 Pin                                | 138                                                |

| RE1/WR/AN6 Pin                                         | RB7:RB4 Port Pins                                  |

| RE2/CS/AN7 Pin                                         | TRISB Register                                     |

| Read Waveforms38                                       | PORTB Register                                     |

| Read/Write Enable (PSPIE Bit)19                        | PORTC                                              |

| Read/Write Flag (PSPIF Bit)20                          | Block Diagram                                      |

| Select (PSPMODE Bit)34, 35, 37                         | Initialization                                     |

| Write Waveforms37                                      | PORTC Register                                     |

| PCL Register 13, 14                                    |                                                    |

| PCLATH Register                                        | RC0/T1OSO/T1CKI Pin                                |

|                                                        | RC1/T1OSI/CCP2 Pin                                 |

|                                                        | RC2/CCP1 Pin                                       |

|                                                        | RC3/SCK/SCL Pin                                    |

| Overflow Interrupt41,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 43                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI Pin7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                |

| RC1/T1OSI/CCP2 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                |

| Special Event Trigger (CCP)43,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                |

| T1CON Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41                                                                                                                                                                                                                                                             |

| TMR1H Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41                                                                                                                                                                                                                                                             |

| TMR1L Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41                                                                                                                                                                                                                                                             |

| Timer2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                |

| Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 46                                                                                                                                                                                                                                                             |

| PR2 Register45,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50                                                                                                                                                                                                                                                             |

| SSP Clock Shift45,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                |

| T2CON Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                |

| TMR2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45                                                                                                                                                                                                                                                             |

| TMR2 to PR2 Match Enable (TMR2IE Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19                                                                                                                                                                                                                                                             |

| TMR2 to PR2 Match Flag (TMR2IF Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                |

| TMR2 to PR2 Match Interrupt45, 46,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50                                                                                                                                                                                                                                                             |

| Timing Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                |

| Acknowledge Sequence Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85                                                                                                                                                                                                                                                             |

| Baud Rate Generator with Clock Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73                                                                                                                                                                                                                                                             |

| BRG Reset Due to SDA Collision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                |

| Brown-out Reset1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63                                                                                                                                                                                                                                                             |

| Bus Collision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                |

| Start Condition Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 91                                                                                                                                                                                                                                                             |

| Bus Collision During a Restart Condition (Case 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                |

| Bus Collision During a Restart Condition (Case2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 93                                                                                                                                                                                                                                                             |