Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | A/D 6x12b                                                                  |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc773t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 2-1 PIC16C77X SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

|                      |             |                                      |                                                     |                         |                  |              |                 | •              | ,         |                          |                               |

|----------------------|-------------|--------------------------------------|-----------------------------------------------------|-------------------------|------------------|--------------|-----------------|----------------|-----------|--------------------------|-------------------------------|

| Address              | Name        | Bit 7                                | Bit 6                                               | Bit 5                   | Bit 4            | Bit 3        | Bit 2           | Bit 1          | Bit 0     | Value on:<br>POR,<br>BOR | Value on all other resets (2) |

| Bank 1               | •           | •                                    |                                                     |                         |                  |              | •               |                |           |                          |                               |

| 80h <sup>(4)</sup>   | INDF        | Addressing                           | this location                                       | uses content            | ts of FSR to add | dress data m | nemory (not a   | a physical rec | gister)   | 0000 0000                | 0000 0000                     |

| 81h                  | OPTION_REG  | RBPU                                 | INTEDG                                              | TOCS                    | T0SE             | PSA          | PS2             | PS1            | PS0       | 1111 1111                | 1111 1111                     |

| 82h <sup>(4)</sup>   | PCL         | Program Co                           | ounter's (PC)                                       | Least Signifi           | cant Byte        | !            |                 |                |           | 0000 0000                | 0000 0000                     |

| 83h <sup>(4)</sup>   | STATUS      | IRP                                  | RP1                                                 | RP0                     | TO               | PD           | Z               | DC             | С         | 0001 1xxx                | 000q quuu                     |

| 84h <sup>(4)</sup>   | FSR         | Indirect data memory address pointer |                                                     |                         |                  |              |                 |                | xxxx xxxx | uuuu uuuu                |                               |

| 85h                  | TRISA       | _                                    | — bit5 <sup>(5)</sup> PORTA Data Direction Register |                         |                  |              |                 |                |           |                          | 11 1111                       |

| 86h                  | TRISB       | PORTB Dat                            | a Direction F                                       | Register                |                  |              |                 |                |           | 1111 1111                | 1111 1111                     |

| 87h                  | TRISC       | PORTC Data Direction Register        |                                                     |                         |                  |              |                 |                |           | 1111 1111                | 1111 1111                     |

| 88h <sup>(5)</sup>   | TRISD       | PORTD Dat                            | ta Direction F                                      | Register                |                  |              |                 |                |           | 1111 1111                | 1111 1111                     |

| 89h <sup>(5)</sup>   | TRISE       | IBF                                  | OBF                                                 | IBOV                    | PSPMODE          | _            | PORTE Dat       | ta Direction E | Bits      | 0000 -111                | 0000 -111                     |

| 8Ah <sup>(1,4)</sup> | PCLATH      | _                                    | _                                                   | _                       | Write Buffer fo  | or the upper | 5 bits of the I | Program Cou    | inter     | 0 0000                   | 0 0000                        |

| 8Bh <sup>(4)</sup>   | INTCON      | GIE                                  | PEIE                                                | TOIE                    | INTE             | RBIE         | TOIF            | INTF           | RBIF      | 0000 000x                | 0000 000u                     |

| 8Ch                  | PIE1        | PSPIE <sup>(3)</sup>                 | ADIE                                                | RCIE                    | TXIE             | SSPIE        | CCP1IE          | TMR2IE         | TMR1IE    | 0000 0000                | 0000 0000                     |

| 8Dh                  | PIE2        | LVDIE                                | _                                                   | _                       | _                | BCLIE        | _               | _              | CCP2IE    | 0 00                     | 0 00                          |

| 8Eh                  | PCON        | _                                    | _                                                   | _                       | _                | _            | _               | POR            | BOR       | qq                       | uu                            |

| 8Fh                  | _           | Unimpleme                            | nted                                                |                         | •                |              |                 |                |           | _                        | _                             |

| 90h                  | _           | Unimpleme                            | nted                                                |                         |                  |              |                 |                |           | _                        | _                             |

| 91h                  | SSPCON2     | GCEN                                 | AKSTAT                                              | AKDT                    | AKEN             | RCEN         | PEN             | RSEN           | SEN       | 0000 0000                | 0000 0000                     |

| 92h                  | PR2         | Timer2 Peri                          | od Register                                         |                         |                  |              |                 |                |           | 1111 1111                | 1111 1111                     |

| 93h                  | SSPADD      | Synchronou                           | ıs Serial Port                                      | (I <sup>2</sup> C mode) | Address Regist   | er           |                 |                |           | 0000 0000                | 0000 0000                     |

| 94h                  | SSPSTAT     | SMP                                  | CKE                                                 | D/A                     | Р                | S            | R/W             | UA             | BF        | 0000 0000                | 0000 0000                     |

| 95h                  | _           | Unimpleme                            | nted                                                |                         |                  |              |                 |                |           | _                        | _                             |

| 96h                  | _           | Unimpleme                            | nted                                                |                         |                  |              |                 |                |           | _                        | _                             |

| 97h                  | _           | Unimpleme                            | nted                                                |                         |                  |              |                 |                |           | _                        | _                             |

| 98h                  | TXSTA       | CSRC                                 | TX9                                                 | TXEN                    | SYNC             | _            | BRGH            | TRMT           | TX9D      | 0000 -010                | 0000 -010                     |

| 99h                  | SPBRG       | Baud Rate                            | Generator Re                                        | egister                 |                  |              | '               |                |           | 0000 0000                | 0000 0000                     |

| 9Ah                  | _           | Unimpleme                            | nted                                                |                         |                  |              |                 |                |           | _                        | _                             |

| 9Bh                  | REFCON      | VRHEN                                | VRLEN                                               | VRHOEN                  | VRLOEN           | _            | _               | _              | _         | 0000                     | 0000                          |

| 9Ch                  | LVDCON      | _                                    | _                                                   | BGST                    | LVDEN            | LV3          | LV2             | LV1            | LV0       | 00 0101                  | 00 0101                       |

| 9Ah                  | _           | Unimplemented                        |                                                     |                         |                  |              |                 |                |           | _                        | _                             |

| 9Eh                  | ADRESL      | A/D Low Byte Result Register         |                                                     |                         |                  |              |                 |                |           | xxxx xxxx                | uuuu uuuu                     |

| 9Fh                  | ADCON1      | ADFM                                 | VCFG2                                               | VCFG1                   | VCFG0            | PCFG3        | PCFG2           | PCFG1          | PCFG0     | 0000 0000                | 0000 0000                     |

| egend.               | x = unknown |                                      |                                                     |                         |                  |              |                 |                | 1         | 1                        | 1                             |

x= unknown, u= unchanged, q= value depends on condition, -= unimplemented read as '0'. Legend:

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

<sup>3:</sup> Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

These registers can be addressed from any bank.

These registers/bits are not implemented on the 28-pin devices read as '0'.

### 3.2 PORTB and the TRISB Register

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISB bit (=0) will make the corresponding PORTB pin an output, i.e., put the contents of the output latch on the selected pin.

### **EXAMPLE 3-1: INITIALIZING PORTB**

```

BCF

STATUS, RPO

CLRF

PORTB

Initialize PORTB by

; clearing output

; data latches

BSF

STATUS. RPO

; Select Bank 1

MOVLW

0xCF

Value used to

; initialize data

: direction

MOVWF

TRISB

; Set RB<3:0> as inputs

; RB<5:4> as outputs

; RB<7:6> as inputs

```

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (OPTION\_REG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

The RB0 pin is multiplexed with the external interrupt (RB0/INT).

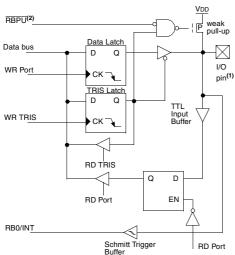

### FIGURE 3-4: BLOCK DIAGRAM OF RB0 PIN

Note 1: I/O pins have diode protection to VDD and Vss.

2: To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (OPTION\_REG<7>).

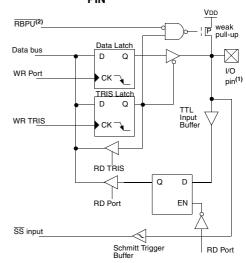

The RB1 pin is multiplexed with the SSP module slave select (RB1/SS).

## FIGURE 3-5: BLOCK DIAGRAM OF RB1/SS

Note 1: I/O pins have diode protection to VDD and VSS.

2: To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (OPTION\_REG<7>).

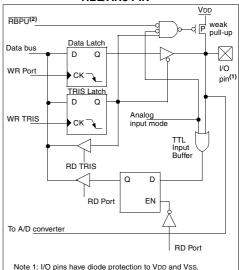

The RB2 pin is multiplexed with analog channel 8 (RB2/AN8).

# FIGURE 3-6: BLOCK DIAGRAM OF RB2/AN8 PIN

2: To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (OPTION\_REG<7>).

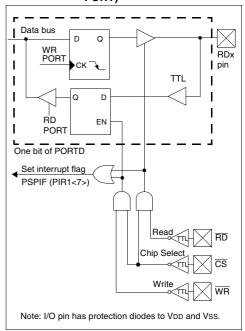

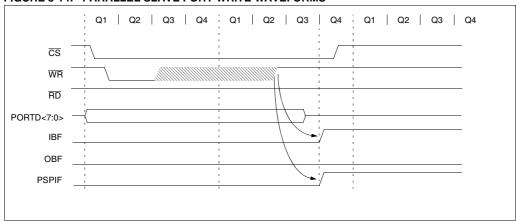

### 3.6 Parallel Slave Port

The Parallel Slave Port is implemented on the 40/44-pin devices only.

PORTD operates as an 8-bit wide Parallel Slave Port, or microprocessor port when control bit PSPMODE (TRISE<4>) is set. In slave mode it is asynchronously readable and writable by the external world through  $\overline{\text{RD}}$  control input pin RE0/ $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  control input pin RE1/ $\overline{\text{WR}}$ .

It can directly interface to an 8-bit microprocessor data bus. The external microprocessor can read or write the PORTD latch as an 8-bit latch. Setting bit PSPMODE enables port pin RE0/RD to be the RD input, RE1/WR to be the WR input and RE2/CS to be the CS (chip select) input. For this functionality, the corresponding data direction bits of the TRISE register (TRISE<2:0>) must be configured as inputs (set). The configuration bits, PCFG3:PCFG0 (ADCON1<3:0>) must be configured to make pins RE2:RE0 as digital I/O.

A write to the PSP occurs when both the  $\overline{CS}$  and  $\overline{WR}$  lines are first detected low. A read from the PSP occurs when both the  $\overline{CS}$  and  $\overline{RD}$  lines are first detected low.

FIGURE 3-13: PORTD AND PORTE BLOCK DIAGRAM (PARALLEL SLAVE PORT)

FIGURE 3-14: PARALLEL SLAVE PORT WRITE WAVEFORMS

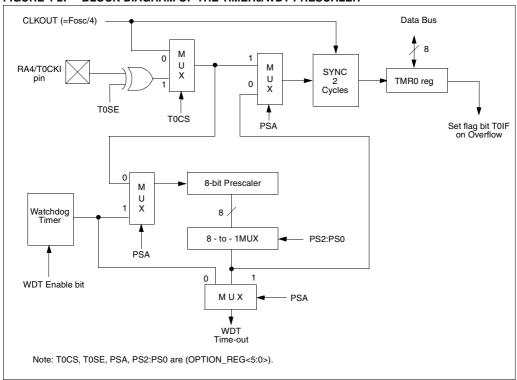

### 4.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

Note:

To avoid an unintended device RESET, a specific instruction sequence (shown in the PICmicro™ Mid-Range Reference Manual, DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

### 4.3 <u>Timer0 Interrupt</u>

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut off during SLEEP.

### FIGURE 4-2: BLOCK DIAGRAM OF THE TIMERO/WDT PRESCALER

### TABLE 4-1 REGISTERS ASSOCIATED WITH TIMERO

| Address               | Name       | Bit 7  | Bit 6       | Bit 5                         | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------------------|------------|--------|-------------|-------------------------------|-------|-------|-------|---------|---------|--------------------------|---------------------------|

| 01h,101h              | TMR0       | Timer0 | module's re | egister                       |       |       |       |         |         | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE    | PEIE        | TOIE                          | INTE  | RBIE  | TOIF  | INTF    | RBIF    | 0000 000x                | 0000 000u                 |

| 81h,181h              | OPTION_REG | RBPU   | INTEDG      | T0CS                          | T0SE  | PSA   | PS2   | PS1     | PS0     | 1111 1111                | 1111 1111                 |

| 85h                   | TRISA      | _      | _           | PORTA Data Direction Register |       |       |       | 11 1111 | 11 1111 |                          |                           |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

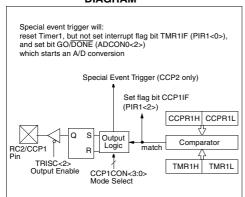

### 7.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- · driven High

- · driven Low

- · remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

FIGURE 7-3: COMPARE MODE OPERATION BLOCK DIAGRAM

### 7.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

Note: Clearing the CCP1CON register will force the RC2/CCP1 compare output latch to the default low level. This is not the data latch.

### 7.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 7.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

### 7.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1

The special trigger output of CCP2 resets the TMR1 register pair, and starts an A/D conversion (if the A/D module is enabled).

Note: The special event trigger from the CCP2 module will not set interrupt flag bit TMR1IF (PIR1<0>).

### TABLE 7-3 REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address               | Name    | Bit 7                               | Bit 6     | Bit 5       | Bit 4       | Bit 3         | Bit 2      | Bit 1       | Bit 0  | PC   | e on:<br>DR,<br>DR | all o | e on<br>other<br>ets |

|-----------------------|---------|-------------------------------------|-----------|-------------|-------------|---------------|------------|-------------|--------|------|--------------------|-------|----------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                                 | PEIE      | TOIE        | INTE        | RBIE          | TOIF       | INTF        | RBIF   | 0000 | 000x               | 0000  | 000u                 |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup>                | ADIF      | RCIF        | TXIF        | SSPIF         | CCP1IF     | TMR2IF      | TMR1IF | 0000 | 0000               | 0000  | 0000                 |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup>                | ADIE      | RCIE        | TXIE        | SSPIE         | CCP1IE     | TMR2IE      | TMR1IE | 0000 | 0000               | 0000  | 0000                 |

| 87h                   | TRISC   | PORTC Da                            | ta Dire   | ction Regis | ter         | •             |            |             |        | 1111 | 1111               | 1111  | 1111                 |

| 0Eh                   | TMR1L   | Holding reg                         | gister fo | r the Least | Significant | Byte of the   | 16-bit TMF | R1 register |        | xxxx | xxxx               | uuuu  | uuuu                 |

| 0Fh                   | TMR1H   | Holding reg                         | gister fo | r the Most  | Significant | Byte of the 1 | 6-bit TMR  | 1register   |        | xxxx | xxxx               | uuuu  | uuuu                 |

| 10h                   | T1CON   | _                                   | _         | T1CKPS1     | T1CKPS0     | T10SCEN       | T1SYNC     | TMR1CS      | TMR10N | 00   | 0000               | uu    | uuuu                 |

| 15h                   | CCPR1L  | Capture/Co                          | mpare     | /PWM regis  | ster1 (LSB) |               |            |             |        | xxxx | xxxx               | uuuu  | uuuu                 |

| 16h                   | CCPR1H  | Capture/Compare/PWM register1 (MSB) |           |             |             |               |            |             |        | xxxx | xxxx               | uuuu  | uuuu                 |

| 17h                   | CCP1CON | _                                   |           | CCP1X       | CCP1Y       | CCP1M3        | CCP1M2     | CCP1M1      | CCP1M0 | 00   | 0000               | 00    | 0000                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin, always maintain these bits clear.

#### 8.1.7 SLEEP OPERATION

In master mode all module clocks are halted, and the transmission/reception will remain in that state until the device wakes from sleep. After the device returns to normal mode, the module will continue to transmit/ receive data

In slave mode, the SPI transmit/receive shift register operates asynchronously to the device. This allows the device to be placed in sleep mode, and data to be shifted into the SPI transmit/receive shift register. When all 8-bits have been received, the MSSP interrupt flag bit will be set and if enabled will wake the device from sleep.

#### 8.1.8 EFFECTS OF A RESET

A reset disables the MSSP module and terminates the current transfer.

TABLE 8-1 REGISTERS ASSOCIATED WITH SPI OPERATION

| Address                | Name    | Bit 7                | Bit 6        | Bit 5      | Bit 4     | Bit 3      | Bit 2  | Bit 1  | Bit 0  | POR, BOR  | MCLR, WDT |

|------------------------|---------|----------------------|--------------|------------|-----------|------------|--------|--------|--------|-----------|-----------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE         | TOIE       | INTE      | RBIE       | TOIF   | INTF   | RBIF   | 0000 000x | 0000 000u |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF         | RCIF       | TXIF      | SSPIF      | CCP1IF | TMR2IF | TMR1IF | 0000 0000 | 0000 0000 |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE         | RCIE       | TXIE      | SSPIE      | CCP1IE | TMR2IE | TMR1IE | 0000 0000 | 0000 0000 |

| 13h                    | SSPBUF  | Synchronou           | ıs Serial Po | rt Receive | Buffer/Tr | ansmit Reg | ister  |        |        | xxxx xxxx | uuuu uuuu |

| 14h                    | SSPCON  | WCOL                 | SSPOV        | SSPEN      | СКР       | SSPM3      | SSPM2  | SSPM1  | SSPM0  | 0000 0000 | 0000 0000 |

| 94h                    | SSPSTAT | SMP                  | CKE          | D/Ā        | Р         | S          | R/W    | UA     | BF     | 0000 0000 | 0000 0000 |

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode. These bits are reserved on the 28-pin devices, always maintain these bits clear. Legend:

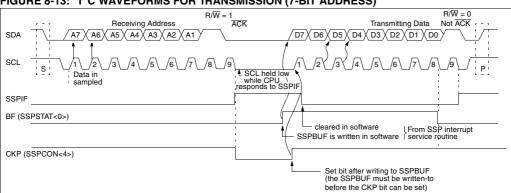

### FIGURE 8-13: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

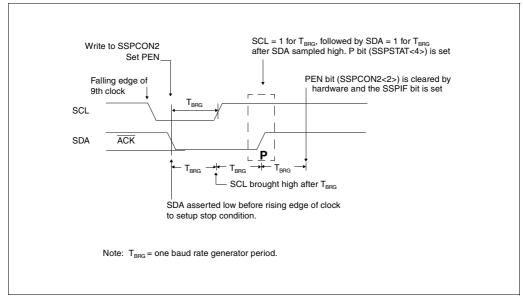

### 8.2.14 STOP CONDITION TIMING

A stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit PEN (SSPCON2<2>). At the end of a receive/transmit the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low . When the SDA line is sampled low, the baud rate generator is reloaded and counts down to 0. When the baud rate generator times out, the SCL pin will be brought high, and one T<sub>BRG</sub> (baud rate generator rollover count) later, the SDA pin will be de-asserted. When the SDA pin is sampled high

while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later the PEN bit is cleared and the SSPIF bit is set (Figure 8-31).

Whenever the firmware decides to take control of the bus, it will first determine if the bus is busy by checking the S and P bits in the SSPSTAT register. If the bus is busy, then the CPU can be interrupted (notified) when a Stop bit is detected (i.e. bus is free).

### 8.2.14.14 WCOL STATUS FLAG

If the user writes the SSPBUF when a STOP sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

FIGURE 8-31: STOP CONDITION RECEIVE OR TRANSMIT MODE

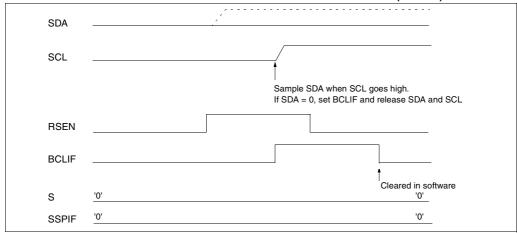

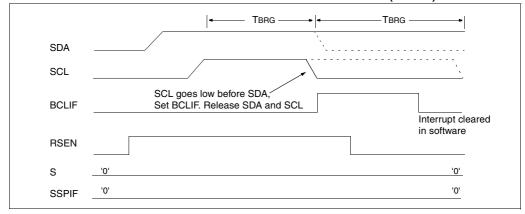

## 8.2.18.16 BUS COLLISION DURING A REPEATED START CONDITION

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user de-asserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0>, and counts down to 0. The SCL pin is then deasserted, and when sampled high, the SDA pin is sampled. If SDA is low, a bus collision has occurred (i.e. another master is attempting to transmit a data '0'). If

however SDA is sampled high then the BRG is reloaded and begins counting. If SDA goes from high to low before the BRG times out, no bus collision occurs, because no two masters can assert SDA at exactly the same time.

If, however, SCL goes from high to low before the BRG times out and SDA has not already been asserted, then a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition.

If at the end of the BRG time out both SCL and SDA are still high, the SDA pin is driven low, the BRG is reloaded, and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete (Figure 8-38).

FIGURE 8-38: BUS COLLISION DURING A REPEATED START CONDITION (CASE 1)

FIGURE 8-39: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

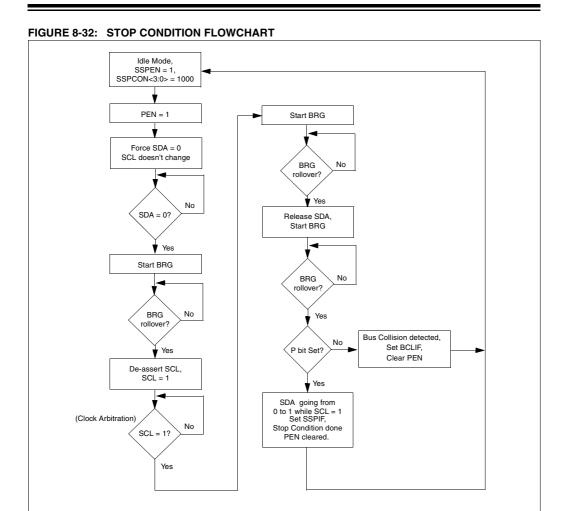

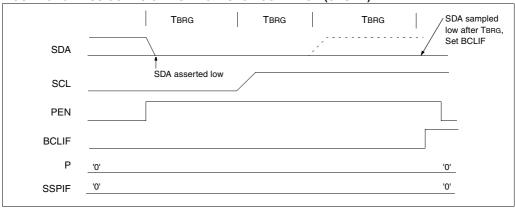

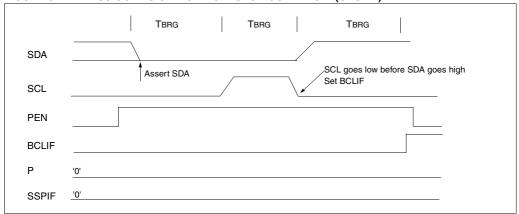

## 8.2.18.17 BUS COLLISION DURING A STOP CONDITION

Bus collision occurs during a STOP condition if:

- After the SDA pin has been de-asserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is de-asserted, SCL is sampled low before SDA goes high.

The STOP condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allow to float. When the pin is sampled high (clock arbitration), the baud rate generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0'. If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 8-40).

FIGURE 8-40: BUS COLLISION DURING A STOP CONDITION (CASE 1)

FIGURE 8-41: BUS COLLISION DURING A STOP CONDITION (CASE 2)

### TABLE 9-5 BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD<br>RATE<br>(K) | FOSC = 2 | % ERROR | SPBRG<br>value<br>(decimal) | 16 MHz<br>KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) | 10 MHz<br>KBAUD | %<br>ERROR | SPBRG<br>value<br>(decimal) | 7.16 MH<br>KBAUD | z<br>%<br>ERROR | SPBRG<br>value<br>(decimal) |

|---------------------|----------|---------|-----------------------------|-----------------|------------|-----------------------------|-----------------|------------|-----------------------------|------------------|-----------------|-----------------------------|

| 9.6                 | 9.615    | +0.16   | 129                         | 9.615           | +0.16      | 103                         | 9.615           | +0.16      | 64                          | 9.520            | -0.83           | 46                          |

| 19.2                | 19.230   | +0.16   | 64                          | 19.230          | +0.16      | 51                          | 18.939          | -1.36      | 32                          | 19.454           | +1.32           | 22                          |

| 38.4                | 37.878   | -1.36   | 32                          | 38.461          | +0.16      | 25                          | 39.062          | +1.7       | 15                          | 37.286           | -2.90           | 11                          |

| 57.6                | 56.818   | -1.36   | 21                          | 58.823          | +2.12      | 16                          | 56.818          | -1.36      | 10                          | 55.930           | -2.90           | 7                           |

| 115.2               | 113.636  | -1.36   | 10                          | 111.111         | -3.55      | 8                           | 125             | +8.51      | 4                           | 111.860          | -2.90           | 3                           |

| 250                 | 250      | 0       | 4                           | 250             | 0          | 3                           | NA              | -          | -                           | NA               | -               | -                           |

| 625                 | 625      | 0       | 1                           | NA              | -          | -                           | 625             | 0          | 0                           | NA               | -               | -                           |

| 1250                | 1250     | 0       | 0                           | NA              | -          | -                           | NA              | -          | -                           | NA               | -               | -                           |

| BAUD  | Fosc = 5 | .068 MHz | SPBRG     | 4 MHz  |       | SPBRG     | 3.579 MI | Ηz     | SPBRG     | 1 MHz  |        | SPBRG     | 32.768 I | кHz   | SPBRG     |

|-------|----------|----------|-----------|--------|-------|-----------|----------|--------|-----------|--------|--------|-----------|----------|-------|-----------|

| RATE  |          | %        | value     |        | %     | value     |          | %      | value     |        | %      | value     |          | %     | value     |

| (K)   | KBAUD    | ERROR    | (decimal) | KBAUD  | ERROR | (decimal) | KBAUD    | ERROR  | (decimal) | KBAUD  | ERROR  | (decimal) | KBAUD    | ERROR | (decimal) |

| 9.6   | 9.6      | 0        | 32        | NA     | -     | -         | 9.727    | +1.32  | 22        | 8.928  | -6.99  | 6         | NA       | -     | -         |

| 19.2  | 18.645   | -2.94    | 16        | 1.202  | +0.17 | 207       | 18.643   | -2.90  | 11        | 20.833 | +8.51  | 2         | NA       | -     | -         |

| 38.4  | 39.6     | +3.12    | 7         | 2.403  | +0.13 | 103       | 37.286   | -2.90  | 5         | 31.25  | -18.61 | 1         | NA       | -     | -         |

| 57.6  | 52.8     | -8.33    | 5         | 9.615  | +0.16 | 25        | 55.930   | -2.90  | 3         | 62.5   | +8.51  | 0         | NA       | -     | -         |

| 115.2 | 105.6    | -8.33    | 2         | 19.231 | +0.16 | 12        | 111.860  | -2.90  | 1         | NA     | -      | -         | NA       | -     | -         |

| 250   | NA       | -        | -         | NA     | -     | -         | 223.721  | -10.51 | 0         | NA     | -      | -         | NA       | -     | -         |

| 625   | NA       | -        | -         | NA     | -     | -         | NA       | -      | -         | NA     | -      | -         | NA       | -     | -         |

| 1250  | NA       | -        | -         | NA     | -     | -         | NA       | -      | -         | NA     | -      | -         | NA       | -     | -         |

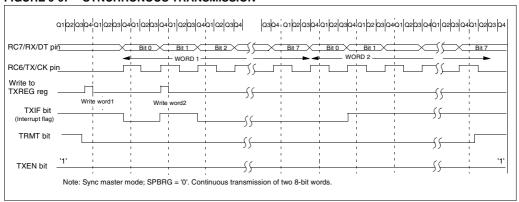

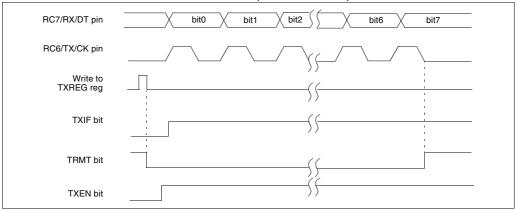

### FIGURE 9-9: SYNCHRONOUS TRANSMISSION

### FIGURE 9-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

### 11.7 Use of the CCP Trigger

An A/D conversion can be started by the "special event trigger" of the CCP module. This requires that the CCPnM<3:0> bits be programmed as 1011b and that the A/D module is enabled (ADON is set). When the trigger occurs, the GO/DONE bit will be set on Q2 to start the A/D conversion and the Timer1 counter will be reset to zero. Timer1 is reset to automatically repeat the A/D conversion cycle, with minimal software overhead (moving the ADRESH and ADRESL to the desired location). The appropriate analog input channel must be selected before the "special event trigger" sets the GO/DONE bit (starts a conversion cycle).

If the A/D module is not enabled (ADON is cleared), then the "special event trigger" will be ignored by the A/D module, but will still reset the Timer1 counter.

### 11.8 Effects of a RESET

A device reset forces all registers to their reset state. This forces the A/D module to be turned off, and any conversion is aborted. The value that is in the ADRESH and ADRESL registers are not modified. The ADRESH and ADRESL registers will contain unknown data after a Power-on Reset.

### 11.9 <u>Faster Conversion - Lower</u> <u>Resolution Trade-off</u>

Not all applications require a result with 12-bits of resolution, but may instead require a faster conversion time. The A/D module allows users to make the trade-off of conversion speed to resolution. Regardless of the resolution required, the acquisition time is the same. To speed up the conversion, the A/D module may be halted by clearing the GO/DONE bit after the desired number of bits in the result have been converted. Once the GO/DONE bit has been cleared, all of the remaining A/D result bits are '0'. The equation to determine the time before the GO/DONE bit can be switched is as follows:

Conversion time = N•TAD + 1TAD

Where: N = number of bits of resolution required, and 1TAD is the amplifier settling time.

Since TAD is based from the device oscillator, the user must use some method (a timer, software loop, etc.) to determine when the A/D GO/DONE bit may be cleared. Table 11-2 shows a comparison of time required for a conversion with 4-bits of resolution, versus the normal 12-bit resolution conversion. The example is for devices operating at 20 MHz. The A/D clock is programmed for 32 Tosc.

TABLE 11-2 4-BIT vs. 12-BIT CONVERSION TIMES

|               | Freq. | Resolution |         |  |  |

|---------------|-------|------------|---------|--|--|

|               | (MHz) | 4-bit      | 12-bit  |  |  |

| Tosc          | 20    | 50 ns      | 50 ns   |  |  |

| TAD = 32 Tosc | 20    | 1.6 μs     | 1.6 μs  |  |  |

| 1TAD+N•TAD    | 20    | 8 μs       | 20.8 μs |  |  |

### TABLE 15-9 A/D CONVERTER CHARACTERISTICS:

| Param<br>No. | Sym   | Characteristic                                       | Min   | Тур†                      | Max                 | Units | Conditions                                                                                                                                                                  |

|--------------|-------|------------------------------------------------------|-------|---------------------------|---------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A01          | NR    | Resolution                                           | _     | _                         | 12 bits             | bit   | Min. resolution for A/D is 1 mV,  VREF+ = AVDD = 4.896V,  VREF- = AVS8 = 0V,  VREF- > VAIN > VREF+                                                                          |

| A03          | EIL   | Integral error                                       | _     | _                         | +/-2 LSb            | -     | VREF+ =\AVD0 = 4.096V,<br>VREF- = AVSS = 0V,<br>VREF- \Leq VAIN \Leq VREF+                                                                                                  |

| A04          | EDL   | Differential error                                   | _     | _                         | +2 LSb<br>-1 LSb    |       | No missing codes to 12 bits<br>VREF+ = AV pD = 4,896V,<br>VREF- = AV3S = 0V,<br>VREF- ≤ VAN ≤ VREF+                                                                         |

| A06          | EOFF  | Offset error                                         | _     |                           | less than<br>±2 LSb |       | VREFT = AVDD = 4.096V,<br>VREF- = AVSS = 0V,<br>VREF- ≤ VAIN ≤ VREF+                                                                                                        |

| A07          | Egn   | Gain Error                                           |       |                           | +/- 2LSb            | LSb   | $\begin{split} & \text{VREF+} = \text{AVDD} = 4.096\text{V}, \\ & \text{VREF-} = \text{AVSS} = 0\text{V}, \\ & \text{VREF-} \leq \text{VAIN} \leq \text{VREF+} \end{split}$ |

| A10          | _     | Monotonicity                                         | \—\   | guaranteed <sup>(3)</sup> | _                   | _     | AVSS ≤ VAIN ≤ VREF+                                                                                                                                                         |

| A20          | VREF  | Reference voltage<br>(VREF+ VREF-)                   | 4.096 |                           | VDD +0.3V           | ٧     | Absolute minimum electrical spec to ensure 12-bit accuracy.                                                                                                                 |

| A21          | VREF+ | Reference V Nigh (AVDD or VREF+)                     | VREF  | _                         | AVDD                | ٧     | Min. resolution for A/D is 1 mV                                                                                                                                             |

| A22          | VREF- | Reference V Low<br>(Avss or VAEF-)                   | AVss  | _                         | VREF+               | ٧     | Min. resolution for A/D is 1 mV                                                                                                                                             |

| A25          | VAIN  | Analog input voltage                                 | VREFL | _                         | VREFH               | ٧     |                                                                                                                                                                             |

| A30          | ŽAIN  | Recommended<br>impedance of analog<br>voltage source | _     | _                         | 2.5                 | kΩ    |                                                                                                                                                                             |

| A50          | /REF  | VREF input current<br>(Note 2)                       | _     | _                         | 10                  | μА    | During VAIN acquisition.  Based on differential of VHOLD to VAIN.  To charge CHOLD see Section 11.0.  During A/D conversion cycle.                                          |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power down current spec includes any such leakage from the A/D module.

<sup>2:</sup> VREF current is from External VREF+, OR VREF-, or AVSS, or AVDD pin, whichever is selected as reference input.

<sup>3:</sup> The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

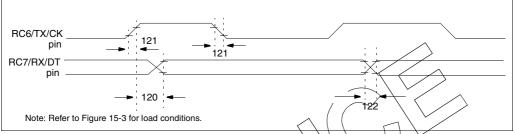

### FIGURE 15-14: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

### TABLE 15-15 USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                    |                         | Min | Typt | Max | Units | Conditions |

|--------------|----------|-----------------------------------|-------------------------|-----|------|-----|-------|------------|

| 120*         | TckH2dtV | SYNC XMIT (MASTER & SLAVE)        | PIC16 <b>C</b> 7774/773 | _   | _    | 80  | ns    |            |

|              |          | Clock high to data out valid      | PIC16LC774/773          | _   | _    | 100 | ns    |            |

| 121*         | Tckrf    | Clock out rise time and fall time | PIC16 <b>C</b> 774/773  | _   | _    | 45  | ns    |            |

|              |          | (Master Mode)                     | PIC16 <b>LC</b> 774/773 | _   | _    | 50  | ns    |            |

| 122*         | Tdtrf    | Data out rise time and fall time  | PIC16 <b>C</b> 774/773  | _   | _    | 45  | ns    |            |

|              |          |                                   | PIC16 <b>LC</b> 774/773 | _   | _    | 50  | ns    |            |

<sup>\*</sup> These parameters are characterized but not tested.

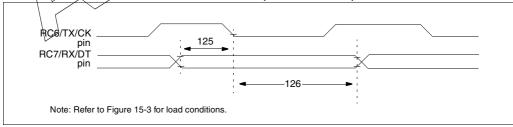

### FIGURE 15-15: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

### TABLE 15-16 USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter No. | Sym      | Characteristic                                                   | Min | Typ† | Max | Units | Conditions |

|---------------|----------|------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125*          | TdtV2ckL | SYNC RCV (MASTER & SLAVE) Data setup before CK ↓ (DT setup time) | 15  | 1    | 1   | ns    |            |

| 126*          | TckL2dtl | Data hold after CK ↓ (DT hold time)                              | 15  |      |     | ns    |            |

These parameters are characterized but not tested.

<sup>†:</sup> Data in "Typ" column is at \$V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>†:</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 17.0 PACKAGING INFORMATION

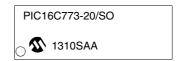

### 17.1 Package Marking Information

### 28-Lead PDIP (Skinny DIP)

### 28-Lead CERDIP Windowed

### 28-Lead SOIC

### 28-Lead SSOP

### Example

### Example

### Example

### Example

| Le | gend: MMM       | Microchip part number information                                       |

|----|-----------------|-------------------------------------------------------------------------|

|    | XXX             | Customer specific information*                                          |

|    | AA              | Year code (last 2 digits of calendar year)                              |

|    | BB              | Week code (week of January 1 is week '01')                              |

|    | С               | Facility code of the plant at which wafer is manufactured               |

|    |                 | O = Outside Vendor                                                      |

|    |                 | C = 5" Line                                                             |

|    |                 | S = 6" Line                                                             |

|    |                 | H = 8" Line                                                             |

|    | D               | Mask revision number                                                    |

|    | E               | Assembly code of the plant or country of origin in which                |

|    |                 | part was assembled                                                      |

| No | ote: In the eve | nt the full Microchip part number cannot be marked on one line, it will |

|    | be carried      | over to the next line thus limiting the number of available characters  |

\* Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

for customer specific information.

| INDEX                                             | С                                   |     |

|---------------------------------------------------|-------------------------------------|-----|

| A                                                 | Capture (CCP Module)                | 48  |

|                                                   | Block Diagram                       | 48  |

| A/D                                               | CCP Pin Configuration               |     |

| A/D Converter Enable (ADIE Bit)                   | CCPR1H:CCPR1L Registers             | 48  |

| A/D Converter Flag (ADIF Bit)                     | Changing Between Capture Prescalers | 48  |

| ADCONI Register                                   | Software Interrupt                  | 48  |

| ADDEC Parister                                    | Timer1 Mode Selection               |     |

| ADRES Register                                    | Capture/Compare/PWM (CCP)           |     |

| Analog Port Pins                                  | CCP1                                |     |

| Block Diagram                                     | CCP1CON Register                    |     |

| Configuring Analog Port119 Conversion time125     | CCPR1H Register                     |     |

| Conversions                                       | CCPR1L Register                     |     |

| converter characteristics                         | Enable (CCP1IE Bit)                 |     |

| Faster Conversion - Lower Resolution Tradeoff 125 | Flag (CCP1IF Bit)                   |     |

| Internal Sampling Switch (Rss) Impedence123       | RC2/CCP1 Pin                        | , - |

| Operation During Sleep126                         | CCP2                                |     |

| Sampling Requirements123                          | CCP2CON Register                    |     |

| Sampling Time                                     | CCPR2H Register                     |     |

| Source Impedance                                  | CCPR2L Register                     |     |

| Special Event Trigger (CCP)49                     | Enable (CCP2IE Bit)                 |     |

| A/D Conversion Clock                              | Flag (CCP2IF Bit)                   |     |

| ACK                                               | RC1/T1OSI/CCP2 Pin                  |     |

| Acknowledge Data bit, AKD56                       | Interaction of Two CCP Modules      |     |

| Acknowledge Pulse                                 | Timer Resources                     |     |

| Acknowledge Sequence Enable bit, AKE56            | CCP1CON                             |     |

| Acknowledge Status bit, AKS56                     | CCP1CON Register                    |     |

| ADCON0 Register117                                | CCP1M3:CCP1M0 BitsCCP1X:CCP1Y Bits  |     |

| ADCON1 Register117, 118                           | CCP2CON                             |     |

| ADRES117                                          | CCP2CON Register                    |     |

| ADRES Register 13, 14, 117, 126                   | CCP2M3:CCP2M0 Bits                  |     |

| AKD56                                             | CCP2X:CCP2Y Bits                    |     |

| AKE56                                             | CCPR1H Register                     |     |

| AKS 56, 79                                        | CCPR1L Register                     |     |

| Application Note AN578, "Use of the SSP           | CCPR2H Register                     |     |

| Module in the I2C Multi-Master Environment." 63   | CCPR2L Register                     |     |

| Architecture                                      | CKE                                 |     |

| PIC16C63A/PIC16C73B Block Diagram5                | CKP                                 |     |

| PIC16C65B/PIC16C74B Block Diagram6                | Clock Polarity Select bit, CKP      |     |

| Assembler                                         | Code Examples                       |     |

| MPASM Assembler147                                | Loading the SSPBUF register         | 58  |

| В                                                 | Code Protection                     |     |

|                                                   | Compare (CCP Module)                |     |

| Banking, Data Memory11, 16                        | Block Diagram                       |     |

| Baud Rate Generator73                             | CCP Pin Configuration               | 49  |

| BF54, 64, 79, 82                                  | CCPR1H:CCPR1L Registers             |     |

| Block Diagrams                                    | Software Interrupt                  |     |

| Baud Rate Generator                               | Special Event Trigger               |     |

| I <sup>2</sup> C Master Mode                      | Timer1 Mode Selection               | 49  |

| 1 <sup>2</sup> C Module                           | Configuration Bits                  | 127 |

| SSP (I <sup>2</sup> C Mode)                       | Conversion Considerations           | 187 |

| SSP (SPI Mode)57 BOR. See Brown-out Reset         | D                                   |     |

| BRG73                                             | =                                   |     |

|                                                   | D/Ā                                 | 54  |

| Brown-out Reset (BOR)                             | Data Memory                         |     |

| Buffer Full bit, BF                               | Bank Select (RP1:RP0 Bits)          |     |

| Buffer Full Status bit, BF                        | General Purpose Registers           |     |

| Bus Arbitration                                   | Register File Map                   |     |

| Bus Collision                                     | Special Function Registers          |     |

| Section                                           | Data/Address bit, D/A               | 54  |

| Bus Collision During a RESTART Condition          | DC Characteristics                  |     |

| Bus Collision During a Start Condition            | PIC16C73                            |     |

| Bus Collision During a Stop Condition             | PIC16C74                            |     |

| 240 Comoion Duning a Grop Condition               | Development Support                 |     |

|                                                   | Development Tools                   |     |

|                                                   | Device Differences                  | 187 |

# BIT/REGISTER CROSS-REFERENCE LIST

| ADCC1-ADCC0   | ADCONO.7.C    |

|---------------|---------------|

| ADCS1:ADCS0   |               |

| ADIE          |               |

| ADIF          |               |

| ADON          |               |

| BF            |               |

| BOR           |               |

| BRGH          |               |

| C             |               |

| CCP1IE        | PIE1<2>       |

| CCP1IF        | PIR1<2>       |

| CCP1M3:CCP1M0 | CCP1CON<3:0>  |

| CCP1X:CCP1Y   | CCP1CON<5:4>  |

| CCP2IE        | PIE2<0>       |

| CCP2IF        | PIR2<0>       |

| CCP2M3:CCP2M0 | CCP2CON<3:0>  |

| CCP2X:CCP2Y   |               |

| CHS2:CHS0     |               |

| CKE           |               |

| CKP           |               |

| CREN          |               |

|               |               |

| CSRC          |               |

| D/A           |               |

| DC            |               |

| FERR          |               |

| GIE           |               |

| GO/DONE       |               |

| IBF           | TRISE<7>      |

| IBOV          | TRISE<5>      |

| INTE          | INTCON<4>     |

| INTEDG        | OPTION_REG<6> |

| INTF          | INTCON<1>     |

| IRP           | STATUS<7>     |

| OBF           |               |

| OERR          |               |

| P             |               |

| PCFG2:PCFG0   |               |

| PD            |               |

| PEIE          |               |

|               |               |

| POR           |               |

| PS2:PS0       | _             |

| PSA           |               |

| PSPIE         |               |

| PSPIF         |               |

| PSPMODE       |               |

| R/W           |               |

| RBIE          |               |

| RBIF          |               |

| RBPU          | OPTION_REG<7> |

| RCIE          | PIE1<5>       |

| RCIF          | PIR1<5>       |

| RP1:RP0       | STATUS<6:5>   |

| RX9           | RCSTA<6>      |

| RX9D          |               |

| S             |               |

| SMP           |               |

| SPEN          |               |

| SREN          |               |

| SSPEN         |               |

| SSPIE         |               |

|               |               |

| SSPIF         |               |

| SSPM3:SSPM0   |               |

| SSPOV         |               |

| SYNC          | I XS IA<4>    |

| T0CS            | OPTION_REG<5> |

|-----------------|---------------|

| TOIE            | INTCON<5>     |

| TOIF            | INTCON<2>     |

| T0SE            | OPTION_REG<4> |

| T1CKPS1:T1CKPS0 | T1CON<5:4>    |

| T10SCEN         | T1CON<3>      |

| T1SYNC          | T1CON<2>      |

| T2CKPS1:T2CKPS0 | T2CON<1:0>    |

| TMR1CS          | T1CON<1>      |

| TMR1IE          | PIE1<0>       |

| TMR1IF          | PIR1<0>       |

| TMR1ON          | T1CON<0>      |

| TMR2IE          | PIE1<1>       |

| TMR2IF          | PIR1<1>       |

| TMR2ON          | T2CON<2>      |

| TO              | STATUS<4>     |

| TOUTPS3:TOUTPS0 | T2CON<6:3>    |

| TRMT            | TXSTA<1>      |

| TX9             | TXSTA<6>      |

| TX9D            | TXSTA<0>      |

| TXEN            | TXSTA<5>      |

| TXIE            | PIE1<4>       |

| TXIF            | PIR1<4>       |

| UA              | SSPSTAT<1>    |

| WCOL            | SSPCON<7>     |

| Z               | STATUS<2>     |