Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                              |

| Data Converters            | A/D 6x12b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc773t-so |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

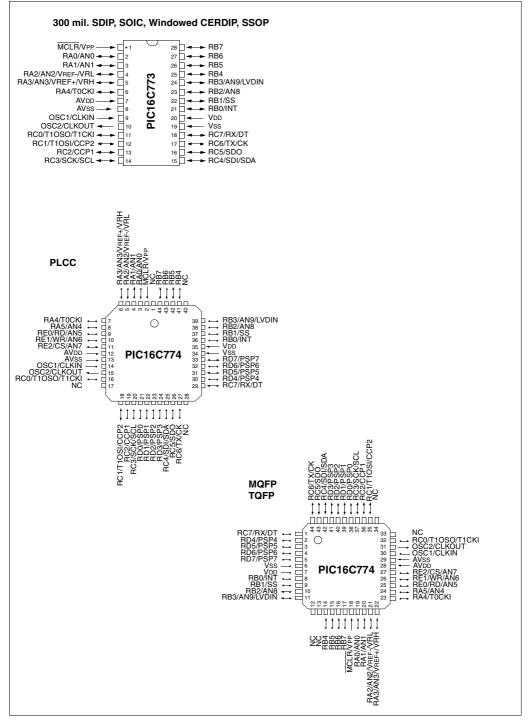

### **Pin Diagrams**

| TABLE 2-1 | PIC16C77X SPECIAL FUNCTION REGISTER SUMMARY | (Cont.'d) |  |

|-----------|---------------------------------------------|-----------|--|

|           | FICTUCITY OF LOAL TONGTION MEDISTEN SUMMANT | (Cont.u)  |  |

| Address               | Name       | Bit 7         | Bit 6          | Bit 5         | Bit 4           | Bit 3        | Bit 2           | Bit 1         | Bit 0   | Value on:<br>POR,<br>BOR | Value on all<br>other resets<br>(2) |

|-----------------------|------------|---------------|----------------|---------------|-----------------|--------------|-----------------|---------------|---------|--------------------------|-------------------------------------|

| Bank 2                |            |               |                |               |                 |              |                 |               |         |                          |                                     |

| 100h <sup>(4)</sup>   | INDF       | Addressing    | this location  | uses content  | s of FSR to ad  | dress data m | nemory (not a   | a physical re | gister) | 0000 0000                | 0000 0000                           |

| 101h                  | TMR0       | Timer0 mod    | lule's registe | r             |                 |              |                 |               |         | xxxx xxxx                | uuuu uuuu                           |

| 102h <sup>(4)</sup>   | PCL        | Program Co    | ounter's (PC)  | Least Signifi | cant Byte       |              |                 |               |         | 0000 0000                | 0000 0000                           |

| 103h <sup>(4)</sup>   | STATUS     | IRP           | RP1            | RP0           | TO              | PD           | Z               | DC            | С       | 0001 1xxx                | 000q quuu                           |

| 104h <sup>(4)</sup>   | FSR        | Indirect data | a memory ad    | dress pointer |                 |              |                 |               |         | xxxx xxxx                | uuuu uuuu                           |

| 105h                  | -          | Unimpleme     | nted           |               |                 |              |                 |               |         | _                        | -                                   |

| 106h                  | PORTB      | PORTB Dat     | a Latch whe    | n written: PO | RTB pins wher   | n read       |                 |               |         | xxxx 11xx                | uuuu 11uu                           |

| 107h                  | —          | Unimpleme     | nted           |               |                 |              |                 |               |         | —                        | —                                   |

| 108h                  | —          | Unimpleme     | nted           |               |                 |              |                 |               |         | _                        | —                                   |

| 109h                  | —          | Unimpleme     | nted           |               | n               |              |                 |               |         | —                        | —                                   |

| 10Ah <sup>(1,4)</sup> | PCLATH     | —             | —              | -             | Write Buffer fo | or the upper | 5 bits of the I | Program Cou   | Inter   | 0 0000                   | 0 0000                              |

| 10Bh <sup>(4)</sup>   | INTCON     | GIE           | PEIE           | TOIE          | INTE            | RBIE         | TOIF            | INTF          | RBIF    | 0000 000x                | 0000 000u                           |

| 10Ch-<br>10Fh         | -          | Unimpleme     | nted           | -             | ·               |              |                 |               |         | —                        | -                                   |

| Bank 3                |            |               |                |               |                 |              |                 |               |         |                          |                                     |

| 180h <sup>(4)</sup>   | INDF       | Addressing    | this location  | uses content  | s of FSR to ad  | dress data m | nemory (not a   | a physical re | gister) | 0000 0000                | 0000 0000                           |

| 181h                  | OPTION_REG | RBPU          | INTEDG         | TOCS          | TOSE            | PSA          | PS2             | PS1           | PS0     | 1111 1111                | 1111 1111                           |

| 182h <sup>(4)</sup>   | PCL        | Program Co    | ounter's (PC)  | Least Signif  | icant Byte      |              |                 |               |         | 0000 0000                | 0000 0000                           |

| 183h <sup>(4)</sup>   | STATUS     | IRP           | RP1            | RP0           | TO              | PD           | z               | DC            | С       | 0001 1xxx                | 000q quuu                           |

| 184h <sup>(4)</sup>   | FSR        | Indirect data | a memory ad    | dress pointer |                 |              |                 |               |         | xxxx xxxx                | uuuu uuuu                           |

| 185h                  | -          | Unimpleme     | nted           |               |                 |              |                 |               |         | _                        | -                                   |

| 186h                  | TRISB      | PORTB Dat     | a Direction F  | Register      |                 |              |                 |               |         | 1111 1111                | 1111 1111                           |

| 187h                  | —          | Unimpleme     | nted           |               |                 |              |                 |               |         | —                        | —                                   |

| 188h                  | _          | Unimpleme     | Unimplemented  |               |                 |              |                 |               |         |                          | —                                   |

| 189h                  | -          | Unimpleme     | nted           |               | 4               |              |                 |               |         | —                        | -                                   |

| 18Ah <sup>(1,4)</sup> | PCLATH     | —             | —              | —             | Write Buffer fe | or the upper | 5 bits of the I | Program Cou   | inter   | 0 0000                   | 0 0000                              |

| 18Bh <sup>(4)</sup>   | INTCON     | GIE           | PEIE           | TOIE          | INTE            | RBIE         | TOIF            | INTF          | RBIF    | 0000 000x                | 0000 000u                           |

| 18Ch-<br>18Fh         | -          | Unimplemented |                |               |                 |              |                 |               |         | —                        | -                                   |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

4: These registers can be addressed from any bank.

5: These registers/bits are not implemented on the 28-pin devices read as '0'.

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although STATUS bits may be affected).

A simple program to clear RAM locations 20h-2Fh using indirect addressing is shown in Example 2-1.

#### EXAMPLE 2-1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT     | incf<br>btfss | FSR<br>INDF<br>FSR<br>FSR,4 | ; to RAM<br>;clear INDF register<br>;inc pointer<br>;all done? |

|----------|---------------|-----------------------------|----------------------------------------------------------------|

|          | goto          | NEX.L.                      | ;NO, clear next                                                |

| CONTINUE |               |                             |                                                                |

|          | :             |                             | ;YES, continue                                                 |

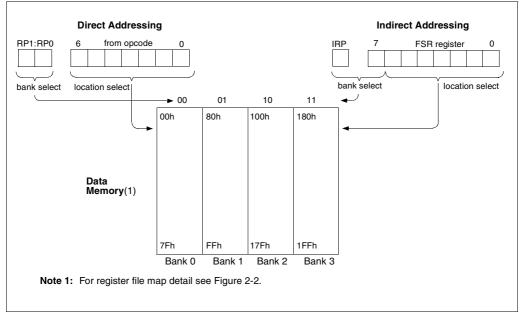

An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-11.

## FIGURE 2-11: DIRECT/INDIRECT ADDRESSING

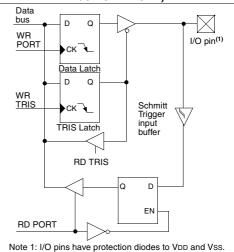

## 3.5 PORTE and TRISE Register

This section is applicable to the 40/44-pin devices only.

PORTE has three pins RE0/RD/AN5, RE1/ $\overline{WR}$ /AN6 and RE2/ $\overline{CS}$ /AN7, which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

I/O PORTE becomes control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs). Ensure ADCON1 is configured for digital I/O. In this mode the input buffers are TTL.

Figure 3-12 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected as an analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

Note: On a Power-on Reset these pins are configured as analog inputs.

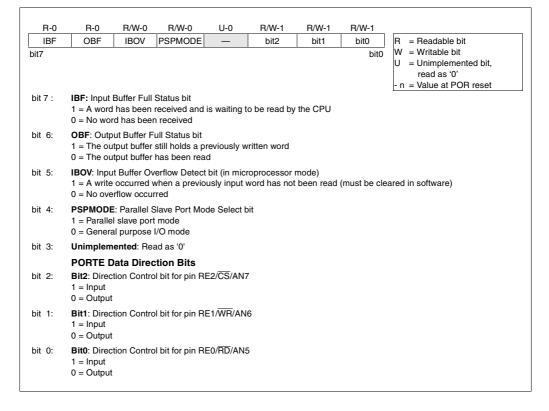

### FIGURE 3-12: TRISE REGISTER (ADDRESS 89h)

#### 5.0 TIMER1 MODULE

The Timer1 module timer/counter has the following features:

- 16-bit timer/counter (Two 8-bit registers; TMR1H and TMR1L)

- Readable and writable (Both registers)

- · Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- · Reset from CCP module trigger

Timer1 has a control register, shown in Figure 5-1. Timer1 can be enabled/disabled by setting/clearing control bit TMR1ON (T1CON<0>).

Figure 5-3 is a simplified block diagram of the Timer1 module.

Additional information on timer modules is available in the PICmicro™ Mid-Range Reference Manual, (DS33023).

#### 5.1 **Timer1 Operation**

Timer1 can operate in one of these modes:

- · As a timer

- · As a synchronous counter

- As an asynchronous counter

The operating mode is determined by the clock select bit. TMR1CS (T1CON<1>).

In timer mode, Timer1 increments every instruction cycle. In counter mode, it increments on every rising edge of the external clock input.

When the Timer1 oscillator is enabled (T1OSCEN is set), the RC1/T1OSI and RC0/T1OSO/T1CKI pins become inputs. That is, the TRISC<1:0> value is ignored.

Timer1 also has an internal "reset input". This reset can be generated by the CCP module (Section 7.0).

#### T1CON: TIMER1 CONTROL REGISTER (ADDRESS 10h) U-0 U-0 R/W-0 R/W-0 B/W-0 R/W-0 **B/W-0** R/W-0 T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON R = Readable bit W = Writable bit bit7 bit0 = Unimplemented bit, U read as '0' n = Value at POR reset bit 7-6: Unimplemented: Read as '0' bit 5-4: T1CKPS1:T1CKPS0: Timer1 Input Clock Prescale Select bits 11 = 1:8 Prescale value 10 = 1:4 Prescale value 01 = 1:2 Prescale value 00 = 1:1 Prescale value T1OSCEN: Timer1 Oscillator Enable Control bit hit 3 1 = Oscillator is enabled 0 = Oscillator is shut off Note: The oscillator inverter and feedback resistor are turned off to eliminate power drain T1SYNC: Timer1 External Clock Input Synchronization Control bit bit 2: TMR1CS = 11 = Do not synchronize external clock input 0 = Synchronize external clock input TMR1CS = 0This bit is ignored. Timer1 uses the internal clock when TMR1CS = 0. TMR1CS: Timer1 Clock Source Select bit bit 1: 1 = External clock from pin RC0/T1OSO/T1CKI (on the rising edge) 0 = Internal clock (Fosc/4)

## FIGURE 5-1:

- 1 = Enables Timer1

- 0 = Stops Timer1

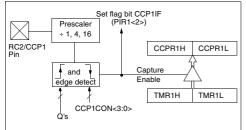

## 7.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RC2/CCP1. An event is defined as:

- · every falling edge

- · every rising edge

- · every 4th rising edge

- every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the interrupt request flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 7.1.1 CCP PIN CONFIGURATION

In Capture mode, the RC2/CCP1 pin should be configured as an input by setting the TRISC<2> bit.

| Note: | If the RC2/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

# FIGURE 7-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 7.1.2 TIMER1 MODE SELECTION

Timer1 must be running in timer mode or synchronized counter mode for the CCP module to use the capture feature. In asynchronous counter mode, the capture operation may not work.

#### 7.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in operating mode.

### 7.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in capture mode, the prescaler counter is cleared. This means that any reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 7-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

## EXAMPLE 7-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

#### 7.3.3 SET-UP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the TRISC<2> bit.

- 4. Set the TMR2 prescale value and enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

## TABLE 7-4 EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 20 MHz

| PWM Frequency              | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|----------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                  | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits)  | 10       | 10       | 10        | 8         | 7         | 5.5       |

#### TABLE 7-5 REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Address               | Name    | Bit 7                | Bit 6                               | Bit 5      | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value<br>PC<br>BC | ,    | all o | e on<br>other<br>sets |

|-----------------------|---------|----------------------|-------------------------------------|------------|---------|---------|--------|---------|---------|-------------------|------|-------|-----------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE                                | TOIE       | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000              | 000x | 0000  | 000u                  |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup> | ADIF                                | RCIF       | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000              | 0000 | 0000  | 0000                  |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup> | ADIE                                | RCIE       | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000              | 0000 | 0000  | 0000                  |

| 87h                   | TRISC   | PORTC Da             | ata Directio                        | n Register |         |         |        |         |         | 1111              | 1111 | 1111  | 1111                  |

| 11h                   | TMR2    | Timer2 mo            | dule's registe                      | er         |         |         |        |         |         | 0000              | 0000 | 0000  | 0000                  |

| 92h                   | PR2     | Timer2 mo            | dule's period                       | l register |         |         |        |         |         | 1111              | 1111 | 1111  | 1111                  |

| 12h                   | T2CON   | —                    | TOUTPS3                             | TOUTPS2    | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000              | 0000 | -000  | 0000                  |

| 15h                   | CCPR1L  | Capture/Co           | Capture/Compare/PWM register1 (LSB) |            |         |         |        |         |         |                   | xxxx | uuuu  | uuuu                  |

| 16h                   | CCPR1H  | Capture/Co           | Capture/Compare/PWM register1 (MSB) |            |         |         |        |         |         |                   | xxxx | uuuu  | uuuu                  |

| 17h                   | CCP1CON | —                    | _                                   | CCP1X      | CCP1Y   | CCP1M3  | CCP1M2 | CCP1M1  | CCP1M0  | 00                | 0000 | 00    | 0000                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PWM and Timer2.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin, always maintain these bits clear.

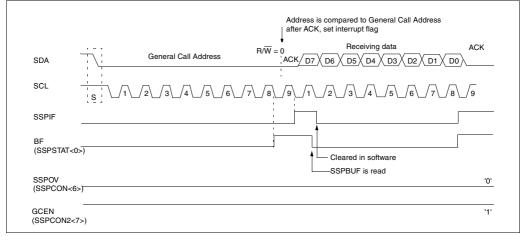

#### 8.2.2 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the START condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all 0's with R/W = 0

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> is set). Following a start-bit detect, 8-bits are shifted into SSPSR and the address is compared against SSPADD, and is also compared to the general call address, fixed in hardware. If the general call address matches, the SSPSR is transfered to the SSPBUF, the BF flag is set (eighth bit), and on the falling edge of the ninth bit ( $\overline{ACK}$  bit) the SSPIF flag is set.

When the interrupt is serviced. The source for the interrupt can be checked by reading the contents of the SSPBUF to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match, and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when GCEN is set while the slave is configured in 10-bit address mode, then the second half of the address is not necessary, the UA bit will not be set, and the slave will begin receiving data after the acknowledge (Figure 8-16).

FIGURE 8-16: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE (7 OR 10-BIT MODE)

#### 8.2.6 MULTI-MASTER OPERATION

In multi-master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored, for abitration, to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

#### 8.2.7 I<sup>2</sup>C MASTER OPERATION SUPPORT

Master Mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON and by setting the SSPEN bit. Once master mode is enabled, the user has six options.

- Assert a start condition on SDA and SCL.

- Assert a Repeated Start condition on SDA and SCL.

- Write to the SSPBUF register initiating transmission of data/address.

- Generate a stop condition on SDA and SCL.

- Configure the I<sup>2</sup>C port to receive data.

- Generate an Acknowledge condition at the end of a received byte of data.

- Note: The MSSP Module, when configured in I<sup>2</sup>C Master Mode, does not allow queueing of events. For instance: The user is not allowed to initiate a start condition, and immediately write the SSPBUF register to initiate transmission before the START condition is complete. In this case the SSPBUF will not be written to, and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

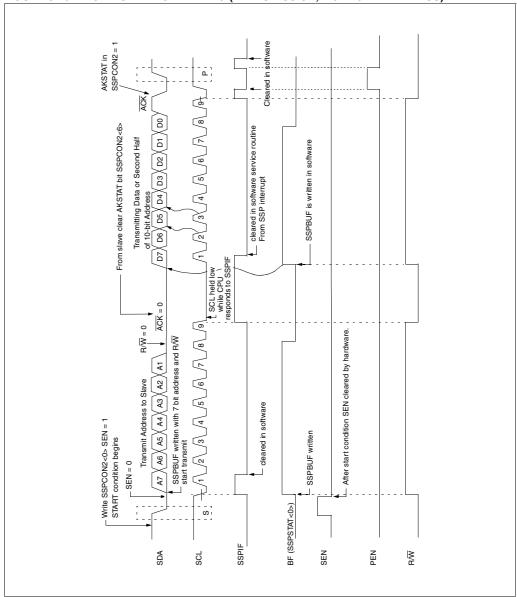

#### 8.2.7.4 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the  $l^2C$  bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write ( $R/\overline{W}$ ) bit. In this case, the  $R/\overline{W}$  bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

In Master receive mode the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/ $\overline{W}$  bit. In this case the R/ $\overline{W}$  bit will be logic '1'. Thus the first byte transmitted is a 7-bit slave address followed by a '1' to indicate receive bit. Serial data is received via SDA while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions indicate the beginning and end of transmission.

The baud rate generator used for SPI mode operation is now used to set the SCL clock frequency for either 100 kHz, 400 kHz, or 1 MHz  $I^2C$  operation. The baud rate generator reload value is contained in the lower 7 bits of the SSPADD register. The baud rate generator will automatically begin counting on a write to the SSP-BUF. Once the given operation is complete (i.e. transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state

A typical transmit sequence would go as follows:

- a) The user generates a Start Condition by setting the START enable bit (SEN) in SSPCON2.

- b) SSPIF is set. The module will wait the required start time before any other operation takes place.

- c) The user loads the SSPBUF with address to transmit.

- d) Address is shifted out the SDA pin until all 8 bits are transmitted.

- e) The MSSP Module shifts in the ACK bit from the slave device, and writes its value into the SSPCON2 register (SSPCON2<6>).

- f) The module generates an interrupt at the end of the ninth clock cycle by setting SSPIF.

- g) The user loads the SSPBUF with eight bits of data.

- h) DATA is shifted out the SDA pin until all 8 bits are transmitted.

FIGURE 8-26: I<sup>2</sup>C MASTER MODE TIMING (TRANSMISSION, 7 OR 10-BIT ADDRESS)

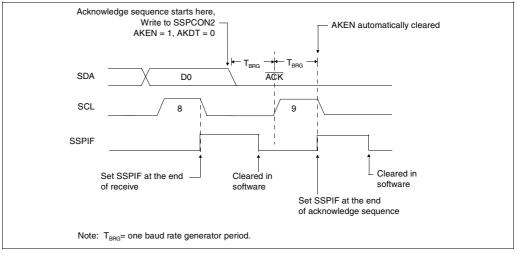

#### 8.2.13 ACKNOWLEDGE SEQUENCE TIMING

An acknowledge sequence is enabled by setting the acknowledge sequence enable bit, AKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the acknowledge data bit is presented on the SDA pin. If the user wishes to generate an acknowledge, then the AKDT bit should be cleared. If not, the user should set the AKDT bit before starting an acknowledge sequence. The baud rate generator then counts for one rollover period ( $T_{BRG}$ ), and the SCL pin is de-asserted (pulled high). When the SCL pin is sampled high (clock arbitration), the baud

rate generator counts for  $T_{BRG}$ . The SCL pin is then pulled low. Following this, the AKEN bit is automatically cleared, the baud rate generator is turned off, and the SSP module then goes into IDLE mode. (Figure 8-29)

#### 8.2.13.13 WCOL STATUS FLAG

If the user writes the SSPBUF when an acknowledege sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 8-29: ACKNOWLEDGE SEQUENCE WAVEFORM

#### 8.2.18.17 BUS COLLISION DURING A STOP CONDITION

Bus collision occurs during a STOP condition if:

- After the SDA pin has been de-asserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is de-asserted, SCL is sampled low before SDA goes high.

The STOP condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allow to float. When the pin is sampled high (clock arbitration), the baud rate generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0'. If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 8-40).

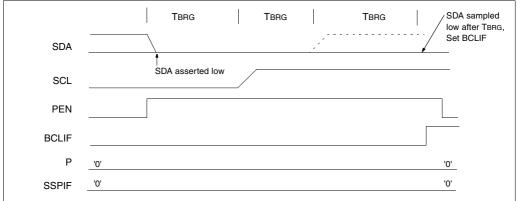

## FIGURE 8-40: BUS COLLISION DURING A STOP CONDITION (CASE 1)

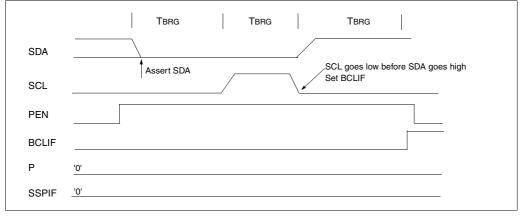

## FIGURE 8-41: BUS COLLISION DURING A STOP CONDITION (CASE 2)

# PIC16C77X

NOTES:

## FIGURE 10-2: REFCON: VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0                                        | R/W-0                                                                                                                                                                                       | R/W-0        | R/W-0        | U-0        | U-0      | U-0       | U-0       |                  |  |  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|------------|----------|-----------|-----------|------------------|--|--|

| VRHEN                                        | VRLEN                                                                                                                                                                                       | VRHOEN       | VRLOEN       | —          | —        | —         | —         | R = Readable bit |  |  |

| bit7 bit0 bit0 bit0 bit0 bit0 bit0 bit0 bit0 |                                                                                                                                                                                             |              |              |            |          |           |           |                  |  |  |

| bit 7:                                       | bit 7: VRHEN: Voltage Reference High Enable bit (VRH = 4.096V)<br>1 = Enabled, powers up reference generator<br>0 = Disabled, powers down reference generator if unused by LVD, BOR, or VRL |              |              |            |          |           |           |                  |  |  |

| bit 6:                                       | VRLEN: Volt<br>1 = Enabled,<br>0 = Disabled                                                                                                                                                 | powers up    | reference ge | nerator    |          |           | BOR, or ' | VRH              |  |  |

| bit 5:                                       |                                                                                                                                                                                             |              |              |            |          |           |           |                  |  |  |

| bit 4:                                       | VRLOEN: Lo<br>1 = Enabled,<br>0 = Disabled                                                                                                                                                  | VRL analog   | reference is | s presente | d on RA2 | if enable | d (VRLEN  | l = 1)           |  |  |

| bit 3-0:                                     | Unimpleme                                                                                                                                                                                   | nted: Read a | as '0'       |            |          |           |           |                  |  |  |

## 10.1 Bandgap Voltage Reference

The bandgap module generates a stable voltage reference of 1.22V over a range of temperatures and device supply voltages. This module is enabled anytime any of the following are enabled:

- Brown-out Reset

- · Low-voltage Detect

- Either of the internal analog references (VRH, VRL)

Whenever the above are all disabled, the bandgap module is disabled and draws no current.

#### 10.2 Internal VREF for A/D Converter

The bandgap output voltage is used to generate two stable references for the A/D converter module. These references are enabled in software to provide the user with the means to turn them on and off in order to minimize current consumption. Each reference can be individually enabled.

The 4.096V reference (VRH) is enabled with control bit VRHEN (REFCON<7>). When this bit is set, the gain amplifier is enabled. After a specified start-up time a stable reference of 4.096V is generated and can be used by the A/D converter as the VRH input.

The 2.048V reference (VRL) is enabled by setting control bit VRLEN (REFCON<6>). When this bit is set, the gain amplifier is enabled. After a specified start up time a stable reference of 2.048V is generated and can be used by the A/D converter as the VRL input. Each voltage reference can source/sink up to 5 mA of current.

Each reference, if enabled, can be presented on an external pin by setting the VRHOEN (high reference output enable) or VRLOEN (low reference output enable) control bit. If the reference is not enabled, the VRHOEN and VRLOEN bits will have no effect on the corresponding pin. The device specific pin can then be used as general purpose I/O.

Note: If VRH or VRL is enabled and the other reference (VRL or VRH), the BOR, and the LVD modules are not enabled, the bandgap will require a start-up time of no more than 50 μs before the bandgap reference is stable. Before using the internal VRH or VRL reference, ensure that the bandgap reference voltage is stable by monitoring the BGST bit in the LVDCON register. The voltage references will not be reliable until the bandgap is stable as shown by BGST being set.

### 12.3 <u>Reset</u>

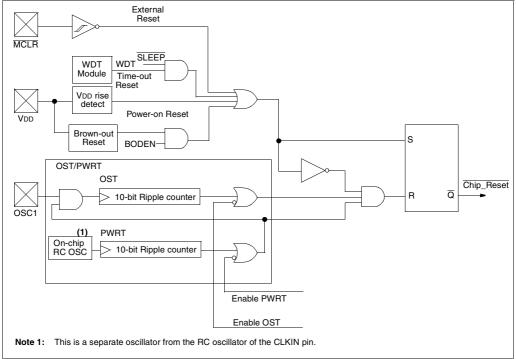

The PIC16C77X devices have several different resets. These resets are grouped into two classifications; power-up and non-power-up. The power-up type resets are the power-on and brown-out resets which assume the device VDD was below its normal operating range for the device's configuration. The non-power up type resets assume normal operating limits were maintained before/during and after the reset.

- · Power-on Reset (POR)

- Brown-out Reset (BOR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (during normal operation)

Some registers are not affected in any reset condition. Their status is unknown on a power-up reset and unchanged in any other reset. Most other registers are placed into an initialized state upon reset, however they are not affected by a WDT reset during sleep because this is considered a WDT Wakeup, which is viewed as the resumption of normal operation.

Several status bits have been provided to indicate which reset occurred (see Table 12-4). See Table 12-6 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 12-5.

These devices have a MCLR noise filter in the MCLR reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

#### FIGURE 12-5: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 14.6 SIMICE Entry-Level Hardware Simulator

SIMICE is an entry-level hardware development system designed to operate in a PC-based environment with Microchip's simulator MPLAB™-SIM. Both SIM-ICE and MPLAB-SIM run under Microchip Technology's MPLAB Integrated Development Environment (IDE) software. Specifically. SIMICE provides hardware simulation for Microchip's PIC12C5XX, PIC12CE5XX, and PIC16C5X families of PICmicro 8-bit microcontrollers. SIMICE works in conjunction with MPLAB-SIM to provide non-real-time I/O port emulation. SIMICE enables a developer to run simulator code for driving the target system. In addition, the target system can provide input to the simulator code. This capability allows for simple and interactive debugging without having to manually generate MPLAB-SIM stimulus files. SIMICE is a valuable debugging tool for entrylevel system development.

## 14.7 <u>PICDEM-1 Low-Cost PICmicro</u> <u>Demonstration Board</u>

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-Plus programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the MPLAB-ICE emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

## 14.8 PICDEM-2 Low-Cost PIC16CXX Demonstration Board

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-Plus, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

## 14.9 <u>PICDEM-3 Low-Cost PIC16CXXX</u> Demonstration Board

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 seqments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

|        |                                          | Standa                | rd Opera     | ting Co             | onditions                 | (unles          | s otherwise stated)                                      |  |  |

|--------|------------------------------------------|-----------------------|--------------|---------------------|---------------------------|-----------------|----------------------------------------------------------|--|--|

|        |                                          | Operating temperature |              |                     | -40°C                     | ≤ TA            | $A \leq +85^{\circ}C$ for industrial and                 |  |  |

| DC CHA | RACTERISTICS                             |                       |              |                     | 0°C                       | ≤ TA            | $\leq$ +70°C for commercial                              |  |  |

|        |                                          | Operati               | ng voltage   | e VDD r             | ange as d                 | escribe         | ed in DC spec Section 15.1 and                           |  |  |

|        |                                          | Section               | 15.2.        |                     |                           |                 | ~                                                        |  |  |

| Param  | Characteristic                           | Sym                   | Min          | Typ†                | Max                       | Units           | Conditions                                               |  |  |

| No.    |                                          |                       |              |                     |                           |                 |                                                          |  |  |

|        | Output High Voltage                      |                       |              |                     |                           |                 |                                                          |  |  |

| D090   | I/O ports (Note 3)                       | Voн                   | VDD - 0.7    | _                   | —                         | V               | $10_{H} = -3.0 \text{ mA}, \text{ VDD} = 4.5 \text{ V},$ |  |  |

|        |                                          |                       |              |                     |                           | $\int$          | -40°C to +85°C                                           |  |  |

| D092   | OSC2/CLKOUT (RC osc config)              |                       | VDD - 0.7    |                     | $\sim$                    | ( v             | IOH = -1.3  mA, VDP = 4.5V,                              |  |  |

|        |                                          |                       |              |                     | $\langle \rangle \rangle$ | $\backslash$    | -40°C to +85°C                                           |  |  |

| D150*  | Open-Drain High Voltage                  | VOD                   | —            | $\sim$              | 8.5                       | X               | RA4 pin                                                  |  |  |

|        | Capacitive Loading Specs on              |                       | <            |                     | 1</td <td></td> <td></td> |                 |                                                          |  |  |

|        | Output Pins                              |                       | ~            | 11                  |                           | $\setminus$ $-$ |                                                          |  |  |

| D100   | OSC2 pin                                 | Cos¢2                 | $\sim$       | $  \neq $           | 15                        | ۶F              | In XT, HS and LP modes when                              |  |  |

|        |                                          |                       | $\backslash$ |                     |                           | ſ               | external clock is used to drive                          |  |  |

|        |                                          | 1 /                   | $ \rangle$   | $\nearrow$ '        | $\searrow$                |                 | OSC1.                                                    |  |  |

| D101   | All I/O pins and OSC2 (in RC \           | Cio                   |              | $\land \rightarrow$ | <b>5</b> 0                | pF              |                                                          |  |  |

| D102   | mode) SCL, SDA in <del>/</del> 2Ĉ mode ∖ | ∖Св                   |              | $\geq$              | 400                       | pF              |                                                          |  |  |

| *      | These parameters are characterized       | zed but               | not tested   |                     | •                         |                 | ·                                                        |  |  |

I nese parameters are characterized but not tested.

Data in "Typ" column is at SV, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels

represent normal operating conditions. Higher leakage current may be measured at different input voltages. 3) Negative current is defined as current sourced by the pin.

The game current is defined as current sourced by the pin.

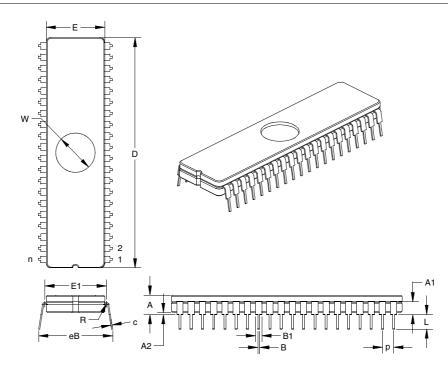

## 17.7 K04-014 40-Lead Ceramic Dual In-line with Window (JW) – 600 mil

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                        |    |       | INCHES* |       | N     | <b>IILLIMETER</b> | S     |

|------------------------------|----|-------|---------|-------|-------|-------------------|-------|

| Dimension Limits             |    | MIN   | NOM     | MAX   | MIN   | NOM               | MAX   |

| PCB Row Spacing              |    |       | 0.600   |       |       | 15.24             |       |

| Number of Pins               | n  |       | 40      |       |       | 40                |       |

| Pitch                        | р  | 0.098 | 0.100   | 0.102 | 2.49  | 2.54              | 2.59  |

| Lower Lead Width             | В  | 0.016 | 0.020   | 0.023 | 0.41  | 0.50              | 0.58  |

| Upper Lead Width             | B1 | 0.050 | 0.053   | 0.055 | 1.27  | 1.33              | 1.40  |

| Shoulder Radius              | R  | 0.000 | 0.005   | 0.010 | 0.00  | 0.13              | 0.25  |

| Lead Thickness               | с  | 0.008 | 0.011   | 0.014 | 0.20  | 0.28              | 0.36  |

| Top to Seating Plane         | А  | 0.190 | 0.205   | 0.220 | 4.83  | 5.21              | 5.59  |

| Top of Lead to Seating Plane | A1 | 0.117 | 0.135   | 0.153 | 2.97  | 3.43              | 3.89  |

| Base to Seating Plane        | A2 | 0.030 | 0.045   | 0.060 | 0.00  | 1.14              | 1.52  |

| Tip to Seating Plane         | L  | 0.135 | 0.140   | 0.145 | 3.43  | 3.56              | 3.68  |

| Package Length               | D  | 2.040 | 2.050   | 2.060 | 51.82 | 52.07             | 52.32 |

| Package Width                | E  | 0.514 | 0.520   | 0.526 | 13.06 | 13.21             | 13.36 |

| Radius to Radius Width       | E1 | 0.560 | 0.580   | 0.600 | 14.22 | 14.73             | 15.24 |

| Overall Row Spacing          | eB | 0.610 | 0.660   | 0.710 | 15.49 | 16.76             | 18.03 |

| Window Diameter              | W  | 0.340 | 0.350   | 0.360 | 8.64  | 8.89              | 9.14  |

\* Controlling Parameter.

# **PIC16C77X**

| Interrupts, Flag Bits               |             |

|-------------------------------------|-------------|

| A/D Converter Flag (ADIF Bit)       |             |

| CCP1 Flag (CCP1IF Bit)              | 20, 48, 49  |

| CCP2 Flag (CCP2IF Bit)              |             |

| Interrupt on Change (RB7:RB4) Flag  |             |

| (RBIF Bit)                          | 18, 30, 138 |

| PSP Read/Write Flag (PSPIF Bit)     |             |

| RB0/INT Flag (INTF Bit)             |             |

| SSP Flag (SSPIF Bit)                |             |

| TMR0 Overflow Flag (T0IF Bit)       | 18, 138     |

| TMR1 Overflow Flag (TMR1IF Bit)     |             |

| TMR2 to PR2 Match Flag (TMR2IF Bit) |             |

| USART Receive Flag (RCIF Bit)       |             |

| USART Transmit Flag (TXIE Bit)      |             |

|                                     |             |

## Κ

KeeLoq® Evaluation and Programming Tools ......148

## Μ

| Master Clear (MCLR)                                     |

|---------------------------------------------------------|

| MCLR Reset, Normal Operation                            |

| MCLR Reset, SLEEP 131, 133, 134                         |

| Memory Organization                                     |

| Data Memory11                                           |

| Program Memory11                                        |

| MPLAB Integrated Development Environment Software . 147 |

| Multi-Master Communication90                            |

| Multi-Master Mode72                                     |

## 0

| OPCODE Field Descriptions |  |

|---------------------------|--|

| OPTION_REG Register       |  |

| INTEDG Bit                |  |

| PS2:PS0 Bits              |  |

| PSA Bit                   |  |

| RBPU Bit                  |  |

| T0CS Bit                  |  |

| T0SE Bit                  |  |

| OSC1/CLKIN Pin            |  |

| OSC2/CLKOUT Pin           |  |

| Oscillator Configuration  |  |

| HS                        |  |

| LP                        |  |

| RC                        |  |

| ХТ                        |  |

| Oscillator, Timer1        |  |

| Oscillator, WDT           |  |

## Ρ

| Ρ                             | 54         |

|-------------------------------|------------|

| Packaging                     | 175        |

| Paging, Program Memory        |            |

| Parallel Slave Port (PSP)     | 9, 34, 37  |

| Block Diagram                 |            |

| RE0/RD/AN5 Pin                | 9, 36, 37  |

| RE1/WR/AN6 Pin                |            |

| RE2/CS/AN7 Pin                |            |

| Read Waveforms                | , ,        |

| Read/Write Enable (PSPIE Bit) |            |

| Read/Write Flag (PSPIF Bit)   |            |

| Select (PSPMODE Bit)          |            |

| Write Waveforms               |            |

| PCL Register                  |            |

| PCLATH Register               |            |

|                               | 10, 14, 10 |

| PCON Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 23, 133                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOR Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                            |

| POR Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                            |

| PICDEM-1 Low-Cost PICmicro Demo Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 146                                                                                                                                                                                                                                                                                                        |

| PICDEM-2 Low-Cost PIC16CXX Demo Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 146                                                                                                                                                                                                                                                                                                        |

| PICDEM-3 Low-Cost PIC16CXXX Demo Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 146                                                                                                                                                                                                                                                                                                        |

| PICSTART® Plus Entry Level Development System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 145                                                                                                                                                                                                                                                                                                        |

| PIE1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19                                                                                                                                                                                                                                                                                                         |

| ADIE Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19                                                                                                                                                                                                                                                                                                         |