Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 22                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                              |

| Data Converters            | A/D 6x12b                                                                |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc773t-ss |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1 | <b>PIC16C773 PINOUT DESCRIPTION</b> |

|-----------|-------------------------------------|

|           |                                     |

| Pin Name          | DIP,<br>SSOP,<br>SOIC<br>Pin# | l/O/P<br>Type | Buffer<br>Type           | Description                                                                                                                                                                                                |  |  |  |  |

|-------------------|-------------------------------|---------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| OSC1/CLKIN        | 9                             | I             | ST/CMOS <sup>(3)</sup>   | Oscillator crystal input/external clock source input.                                                                                                                                                      |  |  |  |  |

| OSC2/CLKOUT       | 10                            | 0             | _                        | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, the OSC2 pin outputs CLKOUT which h 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |  |  |  |  |

| MCLR/Vpp          | 1                             | I/P           | ST                       | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                    |  |  |  |  |

|                   |                               |               |                          | PORTA is a bi-directional I/O port.                                                                                                                                                                        |  |  |  |  |

| RA0/AN0           | 2                             | I/O           | TTL                      | RA0 can also be analog input0                                                                                                                                                                              |  |  |  |  |

| RA1/AN1           | 3                             | I/O           | TTL                      | RA1 can also be analog input1                                                                                                                                                                              |  |  |  |  |

| RA2/AN2/VREF-/VRL | 4                             | I/O           | TTL                      | RA2 can also be analog input2 or negative analog reference voltage<br>input or internal voltage reference low                                                                                              |  |  |  |  |

| RA3/AN3/VREF+/VRH | 5                             | I/O           | TTL                      | RA3 can also be analog input3 or positive analog reference voltage<br>input or internal voltage reference high                                                                                             |  |  |  |  |

| RA4/T0CKI         | 6                             | I/O           | ST                       | RA4 can also be the clock input to the Timer0 module. Output is<br>open drain type.                                                                                                                        |  |  |  |  |

|                   |                               |               |                          | PORTB is a bi-directional I/O port. PORTB can be software pro-<br>grammed for internal weak pull-up on all inputs.                                                                                         |  |  |  |  |

| RB0/INT           | 21                            | I/O           | TTL/ST <sup>(1)</sup>    | RB0 can also be the external interrupt pin.                                                                                                                                                                |  |  |  |  |

| RB1/SS            | 22                            | I/O           | TTL/ST <sup>(1)</sup>    | RB1 can also be the SSP slave select                                                                                                                                                                       |  |  |  |  |

| RB2/AN8           | 23                            | I/O           | TTL                      | RB2 can also be analog input8                                                                                                                                                                              |  |  |  |  |

| RB3/AN9/LVDIN     | 24                            | I/O           | TTL                      | RB3 can also be analog input9 or the low voltage detect input<br>reference                                                                                                                                 |  |  |  |  |

| RB4               | 25                            | I/O           | TTL                      | Interrupt on change pin.                                                                                                                                                                                   |  |  |  |  |

| RB5               | 26                            | I/O           | TTL                      | Interrupt on change pin.                                                                                                                                                                                   |  |  |  |  |

| RB6               | 27                            | I/O           | TTL/ST(2)                | Interrupt on change pin. Serial programming clock.                                                                                                                                                         |  |  |  |  |

| RB7               | 28                            | I/O           | TTL/ST(2)                | Interrupt on change pin. Serial programming data.                                                                                                                                                          |  |  |  |  |

|                   |                               |               |                          | PORTC is a bi-directional I/O port.                                                                                                                                                                        |  |  |  |  |

| RC0/T1OSO/T1CKI   | 11                            | I/O           | ST                       | RC0 can also be the Timer1 oscillator output or Timer1 clock input                                                                                                                                         |  |  |  |  |

| RC1/T1OSI/CCP2    | 12                            | I/O           | ST                       | RC1 can also be the Timer1 oscillator input or Capture2 input<br>Compare2 output/PWM2 output.                                                                                                              |  |  |  |  |

| RC2/CCP1          | 13                            | I/O           | ST                       | RC2 can also be the Capture1 input/Compare1 output/PWM1 output.                                                                                                                                            |  |  |  |  |

| RC3/SCK/SCL       | 14                            | I/O           | ST                       | RC3 can also be the synchronous serial clock input/output for both<br>SPI and I <sup>2</sup> C modes.                                                                                                      |  |  |  |  |

| RC4/SDI/SDA       | 15                            | I/O           | ST                       | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                                                                                                                            |  |  |  |  |

| RC5/SDO           | 16                            | I/O           | ST                       | RC5 can also be the SPI Data Out (SPI mode).                                                                                                                                                               |  |  |  |  |

| RC6/TX/CK         | 17                            | I/O           | ST                       | RC6 can also be the USART Asynchronous Transmit or<br>Synchronous Clock.                                                                                                                                   |  |  |  |  |

| RC7/RX/DT         | 18                            | I/O           | ST                       | RC7 can also be the USART Asynchronous Receive or<br>Synchronous Data.                                                                                                                                     |  |  |  |  |

| AVss              | 8                             | Р             |                          | Ground reference for A/D converter                                                                                                                                                                         |  |  |  |  |

| AVDD              | 7                             | Р             |                          | Positive supply for A/D converter                                                                                                                                                                          |  |  |  |  |

| Vss               | 19                            | Р             | -                        | Ground reference for logic and I/O pins.                                                                                                                                                                   |  |  |  |  |

| Vdd               | 20                            | Р             | -                        | Positive supply for logic and I/O pins.                                                                                                                                                                    |  |  |  |  |

|                   | ) = output<br>– = Not u       | sed           | I/O = input<br>TTL = TTL | input ST = Schmitt Trigger input                                                                                                                                                                           |  |  |  |  |

#### 3.4 PORTD and TRISD Registers

This section is applicable to the 40/44-pin devices only.

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

PORTD can be configured as an 8-bit wide microprocessor port (parallel slave port) by setting control bit PSPMODE (TRISE<4>). In this mode, the input buffers are TTL.

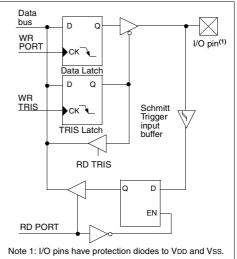

## FIGURE 3-10: PORTD BLOCK DIAGRAM (IN I/O PORT MODE)

#### TABLE 3-7 PORTD FUNCTIONS

| Name     | Bit# | Buffer Type           | Function                                          |

|----------|------|-----------------------|---------------------------------------------------|

| RD0/PSP0 | bit0 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit0 |

| RD1/PSP1 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit1 |

| RD2/PSP2 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit2 |

| RD3/PSP3 | bit3 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit3 |

| RD4/PSP4 | bit4 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit4 |

| RD5/PSP5 | bit5 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit5 |

| RD6/PSP6 | bit6 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit6 |

| RD7/PSP7 | bit7 | ST/TTL <sup>(1)</sup> | Input/output port pin or parallel slave port bit7 |

|          | bit7 | ST/TTL <sup>(1)</sup> |                                                   |

Legend: ST = Schmitt Trigger input TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffer when in Parallel Slave Port Mode.

#### TABLE 3-8 SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Address | Name  | Bit 7 | Bit 6                                                                                                                        | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1     | Bit 0     | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|-------|------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-----------|-----------|-----------|--------------------------|---------------------------|

| 08h     | PORTD | RD7   | RD6                                                                                                                          | RD5   | RD4   | RD3   | RD2       | RD1       | RD0       | xxxx xxxx                | uuuu uuuu                 |

| 88h     | TRISD | PORT  | PORTD Data Direction Register 1111 111                                                                                       |       |       |       |           | 1111 1111 | 1111 1111 |                          |                           |

| 89h     | TRISE | IBF   | IBF         OBF         IBOV         PSPMODE         —         PORTE Data Direction Bits         0000 -111         0000 -111 |       |       |       | 0000 -111 |           |           |                          |                           |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTD.

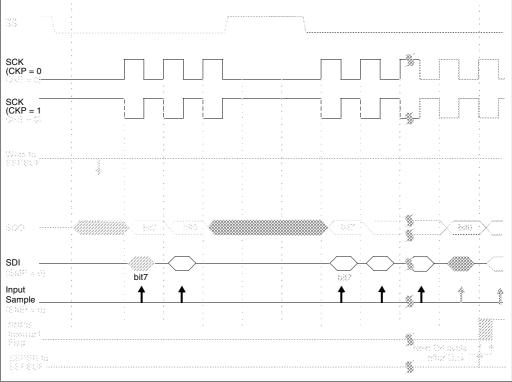

#### 8.1.5 SLAVE MODE

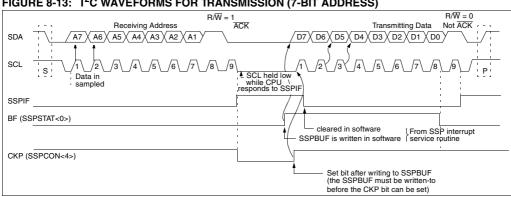

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched the interrupt flag bit SSPIF (PIR1<3>) is set.

While in slave mode the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in sleep mode, the slave can transmit/receive data. When a byte is received the device will wake-up from sleep.

#### 8.1.6 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 0100). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. TRISA<5> must be set. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the

SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. External pull-up/ pull-down resistors may be desirable, depending on the application.

| Note: | When the SPI module is in Slave Mode<br>with $\overline{SS}$ pin control enabled, (SSP-<br>CON<3:0> = 0100) the SPI module will<br>reset if the $\overline{SS}$ pin is set to VDD. |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note: | If the SPI is used in Slave Mode with $CKE = '1'$ , then $\overline{SS}$ pin control must be enabled.                                                                              |

When the SPI module resets, the bit counter is forced to 0. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

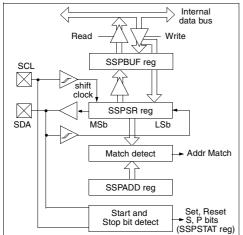

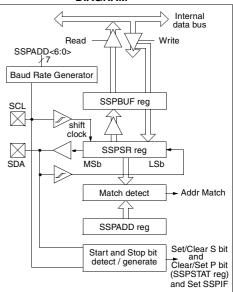

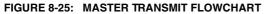

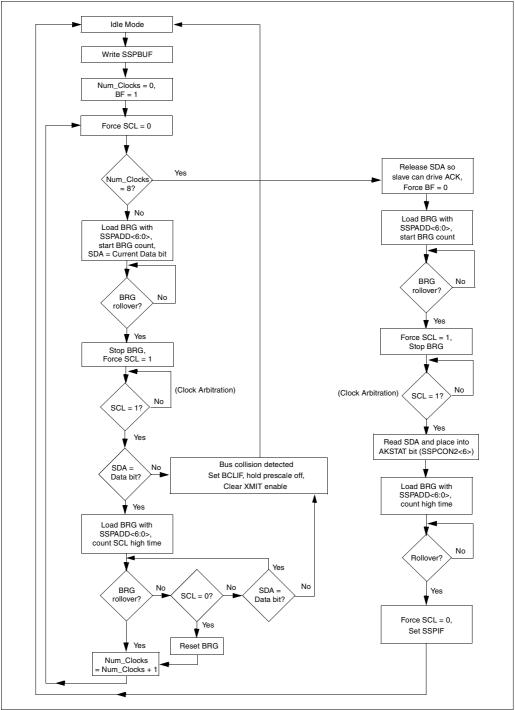

#### 8.2 MSSP I<sup>2</sup>C Operation

The MSSP module in I<sup>2</sup>C mode fully implements all master and slave functions (including general call support) and provides interrupts on start and stop bits in hardware to determine a free bus (multi-master function). The MSSP module implements the standard mode specifications as well as 7-bit and 10-bit addressing.

Refer to Application Note AN578, "Use of the SSP Module in the I<sup>2</sup>C Multi-Master Environment."

A "glitch" filter is on the SCL and SDA pins when the pin is an input. This filter operates in both the 100 kHz and 400 kHz modes. In the 100 kHz mode, when these pins are an output, there is a slew rate control of the pin that is independent of device frequency.

#### FIGURE 8-11: I<sup>2</sup>C MASTER MODE BLOCK DIAGRAM

Two pins are used for data transfer. These are the SCL pin, which is the clock, and the SDA pin, which is the data. The SDA and SCL pins that are automatically configured when the  $l^2C$  mode is enabled. The SSP module functions are enabled by setting SSP Enable bit SSPEN (SSPCON<5>).

The MSSP module has six registers for  ${\rm I}^2 C$  operation. They are the:

- SSP Control Register (SSPCON)

- SSP Control Register2 (SSPCON2)

- SSP Status Register (SSPSTAT)

- Serial Receive/Transmit Buffer (SSPBUF)

- SSP Shift Register (SSPSR) Not directly accessible

- SSP Address Register (SSPADD)

The SSPCON register allows control of the I<sup>2</sup>C operation. Four mode selection bits (SSPCON<3:0>) allow one of the following I<sup>2</sup>C modes to be selected:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Master mode, clock = OSC/4 (SSPADD +1)

Before selecting any  $I^2C$  mode, the SCL and SDA pins must be programmed to inputs by setting the appropriate TRIS bits. Selecting an  $I^2C$  mode, by setting the SSPEN bit, enables the SCL and SDA pins to be used as the clock and data lines in  $I^2C$  mode.

# PIC16C77X

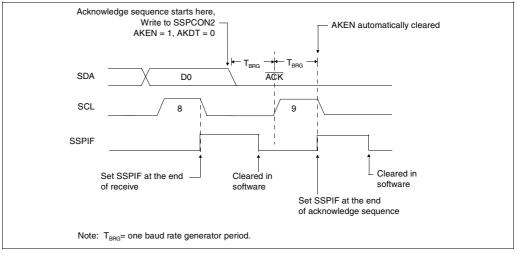

#### 8.2.13 ACKNOWLEDGE SEQUENCE TIMING

An acknowledge sequence is enabled by setting the acknowledge sequence enable bit, AKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the acknowledge data bit is presented on the SDA pin. If the user wishes to generate an acknowledge, then the AKDT bit should be cleared. If not, the user should set the AKDT bit before starting an acknowledge sequence. The baud rate generator then counts for one rollover period ( $T_{BRG}$ ), and the SCL pin is de-asserted (pulled high). When the SCL pin is sampled high (clock arbitration), the baud

rate generator counts for  $T_{BRG}$ . The SCL pin is then pulled low. Following this, the AKEN bit is automatically cleared, the baud rate generator is turned off, and the SSP module then goes into IDLE mode. (Figure 8-29)

#### 8.2.13.13 WCOL STATUS FLAG

If the user writes the SSPBUF when an acknowledege sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 8-29: ACKNOWLEDGE SEQUENCE WAVEFORM

#### 9.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI). The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc. The USART can be configured in the following modes:

- · Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>), and bits TRISC<7:6>, have to be set in order to configure pins RC6/TX/CK and RC7/ RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

The USART module also has a multi-processor communication capability using 9-bit address detection.

#### FIGURE 9-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS 98h)

| R/W-0<br>CSRC | R/W-0<br>TX9                                                                                                                       | R/W-0<br>TXEN | R/W-0<br>SYNC | U-0 | R/W-0<br>BRGH | R-1<br>TRMT | R/W-0<br>TX9D | R = Readable bit                                                                      |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|-----|---------------|-------------|---------------|---------------------------------------------------------------------------------------|

| bit7          | 173                                                                                                                                | TALN          | 31110         |     | DROIT         |             | bitO          | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| oit 7:        | CSRC: Clo                                                                                                                          | ck Source     | Select bit    |     |               |             |               |                                                                                       |

|               | Asynchrone<br>Don't care                                                                                                           | ous mode      |               |     |               |             |               |                                                                                       |

|               | Synchrono<br>1 = Master<br>0 = Slave n                                                                                             | mode (Clo     | •             |     |               | IG)         |               |                                                                                       |

| oit 6:        | <b>TX9</b> : 9-bit 1<br>1 = Selects<br>0 = Selects                                                                                 | 9-bit trans   | smission      |     |               |             |               |                                                                                       |

| oit 5:        | <b>TXEN</b> : Transmit Enable bit<br>1 = Transmit enabled<br>0 = Transmit disabled<br>Note: SREN/CREN overrides TXEN in SYNC mode. |               |               |     |               |             |               |                                                                                       |

| oit 4:        | SYNC: USART Mode Select bit<br>1 = Synchronous mode<br>0 = Asynchronous mode                                                       |               |               |     |               |             |               |                                                                                       |

| oit 3:        | Unimplem                                                                                                                           | ented: Rea    | ad as '0'     |     |               |             |               |                                                                                       |

| oit 2:        | BRGH: Hig                                                                                                                          | h Baud Ra     | ate Select b  | it  |               |             |               |                                                                                       |

|               | Asynchronous mode<br>1 = High speed                                                                                                |               |               |     |               |             |               |                                                                                       |

|               | 0 = Low sp                                                                                                                         |               |               |     |               |             |               |                                                                                       |

|               | Synchrono<br>Unused in t                                                                                                           |               |               |     |               |             |               |                                                                                       |

| oit 1:        | <b>TRMT</b> : Transmit Shift Register Status bit<br>1 = TSR empty<br>0 = TSR full                                                  |               |               |     |               |             |               |                                                                                       |

| oit 0:        | <b>TX9D</b> : 9th                                                                                                                  |               |               |     |               |             |               |                                                                                       |

#### FIGURE 9-2: RCSTA: RECEIVE STATUS AND CONTROL REGISTER (ADDRESS 18h)

| R/W-0<br>SPEN | R/W-0<br>RX9                                                                                                                                                                                                                                                                                                              | SREN                                                                                                       | R/W-0<br>CREN | R/W-0<br>ADDEN | R-0<br>FERR | OERR      | R-x<br>RX9D                | R = Readable bit                                                                     |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------|----------------|-------------|-----------|----------------------------|--------------------------------------------------------------------------------------|

| bit7          |                                                                                                                                                                                                                                                                                                                           |                                                                                                            |               |                |             |           | bit0                       | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n =Value at POR reset |

| bit 7:        | <b>SPEN</b> : Ser<br>1 = Serial p<br>0 = Serial p                                                                                                                                                                                                                                                                         | ort enable                                                                                                 | d (Configu    | res RC7/R      | X/DT and I  | RC6/TX/Cł | <pre>&lt; pins as se</pre> | rial port pins)                                                                      |

| bit 6:        | <b>RX9</b> : 9-bit I<br>1 = Selects<br>0 = Selects                                                                                                                                                                                                                                                                        | 9-bit rece                                                                                                 | otion         |                |             |           |                            |                                                                                      |

| bit 5:        | SREN: Sing                                                                                                                                                                                                                                                                                                                | gle Receive                                                                                                | e Enable b    | it             |             |           |                            |                                                                                      |

|               | <u>Asynchrone</u><br>Don't care                                                                                                                                                                                                                                                                                           | ous mode                                                                                                   |               |                |             |           |                            |                                                                                      |

|               | Synchronous mode - master<br>1 = Enables single receive<br>0 = Disables single receive<br>This bit is cleared after reception is complete.                                                                                                                                                                                |                                                                                                            |               |                |             |           |                            |                                                                                      |

|               | Synchrono<br>Unused in t                                                                                                                                                                                                                                                                                                  |                                                                                                            | <u>slave</u>  |                |             |           |                            |                                                                                      |

| bit 4:        | CREN: Cor                                                                                                                                                                                                                                                                                                                 | ntinuous Re                                                                                                | eceive Ena    | able bit       |             |           |                            |                                                                                      |

|               | <u>Asynchronous mode</u><br>1 = Enables continuous receive<br>0 = Disables continuous receive                                                                                                                                                                                                                             |                                                                                                            |               |                |             |           |                            |                                                                                      |

|               | Synchronous mode<br>1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides SREN)<br>0 = Disables continuous receive                                                                                                                                                                              |                                                                                                            |               |                |             |           |                            |                                                                                      |

| bit 3:        | <ul> <li>ADDEN: Address Detect Enable bit</li> <li>Asynchronous mode 9-bit (RX9 = 1)</li> <li>1 = Enables address detection, enable interrupt and load of the receive buffer when RSR&lt;8&gt; is set</li> <li>0 = Disables address detection, all bytes are received, and ninth bit can be used as parity bit</li> </ul> |                                                                                                            |               |                |             |           |                            |                                                                                      |

| bit 2:        | <ul> <li>FERR: Framing Error bit</li> <li>1 = Framing error (Can be updated by reading RCREG register and receive next valid byte)</li> <li>0 = No framing error</li> </ul>                                                                                                                                               |                                                                                                            |               |                |             |           |                            |                                                                                      |

| bit 1:        | 1 = Overrui                                                                                                                                                                                                                                                                                                               | OERR: Overrun Error bit<br>1 = Overrun error (Can be cleared by clearing bit CREN)<br>0 = No overrun error |               |                |             |           |                            |                                                                                      |

| bit 0:        | <b>RX9D</b> : 9th                                                                                                                                                                                                                                                                                                         | hit of rocoi                                                                                               | und data (i   | Con ho nor     | ity bit)    |           |                            |                                                                                      |

#### 9.4 USART Synchronous Slave Mode

Synchronous slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 9.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the synchronous master and slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit  $\ensuremath{\mathsf{TXIE}}$  .

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

### 9.4.2 USART SYNCHRONOUS SLAVE RECEPTION

The operation of the synchronous master and slave modes is identical except in the case of the SLEEP mode. Also, bit SREN is a don't care in slave mode.

If receive is enabled, by setting bit CREN, prior to the SLEEP instruction, then a word may be received during SLEEP. On completely receiving the word, the RSR register will transfer the data to the RCREG register and if enable bit RCIE bit is set, the interrupt generated will wake the chip from SLEEP. If the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Reception:

- Enable the synchronous master serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. If interrupts are desired, then set enable bit  $\ensuremath{\mathsf{RCIE}}$  .

- 3. If 9-bit reception is desired, then set bit RX9.

- 4. To enable reception, set enable bit CREN.

- Flag bit RCIF will be set when reception is complete and an interrupt will be generated, if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG register.

- 8. If any error occurred, clear the error by clearing bit CREN.

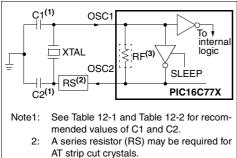

#### FIGURE 12-2: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

3: RF varies with the crystal chosen.

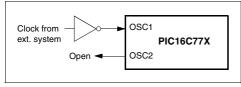

#### FIGURE 12-3: EXTERNAL CLOCK INPUT OPERATION (HS OSC CONFIGURATION)

#### TABLE 12-1 CERAMIC RESONATORS

| Ranges Tested:                                                                                 |                                                       |                                         |                                         |  |  |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------|-----------------------------------------|--|--|

| Mode                                                                                           | Freq                                                  | OSC1                                    | OSC2                                    |  |  |

| XT                                                                                             | 455 kHz<br>2.0 MHz<br>4.0 MHz                         | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |  |  |

| HS                                                                                             | 8.0 MHz<br>16.0 MHz                                   | 10 - 68 pF<br>10 - 22 pF                | 10 - 68 pF<br>10 - 22 pF                |  |  |

| These values are for design guidance only. See<br>notes at bottom of page.<br>Resonators Used: |                                                       |                                         |                                         |  |  |

| 455 kHz                                                                                        | Panasonic E                                           | FO-A455K04B                             | ± 0.3%                                  |  |  |

| 2.0 MHz                                                                                        | Murata Erie                                           | CSA2.00MG                               | $\pm 0.5\%$                             |  |  |

| 4.0 MHz                                                                                        | Murata Erie                                           | Murata Erie CSA4.00MG ± 0.5%            |                                         |  |  |

| 8.0 MHz                                                                                        | Murata Erie CSA8.00MT ± 0.5%                          |                                         |                                         |  |  |

| 16.0 MHz                                                                                       | Murata Erie CSA16.00MX ± 0.5%                         |                                         |                                         |  |  |

| All reso                                                                                       | All resonators used did not have built-in capacitors. |                                         |                                         |  |  |

#### TABLE 12-2 CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq                                                         | Cap. Range<br>C1 | Cap. Range<br>C2 |  |  |

|----------|-------------------------------------------------------------------------|------------------|------------------|--|--|

| LP       | 32 kHz                                                                  | 33 pF            | 33 pF            |  |  |

|          | 200 kHz                                                                 | 15 pF            | 15 pF            |  |  |

| XT       | 200 kHz                                                                 | 47-68 pF         | 47-68 pF         |  |  |

|          | 1 MHz                                                                   | 15 pF            | 15 pF            |  |  |

|          | 4 MHz                                                                   | 15 pF            | 15 pF            |  |  |

| HS       | 4 MHz                                                                   | 15 pF            | 15 pF            |  |  |

|          | 8 MHz                                                                   | 15-33 pF         | 15-33 pF         |  |  |

|          | 20 MHz                                                                  | 15-33 pF         | 15-33 pF         |  |  |

|          | These values are for design guidance only. See notes at bottom of page. |                  |                  |  |  |

|          | Crys                                                                    | tals Used        |                  |  |  |

| 32 kHz   | Epson C-00                                                              | 01R32.768K-A     | ± 20 PPM         |  |  |

| 200 kHz  | STD XTL 2                                                               | ± 20 PPM         |                  |  |  |

| 1 MHz    | ECS ECS-                                                                | ± 50 PPM         |                  |  |  |

| 4 MHz    | ECS ECS-4                                                               | ± 50 PPM         |                  |  |  |

| 8 MHz    | EPSON CA                                                                | -301 8.000M-C    | ± 30 PPM         |  |  |

| 20 MHz   | EPSON CA                                                                | -301 20.000M-C   | ± 30 PPM         |  |  |

Note 1: Recommended values of C1 and C2 are identical to the ranges tested (Table 12-1).

- Higher capacitance increases the stability of oscillator but also increases the start-up time.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification.

| TABLE 12-6 INITIALIZATION CONDITIONS FOR ALL REGISTERS |         |     |                                    |                          |                                 |  |  |

|--------------------------------------------------------|---------|-----|------------------------------------|--------------------------|---------------------------------|--|--|

| Register                                               | Devices |     | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset | Wake-up via WDT or<br>Interrupt |  |  |

| W                                                      | 773     | 774 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |

| INDF                                                   | 773     | 774 | N/A                                | N/A                      | N/A                             |  |  |

| TMR0                                                   | 773     | 774 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |

| PCL                                                    | 773     | 774 | 0000h                              | 0000h                    | PC + 1 <b>(2)</b>               |  |  |

| STATUS                                                 | 773     | 774 | 0001 1xxx                          | 000q quuu <b>(3)</b>     | uuuq quuu <b>(3)</b>            |  |  |

| FSR                                                    | 773     | 774 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |

| PORTA                                                  | 773     | 774 | 0x 0000                            | 0u 0000                  | uu uuuu                         |  |  |

| PORTB                                                  | 773     | 774 | xxxx 11xx                          | uuuu 11uu                | uuuu uuuu                       |  |  |

| PORTC                                                  | 773     | 774 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |

| PORTD                                                  | 773     | 774 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |

| PORTE                                                  | 773     | 774 | 000                                | 000                      | uuu                             |  |  |

| PCLATH                                                 | 773     | 774 | 0 0000                             | 0 0000                   | u uuuu                          |  |  |

| INTCON                                                 | 773     | 774 | 0000 000x                          | 0000 000u                | uuuu uuuu <b>(1)</b>            |  |  |

| PIR1                                                   | 773     | 774 | r000 0000                          | r000 0000                | ruuu uuuu <b>(1)</b>            |  |  |

|                                                        | 773     | 774 | 0000 0000                          | 0000 0000                | uuuu uuuu <b>(1)</b>            |  |  |

| PIR2                                                   | 773     | 774 | 00                                 | 00                       | u uu <b>(1)</b>                 |  |  |

| TMR1L                                                  | 773     | 774 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |

| TMR1H                                                  | 773     | 774 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |

| T1CON                                                  | 773     | 774 | 00 0000                            | uu uuuu                  | uu uuuu                         |  |  |

| TMR2                                                   | 773     | 774 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |

| T2CON                                                  | 773     | 774 | -000 0000                          | -000 0000                | -uuu uuuu                       |  |  |

| SSPBUF                                                 | 773     | 774 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |

| SSPCON                                                 | 773     | 774 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |

| CCPR1L                                                 | 773     | 774 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |

| CCPR1H                                                 | 773     | 774 | XXXX XXXX                          | uuuu uuuu                | uuuu uuuu                       |  |  |

| CCP1CON                                                | 773     | 774 | 00 0000                            | 00 0000                  | uu uuuu                         |  |  |

| RCSTA                                                  | 773     | 774 | 0000 000x                          | 0000 000x                | uuuu uuuu                       |  |  |

| TXREG                                                  | 773     | 774 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |

| RCREG                                                  | 773     | 774 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |

| CCPR2L                                                 | 773     | 774 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |

| CCPR2H                                                 | 773     | 774 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |

| CCP2CON                                                | 773     | 774 | 00 0000                            | 00 0000                  | uu uuuu                         |  |  |

| ADRESH                                                 | 773     | 774 | xxxx xxxx                          | uuuu uuuu                | uuuu uuuu                       |  |  |

| ADCON0                                                 | 773     | 774 | 0000 0000                          | 0000 0000                | uuuu uuuu                       |  |  |

| OPTION_REG                                             | 773     | 774 | 1111 1111                          | 1111 1111                | uuuu uuuu                       |  |  |

| TABLE 12-6 | INITIALIZATION CONDITIONS FOR ALL REGISTERS |

|------------|---------------------------------------------|

|            |                                             |

Legend: u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition

Note 1: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

3: See Table 12-5 for reset value for specific condition.

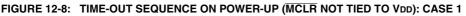

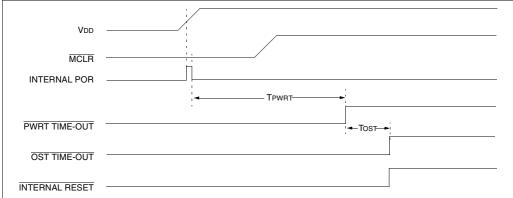

#### FIGURE 12-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

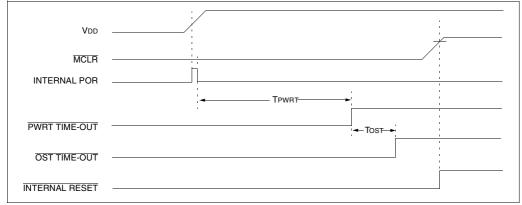

#### FIGURE 12-10: SLOW RISE TIME (MCLR TIED TO VDD)

#### 12.10.1 INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered: either rising if bit INTEDG (OPTION\_REG<6>) is set, or falling, if the INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, flag bit INTF (INTCON<1>) is set. This interrupt can be disabled by clearing enable bit INTE (INTCON<4>). Flag bit INTF must be cleared in software in the interrupt service routine before re-enabling this interrupt. The INT interrupt can wake-up the processor from SLEEP, if bit INTE was set prior to going into SLEEP. The status of global interrupt enable bit GIE decides whether or not the processor branches to the interrupt vector following wake-up. See Section 12.13 for details on SLEEP mode.

#### 12.10.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set flag bit T0IF (INTCON<2>). The interrupt can be enabled/disabled by setting/clearing enable bit T0IE (INTCON<5>). (Section 4.0)

#### 12.10.3 PORTB INTCON CHANGE

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled/disabled by setting/clearing enable bit RBIE (INTCON<4>). (Section 3.2)

#### 12.11 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, i.e., W register and STATUS register. This will have to be implemented in software.

Example 12-1 stores and restores the W and STATUS registers. The register, W\_TEMP, must be defined in each bank and must be defined at the same offset from the bank base address (i.e., if W\_TEMP is defined at 0x20 in bank 0, it must also be defined at 0xA0 in bank 1).

The example:

- a) Stores the W register.

- b) Stores the STATUS register in bank 0.

- c) Stores the PCLATH register.

- d) Executes the interrupt service routine code (User-generated).

- e) Restores the STATUS register (and bank select bit).

- f) Restores the W and PCLATH registers.

#### EXAMPLE 12-1: SAVING STATUS, W, AND PCLATH REGISTERS IN RAM

| MOVWF  | W_TEMP         | ;Copy W to TEMP register, could be bank one or zero       |

|--------|----------------|-----------------------------------------------------------|

| SWAPF  | STATUS,W       | ;Swap status to be saved into W                           |

| CLRF   | STATUS         | ;bank 0, regardless of current bank, Clears IRP, RP1, RP0 |

| MOVWF  | STATUS_TEMP    | ;Save status to bank zero STATUS_TEMP register            |

| MOVF   | PCLATH, W      | ;Only required if using pages 1, 2 and/or 3               |

| MOVWF  | PCLATH_TEMP    | ;Save PCLATH into W                                       |

| CLRF   | PCLATH         | ;Page zero, regardless of current page                    |

| BCF    | STATUS, IRP    | ;Return to Bank 0                                         |

| MOVF   | FSR, W         | ;Copy FSR to W                                            |

| MOVWF  | FSR_TEMP       | ;Copy FSR from W to FSR_TEMP                              |

| :      |                |                                                           |

| :(ISR) |                |                                                           |

| :      |                |                                                           |

| MOVF   | PCLATH_TEMP, W | ;Restore PCLATH                                           |

| MOVWF  | PCLATH         | ;Move W into PCLATH                                       |

| SWAPF  | STATUS_TEMP,W  | ;Swap STATUS_TEMP register into W                         |

|        |                | ;(sets bank to original state)                            |

| MOVWF  | STATUS         | ;Move W into STATUS register                              |

| SWAPF  | W_TEMP,F       | ;Swap W_TEMP                                              |

| SWAPF  | W_TEMP,W       | ;Swap W_TEMP into W                                       |

|        |                |                                                           |

#### 15.5 AC Characteristics: PIC16C77X (Commercial, Industrial)

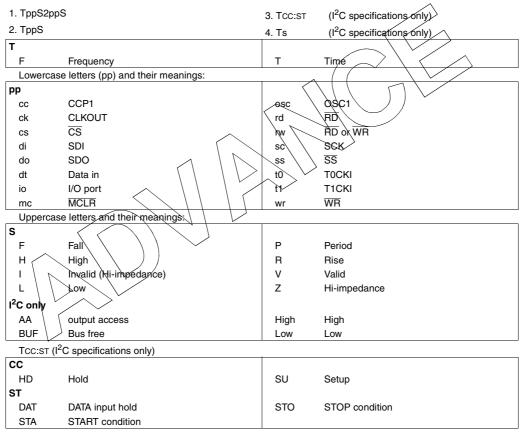

#### 15.5.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

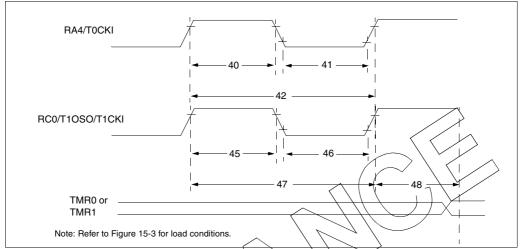

#### FIGURE 15-11: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

|             |                   | 1        |   | \<br>\  | $\sim$    |

|-------------|-------------------|----------|---|---------|-----------|

| TADIE 16 10 | TIMER0 AND TIMER1 | EVTEDN/  |   | OV DENI | INDEMENTO |

| IADLE 13-12 |                   | EXICHINA |   |         |           |

|             |                   |          | r |         |           |

| Param | C         | Characteristic        |                       | $\rightarrow$       | Min                   | Treat | Max   | Unite    | Conditions                     |

|-------|-----------|-----------------------|-----------------------|---------------------|-----------------------|-------|-------|----------|--------------------------------|

| No.   | Sym       | Characteristic        | \ \                   |                     |                       | Тур†  | wax   | Units    | Conditions                     |

| 40*   | TIOLI     | TOOKI Link Dulas K    |                       |                     |                       |       |       |          | March allo a second            |

| 40."  | Tt0H      | T0CKI High Pulse 🕅    |                       | No Prescaler        | 0.5TCY + 20           | _     | _     | ns       | Must also meet<br>parameter 42 |

|       |           |                       |                       | With Prescaler      | 10                    | —     | —     | ns       |                                |

| 41*   | TtOL      | TOCKI Low Pulse W     | /iðth 1               | No Prescaler        | 0.5TCY + 20           | —     | —     | ns       | Must also meet                 |

|       |           |                       |                       | With Prescaler      | 10                    | —     |       | ns       | parameter 42                   |

| 42*   | Tt0P      | TOCK Period           |                       | No Prescaler        | TCY + 40              | —     |       | ns       |                                |

|       |           |                       |                       | With Prescaler      |                       | —     | —     | ns       | N = prescale value             |

|       |           | $\land \land \lor$    |                       |                     | 20 or <u>TCY + 40</u> |       |       |          | (2, 4,, 256)                   |

|       |           |                       |                       |                     | N                     |       |       |          |                                |

| 45*   | Tt1H      | TICKI High Time       | Synchronous, P        |                     | 0.5TCY + 20           | -     |       | ns       | Must also meet                 |

|       |           |                       | Synchronous,          | PIC16 <b>C</b> 77X  | 15                    | —     | —     | ns       | parameter 47                   |

|       |           | 1                     | Prescaler =<br>2,4,8  | PIC16 <b>LC</b> 77X | 25                    | -     |       | ns       |                                |

|       |           |                       | 2,4,8<br>Asynchronous | PIC16 <b>C</b> 77X  | 30                    | _     |       | ns       | -                              |

|       |           |                       | Asynchronous          | PIC16 <b>C</b> 77X  | 50                    |       |       |          | -                              |

| 46*   | Tt1L      | T1CKI Low Time        | Synchronous, P        |                     | 0.5TCY + 20           |       |       | ns       | Must also meet                 |

| 40    | ILL       | I TOKI LOW TIME       | Synchronous, P        | PIC16C77X           | 15                    | _     |       | ns<br>ns | parameter 47                   |

|       |           |                       | Prescaler =           | PIC16 <b>LC</b> 77X | 25                    | _     | _     |          |                                |

|       |           |                       | 2.4.8                 | PIC 16LC//X         | 25                    | _     | _     | ns       |                                |

|       |           |                       | Asynchronous          | PIC16 <b>C</b> 77X  | 30                    | _     |       | ns       |                                |

|       |           |                       | , lognon on ouo       | PIC16 <b>LC</b> 77X | 50                    | _     |       | ns       |                                |

| 47*   | Tt1P      | T1CKI input period    | Synchronous           | PIC16 <b>C</b> 77X  | Greater of:           | _     |       | ns       | N = prescale value             |

|       |           |                       | -,                    |                     | 30 OR TCY + 40        |       |       |          | (1, 2, 4, 8)                   |

|       |           |                       |                       |                     | N                     |       |       |          |                                |

|       |           |                       |                       | PIC16 <b>LC</b> 77X | Greater of:           | —     |       | ns       | N = prescale value             |

|       |           |                       |                       |                     | 50 OR <u>TCY + 40</u> |       |       |          | (1, 2, 4, 8)                   |

|       |           |                       |                       |                     | N                     |       |       |          |                                |

|       |           |                       | Asynchronous          | PIC16 <b>C</b> 77X  | 60                    | —     | -     | ns       |                                |

|       |           |                       |                       | PIC16 <b>LC</b> 77X | 100                   | —     | —     | ns       |                                |

|       | Ft1       | Timer1 oscillator inp |                       |                     | DC                    | —     | 50    | kHz      |                                |

|       |           | (oscillator enabled b |                       |                     |                       |       |       |          |                                |

| 48    | TCKEZtmr1 | Delay from external   | clock edge to tin     | ner increment       | 2Tosc                 | -     | 7Tosc |          |                                |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### Package Marking Information (Cont'd)

####

#### 40-Lead CERDIP Windowed

#### Example

#### Example

#### 44-Lead TQFP

#### Example

#### 44-Lead MQFP

#### 44-Lead PLCC

### Example

#### Example

| RC0/T1OSO/T1CKI Pin7, 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RC1/T1OSI/CCP2 Pin7, 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Special Event Trigger (CCP) 43, 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| T1CON Register41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TMR1H Register41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TMR1L Register41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Timer2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Block Diagram46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PR2 Register 45, 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |