Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 256 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                              |

| Data Converters            | A/D 10x12b                                                               |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc774-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

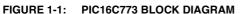

# 1.0 DEVICE OVERVIEW

This document contains device-specific information. Additional information may be found in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

There a two devices (PIC16C773 and PIC16C774) covered by this datasheet. The PIC16C773 devices come in 28-pin packages and the PIC16C774 devices come in 40-pin packages. The 28-pin devices do not have a Parallel Slave Port implemented.

The following two figures are device block diagrams sorted by pin number; 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-1 and Table 1-2, respectively.

# PIC16C77X

### 2.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register which contains various enable and flag bits for the TMR0 register overflow, RB Port change and External RB0/INT pin interrupts. Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### FIGURE 2-5: INTCON REGISTER (ADDRESS 0Bh, 8Bh, 10Bh, 18Bh)

| R/W-0  | R/W-0                                          | R/W-0       | R/W-0       | R/W-0        | R/W-0                           | R/W-0       | R/W-x        |                                                                                                                        |

|--------|------------------------------------------------|-------------|-------------|--------------|---------------------------------|-------------|--------------|------------------------------------------------------------------------------------------------------------------------|

| GIE    | PEIE                                           | TOIE        | INTE        | RBIE         | T0IF                            | INTF        | RBIF         | R = Readable bit                                                                                                       |

| bit7   |                                                |             |             |              |                                 |             | bitO         | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>- n = Value at POR reset</li> </ul> |

| bit 7: | <b>GIE:</b> Glob<br>1 = Enable<br>0 = Disable  | es all un-r | nasked in   |              |                                 |             |              |                                                                                                                        |

| bit 6: | <b>PEIE</b> : Per<br>1 = Enable<br>0 = Disable | es all un-r | nasked pe   | eripheral in | iterrupts                       |             |              |                                                                                                                        |

| bit 5: | <b>TOIE</b> : TMF<br>1 = Enable<br>0 = Disable | es the TM   | R0 interru  | ıpt          | oit                             |             |              |                                                                                                                        |

| bit 4: | IINTE: RE<br>1 = Enable<br>0 = Disable         | es the RB   | 0/INT exte  | ernal interr | upt                             |             |              |                                                                                                                        |

| bit 3: | <b>RBIE</b> : RB<br>1 = Enable<br>0 = Disable  | es the RB   | port char   | ige interru  | pt                              |             |              |                                                                                                                        |

| bit 2: | <b>TOIF</b> : TMF<br>1 = TMR0<br>0 = TMR0      | register h  | nas overflo | wed (mus     | t be cleare                     | d in softwa | re)          |                                                                                                                        |

| bit 1: | INTF: RB(<br>1 = The R<br>0 = The R            | B0/INT ex   | ternal inte | errupt occi  | urred (must                     | be cleared  | d in softwa  | re)                                                                                                                    |

| bit 0: |                                                | st one of t | he RB7:R    | B4 pins ch   | t<br>nanged stat<br>anged state |             | e cleared in | software)                                                                                                              |

### 2.2.2.6 PIE2 REGISTER

This register contains the individual enable bits for the CCP2, SSP bus collision, and low voltage detect interrupts.

| FIGURE 2-8: | PIE2 REGISTER | (ADDRESS 8Dh) |

|-------------|---------------|---------------|

|-------------|---------------|---------------|

| R/W-0    | U-0                                           | U-0          | U-0         | R/W-0      | U-0      | U-0 | R/W-0  |                                                                                                                      |

|----------|-----------------------------------------------|--------------|-------------|------------|----------|-----|--------|----------------------------------------------------------------------------------------------------------------------|

| LVDIE    | —                                             | —            |             | BCLIE      | —        |     | CCP2IE | R = Readable bit                                                                                                     |

| bit7     |                                               |              |             |            |          |     | bit0   | <ul> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |

| bit 7    | <b>LVDIE</b> : Lo<br>1 = LVD Ir<br>0 = LVD Ir | nterrupt is  | enabled     | terrupt En | able bit |     |        |                                                                                                                      |

| bit 6-4: | Unimplen                                      | nented: R    | lead as '0' |            |          |     |        |                                                                                                                      |

| bit 3:   | <b>BCLIE</b> : Bu<br>1 = Bus C<br>0 = Bus C   | ollision int | errupt is e | enabled    | bit      |     |        |                                                                                                                      |

| bit 2-1: | Unimplen                                      | nented: R    | lead as '0' |            |          |     |        |                                                                                                                      |

| bit 0:   | CCP2IE: (<br>1 = Enable<br>0 = Disabl         | es the CC    | P2 interru  | pt         |          |     |        |                                                                                                                      |

# 3.0 I/O PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Additional information on I/O ports may be found in the PICmicro™ Mid-Range Reference Manual, (DS33023).

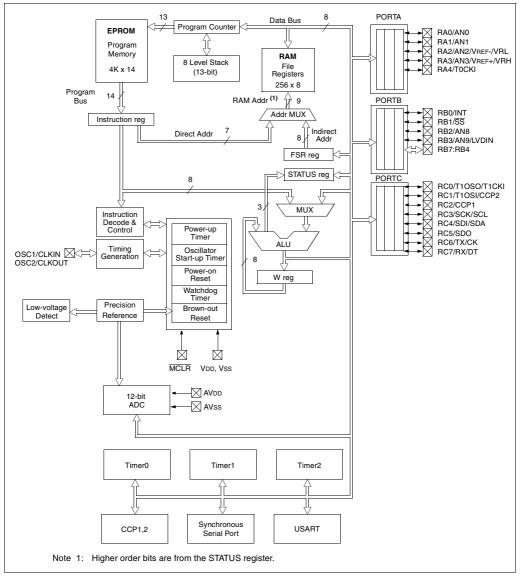

### 3.1 PORTA and the TRISA Register

PORTA is a 6-bit wide bi-directional port for the 40/44 pin devices and is 5-bits wide for the 28-pin devices. PORTA<5> is not on the 28-pin devices. The corresponding data direction register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, i.e., put the corresponding PORTA pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, i.e., put the contents of the output latch on the selected pin.

Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch.

Pin RA4 is multiplexed with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers.

Other PORTA pins are multiplexed with analog inputs and analog VREF inputs and precision on-board references (VRL/VRH). The operation of each pin is selected by clearing/setting the control bits in the ADCON1 register (A/D Control Register1).

Note: On a Power-on Reset, these pins are configured as analog inputs and read as '0'.

The TRISA register controls the direction of the RA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

### EXAMPLE 3-1: INITIALIZING PORTA

| BCF   | STATUS, | RP0 | ; |                       |

|-------|---------|-----|---|-----------------------|

| CLRF  | PORTA   |     | ; | Initialize PORTA by   |

|       |         |     | ; | clearing output       |

|       |         |     | ; | data latches          |

| BSF   | STATUS, | RP0 | ; | Select Bank 1         |

| MOVLW | 0xCF    |     | ; | Value used to         |

|       |         |     | ; | initialize data       |

|       |         |     | ; | direction             |

| MOVWF | TRISA   |     | ; | Set RA<3:0> as inputs |

|       |         |     | ; | RA<5:4> as outputs    |

|       |         |     | ; | TRISA<7:6> are always |

|       |         |     | ; | read as '0'.          |

|       |         |     |   |                       |

### FIGURE 3-1: BLOCK DIAGRAM OF RA3:RA2 PINS

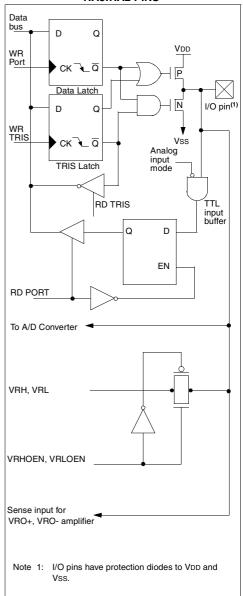

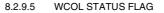

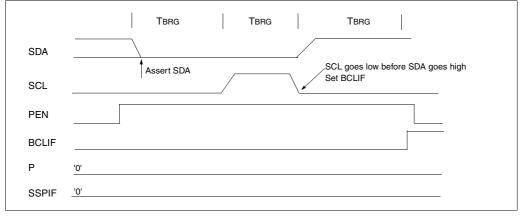

#### 8.2.9 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

To initiate a START condition, the user sets the start condition enable bit, SEN (SSPCON2<0>). If the SDA and SCL pins are sampled high, the baud rate generator is re-loaded with the contents of SSPADD<6:0>. and starts its count. If SCL and SDA are both sampled high when the baud rate generator times out  $(T_{BBG})$ , the SDA pin is driven low. The action of the SDA being driven low while SCL is high is the START condition, and causes the S bit (SSPSTAT<3>) to be set. Following this, the baud rate generator is reloaded with the contents of SSPADD<6:0> and resumes its count. When the baud rate generator times out (T<sub>BRG</sub>), the SEN bit (SSPCON2<0>) will be automatically cleared by hardware, the baud rate generator is suspended leaving the SDA line held low, and the START condition is complete.

Note: If at the beginning of START condition the SDA and SCL pins are already sampled low, or if during the START condition the SCL line is sampled low before the SDA line is driven low, a bus collision occurs, the Bus Collision Interrupt Flag (BCLIF) is set, the START condition is aborted, and the I<sup>2</sup>C module is reset into its IDLE state.

### FIGURE 8-20: FIRST START BIT TIMING

If the user writes the SSPBUF when an START sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

Note: Because queueing of events is not allowed, writing to the lower 5 bits of SSPCON2 is disabled until the START condition is complete.

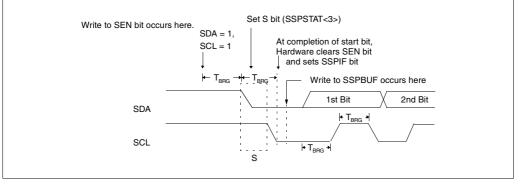

### 8.2.18.15 BUS COLLISION DURING A START CONDITION

During a START condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the START condition (Figure 8-35).

- b) SCL is sampled low before SDA is asserted low. (Figure 8-36).

During a START condition both the SDA and the SCL pins are monitored.

lf:

the SDA pin is already low or the SCL pin is already low,

then:

the START condition is aborted, and the BCLIF flag is set, and the SSP module is reset to its IDLE state (Figure 8-35).

The START condition begins with the SDA and SCL pins de-asserted. When the SDA pin is sampled high, the baud rate generator is loaded from SSPADD<6:0> and counts down to 0. If the SCL pin is sampled low

while SDA is high, a bus collision occurs, because it is assumed that another master is attempting to drive a data '1' during the START condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 8-37). If however a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The baud rate generator is then reloaded and counts down to 0, and during this time, if the SCL pins is sampled as '0', a bus collision does not occur. At the end of the BRG count the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a START condition is that no two bus masters can assert a START condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the START condition, and if the address is the same, arbitration must be allowed to continue into the data portion, REPEATED START, or STOP conditions.

### FIGURE 8-35: BUS COLLISION DURING START CONDITION (SDA ONLY)

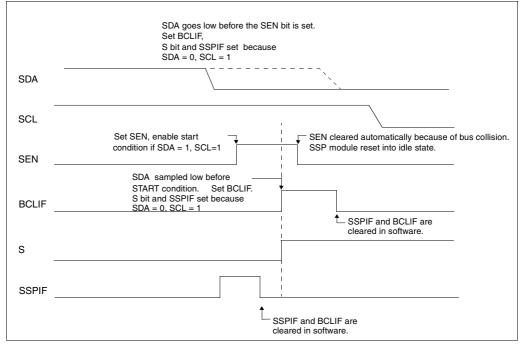

#### 8.2.18.17 BUS COLLISION DURING A STOP CONDITION

Bus collision occurs during a STOP condition if:

- After the SDA pin has been de-asserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is de-asserted, SCL is sampled low before SDA goes high.

The STOP condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allow to float. When the pin is sampled high (clock arbitration), the baud rate generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0'. If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 8-40).

### FIGURE 8-40: BUS COLLISION DURING A STOP CONDITION (CASE 1)

### FIGURE 8-41: BUS COLLISION DURING A STOP CONDITION (CASE 2)

| BAUD<br>RATE | Fosc = 2 | 20 MHz<br>% | SPBRG<br>value |         | 0/    | SPBF<br>valu |      | 10 MHz  |       | %      | SPB<br>vali | SRG   | 7.15909 1 | ИНz<br>%  | SPBRG<br>value |       |           |

|--------------|----------|-------------|----------------|---------|-------|--------------|------|---------|-------|--------|-------------|-------|-----------|-----------|----------------|-------|-----------|

| (K)          | KBAUD    | ERROR       |                | ) KBAUD | ERRO  |              |      | KBAUD   |       |        | (deci       |       | KBAUD     | ERROR     | (decimal)      |       |           |

| 0.3          | NA       |             | -              | NA      | -     | -            |      | NA      |       | -      | -           |       | NA        |           | -              |       |           |

| 1.2          | NA       | -           | -              | NA      | -     | -            |      | NA      |       | -      | -           |       | NA        | -         | -              |       |           |

| 2.4          | NA       | -           | -              | NA      | -     | -            |      | NA      |       | -      | -           |       | NA        | -         | -              |       |           |

| 9.6          | NA       | -           | -              | NA      | -     | -            |      | 9.766   | +1    | .73    | 25          | 55    | 9.622     | +0.23     | 185            |       |           |

| 19.2         | 19.53    | +1.73       | 255            | 19.23   | +0.16 |              |      | 19.23   |       | .16    | 12          |       | 19.24     | +0.23     | 92             |       |           |

| 76.8         | 76.92    | +0.16       | 64             | 76.92   |       |              |      | 75.76   |       | .36    | 3           |       | 77.82     | +1.32     | 22             |       |           |

| 96           | 96.15    | +0.16       | 51             | 95.24   |       |              |      | 96.15   |       | .16    | 25          | -     | 94.20     | -1.88     | 18             |       |           |

| 300          | 294.1    | -1.96       | 16             | 307.69  |       |              |      | 312.5   |       | .17    | 7           |       | 298.3     | -0.57     | 5              |       |           |

| 500          | 500      | 0           | 9              | 500     | 0     | 7            |      | 500     |       | 0      | 4           |       | NA        | -         | -              |       |           |

| HIGH         | 5000     | -           | 0              | 4000    | -     | 0            |      | 2500    |       | -      | 0           |       | 1789.8    | -         | 0              |       |           |

| LOW          | 19.53    | -           | 255            | 15.625  | -     | 255          | 5    | 9.766   |       | -      | 25          | 55    | 6.991     | -         | 255            |       |           |

|              | Fosc =   | 5.0688 MH   | ۱z ،           | 4 MHz   |       |              | 3.57 | '9545 M | Hz    |        | 1           | MHz   |           |           | 32.768 k       | Hz    |           |

| BAUD         |          |             | SPBRG          |         |       | SPBRG        |      |         |       | SPBF   | RG          |       |           | SPBR      | à              |       | SPBRG     |

| RATE         | KBAUD    | %           |                | KBAUD   | %     | value        |      | AUD     | %     | valu   |             | KBAU  |           | value     | KBAUD          | %     | value     |

| (K)          |          | ERROR       | (decimal)      |         | ERROR | decimal)     |      | E       | RROR  | (decin | nal)        |       | ERRC      | R (decima | u)             | ERROR | (decimal) |

| 0.3          | NA       | -           | -              | NA      | -     | -            | Ν    | JA      | -     | -      |             | NA    | -         | -         | 0.303          | +1.14 | 26        |

| 1.2          | NA       | -           | -              | NA      | -     | -            | Ν    | A       | -     | -      |             | 1.20  | 2 +0.1    | 5 207     | 1.170          | -2.48 | 6         |

| 2.4          | NA       | -           | -              | NA      | -     | -            | Ν    | A       | -     | -      |             | 2.40  | 4 +0.1    | 5 103     | NA             | -     | -         |

| 9.6          | 9.6      | 0           | 131            | 9.615   | +0.16 | 103          | 9.   | 622 -   | +0.23 | 92     |             | 9.61  | 5 +0.1    | 6 25      | NA             | -     | -         |

| 19.2         | 19.2     | 0           | 65             | 19.231  | +0.16 | 51           |      |         | 0.83  | 46     |             | 19.24 |           |           | NA             | -     | -         |

| 76.8         | 79.2     | +3.13       | 15             | 76.923  | +0.16 | 12           |      |         | 2.90  | 11     |             | 83.3  | 4 +8.5    | 12        | NA             | -     | -         |

| 96           | 97.48    | +1.54       | 12             | 1000    | +4.17 | 9            |      |         | +3.57 | 8      | 1           | NA    | -         | -         | NA             | -     | -         |

| 300          | 316.8    | +5.60       | 3              | NA      | -     | -            |      |         | 0.57  | 2      |             | NA    | -         | -         | NA             | -     | -         |

| 500          | NA       | -           | -              | NA      | -     | -            |      | JA      | -     | -      |             | NA    | -         | -         | NA             | -     | -         |

| HIGH         | 1267     | -           | 0              | 100     | -     | 0            |      | 4.9     | -     | 0      | 1           | 250   |           | 0         | 8.192          | -     | 0         |

| LOW          | 4.950    | -           | 255            | 3.906   | -     | 255          | 3.   | 496     | -     | 255    | 5           | 0.976 | 6 -       | 255       | 0.032          | -     | 255       |

# TABLE 9-4 BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD        | Fosc = 2 |            | SPBRG             | 16 MHz |                | SPBF             | RG    | 0 MHz   |           |       | PBRG    | 7.15909 M |            | SPBRG              |        |       |

|-------------|----------|------------|-------------------|--------|----------------|------------------|-------|---------|-----------|-------|---------|-----------|------------|--------------------|--------|-------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal | KBAUE  | %<br>ERRO      | valu<br>R (decim |       | KBAUD   | %<br>ERRC |       | alue    | KBAUD     | %<br>ERROR | value<br>(decimal) |        |       |

|             | -        | Ennon      | (uconnui)         |        |                | i (ucom          |       |         | LINK      |       | connun) |           | Ennon      | (aconnai)          |        |       |

| 0.3         | NA       | -          | -                 | NA     | -              | -                |       | NA      | -         |       | -       | NA        | -          | -                  |        |       |

| 1.2         | 1.221    | +1.73      | 255               | 1.202  |                |                  |       | 1.202   | +0.1      |       | 129     | 1.203     | +0.23      | 92                 |        |       |

| 2.4         | 2.404    | +0.16      | 129               | 2.404  |                |                  | ;     | 2.404   | +0.1      |       | 64      | 2.380     | -0.83      | 46                 |        |       |

| 9.6         | 9.469    | -1.36      | 32                | 9.615  | +0.16          |                  |       | 9.766   | +1.7      |       | 15      | 9.322     | -2.90      | 11                 |        |       |

| 19.2        | 19.53    | +1.73      | 15                | 19.23  | +0.16          |                  |       | 19.53   | +1.7      |       | 7       | 18.64     | -2.90      | 5                  |        |       |

| 76.8        | 78.13    | +1.73      | 3                 | 83.33  | +8.51          | 2                |       | 78.13   | +1.7      | 3     | 1       | NA        | -          | -                  |        |       |

| 96          | 104.2    | +8.51      | 2                 | NA     | -              | -                |       | NA      | -         |       | -       | NA        | -          | -                  |        |       |

| 300         | 312.5    | +4.17      | 0                 | NA     | -              | -                |       | NA      | -         |       | -       | NA        | -          | -                  |        |       |

| 500         | NA       | -          | -                 | NA     | -              | -                |       | NA      | -         |       | -       | NA        | -          | -                  |        |       |

| HIGH        | 312.5    | -          | 0                 | 250    | -              | 0                |       | 156.3   | -         |       | 0       | 111.9     | -          | 0                  |        |       |

| LOW         | 1.221    | -          | 255               | 0.977  | -              | 255              | ;     | 0.6104  | -         | :     | 255     | 0.437     | -          | 255                |        |       |

|             | Fosc = ! | 5.0688 MH  | lz 4              | 1 MHz  |                |                  | 3.579 | 9545 MH | z         |       | 1 MHz   |           |            | 32.768 k           | Hz     |       |

| BAUD        |          |            | SPBRG             |        |                | SPBRG            |       |         |           | SPBRG |         |           | SPBRG      |                    |        | SPBRG |

| BAUD        |          | %          | value             |        | %              | value            |       | 0       |           | value |         | %         | value      |                    | %      | value |

| (K)         | KBAUD    |            | (decimal)         | KBAUD  |                |                  | ква   |         |           |       | KBAU    |           |            | ) KBAUD            |        |       |

|             | 0.31     | +3.13      | , ,               | 0.3005 | -0.17          | 207              | 0.30  |         |           | 185   | 0.300   |           | 51         | 0.256              |        |       |

| 0.3<br>1.2  | 1.2      | +3.13      | 255<br>65         | 1.202  | -0.17<br>+1.67 | 207<br>51        | 1.19  |         | .23<br>83 | 46    | 1.202   |           | 12         | 0.256<br>NA        | -14.67 | 1     |

|             |          |            |                   |        |                | -                |       |         |           |       |         |           |            |                    | -      | -     |

| 2.4         | 2.4      | 0          | 32                | 2.404  | +1.67          | 25               | 2.43  |         |           | 22    | 2.232   |           | 6          | NA                 | -      | -     |

| 9.6         | 9.9      | +3.13      | 7                 | NA     | -              | -                | 9.32  |         | 90        | 5     | NA      | -         | -          | NA                 | -      | -     |

| 19.2        | 19.8     | +3.13      | 3                 | NA     | -              | -                | 18.6  |         | 90        | 2     | NA      | -         | -          | NA                 | -      | -     |

| 76.8        | 79.2     | +3.13      | 0                 | NA     | -              | -                | NA    |         | -         | -     | NA      | -         | -          | NA                 | -      | -     |

| 96          | NA       | -          | -                 | NA     | -              | -                | NA    |         | -         | -     | NA      | -         | -          | NA                 | -      | -     |

| 300         | NA       | -          | -                 | NA     | -              | -                | NA    |         | -         | -     | NA      | -         | -          | NA                 | -      | -     |

| 500         | NA       | -          | -                 | NA     | -              | -                | NA    |         | -         | -     | NA      | -         | -          | NA                 | -      | -     |

| HIGH        | 79.2     | -          |                   | 62.500 | -              | 0                | 55.9  |         | -         | 0     | 15.63   |           | 0          | 0.512              | -      | 0     |

| LOW         | 0.3094   | -          | 255               | 3.906  | -              | 255              | 0.21  | 85      | -         | 255   | 0.061   | 0 -       | 255        | 0.0020             | -      | 255   |

### 9.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 9-6. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at FOSC.

The USART module has a special provision for multiprocessor communication. When the RX9 bit is set in the RCSTA register, 9-bits are received and the ninth bit is placed in the RX9D status bit of the RSTA register. The port can be programmed such that when the stop bit is received, the serial port interrupt will only be activated if the RX9D bit = 1. This feature is enabled by setting the ADDEN bit RCSTA<3> in the RCSTA register. This feature can be used in a multi-processor system as follows:

A master processor intends to transmit a block of data to one of many slaves. It must first send out an address byte that identifies the target slave. An address byte is identified by the RX9D bit being a '1' (instead of a '0' for a data byte). If the ADDEN bit is set in the slave's RCSTA register, all data bytes will be ignored. However, if the ninth received bit is equal to a '1', indicating that the received byte is an address, the slave will be interrupted and the contents of the RSR register will be transferred into the receive buffer. This allows the slave can examine the received byte to see if it is addressed. The addressed slave will then clear its ADDEN bit and prepare to receive data bytes from the master.

When ADDEN is set, all data bytes are ignored. Following the STOP bit, the data will not be loaded into the receive buffer, and no interrupt will occur. If another byte is shifted into the RSR register, the previous data byte will be lost.

The ADDEN bit will only take effect when the receiver is configured in 9-bit mode.

The receiver block diagram is shown in Figure 9-6.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

# 9.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

Steps to follow when setting up an Asynchronous Reception with Address Detect Enabled:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- · If interrupts are desired, then set enable bit RCIE.

- Set bit RX9 to enable 9-bit reception.

- · Set ADDEN to enable address detect.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register, to determine if the device is being addressed.

- If any error occurred, clear the error by clearing enable bit CREN.

- If the device has been addressed, clear the ADDEN bit to allow data bytes and address bytes to be read into the receive buffer, and interrupt the CPU.

# 12.0 SPECIAL FEATURES OF THE CPU

These PICmicro devices have a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Low-voltage detection

- SLEEP

- Code protection

- · ID locations

- · In-circuit serial programming

These devices have a Watchdog Timer which can be shut off only through configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up type resets only (POR, BOR), designed to keep the part in reset while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LP crystal option saves power. A set of configuration bits are used to select various options.

Additional information on special features is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

### 12.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

Some of the core features provided may not be necessary to each application that a device may be used for. The configuration word bits allow these features to be configured/enabled/disabled as necessary. These features include code protection, brown-out reset and its trippoint, the power-up timer, the watchdog timer and the devices oscillator mode. As can be seen in Figure 12-1, some additional configuration word bits have been provided for brown-out reset trippoint selection.

## FIGURE 12-1: CONFIGURATION WORD

| CP1     | CP0    | BORV1                | BORV0    | CP1    | CP0      | -                   | BODEN            | CP1              | CP0 | PWRTE | WDTE | FOSC1 | FOSC0       | Register:<br>Address | CONFIG<br>2007h |

|---------|--------|----------------------|----------|--------|----------|---------------------|------------------|------------------|-----|-------|------|-------|-------------|----------------------|-----------------|

| bit13   | 12     | 11                   | 10       | 9      | 8        | 7                   | 6                | 5                | 4   | 3     | 2    | 1     | bit0        | Address              | 2007h           |

| oit 13  | -12: ( | CP1:CP               | 0: Code  | Prote  | ction b  | oits <sup>(2)</sup> |                  |                  |     |       |      |       |             | 1                    |                 |

| bit 9-8 | B: ·   | 11 = Pro             | gram m   | emory  | code p   | rotecti             | on off           |                  |     |       |      |       |             |                      |                 |

| oit 5-4 |        | 10 = 080             |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 01 = 040             |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 00 = 000             |          |        | •        |                     |                  | (3)              |     |       |      |       |             |                      |                 |

| bit 11  |        |                      |          |        | n-out F  | eset V              | oltage bit       | s <sup>(3)</sup> |     |       |      |       |             |                      |                 |

|         |        | 11 = Vвс<br>10 = Vвс |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 0 = VBC              |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         | (      | 00 = Vвс             | R set to | 4.5V   |          |                     |                  |                  |     |       |      |       |             |                      |                 |

| bit 7:  | I      | Unimple              | mented   | I, Rea | d as '1' |                     |                  |                  |     |       |      |       |             |                      |                 |

| bit 6:  |        | BODEN:               | Brown-   | out Re | eset En  | able bi             | <sub>†</sub> (1) |                  |     |       |      |       |             |                      |                 |

|         |        | 1 = Brow             |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         | (      | ) = Brow             | n-out R  | eset d | isabled  |                     |                  |                  |     |       |      |       |             |                      |                 |

| bit 3:  | ī      | WRTE:                | Power-   | up Tin | ner Ena  | ble bit             | (1)              |                  |     |       |      |       |             |                      |                 |

|         |        | 1 = PWF              |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         | (      | D = PWF              | RT enabl | ed     |          |                     |                  |                  |     |       |      |       |             |                      |                 |

| bit 2:  |        | WDTE: \              |          | 0      | er Enał  | ole bit             |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 1 = WDT              |          | -      |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | O = WDT              |          | -      |          |                     |                  |                  |     |       |      |       |             |                      |                 |

| bit 1-0 |        | FOSC1:               |          |        | ator Se  | lectior             | bits             |                  |     |       |      |       |             |                      |                 |

|         |        | 11 = RC<br>10 = HS   |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 0 = HS<br>01 = XT (  |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        | 00 = LP              |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

|         |        |                      |          |        |          |                     |                  |                  |     |       |      |       |             |                      |                 |

| Note    |        |                      |          |        |          |                     |                  |                  |     |       |      |       | dless of th | ne value of b        | it PWRTE.       |

|         |        |                      |          |        |          |                     | ed anytim        |                  |     |       |      |       | tion scher  | na listad            |                 |

|         |        |                      |          |        |          |                     |                  |                  |     |       |      |       |             | election of a        | n unused        |

|         |        |                      |          |        |          |                     | nterrupt.        | , 000            |     |       |      |       |             |                      |                 |

### 12.2 Oscillator Configurations

#### 12.2.1 OSCILLATOR TYPES

The PIC16C77X can be operated in four different oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

# 12.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation (Figure 12-2). The PIC16C77X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications.

A difference from the other mid-range devices may be noted in that the device can be driven from an external clock only when configured in HS mode (Figure 12-3).

# PIC16C77X

NOTES:

# **15.0 ELECTRICAL CHARACTERISTICS**

### Absolute Maximum Ratings †

| Ambient temperature under bias                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Storage temperature                                                                                                                                                                                                                                                                                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR. and RA4)                                                                                                                                                                                                                                      |

| Voltage on VDD with respect to Vss                                                                                                                                                                                                                                                                      |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                                                                                                                                                                            |

| Voltage on RA4 with respect to Vss0 to +8.5V                                                                                                                                                                                                                                                            |

| Total power dissipation (Note 1)                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                         |

| Maximum current out of Vss pin                                                                                                                                                                                                                                                                          |

| Input clamp current, liκ (VI < 0 or VI > VDD)                                                                                                                                                                                                                                                           |

| Output clamp current, loк (Vo < 0 or Vo > VDD)± 20 mA                                                                                                                                                                                                                                                   |

| Maximum output current sunk by any I/Ø pin                                                                                                                                                                                                                                                              |

| Maximum output current sourced by any 1/0 pin                                                                                                                                                                                                                                                           |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined) (Note 3)                                                                                                                                                                                                                                     |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined) (Note 3)                                                                                                                                                                                                                                  |

| Maximum current sunk by PORTC and PORTD (combined) (Note 3)                                                                                                                                                                                                                                             |

| Maximum current sourced by PORTC and PORTD (combined) (Note 3)                                                                                                                                                                                                                                          |

| Note 1: Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\Sigma$ IDH} + $\Sigma$ {(VDD - VOH) x IDH} + $\Sigma$ (VOI x IOL)                                                                                                                                                             |

| Note 2: Voltage spikes below Vss at the $\overline{\text{MCLR}}$ pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100 $\Omega$ should be used when applying a "low" level to the $\overline{\text{MCLR}}$ pin rather than pulling this pin directly to Vss. |

Note 3: RORTD and PORTE are not implemented on the PIC16C773.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### TABLE 15-1 CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| osc | PIC16C773-04<br>PIC16C774-04                                                                                | PIC16C773-20<br>PIC16C774-20                                                                                                                     | PIC16LC773-04<br>PIC16LC774-04                                                                            | JW Devices                                                                                                                                         |

|-----|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| RC  | VDD: 4.0V to 5.5V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freg: 4 MHz max.                    | VDD: 4.5V to 5.5V<br>IDD: 2.7 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4V<br>Freg: 4 MHz max.                                                      | VDD: 2.5V to 5.5V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5 μA max. at 3V<br>Freg: 4 MHz max.                 | VDD: 4.0V to 5.5V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                                                           |

| хт  | VDD: 4.0V to 5.5V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                    | VDD:         4.5V to 5.5V           IDD:         2.7 mA typ. at 5.5V           IPD:         1.5 μA typ. at 4V           Freq:         4 MHz max. | VDD: 2.5V to 5.5V<br>IDD: 3.8 mA max. at 3.0V<br>IPD: 5 μA max. at 3V<br>Freq: 4 MHz max.                 | VDD: 4.0V to 5.5V<br>IDD: 5 mA max. at 5.5V<br>IPD: 16 μA max. at 4V<br>Freq: 4 MHz max.                                                           |

| HS  | VDD: 4.5V to 5.5V<br>IDD: 13.5 mA typ. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 4 MHz max.              | VDD: 4.5V to 5.5V<br>IDD: 20 mA max. at 5.5V<br>IPD: 1.5 μA typ. at 4.5V<br>Freq: 20 MHz max.                                                    | Not tested for functionality                                                                              | VDD:         4.5V to 5.5V           IDD:         20 mA max. at 5.5V           IPD:         1.5 μA typ. at 4.5V           Freq:         20 MHz max. |

| LP  | VDD: 4.0V to 5.5V<br>IDD: 52.5 μA typ. at 32<br>kHz, 4.0V<br>IPD: 0.9 μA typ. at 4.0V<br>Freq: 200 kHz max. | Not tested for functionality                                                                                                                     | VDD: 2.5V to 5.5V<br>IDD: 48 μA max. at 32 kHz,<br>3.0V<br>IPD: 5.0 μA max. at 3.0V<br>Freq: 200 kHz max. | VDD: 2.5V to 5.5V<br>IDD: 48 μA max. at 32 kHz,<br>3.0V<br>IPD: 5.0 μA max. at 3.0V<br>Freq: 200 kHz max.                                          |

The shaded sections indicate oscillator selections which are tested for functionality, but not for MIN/MAX specifications. It is recommended that the user select the device type that ensures the specifications required.

### 15.1 DC Characteristics: PIC16C77X (Commercial, Industrial)

| DC CHA        | RACTERISTICS                                                     |                   | <b>Standa</b><br>Operati |            |            |                  | tions (unless otherwise stated) $0^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and $C \leq TA \leq +70^{\circ}C$ for commercial |

|---------------|------------------------------------------------------------------|-------------------|--------------------------|------------|------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.  | Characteristic                                                   | Sym               | Min                      | Тур†       | Max        | Units            | Conditions                                                                                                                             |

| D001<br>D001A | Supply Voltage                                                   | VDD               | 4.0<br>4.5               | _          | 5.5<br>5.5 | V<br>V           | XT, RC and LP osc configuration<br>HS osc configuration                                                                                |

| D002*         | RAM Data Retention<br>Voltage (Note 1)                           | VDR               | —                        | 1.5        | —          | V                |                                                                                                                                        |

| D003          | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR              | _                        | Vss        | _          | V                | See section on Power on Reset for details                                                                                              |

| D004*         | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD              | 0.05                     | _          | -          | V/ms             | See section on Power-on Reset for details.<br>PWRT enabled                                                                             |

| D010          | Supply Current (Note 2)                                          | IDD               | —                        | 2.7        | 5          | mA               | XT RC osc configuration<br>Fosc = 4 MHz, VDD = 5.5V (Note 4)                                                                           |

| D013          |                                                                  | ٢                 | $\sqrt{-}$               | 1315       | 30         | mA               | HS osc configuration<br>Fosc = 20 MHz, VDD = 5.5V                                                                                      |

| D020<br>D020A | Power-down Current<br>(Note 3) <                                 | IPD               | (                        | 1.5<br>1.5 | 16<br>19   | μ <b>A</b><br>μA | VDD = 4.0V, -0°C to +70°C<br>VDD = 4.0V, -40°C to +85°C                                                                                |

|               | Module Differential Cur-<br>rent (Note 5)                        |                   | 7/                       |            |            |                  |                                                                                                                                        |

| D021          | Watchdog Timer                                                   |                   | $\checkmark$             | 6.0        | 20         | μA               | VDD = 4.0V                                                                                                                             |

| D023*         | Brown-out Reset Current<br>(Note 5)                              |                   | TBD                      | 200        | —          | μA               | BOR enabled, VDD = 5.0V                                                                                                                |

| D023B*        | Bahdgap voltage<br>generator                                     | ∆lbG <sup>6</sup> | —                        | 40μΑ       | TBD        | μA               |                                                                                                                                        |

| D025*         | Timer1 oscillator                                                | ∆IT1osc           | _                        | 5          | 9          | μA               | VDD = 4.0V                                                                                                                             |

| D026*         | A/D Converter                                                    | $\Delta$ IAD      | —                        | 300        | —          | μA               | VDD = 5.5V, A/D on, not converting                                                                                                     |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD MCLR = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: The ∆ current is the additional current consumed when the peripheral is enabled. This current should be added to the base (IPD or IDD) current.

- 6: The bandgap voltate reference provides 1.22V to the VRL, VRH, LVD and BOR circuits. When calculating current consumption use the following formula:  $\Delta$ IVRL +  $\Delta$ IVRH +  $\Delta$ ILVD +  $\Delta$ IBOR +  $\Delta$ IBG. Any of the  $\Delta$ IVRL,  $\Delta$ IVRH,  $\Delta$ ILVD or  $\Delta$ IBOR can be 0.

## 15.4 DC Characteristics: VREF

### TABLE 15-2 ELECTRICAL CHARACTERISTICS: VREF

| DC CHAR      | ACTERISTICS       | Standard Op<br>Operating ter | mperature      | -40°C<br>0°C | C` ≤ TA:<br>≤ TA: | ≤ +85°C<br>≤ +70°C  | for industr<br>for comme | ial and                   |

|--------------|-------------------|------------------------------|----------------|--------------|-------------------|---------------------|--------------------------|---------------------------|

| Param<br>No. | Charact           |                              | Symbol         | Min          | Typ†              | Max                 | Units                    | Conditions                |

| D400         | Output Voltage    |                              | VRL            | 2.0          | 2.048             | 2.1                 | V                        | VDD ≥ 2.5V                |

|              |                   |                              | VRH            | 4.0          | 4.096             | 4.2                 | V                        | VDØ ≥ 4.5V                |

| D401A        | VRL Quiescent S   | upply Current                | $\Delta IVRL$  | —            | 70                | TBD                 | μΑ                       | No load on VRL.           |

| D401B        | VRH Quiescent S   | Supply Current               | $\Delta IVRH$  | _            | 70                | TBD                 | µtA                      | No load on VRH.           |

| D402         | Ouput Voltage Dr  | ift                          | TCVOUT         | —            | 15*               | 50*                 | ppm/°C/                  | Note 1                    |

| D404         | External Load So  | urce                         | IVREFSO        | —            | _                 | ,5* (               | (mA                      |                           |

| D405         | External Load Sir | ık                           | IVREFSI        | —            | _                 | <- <del>5</del> * \ | ∖mA                      |                           |

| D406         | Load Regulation   |                              | AVOUT/         | —            | 1                 | TBD                 |                          | Isource = 0 mA to<br>5 mA |

|              |                   |                              |                | ~            | 71                | TBD*                | Am/V/mA                  | Isink = 0 mA to<br>5 mA   |

| D407         | Line Regulation   |                              | AVOUT/<br>AVDD | A            | _/                | 50*                 | μV/V                     |                           |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Production tested at TAMB  $= 25^{\circ}$ C. Specifications over temp limits guaranteed by characterization.

## 15.5 AC Characteristics: PIC16C77X (Commercial, Industrial)

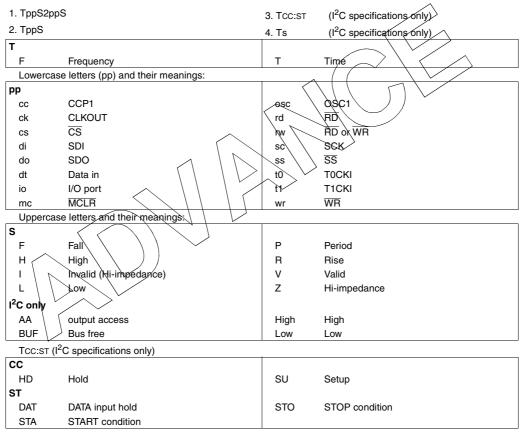

### 15.5.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

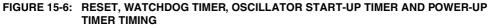

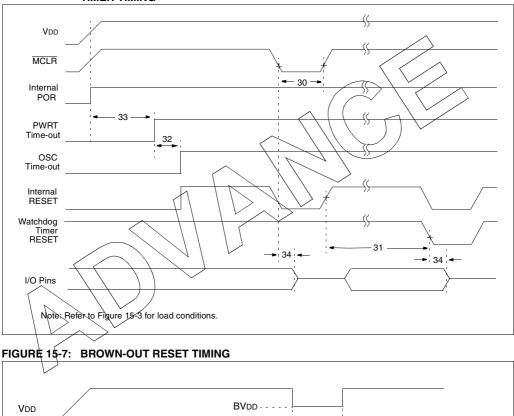

# TABLE 15-7 RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT RESET REQUIREMENTS

← 35 →

| Parameter<br>No. | Sym   | Characteristic                                         | Min | Тур†     | Max | Units | Conditions                                    |

|------------------|-------|--------------------------------------------------------|-----|----------|-----|-------|-----------------------------------------------|

| 30*              | TmcL  | MCLR Pulse Width (low)                                 | 100 | _        | —   | ns    | $VDD = 5V$ , $-40^{\circ}C$ to $+85^{\circ}C$ |

| 31*              | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler)       | 7   | 18       | 33  | ms    | VDD = 5V, -40°C to +85°C                      |

| 32*              | Tost  | Oscillation Start-up Timer Period                      | -   | 1024Tosc |     | —     | Tosc = OSC1 period                            |

| 33*              | Tpwrt | Power up Timer Period                                  | 28  | 72       | 132 | ms    | VDD = 5V, -40°C to +85°C                      |

| 34*              | Tioz  | I/O Hi-impedance from MCLR Low or Watchdog Timer Reset |     | _        | 100 | ns    |                                               |

| 35*              | TBOR  | Brown-out Reset pulse width                            | 100 | —        | —   | μS    | $VDD \le VBOR (D005)$                         |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC16C77X

NOTES: