Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

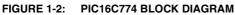

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                               |

| Data Converters            | A/D 10x12b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-TQFP                                                                   |

| Supplier Device Package    | 44-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc774-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-2 P | PIC16C774 PINOUT DESCRIPTION | (Cont.'d) |

|-------------|------------------------------|-----------|

|-------------|------------------------------|-----------|

| Pin Name             | DIP<br>Pin# | PLCC<br>Pin#   | QFP<br>Pin#     | I/O/P<br>Type | Buffer<br>Type                                 | Description                                                                                            |

|----------------------|-------------|----------------|-----------------|---------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------|

|                      |             |                |                 |               |                                                | PORTC is a bi-directional I/O port.                                                                    |

| RC0/T1OSO/T1CKI      | 15          | 16             | 32              | I/O           | ST                                             | RC0 can also be the Timer1 oscillator output or a<br>Timer1 clock input.                               |

| RC1/T1OSI/CCP2       | 16          | 18             | 35              | I/O           | ST                                             | RC1 can also be the Timer1 oscillator input or<br>Capture2 input/Compare2 output/PWM2 output.          |

| RC2/CCP1             | 17          | 19             | 36              | I/O           | ST                                             | RC2 can also be the Capture1 input/Compare1<br>output/PWM1 output.                                     |

| RC3/SCK/SCL          | 18          | 20             | 37              | I/O           | ST                                             | RC3 can also be the synchronous serial clock input/<br>output for both SPI and I <sup>2</sup> C modes. |

| RC4/SDI/SDA          | 23          | 25             | 42              | I/O           | ST                                             | RC4 can also be the SPI Data In (SPI mode) or data $I/O$ ( $I^{2}C$ mode).                             |

| RC5/SDO              | 24          | 26             | 43              | I/O           | ST                                             | RC5 can also be the SPI Data Out (SPI mode).                                                           |

| RC6/TX/CK            | 25          | 27             | 44              | I/O           | ST                                             | RC6 can also be the USART Asynchronous<br>Transmit or Synchronous Clock.                               |

| RC7/RX/DT            | 26          | 29             | 1               | I/O           | ST                                             | RC7 can also be the USART Asynchronous Receive<br>or Synchronous Data.                                 |

|                      |             |                |                 |               |                                                | PORTD is a bi-directional I/O port or parallel slave port                                              |

|                      |             |                |                 |               |                                                | when interfacing to a microprocessor bus.                                                              |

| RD0/PSP0             | 19          | 21             | 38              | I/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD1/PSP1             | 20          | 22             | 39              | I/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD2/PSP2             | 21          | 23             | 40              | I/O           | ST/TTL <sup>(3)</sup><br>ST/TTL <sup>(3)</sup> |                                                                                                        |

| RD3/PSP3<br>RD4/PSP4 | 22<br>27    | 24<br>30       | 41<br>2         | 1/O<br>1/O    | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD5/PSP5             | 27          | 30             | 2               | 1/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD6/PSP6             | 20<br>29    | 32             | 4               | 1/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

| RD7/PSP7             | 29<br>30    | 32             | 4<br>5          | 1/O           | ST/TTL <sup>(3)</sup>                          |                                                                                                        |

|                      | 30          |                | 5               | 1/0           | 31/112                                         | PORTE is a bi-directional I/O port.                                                                    |

| RE0/RD/AN5           | 8           | 9              | 25              | I/O           | ST/TTL <sup>(3)</sup>                          | RE0 can also be read control for the parallel slave<br>port, or analog input5.                         |

| RE1/WR/AN6           | 9           | 10             | 26              | I/O           | ST/TTL <sup>(3)</sup>                          | RE1 can also be write control for the parallel slave<br>port, or analog input6.                        |

| RE2/CS/AN7           | 10          | 11             | 27              | I/O           | ST/TTL <sup>(3)</sup>                          | RE2 can also be select control for the parallel slave<br>port, or analog input7.                       |

| AVss                 | 12          | 13             | 29              | Р             |                                                | Ground reference for A/D converter                                                                     |

| AVDD                 | 11          | 12             | 28              | Р             |                                                | Positive supply for A/D converter                                                                      |

| Vss                  | 31          | 34             | 6               | Р             | _                                              | Ground reference for logic and I/O pins.                                                               |

| VDD                  | 32          | 35             | 7               | P             | _                                              | Positive supply for logic and I/O pins.                                                                |

| NC                   | -           | 1,17,28,<br>40 | 12,13,<br>33,34 |               | -                                              | These pins are not internally connected. These pins should be left unconnected.                        |

| Legend: I = input    | O = outp    | ut             | I/C             | ) = input     | /output                                        | P = power                                                                                              |

|                      | — = Not     | used           | TT              | L = TTL       | . input                                        | ST = Schmitt Trigger input                                                                             |

Note 1: This buffer is a Schmitt Trigger input when configured for the multiplexed function.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured as general purpose I/O and a TTL input when used in the Parallel Slave Port mode (for interfacing to a microprocessor bus).

4: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

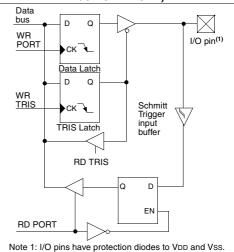

### 3.5 PORTE and TRISE Register

This section is applicable to the 40/44-pin devices only.

PORTE has three pins RE0/RD/AN5, RE1/ $\overline{WR}$ /AN6 and RE2/ $\overline{CS}$ /AN7, which are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers.

I/O PORTE becomes control inputs for the microprocessor port when bit PSPMODE (TRISE<4>) is set. In this mode, the user must make sure that the TRISE<2:0> bits are set (pins are configured as digital inputs). Ensure ADCON1 is configured for digital I/O. In this mode the input buffers are TTL.

Figure 3-12 shows the TRISE register, which also controls the parallel slave port operation.

PORTE pins are multiplexed with analog inputs. When selected as an analog input, these pins will read as '0's.

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

Note: On a Power-on Reset these pins are configured as analog inputs.

### FIGURE 3-12: TRISE REGISTER (ADDRESS 89h)

# PIC16C77X

### TABLE 3-9 PORTE FUNCTIONS

| Name       | Bit# | Buffer Type           | Function                                                                                                                                                                                         |

|------------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/RD/AN5 | bitO | ST/TTL <sup>(1)</sup> | Input/output port pin or read control input in parallel slave port mode or<br>analog input:<br>RD<br>1 = Not a read operation<br>0 = Read operation. Reads PORTD register (if chip selected)     |

| RE1/WR/AN6 | bit1 | ST/TTL <sup>(1)</sup> | Input/output port pin or write control input in parallel slave port mode or<br>analog input:<br>WR<br>1 = Not a write operation<br>0 = Write operation. Writes PORTD register (if chip selected) |

| RE2/CS/AN7 | bit2 | ST/TTL <sup>(1)</sup> | Input/output port pin or chip select control input in parallel slave port<br>mode or analog input:<br>CS<br>1 = Device is not selected<br>0 = Device is selected                                 |

Legend: ST = Schmitt Trigger input TTL = TTL input

Note 1: Input buffers are Schmitt Triggers when in I/O mode and TTL buffers when in Parallel Slave Port Mode.

| Addr | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3 | Bit 2   | Bit 1       | Bit 0    | Value on:<br>POR,<br>BOR | Value on all other resets |

|------|--------|-------|-------|-------|---------|-------|---------|-------------|----------|--------------------------|---------------------------|

| 09h  | PORTE  | —     |       | _     | —       | —     | RE2     | RE1         | RE0      | xxx                      | uuu                       |

| 89h  | TRISE  | IBF   | OBF   | IBOV  | PSPMODE | —     | PORTE D | Data Direct | ion Bits | 0000 -111                | 0000 -111                 |

| 9Fh  | ADCON1 | ADFM  | VCFG2 | VCFG1 | VCFG0   | PCFG3 | PCFG2   | PCFG1       | PCFG0    | 0000 0000                | 0000 0000                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by PORTE.

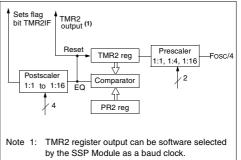

### 6.2 <u>Timer2 Interrupt</u>

The Timer2 module has an 8-bit period register PR2. Timer2 increments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register. The PR2 register is initialized to FFh upon reset.

### 6.3 Output of TMR2

The output of TMR2 (before the postscaler) is fed to the Synchronous Serial Port module which optionally uses it to generate shift clock.

### FIGURE 6-2: TIMER2 BLOCK DIAGRAM

### TABLE 6-1 REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Address               | Name   | Bit 7                | Bit 6          | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on<br>all other<br>resets |

|-----------------------|--------|----------------------|----------------|---------|---------|---------|--------|---------|---------|--------------------------|---------------------------------|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE                  | PEIE           | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x                | 0000 000u                       |

| 0Ch                   | PIR1   | PSPIF <sup>(1)</sup> | ADIF           | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 0000 0000                | 0000 0000                       |

| 8Ch                   | PIE1   | PSPIE <sup>(1)</sup> | ADIE           | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 0000 0000                | 0000 0000                       |

| 11h                   | TMR2   | Timer2 mod           | lule's registe | r       |         |         |        |         |         | 0000 0000                | 0000 0000                       |

| 12h                   | T2CON  | _                    | TOUTPS3        | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                | -000 0000                       |

| 92h                   | PR2    | Timer2 Peri          | od Register    |         |         |         |        |         |         | 1111 1111                | 1111 1111                       |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Timer2 module.

Note 1: These bits are reserved on the 28-pin, always maintain these bits clear.

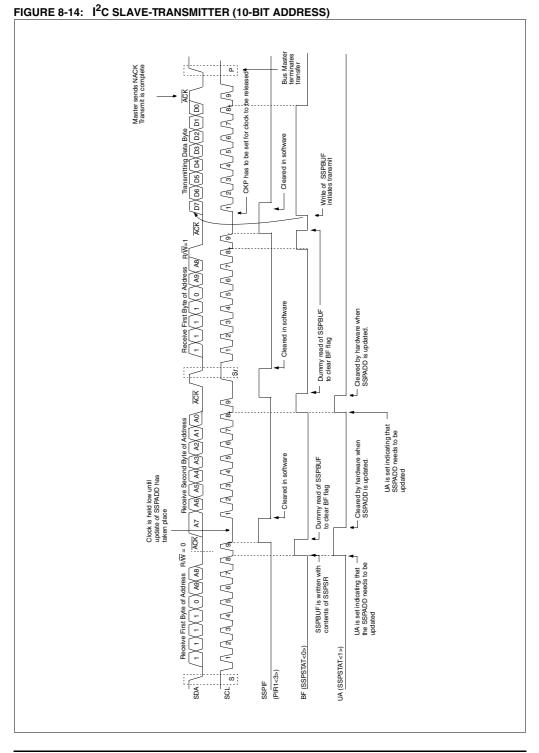

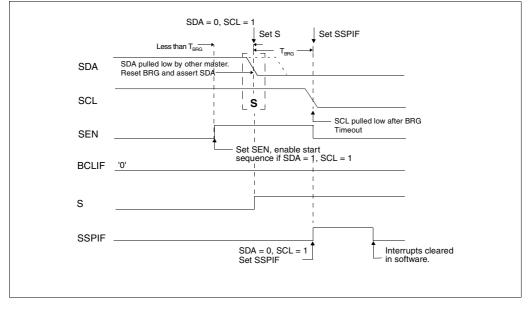

### 8.2.6 MULTI-MASTER OPERATION

In multi-master mode, the interrupt generation on the detection of the START and STOP conditions allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the MSSP module is disabled. Control of the  $I^2C$  bus may be taken when bit P (SSPSTAT<4>) is set, or the bus is idle with both the S and P bits clear. When the bus is busy, enabling the SSP Interrupt will generate the interrupt when the STOP condition occurs.

In multi-master operation, the SDA line must be monitored, for abitration, to see if the signal level is the expected output level. This check is performed in hardware, with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

- · Address Transfer

- Data Transfer

- A Start Condition

- A Repeated Start Condition

- An Acknowledge Condition

### 8.2.7 I<sup>2</sup>C MASTER OPERATION SUPPORT

Master Mode is enabled by setting and clearing the appropriate SSPM bits in SSPCON and by setting the SSPEN bit. Once master mode is enabled, the user has six options.

- Assert a start condition on SDA and SCL.

- Assert a Repeated Start condition on SDA and SCL.

- Write to the SSPBUF register initiating transmission of data/address.

- Generate a stop condition on SDA and SCL.

- Configure the I<sup>2</sup>C port to receive data.

- Generate an Acknowledge condition at the end of a received byte of data.

- Note: The MSSP Module, when configured in I<sup>2</sup>C Master Mode, does not allow queueing of events. For instance: The user is not allowed to initiate a start condition, and immediately write the SSPBUF register to initiate transmission before the START condition is complete. In this case the SSPBUF will not be written to, and the WCOL bit will be set, indicating that a write to the SSPBUF did not occur.

### 8.2.7.4 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the  $l^2C$  bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write ( $R/\overline{W}$ ) bit. In this case, the  $R/\overline{W}$  bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an acknowledge bit is received. START and STOP conditions are output to indicate the beginning and the end of a serial transfer.

In Master receive mode the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/ $\overline{W}$  bit. In this case the R/ $\overline{W}$  bit will be logic '1'. Thus the first byte transmitted is a 7-bit slave address followed by a '1' to indicate receive bit. Serial data is received via SDA while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions indicate the beginning and end of transmission.

The baud rate generator used for SPI mode operation is now used to set the SCL clock frequency for either 100 kHz, 400 kHz, or 1 MHz  $I^2C$  operation. The baud rate generator reload value is contained in the lower 7 bits of the SSPADD register. The baud rate generator will automatically begin counting on a write to the SSP-BUF. Once the given operation is complete (i.e. transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCL pin will remain in its last state

A typical transmit sequence would go as follows:

- a) The user generates a Start Condition by setting the START enable bit (SEN) in SSPCON2.

- SSPIF is set. The module will wait the required start time before any other operation takes place.

- c) The user loads the SSPBUF with address to transmit.

- d) Address is shifted out the SDA pin until all 8 bits are transmitted.

- e) The MSSP Module shifts in the ACK bit from the slave device, and writes its value into the SSPCON2 register (SSPCON2<6>).

- f) The module generates an interrupt at the end of the ninth clock cycle by setting SSPIF.

- g) The user loads the SSPBUF with eight bits of data.

- h) DATA is shifted out the SDA pin until all 8 bits are transmitted.

### 8.2.11 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address, or either half of a 10-bit address is accomplished by simply writing a value to SSPBUF register. This action will set the buffer full flag (BF) and allow the baud rate generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time spec). SCL is held low for one baud rate generator roll over count (T<sub>BRG</sub>). Data should be valid before SCL is released high (see Data setup time spec). When the SCL pin is released high, it is held that way for T<sub>BRG</sub>, the data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA allowing the slave device being addressed to respond with an ACK bit during the ninth bit time, if an address match occurs or if data was received properly. The status of ACK is read into the AKDT on the falling edge of the ninth clock. If the master receives an acknowledge, the acknowledge status bit (AKSTAT) is cleared. If not, the bit is set. After the ninth clock the SSPIF is set, and the master clock (baud rate generator) is suspended until the next data byte is loaded into the SSPBUF leaving SCL low and SDA unchanged (Figure 8-26).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock the master will de-assert the SDA pin allowing the slave to respond with an acknowledge. On the falling edge of the ninth clock the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the AKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared, and the baud rate generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 8.2.11.7 BF STATUS FLAG

In transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

#### 8.2.11.8 WCOL STATUS FLAG

If the user writes the SSPBUF when a transmit is already in progress (i.e. SSPSR is still shifting out a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

### 8.2.11.9 AKSTAT STATUS FLAG

In transmit mode, the AKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an acknowledge  $(\overline{ACK} = 0)$ , and is set when the slave does not acknowledge  $(\overline{ACK} = 1)$ . A slave sends an acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

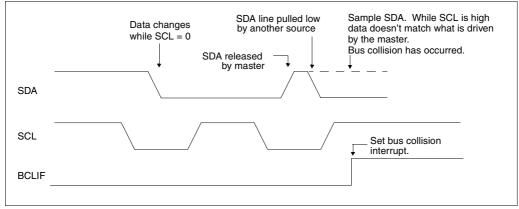

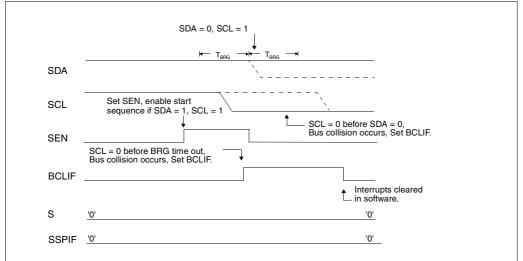

## 8.2.18 MULTI -MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the I<sup>2</sup>C port to its IDLE state. (Figure 8-34).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are de-asserted, and the SSPBUF can be written to. When the user services the bus collision interrupt service routine, and if the  $l^2C$  bus is free, the user can resume communication by asserting a START condition.

If a START, Repeated Start, STOP, or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision interrupt service routine, and if the  $l^2$ C bus is free, the user can resume communication by asserting a START condition.

The Master will continue to monitor the SDA and SCL pins, and if a STOP condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when bus collision occurred.

In multi-master mode, the interrupt generation on the detection of start and stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is idle and the S and P bits are cleared.

FIGURE 8-34: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

### FIGURE 8-37: BRG RESET DUE TO SDA COLLISION DURING START CONDITION

| BAUD<br>RATE | Fosc = 2 | 20 MHz<br>% | SPBRG<br>value |         | 0/    | SPBF<br>valu |      | 10 MHz  |       | %      | SPB<br>vali | SRG   | 7.15909 1 | ИНz<br>%  | SPBRG<br>value |       |           |

|--------------|----------|-------------|----------------|---------|-------|--------------|------|---------|-------|--------|-------------|-------|-----------|-----------|----------------|-------|-----------|

| (K)          | KBAUD    | ERROR       |                | ) KBAUD | ERRO  |              |      | KBAUD   |       |        | (deci       |       | KBAUD     | ERROR     | (decimal)      |       |           |

| 0.3          | NA       |             | -              | NA      | -     | -            |      | NA      |       | -      | -           |       | NA        |           | -              |       |           |

| 1.2          | NA       | -           | -              | NA      | -     | -            |      | NA      |       | -      | -           |       | NA        | -         | -              |       |           |

| 2.4          | NA       | -           | -              | NA      | -     | -            |      | NA      |       | -      | -           |       | NA        | -         | -              |       |           |

| 9.6          | NA       | -           | -              | NA      | -     | -            |      | 9.766   | +1    | .73    | 25          | 55    | 9.622     | +0.23     | 185            |       |           |

| 19.2         | 19.53    | +1.73       | 255            | 19.23   | +0.16 |              |      | 19.23   |       | .16    | 12          |       | 19.24     | +0.23     | 92             |       |           |

| 76.8         | 76.92    | +0.16       | 64             | 76.92   |       |              |      | 75.76   |       | .36    | 3           |       | 77.82     | +1.32     | 22             |       |           |

| 96           | 96.15    | +0.16       | 51             | 95.24   |       |              |      | 96.15   |       | .16    | 25          | -     | 94.20     | -1.88     | 18             |       |           |

| 300          | 294.1    | -1.96       | 16             | 307.69  |       |              |      | 312.5   |       | .17    | 7           |       | 298.3     | -0.57     | 5              |       |           |

| 500          | 500      | 0           | 9              | 500     | 0     | 7            |      | 500     |       | 0      | 4           |       | NA        | -         | -              |       |           |

| HIGH         | 5000     | -           | 0              | 4000    | -     | 0            |      | 2500    |       | -      | 0           |       | 1789.8    | -         | 0              |       |           |

| LOW          | 19.53    | -           | 255            | 15.625  | -     | 255          | 5    | 9.766   |       | -      | 25          | 55    | 6.991     | -         | 255            |       |           |

|              | Fosc =   | 5.0688 MH   | ۱z ،           | 4 MHz   |       |              | 3.57 | '9545 M | Hz    |        | 1           | MHz   |           |           | 32.768 k       | Hz    |           |

| BAUD         |          |             | SPBRG          |         |       | SPBRG        |      |         |       | SPBF   | RG          |       |           | SPBR      | à              |       | SPBRG     |

| RATE         | KBAUD    | %           |                | KBAUD   | %     | value        |      | AUD     | %     | valu   |             | KBAU  |           | value     | KBAUD          | %     | value     |

| (K)          |          | ERROR       | (decimal)      |         | ERROR | decimal)     |      | E       | RROR  | (decin | nal)        |       | ERRC      | R (decima | u)             | ERROR | (decimal) |

| 0.3          | NA       | -           | -              | NA      | -     | -            | Ν    | JA      | -     | -      |             | NA    | -         | -         | 0.303          | +1.14 | 26        |

| 1.2          | NA       | -           | -              | NA      | -     | -            | Ν    | A       | -     | -      |             | 1.20  | 2 +0.1    | 5 207     | 1.170          | -2.48 | 6         |

| 2.4          | NA       | -           | -              | NA      | -     | -            | Ν    | A       | -     | -      |             | 2.40  | 4 +0.1    | 5 103     | NA             | -     | -         |

| 9.6          | 9.6      | 0           | 131            | 9.615   | +0.16 | 103          | 9.   | 622 -   | +0.23 | 92     |             | 9.61  | 5 +0.1    | 6 25      | NA             | -     | -         |

| 19.2         | 19.2     | 0           | 65             | 19.231  | +0.16 | 51           |      |         | 0.83  | 46     |             | 19.24 |           |           | NA             | -     | -         |

| 76.8         | 79.2     | +3.13       | 15             | 76.923  | +0.16 | 12           |      |         | 2.90  | 11     |             | 83.3  | 4 +8.5    | 12        | NA             | -     | -         |

| 96           | 97.48    | +1.54       | 12             | 1000    | +4.17 | 9            |      |         | +3.57 | 8      | 1           | NA    | -         | -         | NA             | -     | -         |

| 300          | 316.8    | +5.60       | 3              | NA      | -     | -            |      |         | 0.57  | 2      |             | NA    | -         | -         | NA             | -     | -         |

| 500          | NA       | -           | -              | NA      | -     | -            |      | JA      | -     | -      |             | NA    | -         | -         | NA             | -     | -         |

| HIGH         | 1267     | -           | 0              | 100     | -     | 0            |      | 4.9     | -     | 0      | 1           | 250   |           | 0         | 8.192          | -     | 0         |

| LOW          | 4.950    | -           | 255            | 3.906   | -     | 255          | 3.   | 496     | -     | 255    | 5           | 0.976 | 6 -       | 255       | 0.032          | -     | 255       |

### TABLE 9-4 BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 0)

| BAUD        | Fosc = 2 |            | SPBRG             | 16 MHz |                | SPBF             | RG    | 0 MHz   |           |       | PBRG    | 7.15909 M |            | SPBRG              |        |       |

|-------------|----------|------------|-------------------|--------|----------------|------------------|-------|---------|-----------|-------|---------|-----------|------------|--------------------|--------|-------|

| RATE<br>(K) | KBAUD    | %<br>ERROR | value<br>(decimal | KBAUE  | %<br>ERRO      | valu<br>R (decim |       | KBAUD   | %<br>ERRC |       | alue    | KBAUD     | %<br>ERROR | value<br>(decimal) |        |       |

|             | -        | Ennon      | (uconnui)         |        |                | i (ucom          |       |         |           |       | connun) |           | Ennon      | (aconnai)          |        |       |

| 0.3         | NA       | -          | -                 | NA     | -              | -                |       | NA      | -         |       | -       | NA        | -          | -                  |        |       |

| 1.2         | 1.221    | +1.73      | 255               | 1.202  |                |                  |       | 1.202   | +0.1      |       | 129     | 1.203     | +0.23      | 92                 |        |       |

| 2.4         | 2.404    | +0.16      | 129               | 2.404  |                |                  | ;     | 2.404   | +0.1      |       | 64      | 2.380     | -0.83      | 46                 |        |       |

| 9.6         | 9.469    | -1.36      | 32                | 9.615  | +0.16          |                  |       | 9.766   | +1.7      |       | 15      | 9.322     | -2.90      | 11                 |        |       |

| 19.2        | 19.53    | +1.73      | 15                | 19.23  | +0.16          |                  |       | 19.53   | +1.7      |       | 7       | 18.64     | -2.90      | 5                  |        |       |

| 76.8        | 78.13    | +1.73      | 3                 | 83.33  | +8.51          | 2                |       | 78.13   | +1.7      | 3     | 1       | NA        | -          | -                  |        |       |

| 96          | 104.2    | +8.51      | 2                 | NA     | -              | -                |       | NA      | -         |       | -       | NA        | -          | -                  |        |       |

| 300         | 312.5    | +4.17      | 0                 | NA     | -              | -                |       | NA      | -         |       | -       | NA        | -          | -                  |        |       |

| 500         | NA       | -          | -                 | NA     | -              | -                |       | NA      | -         |       | -       | NA        | -          | -                  |        |       |

| HIGH        | 312.5    | -          | 0                 | 250    | -              | 0                |       | 156.3   | -         |       | 0       | 111.9     | -          | 0                  |        |       |

| LOW         | 1.221    | -          | 255               | 0.977  | -              | 255              | ;     | 0.6104  | -         | :     | 255     | 0.437     | -          | 255                |        |       |

|             | Fosc = ! | 5.0688 MH  | lz 4              | 1 MHz  |                |                  | 3.579 | 9545 MH | z         |       | 1 MHz   |           |            | 32.768 k           | Hz     |       |

| BAUD        |          |            | SPBRG             |        |                | SPBRG            |       |         |           | SPBRG |         |           | SPBRG      |                    |        | SPBRG |

| BAUD        |          | %          | value             |        | %              | value            |       | 0       |           | value |         | %         | value      |                    | %      | value |

| (K)         | KBAUD    |            | (decimal)         | KBAUD  |                |                  | ква   |         |           |       | KBAU    |           |            | ) KBAUD            |        |       |

|             | 0.31     | +3.13      | , ,               | 0.3005 | -0.17          | 207              | 0.30  |         |           | 185   | 0.300   |           | 51         | 0.256              |        |       |

| 0.3<br>1.2  | 1.2      | +3.13      | 255<br>65         | 1.202  | -0.17<br>+1.67 | 207<br>51        | 1.19  |         | .23<br>83 | 46    | 1.202   |           | 12         | 0.256<br>NA        | -14.67 | 1     |

|             |          |            |                   |        |                | -                |       |         |           |       |         |           |            |                    | -      | -     |

| 2.4         | 2.4      | 0          | 32                | 2.404  | +1.67          | 25               | 2.43  |         |           | 22    | 2.232   |           | 6          | NA                 | -      | -     |

| 9.6         | 9.9      | +3.13      | 7                 | NA     | -              | -                | 9.32  |         | 90        | 5     | NA      | -         | -          | NA                 | -      | -     |

| 19.2        | 19.8     | +3.13      | 3                 | NA     | -              | -                | 18.6  |         | 90        | 2     | NA      | -         | -          | NA                 | -      | -     |

| 76.8        | 79.2     | +3.13      | 0                 | NA     | -              | -                | NA    |         | -         | -     | NA      | -         | -          | NA                 | -      | -     |

| 96          | NA       | -          | -                 | NA     | -              | -                | NA    |         | -         | -     | NA      | -         | -          | NA                 | -      | -     |

| 300         | NA       | -          | -                 | NA     | -              | -                | NA    |         | -         | -     | NA      | -         | -          | NA                 | -      | -     |

| 500         | NA       | -          | -                 | NA     | -              | -                | NA    |         | -         | -     | NA      | -         | -          | NA                 | -      | -     |

| HIGH        | 79.2     | -          |                   | 62.500 | -              | 0                | 55.9  |         | -         | 0     | 15.63   |           | 0          | 0.512              | -      | 0     |

| LOW         | 0.3094   | -          | 255               | 3.906  | -              | 255              | 0.21  | 85      | -         | 255   | 0.061   | 0 -       | 255        | 0.0020             | -      | 255   |

| 1) |

|----|

| 1  |

| BAUD<br>RATE<br>(K)                                        | Fosc = 2<br>KBAUD                                     | 0 MHz<br>%<br>ERROR                                 | SPBRG<br>value<br>(decimal)                            | 16 MHz<br>KBAUD                                        | %<br>ERROF                       | SPBRG<br>value<br>decimal                               |                                                                    | %                                                       | b Va                                          | PBRG<br>alue<br>cimal)                           | 7.16 MHz<br>KBAUD E                                                                       | %                                             | SPBRG<br>value<br>decimal)                  |                                               |                                                  |

|------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|----------------------------------|---------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------|-----------------------------------------------|--------------------------------------------------|

| 9.6                                                        | 9.615                                                 | +0.16                                               | 129                                                    | 9.615                                                  | +0.16                            | 103                                                     | 9.615                                                              | 5 +0.                                                   | 16                                            | 64                                               | 9.520                                                                                     | -0.83                                         | 46                                          |                                               |                                                  |

| 19.2                                                       | 19.230                                                | +0.16                                               | 64                                                     | 19.230                                                 | +0.16                            | 51                                                      | 18.93                                                              | 9 -1.3                                                  | 36                                            | 32                                               | 19.454                                                                                    | +1.32                                         | 22                                          |                                               |                                                  |

| 38.4                                                       | 37.878                                                | -1.36                                               | 32                                                     | 38.461                                                 | +0.16                            | 25                                                      | 39.06                                                              | 2 +1                                                    | .7                                            | 15                                               | 37.286                                                                                    | -2.90                                         | 11                                          |                                               |                                                  |

| 57.6                                                       | 56.818                                                | -1.36                                               | 21                                                     | 58.823                                                 | +2.12                            | 16                                                      | 56.81                                                              | 8 -1.3                                                  | 36                                            | 10                                               | 55.930                                                                                    | -2.90                                         | 7                                           |                                               |                                                  |

| 115.2                                                      | 113.636                                               | -1.36                                               | 10                                                     | 111.111                                                | -3.55                            | 8                                                       | 125                                                                | +8.                                                     | 51                                            | 4                                                | 111.860                                                                                   | -2.90                                         | 3                                           |                                               |                                                  |

| 250                                                        | 250                                                   | 0                                                   | 4                                                      | 250                                                    | 0                                | 3                                                       | NA                                                                 | -                                                       |                                               | -                                                | NA                                                                                        | -                                             | -                                           |                                               |                                                  |

| 625                                                        | 625                                                   | 0                                                   | 1                                                      | NA                                                     | -                                | -                                                       | 625                                                                | 0                                                       |                                               | 0                                                | NA                                                                                        | -                                             | -                                           |                                               |                                                  |

| 1250                                                       | 1250                                                  | 0                                                   | 0                                                      | NA                                                     | -                                | -                                                       | NA                                                                 | -                                                       |                                               | -                                                | NA                                                                                        | -                                             | -                                           |                                               |                                                  |

| DALID                                                      | Fosc = 5                                              | 000 1411-                                           |                                                        |                                                        |                                  |                                                         |                                                                    |                                                         |                                               |                                                  |                                                                                           |                                               |                                             |                                               |                                                  |

| BAUD<br>RATE                                               |                                                       | %                                                   | SPBRG<br>value                                         | 4 MHz                                                  | %                                | SPBRG<br>value                                          | 8.579 MH                                                           | %                                                       | SPBRG<br>value                                |                                                  | %                                                                                         | SPBRG<br>value                                |                                             | %                                             | SPBRG<br>value                                   |

|                                                            | KBAUD                                                 | %                                                   | SPBRG<br>value                                         |                                                        |                                  | SPBRG                                                   |                                                                    | %                                                       | value                                         |                                                  | %                                                                                         |                                               |                                             |                                               | value                                            |

| RATE                                                       |                                                       | %                                                   | SPBRG<br>value                                         |                                                        |                                  | SPBRG<br>value<br>(decimal) ł                           |                                                                    | %                                                       | value                                         |                                                  | %<br>UD ERROF                                                                             | value                                         |                                             | %                                             | value                                            |

| RATE<br>(K)                                                | KBAUD                                                 | %<br>ERROR                                          | SPBRG<br>value<br>(decimal)                            | KBAUD                                                  |                                  | SPBRG<br>value<br>(decimal) ł                           | KBAUD                                                              | %<br>ERROR                                              | value<br>(decimal                             | ) KBA                                            | %<br>UD ERROF<br>28 -6.99                                                                 | value<br>(decimal)                            | ) KBAUD                                     | %                                             | value                                            |

| RATE<br>(K)<br>9.6                                         | KBAUD<br>9.6                                          | %<br>ERROR<br>0                                     | SPBRG<br>value<br>(decimal)<br>32                      | KBAUD<br>NA                                            | ERROR<br>-                       | SPBRG<br>value<br>(decimal) H                           | KBAUD<br>9.727                                                     | %<br>ERROR<br>+1.32                                     | value<br>(decimal<br>22                       | ) KBA                                            | %<br>UD ERROF<br>28 -6.99<br>33 +8.51                                                     | value<br>(decimal)<br>6                       | ) KBAUD                                     | %                                             | value                                            |

| RATE<br>(K)<br>9.6<br>19.2                                 | KBAUD<br>9.6<br>18.645                                | %<br>ERROR<br>0<br>-2.94                            | SPBRG<br>value<br>(decimal)<br>32<br>16                | KBAUD<br>NA<br>1.202                                   | ERROR<br>-<br>+0.17              | SPBRG<br>value<br>(decimal) F<br>-<br>207<br>103        | KBAUD<br>9.727<br>18.643                                           | %<br>ERROR<br>+1.32<br>-2.90                            | value<br>(decimal)<br>22<br>11                | ) KBA<br>8.92<br>20.8                            | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61                                        | value<br>(decimal)<br>6<br>2                  | ) KBAUD<br>NA<br>NA                         | ERROR<br>-<br>-                               | value<br>(decimal)<br>-<br>-                     |

| RATE<br>(K)<br>9.6<br>19.2<br>38.4<br>57.6<br>115.2        | KBAUD<br>9.6<br>18.645<br>39.6<br>52.8<br>105.6       | %<br>ERROR<br>0<br>-2.94<br>+3.12                   | SPBRG<br>value<br>(decimal)<br>32<br>16<br>7           | KBAUD<br>NA<br>1.202<br>2.403<br>9.615<br>19.231       | ERROR<br>-<br>+0.17<br>+0.13     | SPBRG<br>value<br>(decimal) H<br>207<br>103<br>25<br>12 | KBAUD<br>9.727<br>18.643<br>37.286<br>55.930<br>111.860            | %<br>ERROR<br>+1.32<br>-2.90<br>-2.90<br>-2.90<br>-2.90 | value<br>(decimal<br>22<br>11<br>5            | ) KBA<br>8.92<br>20.8<br>31.2<br>62.<br>NA       | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61<br>5 +8.51<br>A -                      | value<br>(decimal)<br>6<br>2<br>1             | ) KBAUD<br>NA<br>NA<br>NA<br>NA<br>NA       | * ERROR<br>-<br>-<br>-                        | value<br>(decimal)<br>-<br>-                     |

| RATE<br>(K)<br>9.6<br>19.2<br>38.4<br>57.6<br>115.2<br>250 | KBAUD<br>9.6<br>18.645<br>39.6<br>52.8<br>105.6<br>NA | %<br>ERROR<br>0<br>-2.94<br>+3.12<br>-8.33          | SPBRG<br>value<br>(decimal)<br>32<br>16<br>7<br>5      | KBAUD<br>NA<br>1.202<br>2.403<br>9.615<br>19.231<br>NA | +0.17<br>+0.13<br>+0.16          | SPBRG<br>value<br>(decimal) H<br>207<br>103<br>25<br>12 | KBAUD<br>9.727<br>18.643<br>37.286<br>55.930<br>111.860<br>223.721 | %<br>ERROR<br>+1.32<br>-2.90<br>-2.90<br>-2.90          | value<br>(decimal<br>22<br>11<br>5<br>3       | ) KBA<br>8.92<br>20.8<br>31.2<br>62.<br>NA<br>NA | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61<br>5 +8.51<br>A -<br>A -               | value<br>(decimal)<br>6<br>2<br>1<br>0        | ) KBAUD<br>NA<br>NA<br>NA<br>NA<br>NA<br>NA | * ERROR<br>-<br>-<br>-<br>-                   | value<br>(decimal)<br>-<br>-<br>-<br>-           |

| RATE<br>(K)<br>9.6<br>19.2<br>38.4<br>57.6<br>115.2        | KBAUD<br>9.6<br>18.645<br>39.6<br>52.8<br>105.6       | %<br>ERROR<br>0<br>-2.94<br>+3.12<br>-8.33<br>-8.33 | SPBRG<br>value<br>(decimal)<br>32<br>16<br>7<br>5<br>2 | KBAUD<br>NA<br>1.202<br>2.403<br>9.615<br>19.231       | +0.17<br>+0.13<br>+0.16<br>+0.16 | SPBRG<br>value<br>(decimal) H<br>207<br>103<br>25<br>12 | KBAUD<br>9.727<br>18.643<br>37.286<br>55.930<br>111.860            | %<br>ERROR<br>+1.32<br>-2.90<br>-2.90<br>-2.90<br>-2.90 | value<br>(decimal)<br>22<br>11<br>5<br>3<br>1 | ) KBA<br>8.92<br>20.8<br>31.2<br>62.<br>NA       | %<br>UD ERROF<br>28 -6.99<br>33 +8.51<br>25 -18.61<br>5 +8.51<br>A -<br>A -<br>A -<br>A - | value<br>R (decimal)<br>6<br>2<br>1<br>0<br>- | ) KBAUD<br>NA<br>NA<br>NA<br>NA<br>NA       | %<br>ERROR<br>-<br>-<br>-<br>-<br>-<br>-<br>- | value<br>(decimal)<br>-<br>-<br>-<br>-<br>-<br>- |

### 9.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 9-6. The data is received on the RC7/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at FOSC.

The USART module has a special provision for multiprocessor communication. When the RX9 bit is set in the RCSTA register, 9-bits are received and the ninth bit is placed in the RX9D status bit of the RSTA register. The port can be programmed such that when the stop bit is received, the serial port interrupt will only be activated if the RX9D bit = 1. This feature is enabled by setting the ADDEN bit RCSTA<3> in the RCSTA register. This feature can be used in a multi-processor system as follows:

A master processor intends to transmit a block of data to one of many slaves. It must first send out an address byte that identifies the target slave. An address byte is identified by the RX9D bit being a '1' (instead of a '0' for a data byte). If the ADDEN bit is set in the slave's RCSTA register, all data bytes will be ignored. However, if the ninth received bit is equal to a '1', indicating that the received byte is an address, the slave will be interrupted and the contents of the RSR register will be transferred into the receive buffer. This allows the slave can examine the received byte to see if it is addressed. The addressed slave will then clear its ADDEN bit and prepare to receive data bytes from the master.

When ADDEN is set, all data bytes are ignored. Following the STOP bit, the data will not be loaded into the receive buffer, and no interrupt will occur. If another byte is shifted into the RSR register, the previous data byte will be lost.

The ADDEN bit will only take effect when the receiver is configured in 9-bit mode.

The receiver block diagram is shown in Figure 9-6.

Once Asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

## 9.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

Steps to follow when setting up an Asynchronous Reception with Address Detect Enabled:

- Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is desired, set bit BRGH.

- Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

- · If interrupts are desired, then set enable bit RCIE.

- Set bit RX9 to enable 9-bit reception.

- · Set ADDEN to enable address detect.

- Enable the reception by setting enable bit CREN.

- Flag bit RCIF will be set when reception is complete, and an interrupt will be generated if enable bit RCIE was set.

- Read the RCSTA register to get the ninth bit and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREG register, to determine if the device is being addressed.

- If any error occurred, clear the error by clearing enable bit CREN.

- If the device has been addressed, clear the ADDEN bit to allow data bytes and address bytes to be read into the receive buffer, and interrupt the CPU.

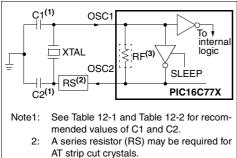

### FIGURE 12-2: CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP OSC CONFIGURATION)

3: RF varies with the crystal chosen.

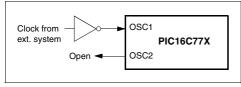

### FIGURE 12-3: EXTERNAL CLOCK INPUT OPERATION (HS OSC CONFIGURATION)

### TABLE 12-1 CERAMIC RESONATORS

| Ranges Te                                                                                                                                                                 | ested:                        |                                         |               |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------|---------------|--|--|--|--|--|--|--|--|

| Mode                                                                                                                                                                      | Freq OSC1 OSC2                |                                         |               |  |  |  |  |  |  |  |  |

| XT                                                                                                                                                                        | 455 kHz<br>2.0 MHz<br>4.0 MHz | 68 - 100 pF<br>15 - 68 pF<br>15 - 68 pF |               |  |  |  |  |  |  |  |  |

| 4.0 MHz         15 - 68 pF         15 - 68 pF           HS         8.0 MHz         10 - 68 pF         10 - 68 pF           16.0 MHz         10 - 22 pF         10 - 22 pF |                               |                                         |               |  |  |  |  |  |  |  |  |

|                                                                                                                                                                           | es at bottom of p             | <b>or design guidar</b><br>bage.        | nce only. See |  |  |  |  |  |  |  |  |

| 455 kHz                                                                                                                                                                   | Panasonic E                   | FO-A455K04B                             | ± 0.3%        |  |  |  |  |  |  |  |  |

| 2.0 MHz                                                                                                                                                                   | Murata Erie                   | CSA2.00MG                               | $\pm 0.5\%$   |  |  |  |  |  |  |  |  |

| 4.0 MHz                                                                                                                                                                   | Murata Erie                   | CSA4.00MG                               | $\pm 0.5\%$   |  |  |  |  |  |  |  |  |

| 8.0 MHz                                                                                                                                                                   | Murata Erie (                 | CSA8.00MT                               | ± 0.5%        |  |  |  |  |  |  |  |  |

| 16.0 MHz                                                                                                                                                                  | Murata Erie                   | CSA16.00MX                              | $\pm 0.5\%$   |  |  |  |  |  |  |  |  |

| All reso                                                                                                                                                                  | onators used did              | d not have built-in                     | capacitors.   |  |  |  |  |  |  |  |  |

### TABLE 12-2 CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Osc Type                                                                | Crystal<br>Freq                 | Cap. Range<br>C1 | Cap. Range<br>C2 |  |  |  |

|-------------------------------------------------------------------------|---------------------------------|------------------|------------------|--|--|--|

| LP                                                                      | 32 kHz                          | 33 pF            | 33 pF            |  |  |  |

|                                                                         | 200 kHz                         | 15 pF            | 15 pF            |  |  |  |

| XT                                                                      | 200 kHz                         | 47-68 pF         | 47-68 pF         |  |  |  |

|                                                                         | 1 MHz                           | 15 pF            | 15 pF            |  |  |  |

|                                                                         | 4 MHz                           | 15 pF            | 15 pF            |  |  |  |

| HS                                                                      | 4 MHz                           | 15 pF            | 15 pF            |  |  |  |

|                                                                         | 8 MHz                           | 15-33 pF         | 15-33 pF         |  |  |  |

|                                                                         | 20 MHz                          | 15-33 pF         | 15-33 pF         |  |  |  |

| These values are for design guidance only. See notes at bottom of page. |                                 |                  |                  |  |  |  |

| Crystals Used                                                           |                                 |                  |                  |  |  |  |

| 32 kHz                                                                  | Epson C-00                      | ± 20 PPM         |                  |  |  |  |

| 200 kHz                                                                 | STD XTL 2                       | ± 20 PPM         |                  |  |  |  |

| 1 MHz                                                                   | ECS ECS-                        | ± 50 PPM         |                  |  |  |  |

| 4 MHz                                                                   | ECS ECS-4                       | ± 50 PPM         |                  |  |  |  |

| 8 MHz                                                                   | EPSON CA                        | ± 30 PPM         |                  |  |  |  |

| 20 MHz                                                                  | EPSON CA-301 20.000M-C ± 30 PPM |                  |                  |  |  |  |

Note 1: Recommended values of C1 and C2 are identical to the ranges tested (Table 12-1).

- Higher capacitance increases the stability of oscillator but also increases the start-up time.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4: Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification.

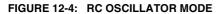

### 12.2.3 RC OSCILLATOR

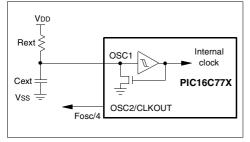

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. These factors and the variation due to tolerances of external R and C components used need to be taken into account for each application. Figure 12-4 shows how the R/C combination is connected to the PIC16C77X.

### FIGURE 12-14: WAKE-UP FROM SLEEP THROUGH INTERRUPT

|                                                         |              | Q1 Q2 Q3 Q4  | Q1 Q2 Q3 Q4       | Q1   Q2   Q3   Q4 | Q1 Q2 Q3 Q4 |

|---------------------------------------------------------|--------------|--------------|-------------------|-------------------|-------------|

|                                                         |              |              |                   |                   |             |

| CLKOUT(4) \                                             | Tost(2)      |              | \                 | \ <sup>_</sup>    | \/          |

| INT pin                                                 |              |              | 1 1<br>1 1        | 1                 |             |

| INTF flag                                               | <u>ل</u>     |              | Interrupt Latency |                   |             |

| (INTCOŇ<1>)                                             |              |              | (Note 2)          | 1                 | 1           |

| GIE bit<br>(INTCON<7>)                                  | Processor in |              |                   | 1                 |             |

| (                                                       | SLEEP        |              | · ·               | i<br>I            | 1           |

| INSTRUCTION FLOW                                        |              |              | 1 I<br>1 I        | i<br>I            | 1           |

| PC X PC X PC+1                                          | PC+2         | PC+2         | χ PC + 2          | ( 0004h           | ( 0005h     |

| Instruction<br>fetched<br>Inst(PC) = SLEEP Inst(PC + 1) |              | Inst(PC + 2) | 1 1<br>1 1<br>1 1 | Inst(0004h)       | Inst(0005h) |

| Instruction<br>executed Inst(PC - 1) SLEEP              |              | Inst(PC + 1) | Dummy cycle       | Dummy cycle       | Inst(0004h) |

| Note 1: XT, HS or LP oscillator mode assumed.           |              |              |                   |                   |             |

2: TOST = 1024TOSC (drawing not to scale) This delay will not be there for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

### 12.14 Program Verification/Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

Note: Microchip does not recommend code protecting windowed devices.

### 12.15 ID Locations

Four memory locations (2000h - 2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. It is recommended that only the 4 least significant bits of the ID location are used.

For ROM devices, these values are submitted along with the ROM code.

### 12.16 In-Circuit Serial Programming

PIC16CXXX microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

For complete details of serial programming, please refer to the In-Circuit Serial Programming (ICSP™) Guide, (DS30277).

## PIC16C77X

NOTES:

| 15.2 | DC Characteristics:PIC16LC77X-04 ( | (Commercial | . Industrial) |  |

|------|------------------------------------|-------------|---------------|--|

|      |                                    |             |               |  |

| DC CHA        | RACTERISTICS                                                     |               |      | ard Ope<br>ing tem |           |          | tions (unless otherwise stated)<br>$0^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial and<br>$C \leq TA \leq +70^{\circ}C$ for commercial |

|---------------|------------------------------------------------------------------|---------------|------|--------------------|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.  | Characteristic                                                   | Sym           | Min  | Тур†               | Max       | Units    | Conditions                                                                                                                                   |

| D001          | Supply Voltage                                                   | Vdd           | 2.5  | _                  | 5.5       | V        | LP, XT, RC osc configuration (DC - 4<br>MHz)                                                                                                 |

| D002*         | RAM Data Retention<br>Voltage (Note 1)                           | Vdr           |      | 1.5                | —         | V        |                                                                                                                                              |

| D003          | VDD start voltage to<br>ensure internal Power-on<br>Reset signal | VPOR          | _    | Vss                |           | V \      | See section on Power-on Reset for<br>details                                                                                                 |

| D004*         | VDD rise rate to ensure<br>internal Power-on Reset<br>signal     | SVDD          | 0.05 | -                  | Ĺ         | V/ms     | See section on Power-on Reset for<br>details. PWRT enabled                                                                                   |

| D010<br>D010A | Supply Current (Note 2)                                          | IDB           |      | 2.0                | 3.8<br>48 | mA<br>μA | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)<br>LP osc configuration<br>Fosc = 32 kHz, VDD = 3.0V, WDT dis-<br>abled        |

| D020<br>D020A | Power-down Current<br>(Note 3)                                   | IPD           |      | 0.9<br>0.9         | 5<br>5    | μΑ<br>μΑ | VDD = 3.0V, 0°C to +70°C<br>VDD = 3.0V, -40°C to +85°C                                                                                       |

|               | Module Differential Cur-<br>rent (note5)                         |               |      |                    |           |          |                                                                                                                                              |

| D021          | Watehdog Timer                                                   | $\Delta$ IWDT | —    | 6                  | 20        | μA       | VDD = 3.0V                                                                                                                                   |

| D023*         | Brown-out Reset Current<br>(Note 5)                              | $\Delta$ IBOR | TBD  | 200                | —         | μA       | BOR enabled, VDD = 5.0V                                                                                                                      |

| D025*         | Timer1 oscillator                                                | ∆I⊤1osc       | —    | 1.5                | 3         | μA       | VDD = 3.0V                                                                                                                                   |

| D026*         | A/D Converter                                                    | $\Delta IAD$  | —    | 300                | —         | μA       | VDD = 5.5V, A/D on, not converting                                                                                                           |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

$\frac{OSC1}{MCLR}$  = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD  $\frac{MCLR}{MCLR}$  = VDD; WDT enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

5: The ∆ current is the additional current consumed when the peripheral is enabled. This current should be added to the base (IPD or IDD) current.

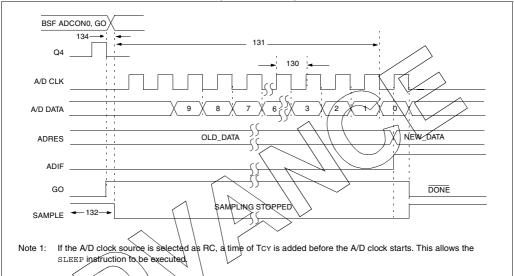

### FIGURE 15-10: A/D CONVERSION TIMING (SLEEP MODE)

### TABLE 15-11 A/D CONVERSION REQUIREMENTS

| Parameter | Sym        | Characteristic                         | Min    | Typ†         | Max | Units | Conditions                                                                                                                                                                                                           |