Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | PIC                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 20MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 33                                                                     |

| Program Memory Size        | 7KB (4K x 14)                                                          |

| Program Memory Type        | ОТР                                                                    |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                            |

| Data Converters            | A/D 10x12b                                                             |

| Oscillator Type            | External                                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                        |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                               |

| Supplier Device Package    | 40-PDIP                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc774-p |

#### TABLE 2-1 PIC16C77X SPECIAL FUNCTION REGISTER SUMMARY (Cont.'d)

| Address               | Name       | Bit 7         | Bit 6           | Bit 5         | Bit 4           | Bit 3        | Bit 2           | Bit 1       | Bit 0   | Value on:<br>POR,<br>BOR | Value on all other resets (2) |

|-----------------------|------------|---------------|-----------------|---------------|-----------------|--------------|-----------------|-------------|---------|--------------------------|-------------------------------|

| Bank 2                | -          | 1             |                 |               |                 |              |                 |             |         | -                        |                               |

| 100h <sup>(4)</sup>   | INDF       | Addressing    | this location   | uses content  | s of FSR to ad  | dress data m | emory (not a    | physical re | gister) | 0000 0000                | 0000 0000                     |

| 101h                  | TMR0       | Timer0 mod    | lule's register | •             |                 |              |                 |             |         | xxxx xxxx                | uuuu uuuu                     |

| 102h <sup>(4)</sup>   | PCL        | Program Co    | ounter's (PC)   |               | 0000 0000       | 0000 0000    |                 |             |         |                          |                               |

| 103h <sup>(4)</sup>   | STATUS     | IRP           | RP1             | RP0           | TO              | PD           | Z               | DC          | С       | 0001 1xxx                | 000q quuu                     |

| 104h <sup>(4)</sup>   | FSR        | Indirect data | memory ad       | dress pointer |                 |              |                 |             |         | xxxx xxxx                | uuuu uuuu                     |

| 105h                  | _          | Unimpleme     | nted            |               |                 |              |                 |             |         | _                        | _                             |

| 106h                  | PORTB      | PORTB Dat     | a Latch whe     |               | xxxx 11xx       | uuuu 11uu    |                 |             |         |                          |                               |

| 107h                  | _          | Unimpleme     | nted            |               |                 |              |                 |             |         | _                        | _                             |

| 108h                  | _          | Unimpleme     | nted            |               |                 |              |                 |             |         | _                        | _                             |

| 109h                  | _          | Unimpleme     | nted            |               |                 |              |                 |             |         | _                        | _                             |

| 10Ah <sup>(1,4)</sup> | PCLATH     | _             | 1               | inter         | 0 0000          | 0 0000       |                 |             |         |                          |                               |

| 10Bh <sup>(4)</sup>   | INTCON     | GIE           | PEIE            | RBIF          | 0000 000x       | 0000 000u    |                 |             |         |                          |                               |

| 10Ch-<br>10Fh         | -          | Unimpleme     | nted            |               |                 |              |                 |             |         | _                        | _                             |

| Bank 3                |            |               |                 |               |                 |              |                 |             |         |                          |                               |

| 180h <sup>(4)</sup>   | INDF       | Addressing    | this location   | uses content  | s of FSR to ad  | dress data m | emory (not a    | physical re | gister) | 0000 0000                | 0000 0000                     |

| 181h                  | OPTION_REG | RBPU          | INTEDG          | T0CS          | T0SE            | PSA          | PS2             | PS1         | PS0     | 1111 1111                | 1111 1111                     |

| 182h <sup>(4)</sup>   | PCL        | Program Co    | ounter's (PC)   | Least Signif  | icant Byte      |              |                 |             |         | 0000 0000                | 0000 0000                     |

| 183h <sup>(4)</sup>   | STATUS     | IRP           | RP1             | RP0           | TO              | PD           | z               | DC          | С       | 0001 1xxx                | 000q quuu                     |

| 184h <sup>(4)</sup>   | FSR        | Indirect data | a memory ad     | dress pointer |                 |              |                 |             |         | xxxx xxxx                | uuuu uuuu                     |

| 185h                  | _          | Unimpleme     | nted            |               |                 |              |                 |             |         | _                        | _                             |

| 186h                  | TRISB      | PORTB Dat     | a Direction F   | legister      |                 |              |                 |             |         | 1111 1111                | 1111 1111                     |

| 187h                  | _          | Unimplemented |                 |               |                 |              |                 |             |         |                          | _                             |

| 188h                  | _          | Unimpleme     | nted            |               |                 |              |                 |             |         | _                        | _                             |

| 189h                  | _          | Unimpleme     | nted            |               |                 |              |                 |             |         | _                        | _                             |

| 18Ah <sup>(1,4)</sup> | PCLATH     | _             | _               | _             | Write Buffer fo | or the upper | 5 bits of the F | Program Cou | inter   | 0 0000                   | 0 0000                        |

| 18Bh <sup>(4)</sup>   | INTCON     | GIE           | PEIE            | TOIE          | INTE            | RBIE         | TOIF            | INTF        | RBIF    | 0000 000x                | 0000 000u                     |

| 18Ch-<br>18Fh         | -          | Unimpleme     | nted            |               |                 |              |                 |             |         | -                        | _                             |

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented read as '0'.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8> whose contents are transferred to the upper byte of the program counter.

2: Other (non power-up) resets include external reset through MCLR and Watchdog Timer Reset.

3: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

<sup>4:</sup> These registers can be addressed from any bank.

5: These registers/bits are not implemented on the 28-pin devices read as '0'.

TABLE 3-5 PORTC FUNCTIONS

| Name            | Bit# | Buffer Type | Function                                                                                       |

|-----------------|------|-------------|------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input                           |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1 output                            |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes.          |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output                                   |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin or USART Asynchronous transmit or Synchronous clock                      |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin or USART Asynchronous receive or Synchronous data                        |

Legend: ST = Schmitt Trigger input

### TABLE 3-6 SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7   | Bit 6       | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|---------|-------------|------------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 07h     | PORTC | RC7     | RC6         | RC5        | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                 |

| 87h     | TRISC | PORTC I | Data Direct | ion Regist | er    |       |       |       |       | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged.

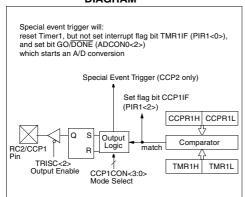

#### 7.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RC2/CCP1 pin is:

- · driven High

- · driven Low

- · remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

FIGURE 7-3: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 7.2.1 CCP PIN CONFIGURATION

The user must configure the RC2/CCP1 pin as an output by clearing the TRISC<2> bit.

Note: Clearing the CCP1CON register will force the RC2/CCP1 compare output latch to the default low level. This is not the data latch.

#### 7.2.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 7.2.3 SOFTWARE INTERRUPT MODE

When generate software interrupt is chosen the CCP1 pin is not affected. Only a CCP interrupt is generated (if enabled).

#### 7.2.4 SPECIAL EVENT TRIGGER

In this mode, an internal hardware trigger is generated which may be used to initiate an action.

The special event trigger output of CCP1 resets the TMR1 register pair. This allows the CCPR1 register to effectively be a 16-bit programmable period register for Timer1

The special trigger output of CCP2 resets the TMR1 register pair, and starts an A/D conversion (if the A/D module is enabled).

Note: The special event trigger from the CCP2 module will not set interrupt flag bit TMR1IF (PIR1<0>).

#### TABLE 7-3 REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, AND TIMER1

| Address               | Name    | Bit 7                                  | Bit 6                               | it 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |             |               |            |             |        |      | Value on:<br>POR,<br>BOR |      | Value on<br>all other<br>resets |  |

|-----------------------|---------|----------------------------------------|-------------------------------------|------------------------------------------|-------------|---------------|------------|-------------|--------|------|--------------------------|------|---------------------------------|--|

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON  | GIE                                    | PEIE                                | TOIE                                     | INTE        | RBIE          | TOIF       | INTF        | RBIF   | 0000 | 000x                     | 0000 | 000u                            |  |

| 0Ch                   | PIR1    | PSPIF <sup>(1)</sup>                   | ADIF                                | RCIF                                     | TXIF        | SSPIF         | CCP1IF     | TMR2IF      | TMR1IF | 0000 | 0000                     | 0000 | 0000                            |  |

| 8Ch                   | PIE1    | PSPIE <sup>(1)</sup>                   | ADIE                                | RCIE                                     | TXIE        | SSPIE         | CCP1IE     | TMR2IE      | TMR1IE | 0000 | 0000                     | 0000 | 0000                            |  |

| 87h                   | TRISC   | PORTC Da                               | ta Dire                             | ction Regis                              | ter         | •             |            |             |        | 1111 | 1111                     | 1111 | 1111                            |  |

| 0Eh                   | TMR1L   | Holding reg                            | gister fo                           | r the Least                              | Significant | Byte of the   | 16-bit TMF | R1 register |        | xxxx | xxxx                     | uuuu | uuuu                            |  |

| 0Fh                   | TMR1H   | Holding reg                            | gister fo                           | r the Most                               | Significant | Byte of the 1 | 6-bit TMR  | 1register   |        | xxxx | xxxx                     | uuuu | uuuu                            |  |

| 10h                   | T1CON   | _                                      | _                                   | T1CKPS1                                  | T1CKPS0     | T10SCEN       | T1SYNC     | TMR1CS      | TMR10N | 00   | 0000                     | uu   | uuuu                            |  |

| 15h                   | CCPR1L  | Capture/Co                             | Capture/Compare/PWM register1 (LSB) |                                          |             |               |            |             |        | xxxx | xxxx                     | uuuu | uuuu                            |  |

| 16h                   | CCPR1H  | Capture/Co                             | Capture/Compare/PWM register1 (MSB) |                                          |             |               |            |             |        |      | xxxx                     | uuuu | uuuu                            |  |

| 17h                   | CCP1CON | - CCP1X CCP1Y CCP1M3 CCP1M2 CCP1M1 CCP |                                     |                                          |             |               |            |             |        | 00   | 0000                     | 00   | 0000                            |  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by Capture and Timer1.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin, always maintain these bits clear.

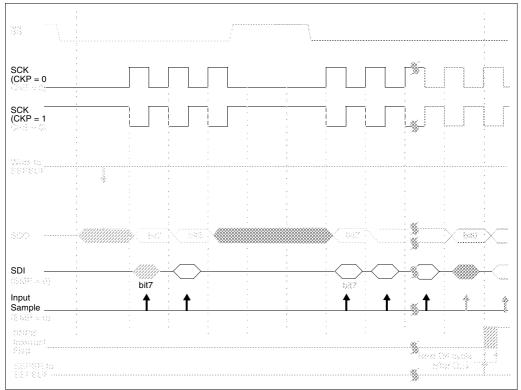

#### 8.1.5 SLAVE MODE

In slave mode, the data is transmitted and received as the external clock pulses appear on SCK. When the last bit is latched the interrupt flag bit SSPIF (PIR1<3>) is set

While in slave mode the external clock is supplied by the external clock source on the SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

While in sleep mode, the slave can transmit/receive data. When a byte is received the device will wake-up from sleep.

#### 8.1.6 SLAVE SELECT SYNCHRONIZATION

The  $\overline{SS}$  pin allows a synchronous slave mode. The SPI must be in slave mode with  $\overline{SS}$  pin control enabled (SSPCON<3:0> = 0100). The pin must not be driven low for the  $\overline{SS}$  pin to function as an input. TRISA<5> must be set. When the  $\overline{SS}$  pin is low, transmission and reception are enabled and the SDO pin is driven. When the  $\overline{SS}$  pin goes high, the

SDO pin is no longer driven, even if in the middle of a transmitted byte, and becomes a floating output. External pull-up/pull-down resistors may be desirable, depending on the application.

Note: When the SPI module is in Slave Mode with  $\overline{SS}$  pin control enabled, (SSP-CON<3:0> = 0100) the SPI module will reset if the  $\overline{SS}$  pin is set to VDD.

**Note:** If the SPI is used in Slave Mode with CKE = '1', then  $\overline{SS}$  pin control must be enabled.

When the SPI module resets, the bit counter is forced to 0. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit.

To emulate two-wire communication, the SDO pin can be connected to the SDI pin. When the SPI needs to operate as a receiver the SDO pin can be configured as an input. This disables transmissions from the SDO. The SDI can always be left as an input (SDI function) since it cannot create a bus conflict.

FIGURE 8-7: SLAVE SYNCHRONIZATION WAVEFORM

#### 8.1.7 SLEEP OPERATION

In master mode all module clocks are halted, and the transmission/reception will remain in that state until the device wakes from sleep. After the device returns to normal mode, the module will continue to transmit/ receive data

In slave mode, the SPI transmit/receive shift register operates asynchronously to the device. This allows the device to be placed in sleep mode, and data to be shifted into the SPI transmit/receive shift register. When all 8-bits have been received, the MSSP interrupt flag bit will be set and if enabled will wake the device from sleep.

#### 8.1.8 EFFECTS OF A RESET

A reset disables the MSSP module and terminates the current transfer.

TABLE 8-1 REGISTERS ASSOCIATED WITH SPI OPERATION

| Address                | Name    | Bit 7                | Bit 6        | Bit 5      | Bit 4     | Bit 3      | Bit 2  | Bit 1  | Bit 0  | POR, BOR  | MCLR, WDT |

|------------------------|---------|----------------------|--------------|------------|-----------|------------|--------|--------|--------|-----------|-----------|

| 0Bh, 8Bh,<br>10Bh,18Bh | INTCON  | GIE                  | PEIE         | TOIE       | INTE      | RBIE       | TOIF   | INTF   | RBIF   | 0000 000x | 0000 000u |

| 0Ch                    | PIR1    | PSPIF <sup>(1)</sup> | ADIF         | RCIF       | TXIF      | SSPIF      | CCP1IF | TMR2IF | TMR1IF | 0000 0000 | 0000 0000 |

| 8Ch                    | PIE1    | PSPIE <sup>(1)</sup> | ADIE         | RCIE       | TXIE      | SSPIE      | CCP1IE | TMR2IE | TMR1IE | 0000 0000 | 0000 0000 |

| 13h                    | SSPBUF  | Synchronou           | ıs Serial Po | rt Receive | Buffer/Tr | ansmit Reg | ister  |        |        | xxxx xxxx | uuuu uuuu |

| 14h                    | SSPCON  | WCOL                 | SSPOV        | SSPEN      | СКР       | SSPM3      | SSPM2  | SSPM1  | SSPM0  | 0000 0000 | 0000 0000 |

| 94h                    | SSPSTAT | SMP                  | CKE          | D/Ā        | Р         | S          | R/W    | UA     | BF     | 0000 0000 | 0000 0000 |

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the SSP in SPI mode. These bits are reserved on the 28-pin devices, always maintain these bits clear. Legend:

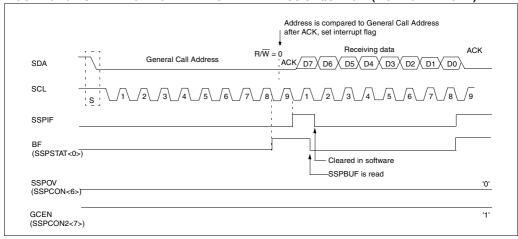

#### 8.2.2 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the I<sup>2</sup>C bus is such that the first byte after the START condition usually determines which device will be the slave addressed by the master. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is one of eight addresses reserved for specific purposes by the  $I^2C$  protocol. It consists of all 0's with  $P/\overline{W} = 0$

The general call address is recognized when the General Call Enable bit (GCEN) is enabled (SSPCON2<7> is set). Following a start-bit detect, 8-bits are shifted into SSPSR and the address is compared against SSPADD, and is also compared to the general call address, fixed in hardware.

If the general call address matches, the SSPSR is transfered to the SSPBUF, the BF flag is set (eighth bit), and on the falling edge of the ninth bit (ACK bit) the SSPIF flag is set.

When the interrupt is serviced. The source for the interrupt can be checked by reading the contents of the SSPBUF to determine if the address was device specific or a general call address.

In 10-bit mode, the SSPADD is required to be updated for the second half of the address to match, and the UA bit is set (SSPSTAT<1>). If the general call address is sampled when GCEN is set while the slave is configured in 10-bit address mode, then the second half of the address is not necessary, the UA bit will not be set, and the slave will begin receiving data after the acknowledge (Figure 8-16).

FIGURE 8-16: SLAVE MODE GENERAL CALL ADDRESS SEQUENCE (7 OR 10-BIT MODE)

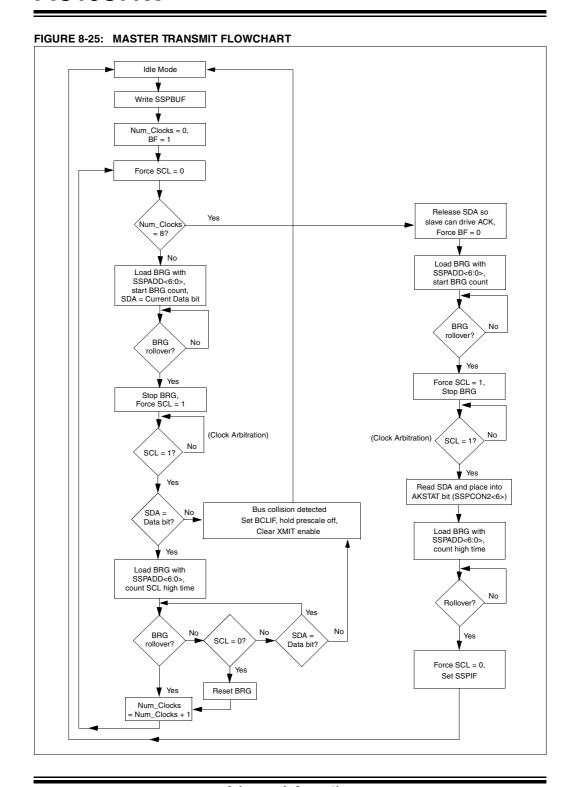

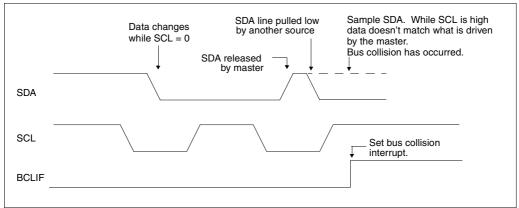

## 8.2.18 MULTI -MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

Multi-Master mode support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high and another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = '0', then a bus collision has taken place. The master will set the Bus Collision Interrupt Flag, BCLIF and reset the I<sup>2</sup>C port to its IDLE state. (Figure 8-34).

If a transmit was in progress when the bus collision occurred, the transmission is halted, the BF flag is cleared, the SDA and SCL lines are de-asserted, and the SSPBUF can be written to. When the user services the bus collision interrupt service routine, and if the  $\rm l^2C$  bus is free, the user can resume communication by asserting a START condition.

If a START, Repeated Start, STOP, or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the SSPCON2 register are cleared. When the user services the bus collision interrupt service routine, and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a START condition.

The Master will continue to monitor the SDA and SCL pins, and if a STOP condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of data at the first data bit, regardless of where the transmitter left off when bus collision occurred.

In multi-master mode, the interrupt generation on the detection of start and stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the SSPSTAT register, or the bus is idle and the S and P bits are cleared.

FIGURE 8-34: BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

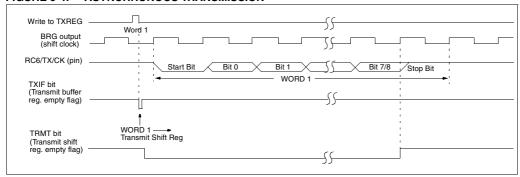

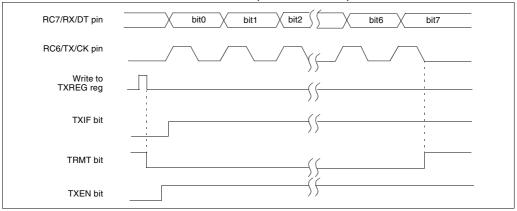

#### FIGURE 9-4: ASYNCHRONOUS TRANSMISSION

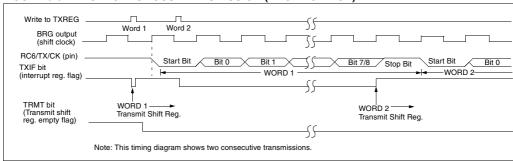

#### FIGURE 9-5: ASYNCHRONOUS TRANSMISSION (BACK TO BACK)

#### TABLE 9-6 REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address | Name  | Bit 7                | Bit 6    | Bit 5    | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on<br>all other<br>Resets |

|---------|-------|----------------------|----------|----------|-------|-------|--------|--------|--------|--------------------------|---------------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF     | RCIF     | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                       |

| 18h     | RCSTA | SPEN                 | RX9      | SREN     | CREN  | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                       |

| 19h     | TXREG | USART Tra            | ansmit F | Register |       |       |        |        |        | 0000 0000                | 0000 0000                       |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE     | RCIE     | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                       |

| 98h     | TXSTA | CSRC                 | TX9      | TXEN     | SYNC  | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                       |

| 99h     | SPBRG | Baud Rate            | Genera   | tor Regi | ster  |       |        |        |        | 0000 0000                | 0000 0000                       |

Legend: x = unknown, - = unimplemented locations read as '0'. Shaded cells are not used for Asynchronous Transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

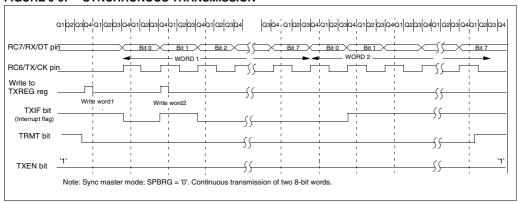

### FIGURE 9-9: SYNCHRONOUS TRANSMISSION

### FIGURE 9-10: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### TABLE 9-10 REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

| Address | Name  | Bit 7                | Bit 6  | Bit 5    | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|--------|----------|--------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF   | RCIF     | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9    | SREN     | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                 |

| 19h     | TXREG | USART Tr             | ansmit | Register |        |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE   | RCIE     | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9    | TXEN     | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate            | Gener  | ator Reg | jister |       |        | •      |        | 0000 0000                | 0000 0000                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Transmission.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

#### TABLE 9-11 REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

| Address | Name  | Bit 7                | Bit 6    | Bit 5    | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR,<br>BOR | Value on all other Resets |

|---------|-------|----------------------|----------|----------|--------|-------|--------|--------|--------|--------------------------|---------------------------|

| 0Ch     | PIR1  | PSPIF <sup>(1)</sup> | ADIF     | RCIF     | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000                | 0000 0000                 |

| 18h     | RCSTA | SPEN                 | RX9      | SREN     | CREN   | ADDEN | FERR   | OERR   | RX9D   | 0000 000x                | 0000 000x                 |

| 1Ah     | RCREG | USART R              | eceive I | Register |        |       |        |        |        | 0000 0000                | 0000 0000                 |

| 8Ch     | PIE1  | PSPIE <sup>(1)</sup> | ADIE     | RCIE     | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000                | 0000 0000                 |

| 98h     | TXSTA | CSRC                 | TX9      | TXEN     | SYNC   | _     | BRGH   | TRMT   | TX9D   | 0000 -010                | 0000 -010                 |

| 99h     | SPBRG | Baud Rate            | Gener    | ator Reg | jister |       |        |        |        | 0000 0000                | 0000 0000                 |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for Synchronous Slave Reception.

Note 1: Bits PSPIE and PSPIF are reserved on the 28-pin devices, always maintain these bits clear.

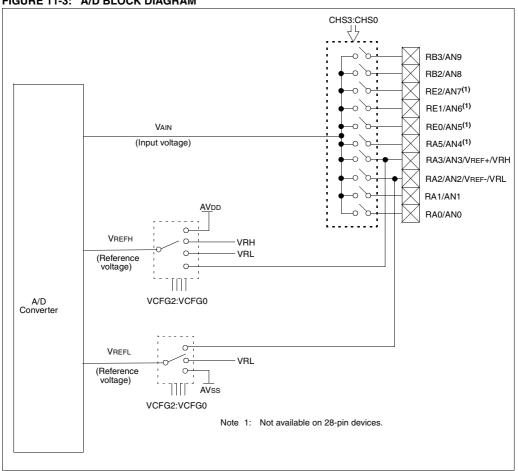

# 11.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

The analog-to-digital (A/D) converter module has six inputs for the PIC16C773 and ten for the PIC16C774.

The analog-to-digital converter (A/D) allows conversion of an analog input signal to a corresponding 12-bit digital number. The A/D module has up to 10 analog inputs, which are multiplexed into one sample and hold. The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog reference voltages are software selectable to either the device's analog positive and negative supply voltages (AVDD/AVss), the voltage level on the VREF+ and VREF- pins, or internal voltage references if available (VRH, VRL).

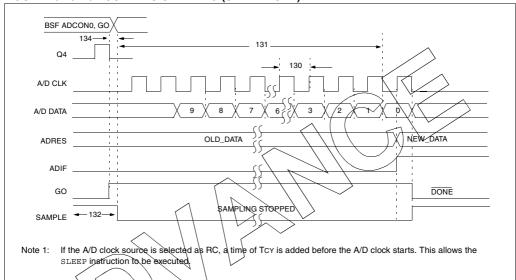

The A/D converter has a unique feature of being able to operate while the device is in SLEEP mode. To operate in sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The A/D module has four registers. These registers are:

- A/D Result Register Low ADRESL

- · A/D Result Register High ADRESH

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

A device reset forces all registers to their reset state. This forces the A/D module to be turned off and any conversion is aborted.

#### 11.1 Control Registers

The ADCON0 register, shown in Figure 11-1, controls the operation of the A/D module. The ADCON1 register, shown in Figure 11-2, configures the functions of the port pins, the voltage reference configuration and the result format. The port pins can be configured as analog inputs or as digital I/O.

The combination of the ADRESH and ADRESL registers contain the result of the A/D conversion. The register pair is referred to as the ADRES register. When the A/D conversion is complete, the result is loaded into ADRES, the GO/DONE bit (ADCON0<2>) is cleared, and the A/D interrupt flag ADIF is set. The block diagram of the A/D module is shown in Figure 11-3.

#### FIGURE 11-1: ADCONO REGISTER (ADDRESS 1Fh).

| R/W-0     | R/W-0                                                         | R/W-0                                                                                                         | R/W-0                                                                                            | R/W-0                                            | R/W-0                                                                                | R/W-0                                     | R/W-0                |              |                                    |

|-----------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------|----------------------|--------------|------------------------------------|

| ADCS1     | ADCS0                                                         | CHS2                                                                                                          | CHS1                                                                                             | CHS0                                             | GO/DONE                                                                              | CHS3                                      | ADON                 | R =          | Readable bit                       |

| bit7      |                                                               |                                                                                                               |                                                                                                  |                                                  |                                                                                      |                                           | bit 0                | W =<br>- n = | Writable bit<br>Value at POR reset |

| bit 7:6   | 00 = Fosc<br>01 = Fosc<br>10 = Fosc                           | /2<br>/8<br>/32                                                                                               |                                                                                                  |                                                  | Select bits  illator = 1 MHz                                                         | z max)                                    |                      |              |                                    |

| bit 5:3,1 | 0101 = ch<br>0110 = ch<br>0111 = ch<br>1000 = ch<br>1001 = ch | annel 00 ( annel 01 ( annel 02 ( annel 03 ( annel 04 ( annel 05 ( annel 06 ( annel 07 ( annel 08 ( annel 09 ( | AN0)<br>AN1)<br>AN2)<br>AN3)<br>AN4) (Re:<br>AN5) (Re:<br>AN6) (Re:<br>AN7) (Re:<br>AN8)<br>AN9) | served on<br>served on<br>served on<br>served on | 28-pin device:<br>28-pin device:<br>28-pin device:<br>28-pin device:<br>reserved, do | s, do not u<br>s, do not u<br>s, do not u | ise)<br>ise)<br>ise) |              |                                    |

| bit 2:    |                                                               | onversion on automatic                                                                                        | cycle in pr<br>ally cleare                                                                       | ogress. Seed by hard                             | etting this bit s<br>ware when the<br>ogress                                         |                                           |                      |              |                                    |

| bit 0:    | ADON: A/<br>1 = A/D co<br>0 = A/D co                          | nverter m                                                                                                     |                                                                                                  |                                                  |                                                                                      |                                           |                      |              |                                    |

FIGURE 11-3: A/D BLOCK DIAGRAM

#### 14.10 MPLAB Integrated Development Environment Software

The MPLAB IDE Software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a windows based application which contains:

- · A full featured editor

- · Three operating modes

- editor

- emulator

- simulator

- · A project manager

- · Customizable tool bar and key mapping

- · A status bar with project information

- · Extensive on-line help

#### MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PICmicro tools (automatically updates all project information)

- · Debug using:

- source files

- absolute listing file

The ability to use MPLAB with Microchip's simulator allows a consistent platform and the ability to easily switch from the low cost simulator to the full featured emulator with minimal retraining due to development tools.

#### 14.11 Assembler (MPASM)

The MPASM Universal Macro Assembler is a PC-hosted symbolic assembler. It supports all microcontroller series including the PIC12C5XX, PIC14000, PIC16C5X, PIC16CXXX, and PIC17CXX families.

MPASM offers full featured Macro capabilities, conditional assembly, and several source and listing formats. It generates various object code formats to support Microchip's development tools as well as third party programmers.

MPASM allows full symbolic debugging from MPLAB-ICE, Microchip's Universal Emulator System.

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- · Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PICmicro. Directives are helpful in making the development of your assemble source code shorter and more maintainable

#### 14.12 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PICmicro series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C17 and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

#### 14.13 MPLAB-C17 Compiler

The MPLAB-C17 Code Development System is a complete ANSI 'C' compiler and integrated development environment for Microchip's PIC17CXXX family of microcontrollers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display.

## 14.14 Fuzzy Logic Development System (fuzzyTECH-MP)

fuzzyTECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, fuzzyTECH-MP, Edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB™ demonstration board for hands-on experience with fuzzy logic systems implementation.

## 14.15 <u>SEEVAL® Evaluation and</u> Programming System

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials™ and secure serials. The Total Endurance™ Disk is included to aid in trade-off analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

#### **DC Characteristics: VREF** 15.4

#### **TABLE 15-2 ELECTRICAL CHARACTERISTICS: VREF**

| DC CHAR      | Standard O Operating te Operating vo | mperature       | -40°C | C ` ≤ TA :<br>≤ TA : | ≤ +85°C 1<br>≤ +70°C 1 | for industr<br>for comme | ial and           |

|--------------|--------------------------------------|-----------------|-------|----------------------|------------------------|--------------------------|-------------------|

| Param<br>No. | Characteristic                       | Symbol          | Min   | Тур†                 | Max                    | Units                    | Conditions        |

| D400         | Output Voltage                       | VRL             | 2.0   | 2.048                | 2.1                    | V                        | VDD ≥ 2.5V)       |

|              |                                      | VRH             | 4.0   | 4.096                | 4.2                    | V                        | VDØ ≥ 4.5V        |

| D401A        | VRL Quiescent Supply Current         | $\Delta IV$ RL  | _     | 70                   | TBD                    | μΑ                       | No load on VRL.   |

| D401B        | VRH Quiescent Supply Current         | ΔIVRH           | _     | 70                   | TBD                    | μA                       | No load on VRH.   |

| D402         | Ouput Voltage Drift                  | TCVout          | _     | 15*                  | 50*                    | ppm/°C/                  | Note 1            |

| D404         | External Load Source                 | IVREFSO         | _     | _                    | 5*                     | /mA                      |                   |

| D405         | External Load Sink                   | Ivrefsi         | _     | _                    | -5*                    | \mA                      |                   |

| D406         | Load Regulation                      |                 | _     | 1                    | J/BD/                  |                          | Isource = 0 mA to |

|              |                                      | $\Delta V$ OUT/ |       |                      |                        | mV/mA                    | 5 mA              |

|              |                                      | $\Delta$ lout   | . —   | 11 /                 | TBD∕₹                  | ALLACTIVA                | Isink = 0 mA to   |

|              |                                      |                 |       | \ \                  |                        |                          | 5 mA              |

| D407         | Line Regulation                      | ∆Vout/<br>∆Vdd  | P     | _/                   | \$0*                   | μ <b>V/V</b>             |                   |

Note 1: Production tested at TAMB = 25 °C. Specifications over temp limits guaranteed by characterization.

<sup>\*</sup> These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

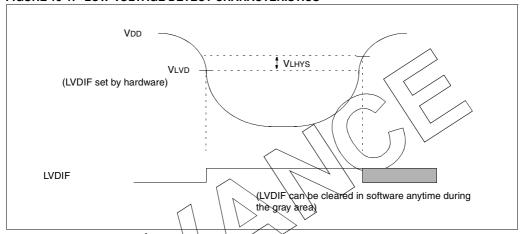

FIGURE 15-1: LOW-VOLTAGE DETECT CHARACTERISTICS

TABLE 15-3 ELECTRICAL CHARACTER STICS: LVD

|         |                     | Standard Opera    | ating Condit  | ione (u | nless (  | therwi  | se stater   | 1)                          |

|---------|---------------------|-------------------|---------------|---------|----------|---------|-------------|-----------------------------|

|         |                     | Operating temper  |               |         |          |         | for industr |                             |

| DC CHAI | RACTERISTICS        | Operating tempe   |               | °C      |          |         | for comme   |                             |

|         |                     | Operating voltage | -             | -       |          |         |             | on 15.1 and Section 15.2.   |

| Barra   | $\overline{}$       | porating voitage  | le voo range  | uo uco  | CIIDCA I | 11 00 3 | pec occin   | 011 10:1 una Occiloti 10:2: |

| Param   | Charact             | eristic           | Symbol        | Min     | Typ†     | Max     | Units       | Conditions                  |

| No.     |                     | <u>/</u>          | -             |         |          |         |             |                             |

| D420    | LVD Voltage         | LVV = 0100        |               | 2.5     | 2.58     | 2.66    | V           |                             |

| \       |                     | LVV = 0101        |               | 2.7     | 2.78     | 2.86    | V           |                             |

| \       |                     | LVV = 0110        |               | 2.8     | 2.89     | 2.98    | V           |                             |

| \       |                     | LVV = 0111        |               | 3.0     | 3.1      | 3.2     | V           |                             |

|         |                     | LVV = 1000        |               | 3.3     | 3.41     | 3.52    | V           |                             |

|         |                     | LVV = 1001        |               | 3.5     | 3.61     | 3.72    | V           |                             |

|         |                     | LVV = 1010        |               | 3.6     | 3.72     | 3.84    | V           |                             |

|         |                     | LVV = 1011        |               | 3.8     | 3.92     | 4.04    | V           |                             |

|         |                     | LVV = 1100        |               | 4.0     | 4.13     | 4.26    | V           |                             |

|         |                     | LVV = 1101        |               | 4.2     | 4.33     | 4.46    | V           |                             |

|         |                     | LVV = 1110        |               | 4.5     | 4.64     | 4.78    | V           |                             |

| D421    | Supply Current      |                   | ΔİLVD         | _       | 10       | 20      | μΑ          |                             |

| D422*   | LVD Voltage Drift 7 | emperature        | TCVout        | _       | 15       | 50      | ppm/°C      |                             |

|         | coefficient         |                   |               |         |          |         |             |                             |

| D423*   | LVD Voltage Drift v | vith respect to   | ΔVLVD/        | _       | _        | 50      | μV/V        |                             |

|         | VDD Regulation      |                   | $\Delta V$ DD |         |          |         |             |                             |

| D424*   | Low-voltage Detec   | t Hysteresis      | VLHYS         | TBD     | _        | 100     | mV          |                             |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Production tested at Tamb = 25°C. Specifications over temp limits ensured by characterization.

#### FIGURE 15-10: A/D CONVERSION TIMING (SLEEP MODE)

### TABLE 15-11 A/D CONVERSION REQUIREMENTS

| Parameter | Sym  | Characteristic                                           | Min    | Typ†         | Max | Units | Conditions                                                                                                                                                                                            |

|-----------|------|----------------------------------------------------------|--------|--------------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.       |      |                                                          |        | -761         |     |       |                                                                                                                                                                                                       |

| 130       | TAD  | A/D clock period                                         | 1.6    | _            | _   | μS    | VREF ≥ 2.5V                                                                                                                                                                                           |

| \         |      |                                                          | TBD    | _            | _   | μS    | VREF full range                                                                                                                                                                                       |

| 130*      | TAD  | A/D Internal RC                                          |        |              |     |       | ADCS1:ADCS0 = 11 (RC mode)                                                                                                                                                                            |

|           |      | oscillator period                                        | 3.0    | 6.0          | 9.0 | μS    | At VDD = 3.0V                                                                                                                                                                                         |

|           |      |                                                          | 2.0    | 4.0          | 6.0 | μS    | At VDD = 5.0V                                                                                                                                                                                         |

| 131*      | TCNV | Conversion time (not including acquisition time)(Note 1) | _      | 13TAD        | _   | _     |                                                                                                                                                                                                       |

| 132*      | TACQ | Acquisition Time                                         | Note 2 | 11.5         |     | μS    |                                                                                                                                                                                                       |

|           |      |                                                          | 5*     | _            | l   | μѕ    | The minimum time is the amplifier settling time. This may be used if the "new" input voltage has not changed by more than 1LSb (i.e 1mV @ 4.096V) from the last sampled voltage (as stated on CHOLD). |

| 134*      | TGO  | Q4 to A/D clock start                                    | _      | Tosc/2 + Tcy | _   | _     | If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                      |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: ADRES register may be read on the following Tcy cycle.

<sup>2:</sup> See Section 11.6 for minimum conditions.

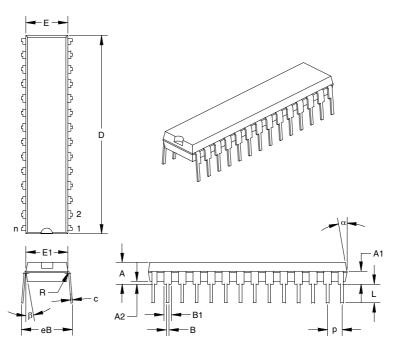

### 17.2 K04-070 28-Lead Skinny Plastic Dual In-line (SP) – 300 mil

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                        |                 | INCHES* |       |       | MILLIMETERS |       |       |

|------------------------------|-----------------|---------|-------|-------|-------------|-------|-------|

| Dimension Limits             |                 | MIN     | MON   | MAX   | MIN         | MOM   | MAX   |

| PCB Row Spacing              |                 |         | 0.300 |       |             | 7.62  |       |

| Number of Pins               | n               |         | 28    |       |             | 28    |       |

| Pitch                        | р               |         | 0.100 |       |             | 2.54  |       |

| Lower Lead Width             | В               | 0.016   | 0.019 | 0.022 | 0.41        | 0.48  | 0.56  |

| Upper Lead Width             | B1 <sup>†</sup> | 0.040   | 0.053 | 0.065 | 1.02        | 1.33  | 1.65  |

| Shoulder Radius              | R               | 0.000   | 0.005 | 0.010 | 0.00        | 0.13  | 0.25  |

| Lead Thickness               | С               | 0.008   | 0.010 | 0.012 | 0.20        | 0.25  | 0.30  |

| Top to Seating Plane         | Α               | 0.140   | 0.150 | 0.160 | 3.56        | 3.81  | 4.06  |

| Top of Lead to Seating Plane | A1              | 0.070   | 0.090 | 0.110 | 1.78        | 2.29  | 2.79  |

| Base to Seating Plane        | A2              | 0.015   | 0.020 | 0.025 | 0.38        | 0.51  | 0.64  |

| Tip to Seating Plane         | L               | 0.125   | 0.130 | 0.135 | 3.18        | 3.30  | 3.43  |

| Package Length               | D <sup>‡</sup>  | 1.345   | 1.365 | 1.385 | 34.16       | 34.67 | 35.18 |

| Molded Package Width         | E‡              | 0.280   | 0.288 | 0.295 | 7.11        | 7.30  | 7.49  |

| Radius to Radius Width       | E1              | 0.270   | 0.283 | 0.295 | 6.86        | 7.18  | 7.49  |

| Overall Row Spacing          | eB              | 0.320   | 0.350 | 0.380 | 8.13        | 8.89  | 9.65  |

| Mold Draft Angle Top         | α               | 5       | 10    | 15    | 5           | 10    | 15    |

| Mold Draft Angle Bottom      | β               | 5       | 10    | 15    | 5           | 10    | 15    |

<sup>\*</sup> Controlling Parameter.

<sup>&</sup>lt;sup>†</sup> Dimension "B1" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B1."

<sup>&</sup>lt;sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E."

| RC4/SDI/SDA Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7, 9                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| RC5/SDO Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7, 9                                                         |

| RC6/TX/CK Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7, 9, 98                                                     |

| RC7/RX/DT Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7, 9, 98, 99                                                 |

| TRISC Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32, 97                                                       |

| PORTC Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13                                                           |

| PORTD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9, 15, 37                                                    |

| Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              |

| Parallel Slave Port (PSP) Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 34                                                           |

| PORTD Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                                                           |

| TRISD Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                                                           |

| PORTD Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13                                                           |

| PORTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9, 15                                                        |

| Analog Port Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9, 36, 37                                                    |

| Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35                                                           |

| Input Buffer Full Status (IBF Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35                                                           |

| Input Buffer Overflow (IBOV Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35                                                           |

| Output Buffer Full Status (OBF Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35                                                           |

| PORTE Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35                                                           |

| PSP Mode Select (PSPMODE Bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 34, 35, 37                                                   |

| RE0/RD/AN5 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9. 36. 37                                                    |

| RE1/WR/AN6 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                              |

| RE2/CS/AN7 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                              |

| TRISE Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                              |