# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 7KB (4K x 14)                                                           |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                             |

| Data Converters            | A/D 10x12b                                                              |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-QFP                                                                  |

| Supplier Device Package    | 44-MQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc774-pq |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

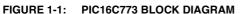

#### 1.0 DEVICE OVERVIEW

This document contains device-specific information. Additional information may be found in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023), which may be obtained from your local Microchip Sales Representative or downloaded from the Microchip website. The Reference Manual should be considered a complementary document to this data sheet, and is highly recommended reading for a better understanding of the device architecture and operation of the peripheral modules.

There a two devices (PIC16C773 and PIC16C774) covered by this datasheet. The PIC16C773 devices come in 28-pin packages and the PIC16C774 devices come in 40-pin packages. The 28-pin devices do not have a Parallel Slave Port implemented.

The following two figures are device block diagrams sorted by pin number; 28-pin for Figure 1-1 and 40-pin for Figure 1-2. The 28-pin and 40-pin pinouts are listed in Table 1-1 and Table 1-2, respectively.

#### 2.2.2.5 PIR1 REGISTER

This register contains the individual flag bits for the peripheral interrupts.

Note: Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 2-7: PIR1 REGISTER (ADDRESS 0Ch)

| R/W-0                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                           | R-0                                                                                                                                                                      | R-0         | R/W-0         | R/W-0                        | R/W-0        | R/W-0          |                                                                   |  |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|------------------------------|--------------|----------------|-------------------------------------------------------------------|--|--|

| PSPIF <sup>(1)</sup><br>bit7 | ADIF                                                                                                                                                                                                                                                                                                                                                                            | RCIF                                                                                                                                                                     | TXIF        | SSPIF         | CCP1IF                       | TMR2IF       | TMR1IF<br>bit0 | R = Readable bit<br>W = Writable bit                              |  |  |

| 2                            |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                          |             |               |                              |              | 5110           | U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |

| bit 7:                       |                                                                                                                                                                                                                                                                                                                                                                                 | d or a write                                                                                                                                                             | e operatio  | n has take    | e Interrupt I<br>en place (m |              | red in soft    | ware)                                                             |  |  |

| bit 6:                       | <b>ADIF</b> : A/E<br>1 = An A/I<br>0 = The A                                                                                                                                                                                                                                                                                                                                    | D convers                                                                                                                                                                | ion compl   | eted (mus     | t be cleared                 | d in softwa  | re)            |                                                                   |  |  |

| bit 5:                       | <b>RCIF</b> : US<br>1 = The U<br>0 = The U                                                                                                                                                                                                                                                                                                                                      | ISART rec                                                                                                                                                                | eive buffe  | r is full (cl | eared by re                  | ading RCF    | REG)           |                                                                   |  |  |

| bit 4:                       | <b>TXIF</b> : US/<br>1 = The U<br>0 = The U                                                                                                                                                                                                                                                                                                                                     | ISART trai                                                                                                                                                               | nsmit buffe | er is empty   | t<br>y (cleared              | by writing t | o TXREG)       |                                                                   |  |  |

| bit 3:                       | 1 = The tr                                                                                                                                                                                                                                                                                                                                                                      | <b>SSPIF</b> : Synchronous Serial Port Interrupt Flag bit<br>1 = The transmission/reception is complete (must be cleared in software)<br>0 = Waiting to transmit/receive |             |               |                              |              |                |                                                                   |  |  |

| bit 2:                       | 0 = Waiting to transmit/receive<br>CCP1IF: CCP1 Interrupt Flag bit<br>Capture Mode<br>1 = A TMR1 register capture occurred (must be cleared in software)<br>0 = No TMR1 register capture occurred<br>Compare Mode<br>1 = A TMR1 register compare match occurred (must be cleared in software)<br>0 = No TMR1 register compare match occurred<br>PWM Mode<br>Unused in this mode |                                                                                                                                                                          |             |               |                              |              |                |                                                                   |  |  |

| bit 1:                       | TMR2IF:<br>1 = TMR2<br>0 = No TM                                                                                                                                                                                                                                                                                                                                                | to PR2 m                                                                                                                                                                 | natch occu  | irred (mus    | Flag bit<br>t be cleared     | d in softwa  | re)            |                                                                   |  |  |

| bit 0:                       | <b>TMR1IF</b> : 1<br>1 = TMR1<br>0 = TMR1                                                                                                                                                                                                                                                                                                                                       | register o                                                                                                                                                               | overflowed  | l (must be    | bit<br>cleared in s          | software)    |                |                                                                   |  |  |

| Note 1:                      | PSPIF is                                                                                                                                                                                                                                                                                                                                                                        | reserved o                                                                                                                                                               | on the 28-  | pin device    | s, always m                  | naintain thi | s bit clear.   |                                                                   |  |  |

#### 2.2.2.7 PIR2 REGISTER

Γ

This register contains the CCP2, SSP Bus Collision, and Low-voltage detect interrupt flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 2-9: PIR2 REGISTER (ADDRESS 0Dh)

| R/W-0         | U-0                                                                                                                                                                                                                           | U-0                                                                                                                                                                                                                       | U-0        | R/W-0                    | U-0         | U-0        | R/W-0          |                                                                                                                |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------|-------------|------------|----------------|----------------------------------------------------------------------------------------------------------------|--|--|--|

| LVDIF<br>bit7 | _                                                                                                                                                                                                                             | _                                                                                                                                                                                                                         | _          | BCLIF                    |             | _          | CCP2IF<br>bit0 | <ul> <li>R = Readable bit</li> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> </ul> |  |  |  |

| bit 7:        | LVDIF: Low-voltage Detect Interrupt Flag bit         1 = The supply voltage has fallen below the specified LVD voltage (must be cleared in software)         0 = The supply voltage is greater than the specified LVD voltage |                                                                                                                                                                                                                           |            |                          |             |            |                |                                                                                                                |  |  |  |

| bit 6-4:      | Unimplen                                                                                                                                                                                                                      | nented: R                                                                                                                                                                                                                 | ead as '0  | 1                        |             |            |                |                                                                                                                |  |  |  |

| bit 3:        | 1 = A bus<br>(must be d                                                                                                                                                                                                       | BCLIF: Bus Collision Interrupt Flag bit<br>1 = A bus collision has occurred while the SSP module configured in I <sup>2</sup> C Master was transmitting<br>(must be cleared in software)<br>0 = No bus collision occurred |            |                          |             |            |                |                                                                                                                |  |  |  |

| bit 2-1:      | Unimplen                                                                                                                                                                                                                      | nented: R                                                                                                                                                                                                                 | ead as '0  | i                        |             |            |                |                                                                                                                |  |  |  |

| bit 0:        | CCP2IF: (                                                                                                                                                                                                                     | CCP2 Inte                                                                                                                                                                                                                 | rrupt Flag | bit                      |             |            |                |                                                                                                                |  |  |  |

|               | <u>Capture M</u><br>1 = A TMF<br>0 = No TM                                                                                                                                                                                    | R1 registe                                                                                                                                                                                                                |            |                          | nust be cle | ared in sc | ftware)        |                                                                                                                |  |  |  |

|               |                                                                                                                                                                                                                               | R1 registe                                                                                                                                                                                                                | •          | e match oc<br>re match o | •           | st be clea | red in softw   | are)                                                                                                           |  |  |  |

|               | <u>PWM Moo</u><br>Unused                                                                                                                                                                                                      | <u>de</u>                                                                                                                                                                                                                 |            |                          |             |            |                |                                                                                                                |  |  |  |

#### 2.3 PCL and PCLATH

The program counter (PC) specifies the address of the instruction to fetch for execution. The PC is 13 bits wide. The low byte is called the PCL register. This register is readable and writable. The high byte is called the PCH register. This register contains the PC<12:8> bits and is not directly readable or writable. All updates to the PCH register go through the PCLATH register.

#### 2.3.1 STACK

The stack allows a combination of up to 8 program calls and interrupts to occur. The stack contains the return address from this branch in program execution.

Midrange devices have an 8 level deep x 13-bit wide hardware stack. The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not modified when the stack is PUSHed or POPed.

After the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

#### 2.4 Program Memory Paging

PIC16C77X devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<4:3> bits are not required for the return instructions (which POPs the address from the stack).

#### TABLE 3-5 PORTC FUNCTIONS

| Name            | Bit# | Buffer Type | Function                                                                                       |

|-----------------|------|-------------|------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI | bit0 | ST          | Input/output port pin or Timer1 oscillator output/Timer1 clock input                           |

| RC1/T1OSI/CCP2  | bit1 | ST          | Input/output port pin or Timer1 oscillator input or Capture2 input/Compare2 output/PWM2 output |

| RC2/CCP1        | bit2 | ST          | Input/output port pin or Capture1 input/Compare1 output/PWM1<br>output                         |

| RC3/SCK/SCL     | bit3 | ST          | RC3 can also be the synchronous serial clock for both SPI and I <sup>2</sup> C modes.          |

| RC4/SDI/SDA     | bit4 | ST          | RC4 can also be the SPI Data In (SPI mode) or data I/O (I <sup>2</sup> C mode).                |

| RC5/SDO         | bit5 | ST          | Input/output port pin or Synchronous Serial Port data output                                   |

| RC6/TX/CK       | bit6 | ST          | Input/output port pin or USART Asynchronous transmit or<br>Synchronous clock                   |

| RC7/RX/DT       | bit7 | ST          | Input/output port pin or USART Asynchronous receive or<br>Synchronous data                     |

Legend: ST = Schmitt Trigger input

#### TABLE 3-6 SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name  | Bit 7   | Bit 6       | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR,<br>BOR | Value on all other resets |

|---------|-------|---------|-------------|------------|-------|-------|-------|-------|-------|--------------------------|---------------------------|

| 07h     | PORTC | RC7     | RC6         | RC5        | RC4   | RC3   | RC2   | RC1   | RC0   | xxxx xxxx                | uuuu uuuu                 |

| 87h     | TRISC | PORTC I | Data Direct | ion Regist | er    |       |       |       |       | 1111 1111                | 1111 1111                 |

Legend: x = unknown, u = unchanged.

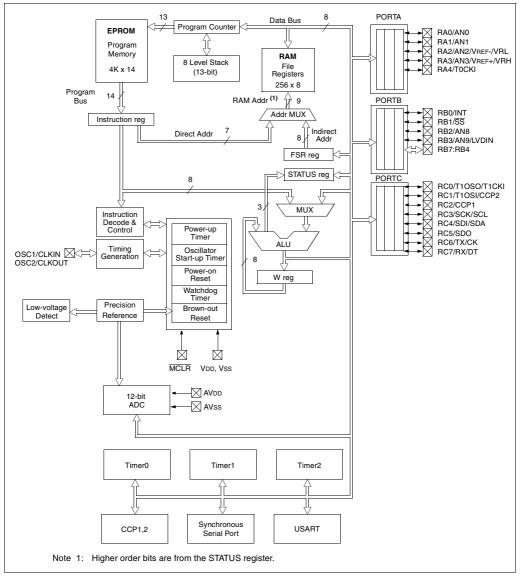

#### FIGURE 3-15: PARALLEL SLAVE PORT READ WAVEFORMS

#### TABLE 3-11 REGISTERS ASSOCIATED WITH PARALLEL SLAVE PORT

| Address | Name   | Bit 7    | Bit 6     | Bit 5      | Bit 4          | Bit 3    | Bit 2   | Bit 1       | Bit 0    | Value<br>PC<br>BC | R,   | Value<br>other |      |

|---------|--------|----------|-----------|------------|----------------|----------|---------|-------------|----------|-------------------|------|----------------|------|

| 08h     | PORTD  | Port dat | a latch w | hen writte | n: Port pins v | hen read |         |             |          | xxxx              | xxxx | uuuu           | uuuu |

| 09h     | PORTE  | _        | _         | _          | _              | —        | RE2     | RE1         | RE0      |                   | -xxx |                | -uuu |

| 89h     | TRISE  | IBF      | OBF       | IBOV       | PSPMODE        |          | PORTE I | Data Direct | ion Bits | 0000              | -111 | 0000           | -111 |

| 0Ch     | PIR1   | PSPIF    | ADIF      | RCIF       | TXIF           | SSPIF    | CCP1IF  | TMR2IF      | TMR1IF   | 0000              | 0000 | 0000           | 0000 |

| 8Ch     | PIE1   | PSPIE    | ADIE      | RCIE       | TXIE           | SSPIE    | CCP1IE  | TMR2IE      | TMR1IE   | 0000              | 0000 | 0000           | 0000 |

| 9Fh     | ADCON1 | ADFM     | VCFG2     | VCFG1      | VCFG0          | PCFG3    | PCFG2   | PCFG1       | PCFG0    | 0000              | 0000 | 0000           | 0000 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used by the Parallel Slave Port.

#### 4.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- · Readable and writable

- · Internal or external clock select

- · Edge select for external clock

- 8-bit software programmable prescaler

- Interrupt on overflow from FFh to 00h

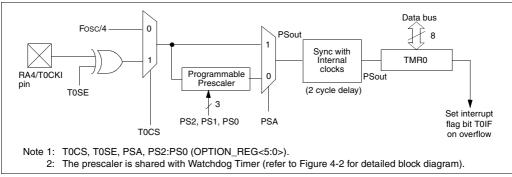

Figure 4-1 is a simplified block diagram of the Timer0 module.

Additional information on timer modules is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

#### 4.1 <u>Timer0 Operation</u>

Timer0 can operate as a timer or as a counter.

Timer mode is selected by clearing bit T0CS (OPTION\_REG<5>). In timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If the TMR0 register is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting bit T0CS (OPTION\_REG<5>). In counter mode, Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the Timer0 Source Edge Select bit T0SE (OPTION\_REG<4>). Clearing bit T0SE selects the rising edge. Restrictions on the external clock input are discussed in below.

When an external clock input is used for Timer0, it must meet certain requirements. The requirements ensure the external clock can be synchronized with the internal phase clock (Tosc). Also, there is a delay in the actual incrementing of Timer0 after synchronization. Additional information on external clock requirements is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

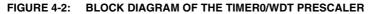

#### 4.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 4-2). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusively shared between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

The prescaler is not readable or writable.

The PSA and PS2:PS0 bits (OPTION\_REG<3:0>) determine the prescaler assignment and prescale ratio.

Clearing bit PSA will assign the prescaler to the Timer0 module. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, ..., 1:256 are selectable.

Setting bit PSA will assign the prescaler to the Watchdog Timer (WDT). When the prescaler is assigned to the WDT, prescale values of 1:1, 1:2, ..., 1:128 are selectable.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g. CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

Note: Writing to TMR0 when the prescaler is assigned to Timer0 will clear the prescaler count, but will not change the prescaler assignment.

#### FIGURE 4-1: TIMER0 BLOCK DIAGRAM

#### 4.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution.

Note: To avoid an unintended device RESET, a specific instruction sequence (shown in the PICmicro™ Mid-Range Reference Manual, DS33023) must be executed when changing the prescaler assignment from Timer0 to the WDT. This sequence must be followed even if the WDT is disabled.

#### 4.3 Timer0 Interrupt

The TMR0 interrupt is generated when the TMR0 register overflows from FFh to 00h. This overflow sets bit T0IF (INTCON<2>). The interrupt can be masked by clearing bit T0IE (INTCON<5>). Bit T0IF must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The TMR0 interrupt cannot awaken the processor from SLEEP since the timer is shut off during SLEEP.

#### TABLE 4-1 REGISTERS ASSOCIATED WITH TIMER0

| Address               | Name       | Bit 7  | Bit 6      | Bit 5                         | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR | Value on all other resets |

|-----------------------|------------|--------|------------|-------------------------------|-------|-------|-------|---------|---------|--------------------------|---------------------------|

| 01h,101h              | TMR0       | Timer0 | module's r | egister                       |       |       |       |         |         | xxxx xxxx                | uuuu uuuu                 |

| 0Bh,8Bh,<br>10Bh,18Bh | INTCON     | GIE    | PEIE       | TOIE                          | INTE  | RBIE  | TOIF  | INTF    | RBIF    | 0000 000x                | 0000 000u                 |

| 81h,181h              | OPTION_REG | RBPU   | INTEDG     | TOCS                          | TOSE  | PSA   | PS2   | PS1     | PS0     | 1111 1111                | 1111 1111                 |

| 85h                   | TRISA      | _      | _          | PORTA Data Direction Register |       |       |       | 11 1111 | 11 1111 |                          |                           |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

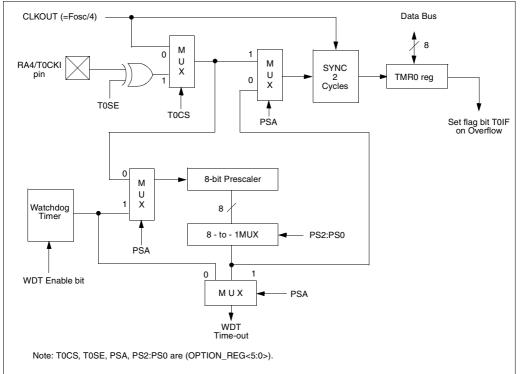

#### 7.0 CAPTURE/COMPARE/PWM (CCP) MODULE(S)

Each CCP (Capture/Compare/PWM) module contains a 16-bit register which can operate as a 16-bit capture register, as a 16-bit compare register or as a PWM master/slave Duty Cycle register. Table 7-1 shows the timer resources of the CCP module modes.

The operation of CCP1 is identical to that of CCP2, with the exception of the special trigger. Therefore, operation of a CCP module in the following sections is described with respect to CCP1.

Table 7-2 shows the interaction of the CCP modules.

#### CCP1 Module

Capture/Compare/PWM Register1 (CCPR1) is comprised of two 8-bit registers: CCPR1L (low byte) and CCPR1H (high byte). The CCP1CON register controls the operation of CCP1. All are readable and writable.

#### CCP2 Module

Capture/Compare/PWM Register2 (CCPR2) is comprised of two 8-bit registers: CCPR2L (low byte) and CCPR2H (high byte). The CCP2CON register controls the operation of CCP2. All are readable and writable.

Additional information on the CCP module is available in the PICmicro<sup>™</sup> Mid-Range Reference Manual, (DS33023).

#### TABLE 7-1 CCP MODE - TIMER RESOURCE

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

| CCPx Mode | CCPy Mode | Interaction                                                                           |

|-----------|-----------|---------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time-base.                                                                  |

| Capture   | Compare   | The compare should be configured for the special event trigger, which clears TMR1.    |

| Compare   | Compare   | The compare(s) should be configured for the special event trigger, which clears TMR1. |

| PWM       | PWM       | The PWMs will have the same frequency, and update rate (TMR2 interrupt).              |

| PWM       | Capture   | None                                                                                  |

| PWM       | Compare   | None                                                                                  |

#### TABLE 7-2 INTERACTION OF TWO CCP MODULES

#### FIGURE 7-1: CCP1CON REGISTER (ADDRESS 17h) / CCP2CON REGISTER (ADDRESS 1Dh)

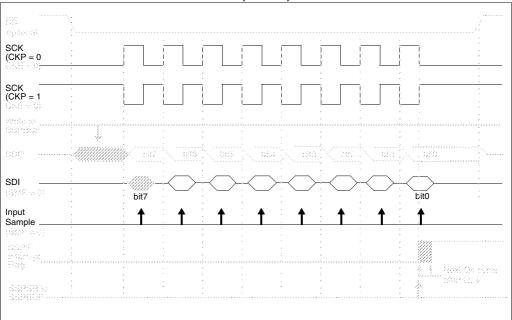

#### FIGURE 8-8: SPI SLAVE MODE WAVEFORM (CKE = 0)

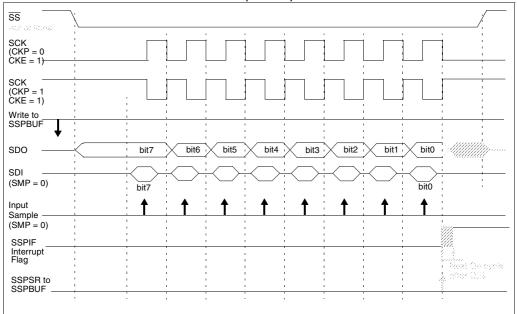

#### FIGURE 8-9: SPI SLAVE MODE WAVEFORM (CKE = 1)

#### 8.2.11 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address, or either half of a 10-bit address is accomplished by simply writing a value to SSPBUF register. This action will set the buffer full flag (BF) and allow the baud rate generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time spec). SCL is held low for one baud rate generator roll over count (T<sub>BRG</sub>). Data should be valid before SCL is released high (see Data setup time spec). When the SCL pin is released high, it is held that way for T<sub>BRG</sub>, the data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA allowing the slave device being addressed to respond with an ACK bit during the ninth bit time, if an address match occurs or if data was received properly. The status of ACK is read into the AKDT on the falling edge of the ninth clock. If the master receives an acknowledge, the acknowledge status bit (AKSTAT) is cleared. If not, the bit is set. After the ninth clock the SSPIF is set, and the master clock (baud rate generator) is suspended until the next data byte is loaded into the SSPBUF leaving SCL low and SDA unchanged (Figure 8-26).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock the master will de-assert the SDA pin allowing the slave to respond with an acknowledge. On the falling edge of the ninth clock the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the AKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared, and the baud rate generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 8.2.11.7 BF STATUS FLAG

In transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

#### 8.2.11.8 WCOL STATUS FLAG

If the user writes the SSPBUF when a transmit is already in progress (i.e. SSPSR is still shifting out a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

#### 8.2.11.9 AKSTAT STATUS FLAG

In transmit mode, the AKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an acknowledge  $(\overline{ACK} = 0)$ , and is set when the slave does not acknowledge  $(\overline{ACK} = 1)$ . A slave sends an acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

#### 8.2.12 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the receive enable bit, RCEN (SSPCON2<3>).

| Note: | The SSP Module must be in an IDLE        |

|-------|------------------------------------------|

|       | STATE before the RCEN bit is set, or the |

|       | RCEN bit will be disregarded.            |

The baud rate generator begins counting, and on each rollover, the state of the SCL pin changes (high to low/ low to high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag is set, the SSPIF is set, and the baud rate generator is suspended from counting, holding SCL low. The SSP is now in IDLE state, awaiting the next command. When the buffer is read by the CPU, the BF flag is automatically cleared. The user can then send an acknowledge bit at the end of reception, by setting the acknowledge sequence enable bit, AKEN (SSPCON2<4>).

#### 8.2.12.10 BF STATUS FLAG

In receive operation, BF is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when SSPBUF is read.

#### 8.2.12.11 SSPOV STATUS FLAG

In receive operation, SSPOV is set when 8 bits are received into the SSPSR, and the BF flag is already set from a previous reception.

#### 8.2.12.12 WCOL STATUS FLAG

If the user writes the SSPBUF when a receive is already in progress (i.e. SSPSR is still shifting in a data byte), then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### 8.2.15 CLOCK ARBITRATION

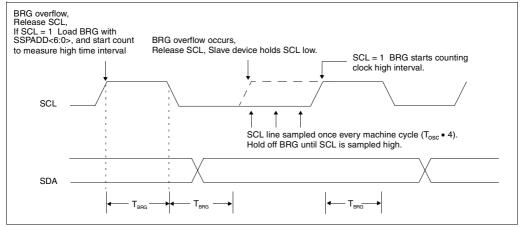

Clock arbitration occurs when the master, during any receive, transmit, or repeated start/stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the baud rate generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the baud rate generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 8-33).

#### 8.2.16 SLEEP OPERATION

While in sleep mode, the I<sup>2</sup>C module can receive addresses or data, and when an address match or complete byte transfer occurs wake the processor from sleep (if the SSP interrupt is enabled).

#### 8.2.17 EFFECTS OF A RESET

A reset disables the SSP module and terminates the current transfer.

#### FIGURE 8-33: CLOCK ARBITRATION TIMING IN MASTER TRANSMIT MODE

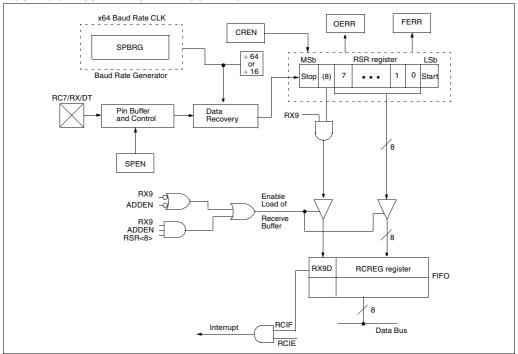

#### FIGURE 9-6: USART RECEIVE BLOCK DIAGRAM

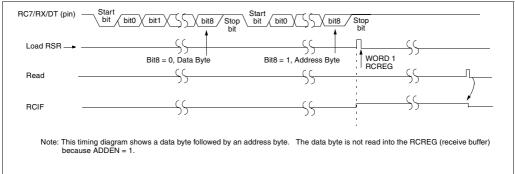

#### FIGURE 9-7: ASYNCHRONOUS RECEPTION WITH ADDRESS DETECT

#### 10.3 Low-voltage Detect (LVD)

This module is used to generate an interrupt when the supply voltage falls below a specified "trip" voltage. This module operates completely under software

control. This allows a user to power the module on and off to periodically monitor the supply voltage, and thus minimize total current consumption.

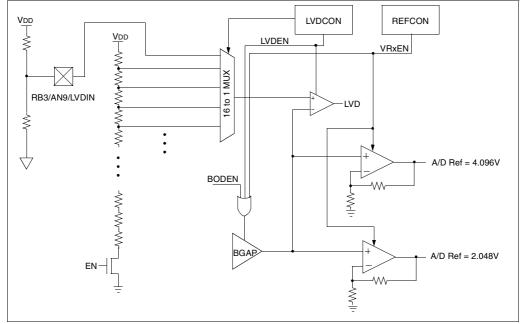

FIGURE 10-3: BLOCK DIAGRAM OF LVD AND VOLTAGE REFERENCE CIRCUIT

The LVD module is enabled by setting the LVDEN bit in the LVDCON register. The "trip point" voltage is the minimum supply voltage level at which the device can operate before the LVD module asserts an interrupt. When the supply voltage is equal to or less than the trip point, the module will generate an interrupt signal setting interrupt flag bit LVDIF. If interrupt enable bit LVDIE was set, then an interrupt is generated. The LVD interrupt can wake the device from sleep. The "trip point" voltage is software programmable to any one of 16 values, five of which are reserved (See Figure 10-1). The trip point is selected by programming the LV3:LV0 bits (LVDCON<3:0>).

Note: The LVDIF bit can not be cleared until the supply voltage rises above the LVD trip point. If interrupts are enabled, clear the LVDIE bit once the first LVD interrupt occurs to prevent reentering the interrupt service routine immediately after exiting the ISR.

Once the LV bits have been programmed for the specified trip voltage, the low-voltage detect circuitry is then enabled by setting the LVDEN (LVDCON<4>) bit. If the bandgap reference voltage is previously unused by either the brown-out circuitry or the voltage reference circuitry, then the bandgap circuit requires a time to start-up and become stable before a low voltage condition can be reliably detected. The low-voltage interrupt flag is prevented from being set until the bandgap has reached a stable reference voltage.

When the bandgap is stable the BGST (LVDCON<5>) bit is set indicating that the low-voltage interrupt flag bit is released to be set if VDD is equal to or less than the LVD trip point.

#### 10.3.1 EXTERNAL ANALOG VOLTAGE INPUT

The LVD module has an additional feature that allows the user to supply the trip voltage to the module from an external source. This mode is enabled when LV3:LV0 = 1111. When these bits are set the comparator input is multiplexed from an external input pin (RB3/AN9/LVDIN.

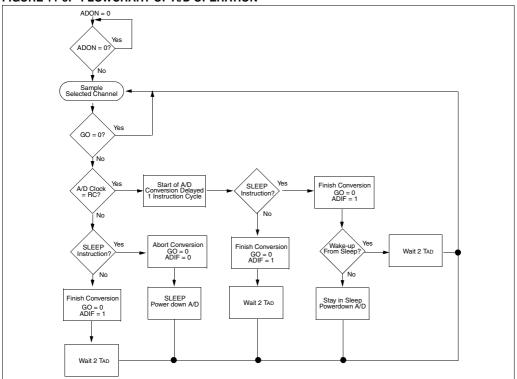

#### 11.4 Selecting the A/D Conversion Clock

The A/D conversion cycle requires 13TAD: 1 TAD for settling time, and 12 TAD for conversion. The source of the A/D conversion clock is software selected. The four possible options for TAD are:

- 2 Tosc

- 8 Tosc

- 32 Tosc

- Internal RC oscillator

#### TABLE 11-1 TAD VS. DEVICE OPERATING FREQUENCIES

Note that these options are the same as those of the 8-bit A/D.

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 1.6  $\mu s.$  Table 11-1 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

The ADIF bit is set on the rising edge of the 14th TAD. The GO/DONE bit is cleared on the falling edge of the 14th TAD.

| AD Clock  | k Source (TAD) | Device Frequency          |                           |                           |                           |  |  |  |  |

|-----------|----------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|--|--|

| Operation | ADCS<1:0>      | 20 MHz                    | 5 MHz                     | 4 MHz                     | 1.25 MHz                  |  |  |  |  |

| 2 Tosc    | 00             | 100 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 500 ns <sup>(2)</sup>     | 1.6 μs                    |  |  |  |  |

| 8 Tosc    | 01             | 800 ns <sup>(2)</sup>     | 1.6 μs                    | 2.0 μs                    | 6.4 μs                    |  |  |  |  |

| 32 Tosc   | 10             | 1.6 μs                    | 6.4 μs                    | 8.0 μs <sup>(3)</sup>     | 24 μs <sup>(3)</sup>      |  |  |  |  |

| RC        | 11             | 2 - 6 μs <sup>(1,4)</sup> |  |  |  |  |

Note 1: The RC source has a typical TAD time of 4  $\mu s$  for VDD > 3.0V.

2: These values violate the minimum required TAD time.

3: For faster conversion times, the selection of another clock source is recommended.

4: When the device frequency is greater than 1 MHz, the RC A/D conversion clock source is only recommended if the conversion will be performed during sleep.

#### 11.5 A/D Conversions

Figure 11-5 shows an example that performs an A/D conversion. The port pins are configured as analog inputs. The analog reference VREF+ is the device AVDD and the analog reference VREF- is the device AVSS. The A/D interrupt is enabled, and the A/D conversion clock is TRc. The conversion is performed on the ANO channel.

#### FIGURE 11-4: PERFORMING AN A/D CONVERSION

|   | BCF       | PIR1, ADIF       | ;Clear A/D Int Flag       |

|---|-----------|------------------|---------------------------|

|   | BSF       | STATUS, RPO      | ;Select Page 1            |

|   | CLRF      | ADCON1           | ;Configure A/D Inputs     |

|   | BSF       | PIE1, ADIE       | ;Enable A/D interrupt     |

|   | BCF       | STATUS, RPO      | ;Select Page 0            |

|   | MOVLW     | 0xC1             | ;RC clock, A/D is on,     |

|   |           |                  | ;Ch 0 is selected         |

|   | MOVWF     | ADCON0           | ;                         |

|   | BSF       | INTCON, PEIE     | ;Enable Peripheral        |

|   | BSF       | INTCON, GIE      | ;Enable All Interrupts    |

| ; |           |                  |                           |

| ; | Ensure tl | hat the required | d sampling time for the   |

| ; | selected  | input channel h  | nas lapsed. Then the      |

| ; | conversio | on may be starte | ed.                       |

|   | BSF       | ADCON0, GO       | ;Start A/D Conversion     |

|   |           | :                | ;The ADIF bit will be     |

|   |           |                  | ;set and the GO/DONE bit  |

|   |           | :                | ;cleared upon completion- |

|   |           |                  | ;of the A/D conversion.   |

#### 15.4 DC Characteristics: VREF

#### TABLE 15-2 ELECTRICAL CHARACTERISTICS: VREF

| DC CHAR      | ACTERISTICS                  | Operating ter | Derating Conditions (unless otherwise stated)<br>mperature -40°C ≤ TA ≤ +85°C for industrial and<br>0°C ≤ TA ≤ +70°C for commercial<br>Itage VDD range as described in DC spec Section 15.1 and Section 15. |     |              |                     |         |                                 |  |  |

|--------------|------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------|---------------------|---------|---------------------------------|--|--|

| Param<br>No. | Characte                     |               | Symbol                                                                                                                                                                                                      | Min | Typ†         | Max                 | Units   | Conditions                      |  |  |

| D400         | Output Voltage               |               | VRL                                                                                                                                                                                                         | 2.0 | 2.048        | 2.1                 | V       | $VDD \ge 2.5V$                  |  |  |

|              |                              |               | VRH                                                                                                                                                                                                         | 4.0 | 4.096        | 4.2                 | V       | VDB ≥ 4.5V                      |  |  |

| D401A        | VRL Quiescent Supply Current |               | $\Delta IVRL$                                                                                                                                                                                               | —   | 70           | TBD                 | μΑ      | No load on VRL.                 |  |  |

| D401B        | VRH Quiescent Supply Current |               | $\Delta IVRH$                                                                                                                                                                                               | _   | 70           | TBD                 | µtA     | No load on VRH.                 |  |  |

| D402         | Ouput Voltage Drift          |               | TCVOUT                                                                                                                                                                                                      | —   | 15*          | 50*                 | ppm/°C/ | Note 1                          |  |  |

| D404         | External Load Source         |               | IVREFSO                                                                                                                                                                                                     | —   | —            | ,5*                 | (mA     |                                 |  |  |

| D405         | External Load Sink           |               | IVREFSI                                                                                                                                                                                                     | —   | —            | <- <del>5</del> * \ | ∖mA     | $\square$                       |  |  |

| D406         | Load Regulation              |               |                                                                                                                                                                                                             | —   | $\checkmark$ | †βD∕{               |         | Isource = 0 mA to               |  |  |

|              |                              |               | ΔVout/<br>Δlout                                                                                                                                                                                             | ~   | 17           | TBD*                | mV/mA   | 5 mA<br>Isink = 0 mA to<br>5 mA |  |  |

| D407         | Line Regulation              |               | AVOUT/<br>AVDD                                                                                                                                                                                              | A   | _/           | \$0*                | μV/V    |                                 |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Production tested at TAMB  $= 25^{\circ}$ C. Specifications over temp limits guaranteed by characterization.

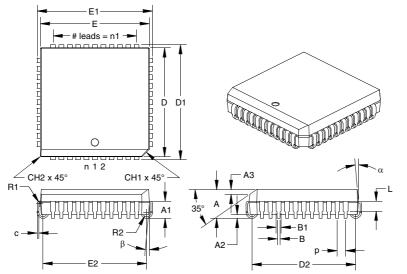

#### 17.10 K04-048 44-Lead Plastic Leaded Chip Carrier (L) – Square

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                   |                 |       | INCHES* |       | MILLIMETERS |       |       |

|-------------------------|-----------------|-------|---------|-------|-------------|-------|-------|

| Dimension Limits        |                 | MIN   | NOM     | MAX   | MIN         | NOM   | MAX   |

| Number of Pins          | n               |       | 44      |       |             | 44    |       |

| Pitch                   | р               |       | 0.050   |       |             | 1.27  |       |

| Overall Pack. Height    | А               | 0.165 | 0.173   | 0.180 | 4.19        | 4.38  | 4.57  |

| Shoulder Height         | A1              | 0.095 | 0.103   | 0.110 | 2.41        | 2.60  | 2.79  |

| Standoff                | A2              | 0.015 | 0.023   | 0.030 | 0.38        | 0.57  | 0.76  |

| Side 1 Chamfer Dim.     | A3              | 0.024 | 0.029   | 0.034 | 0.61        | 0.74  | 0.86  |

| Corner Chamfer (1)      | CH1             | 0.040 | 0.045   | 0.050 | 1.02        | 1.14  | 1.27  |

| Corner Chamfer (other)  | CH2             | 0.000 | 0.005   | 0.010 | 0.00        | 0.13  | 0.25  |

| Overall Pack. Width     | E1              | 0.685 | 0.690   | 0.695 | 17.40       | 17.53 | 17.65 |

| Overall Pack. Length    | D1              | 0.685 | 0.690   | 0.695 | 17.40       | 17.53 | 17.65 |

| Molded Pack. Width      | E‡              | 0.650 | 0.653   | 0.656 | 16.51       | 16.59 | 16.66 |

| Molded Pack. Length     | D‡              | 0.650 | 0.653   | 0.656 | 16.51       | 16.59 | 16.66 |

| Footprint Width         | E2              | 0.610 | 0.620   | 0.630 | 15.49       | 15.75 | 16.00 |

| Footprint Length        | D2              | 0.610 | 0.620   | 0.630 | 15.49       | 15.75 | 16.00 |

| Pins along Width        | n1              |       | 11      |       |             | 11    |       |

| Lead Thickness          | с               | 0.008 | 0.010   | 0.012 | 0.20        | 0.25  | 0.30  |

| Upper Lead Width        | B1 <sup>†</sup> | 0.026 | 0.029   | 0.032 | 0.66        | 0.74  | 0.81  |

| Lower Lead Width        | В               | 0.015 | 0.018   | 0.021 | 0.38        | 0.46  | 0.53  |

| Upper Lead Length       | L               | 0.050 | 0.058   | 0.065 | 1.27        | 1.46  | 1.65  |

| Shoulder Inside Radius  | R1              | 0.003 | 0.005   | 0.010 | 0.08        | 0.13  | 0.25  |

| J-Bend Inside Radius    | R2              | 0.015 | 0.025   | 0.035 | 0.38        | 0.64  | 0.89  |

| Mold Draft Angle Top    | α               | 0     | 5       | 10    | 0           | 5     | 10    |

| Mold Draft Angle Bottom | β               | 0     | 5       | 10    | 0           | 5     | 10    |

Controlling Parameter.

<sup>†</sup> Dimension "B1" does not include dam-bar protrusions. Dam-bar protrusions shall not exceed 0.003" (0.076 mm) per side or 0.006" (0.152 mm) more than dimension "B1."

<sup>‡</sup> Dimensions "D" and "E" do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010" (0.254 mm) per side or 0.020" (0.508 mm) more than dimensions "D" or "E." JEDEC equivalent:MO-047 AC

### Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tei: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820